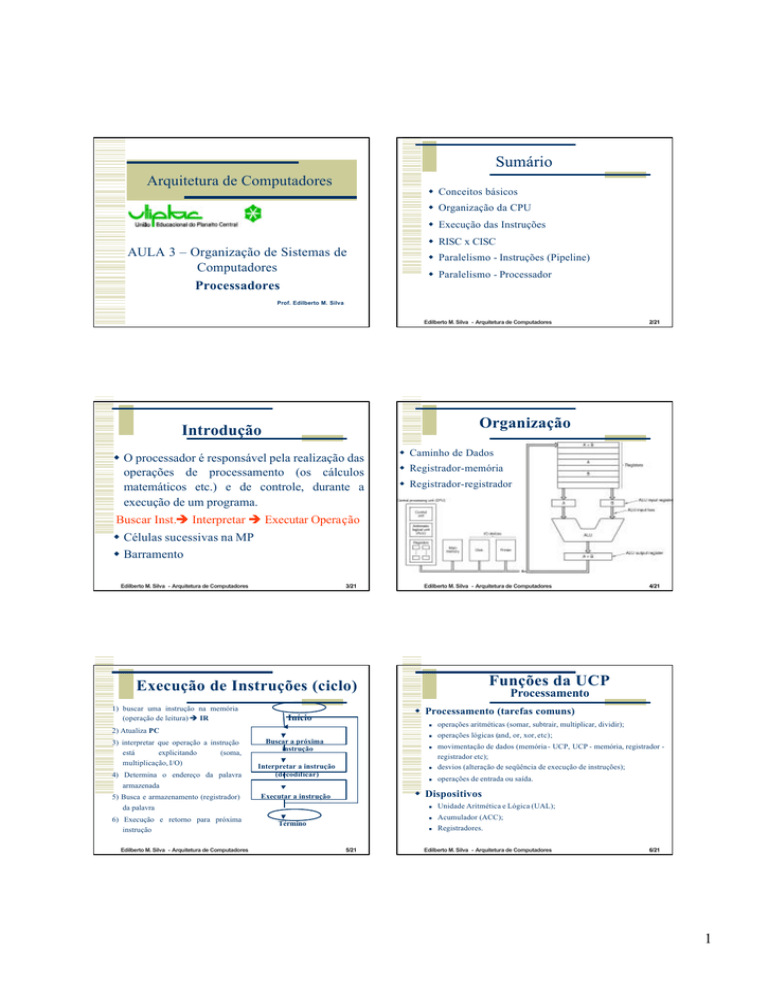

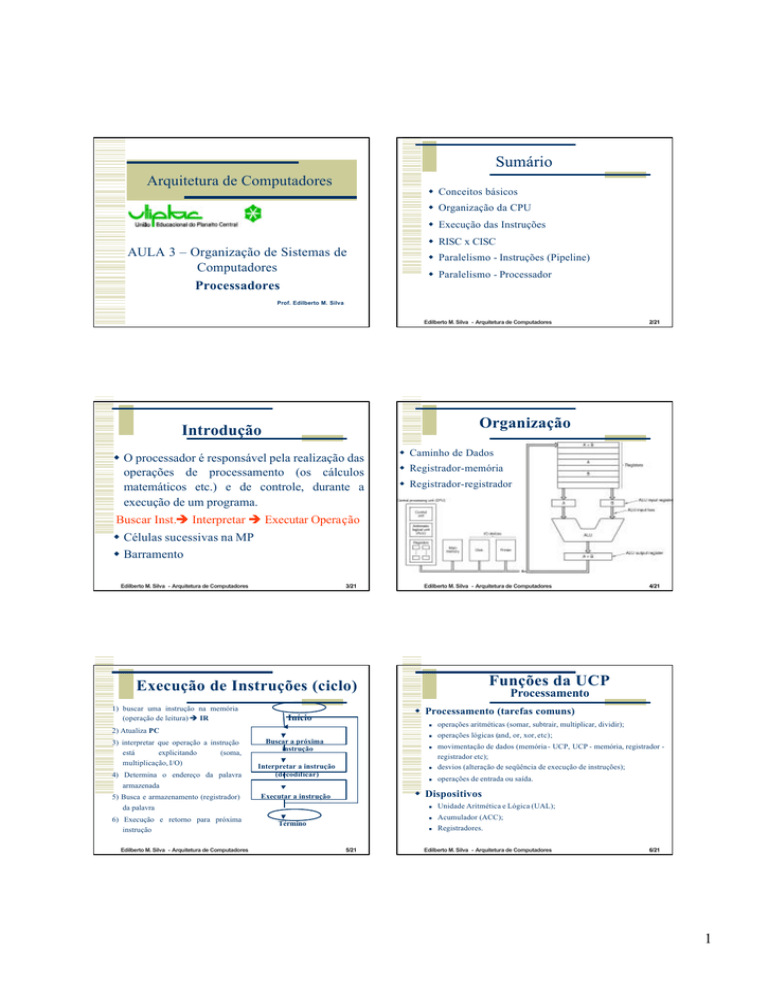

Sumário

Arquitetura de Computadores

w Conceitos básicos

w Organização da CPU

w Execução das Instruções

w RISC x CISC

AULA 3 – Organização de Sistemas de

Computadores

Processadores

w Paralelismo - Instruções (Pipeline)

w Paralelismo - Processador

Prof. Edilberto M. Silva

Edilberto M. Silva - Arquitetura de Computadores

2/21

Organização

Introdução

w O processador é responsável pela realização das

operações de processamento (os cálculos

matemáticos etc.) e de controle, durante a

execução de um programa.

w Caminho de Dados

w Registrador-memória

w Registrador-registrador

Buscar Inst.è Interpretar è Executar Operação

w Células sucessivas na MP

w Barramento

Edilberto M. Silva - Arquitetura de Computadores

3/21

Edilberto M. Silva - Arquitetura de Computadores

Funções da UCP

Execução de Instruções (ciclo)

1) buscar uma instrução na memória

(operação de leitura) è IR

Processamento

w Processamento (tarefas comuns)

Início

n

2) Atualiza PC

3) interpretar que operação a instrução

está

explicitando

(soma,

multiplicação, I/O)

4) Determina o endereço da palavra

armazenada

5) Busca e armazenamento (registrador)

da palavra

6) Execução e retorno para próxima

instrução

Edilberto M. Silva - Arquitetura de Computadores

4/21

n

Buscar a próxima

instrução

n

movimentação de dados (memória - UCP, UCP - memória, registrador registrador etc);

desvios (alteração de seqüência de execução de instruções);

n

operações de entrada ou saída.

n

Interpretar a instrução

(decodificar)

operações aritméticas (somar, subtrair, multiplicar, dividir);

operações lógicas (and, or, xor, etc);

w Dispositivos

Executar a instrução

Término

n

Unidade Aritmética e Lógica (UAL);

n

Acumulador (ACC);

Registradores.

n

5/21

Edilberto M. Silva - Arquitetura de Computadores

6/21

1

UCP - Esquema simplificado

Funções da UCP

Controle

w Controle (tarefas comuns)

n

n

atividades de busca

interpretação e controle da execução das instruções

controle da ação de componentes (memória, entrada/saída).

RDM

ACC

UAL

Registradores

REM

CI(PC)

Barramento

de endereços

w Dispositivos

n

n

n

n

n

n

unidade de controle (UC);

Decodificador;

Registrador de Instrução (RI)

Contador de Instrução (CI) ou PC “Program Counter”;

relógio ou "clock";

registradores de endereço de memória (REM) e de dados da

memória (RDM).

Edilberto M. Silva - Arquitetura de Computadores

7/21

Relógio

n

Op. lógica AND, OR e XOR;

n

deslocamentos à direita e à esquerda;

n

incremento e decremento;

n

op complemento.

Edilberto M. Silva - Arquitetura de Computadores

Decodificador

de instruções

UC

Edilberto M. Silva - Arquitetura de Computadores

8/21

w Dado ou Resultado - armazenados em um

registrador (memória da UCP)

n

Reutilização ou transferência para MP

Dado/Resultado è UAL

w ACC - ligação da UAL com os outros

dispositivos da UCP

9/21

A influência do tamanho da

palavra

Edilberto M. Silva - Arquitetura de Computadores

10/21

A influência do tamanho da palavra

Exemplo

w Capacidade de processamento (ciclo de

instrução)

w Determina o tamanho dos elementos ligados à

área de processamento, entre estes, a UAL.

w Acarreta

diferenças

fundamentais

de

desempenho da UCP

w Sejam os valores A = 3A25 e B = 172C

l

Inteiros, sem sinal e com 16 bits de tamanho cada

Sistema 2 ( Intel 8086)

Sistema 1 ( Intel 8080/8085)

palavra 8 bits; MP 64K com

células de 8 bits cada uma

palavra de 16 bits; MP 1M células com

células de 8 bits cada uma

UCP

UCP

8 bits

16 bits

MP

25 + 2C (1º)

3A + 17 (2º)

UAL

11/21

MP

3A

8 bits

ACC

25

17

2C

8 bits

Edilberto M. Silva - Arquitetura de Computadores

Barramento

de controle

Registradores

w Dispositivo da UCP que executa realmente as

operações matemáticas com os dados.

soma, multiplicação, subtração e divisão;

Dados/

Endereço

Controle

IR

Unidade Aritmética e Lógica

UAL

n

MP

n

Barramento

de dados

UCP

Edilberto M. Silva - Arquitetura de Computadores

3A

3A25 + 172C

(1º)

UAL

16 bits

ACC

25

17

2C

16 bits

12/21

2

Funções de Controle

Funções de Controle

w Unidade de Controle (UC)

w Registrador de Instrução – RI

n

É o dispositivo mais complexo da UCP.

Movimentação de dados e instruções de/e para a

UCP

n

Controla a ação da UAL.

n

n

Gerador de pulsos (ciclo)

Define freqüência (velocidade da UCP)

Edilberto M. Silva - Arquitetura de Computadores

armazenar a instrução a ser executada pela UCP

n

emite o sinal de controle que acarretará a realização

de um ciclo de leitura

w Program Counter

w Relógio

n

n

n

13/21

armazenar o endereço da próxima instrução a ser

executada.

Edilberto M. Silva - Arquitetura de Computadores

Funções de Controle

CISC x RISC

w CISC - Complex Instruction Set Computer

w Decodificador de Instrução

n

Identificar as operações a serem realizadas, que

estão correlacionadas à instrução em execução

w RDM – Registrador de Dados da Memória

REM – Registrador de Endereço da Memória

n

15/21

n

Compatibilidade com máquinas + antigas

n

Incorporação da tecnologia RISC (núcleo)

w RISC - Reduced Complex Instruction Set Computer

Comunicação e transferências de informações entre

a UCP e a MP

Edilberto M. Silva - Arquitetura de Computadores

n

Conjunto menor de instruções

n

Execução otimizada de chamada de funções

n

Menor quantidade de modos de endereçamento

n

Alta produtividade de pipelining

Edilberto M. Silva - Arquitetura de Computadores

Paralelismo no

Nível de Instrução

16/21

Paralelismo no

Nível de Instrução (Pipeline)

w Pipeline

n

14/21

6

Consiste em dividir o ciclo de instrução em estágios

independentes que podem se superpor uns aos outros no

tempo.

7

8

9

10

11

Tempo

T

a

r

e

f

a

s

s

e

q

30 40 20 30 40 20 30 40 20 30 40 20

A

B

C

A

B

C

4

D

pessoas

Lavar 30’

Secar 40’

Dobrar 20’

D

w Lavanderia sequencial leva 6 horas para terminar

w Se eles conhecessem computação, quanto tempo levaria?

Edilberto M. Silva - Arquitetura de Computadores

17/21

Edilberto M. Silva - Arquitetura de Computadores

18/21

3

Paralelismo no

Nível de Processador

Lavanderia com Pipeline

6

7

8

9

w Pipelining não melhora a

latência de uma única

tarefa, mas melhora o

30 40 40 40 40 20

T

throughput do trabalho

a

A

todo

r

e

w

Taxa de inserção de

f

B

tarefas é limitada pela

a

s

tarefa mais lenta

C

s

w Existem múltiplas

e

D

tarefas sendo executadas

q

em um dado instante

w Lavanderia com pipelining leva 3.5 horas !!!

Tempo

Edilberto M. Silva - Arquitetura de Computadores

19/21

® Computadores Matriciais

n

Processador Matricial - Vários processadores iguais / mesma

sequência

n

Processador Vetorial – Vários processadores e Uma única UAL

w Multiprocessadores

w Multicomputadores

Edilberto M. Silva - Arquitetura de Computadores

20/21

FIM

Edilberto M. Silva - Arquitetura de Computadores

21/21

4