Projeto de um Sistema de Medição e Circuitos de Interface Integrados para

Caracterização de Células de Memória de Corrente Chaveada

Adriano M. Pereira1, Robson L. Moreno1, Alberto Martins Jorge2, Edgar Charry R. 3

1- Grupo de Microeletrônica - Escola Federal de Engenharia de Itajubá (EFEI)

Caixa Postal 50 - CEP 37500-000 - Itajubá, MG - Brasil

2- DEMIC - Faculdade de Engenharia Elétrica e de Computação - UNICAMP

Caixa Postal 6101 - CEP 13081-970 - Campinas, SP - Brasil

3- Divisão de Microeletrônica, CPqD - Telebrás

Caixa Postal 1579 - CEP 13088-061 - Campinas - SP - Brasil

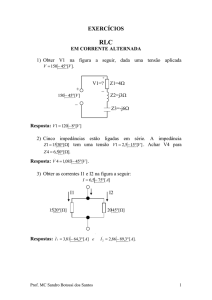

entrada e o dispositivo de saída de um espelho.

Abstract - Dynamic current mirrors, or SI memory

cells, are widely used in analog signal processing

circuits, which can be implemented using any standard

cell metodology, if an SI cell´s library is available.

Aiming the creation of that library, this work presents

the project of the measuring system and the interface

circuits (on chip) necessary to test the SI cells, having

a precision of 450ppm and a clock rate of 3MHz.

Measurements performed on the prototypes of the

interface circuit (V/I converter) show a 68dB signal-tonoise ratio and a total harmonic distortion of 0.04%.

Ib

S2

S3

Iin

φ1

Iout

φ2

S1

φ1

M1

1- Introdução

Clock Phases

Em espelhos de corrente convencionais, há a

necessidade de pelo menos dois transistores. No

transistor de entrada, conectado como diodo, é

aplicada uma corrente Iin, a qual gera uma tensão gatesource de referência. Esta tensão é aplicada ao gate do

transistor de saída, o qual drena uma corrente Iout. Se

os dois transistores tiverem a mesma área e forem

perfeitamente casados, a corrente Iout será igual a Iin.

Portanto, os espelhos convencionais dependem muito

das variações no processo de fabricação e geralmente

exigem transistores grandes para um bom casamento.

Isto, além de aumentar a área do circuito, também

diminui a máxima frequência das correntes a serem

espelhadas, devido ao aumento das capacitâncias dos

transistores.

Nos transistores MOS existe um isolamento

quase perfeito no eletrodo de gate. Por isto, estes

dispositivos tem a capacidade de armazenar

temporariamente alguma informação analógica nos

capacitores de gate. Esta propriedade é a base para o

funcionamento do espelho de corrente dinâmico, ou

célula de memória de corrente chaveada (célula SI). A

Fig. 1 mostra a célula de memória básica. O seu

funcionamento consiste em aplicar os sinais de clock

φ1 e φ2, de forma que o transistor M1 seja

sequencialmente conectado como o dispositivo de

φ1

φ2

Figura 1 : Célula de memória de corrente básica e

sinais de controle.

Na célula básica (Fig. 1), inicialmente as chaves

S1 e S2 estão fechadas (φ1 em nível alto), fazendo com

que a capacitância gate-source (CGS) de M1 se

carregue com uma tensão tal que a corrente de dreno

de M1 seja igual a Iin. Após isto, as chaves S1 e S2 se

abrem e S3 se fecha (φ1 em nível baixo e φ2 em nível

alto), conectando o transistor M1 como dispositivo de

saída. A tensão que foi memorizada na primeira fase

faz com que M1 drene uma corrente Iout igual a Iin.

Assim, utilizando o mesmo transistor como dispositivo

de entrada e de saída, o problema de casamento ou

linearidade de capacitores ou transistores desaparece,

ou seja, há uma insensibilidade às variações de

processo. Como nas células de memória de corrente

chaveada (SI) o único componente requerido é o

transistor MOS, os circuitos SI são totalmente

compatíveis com processos CMOS digital padrão. Por

estas e outras vantagens, as células SI são muito

utilizadas em aplicações na área de processamento de

sinais. As que tem sido reportadas na literatura,

enfatizam que os circuitos possuem pequena área e

baixo consumo [1,2,3].

Os fatores limitantes à precisão desses espelhos

são, principalmente, a injeção de carga e o clock

feedthrough no capacitor de memorização do gate e a

condutância de saída das células SI. A injeção de carga

é minimizada usando chaves cuidadosamente

projetadas e controlando algumas tensões de gate

[4,5,6]. O efeito da condutância de saída é reduzido

com estruturas cascode [7,8] ou conveyor de corrente

[6]. Utilizando-se destas e de outras técnicas para

corrigir as não idealidades da memorização da

corrente, é possível obter células SI com precisão da

ordem de 50ppm [6].

2-Biblioteca de células de memória SI para

utilização

em

circuitos

analógicos

de

processamtento de sinais

As células de memorização de corrente

apresentam uma enorme gama de aplicações, tais

como redes neurais [9], filtros[10], conversores D/A

[2] e A/D [6,9,11], sendo a célula SI o circuito

principal nestes casos. Em tais circuitos o sucesso do

projeto depende basicamente do bom desempenho da

célula de memória em relação a precisão DC, distorção

harmônica, frequência de chaveamento, etc. Para

realizar simulações elétricas destes circuitos que

utilizam várias células, toma-se muito tempo e surgem

muitos problemas de convergência, devido ao

chaveamento das correntes. Além disso, o principal

problema da célula de memória, a injeção de cargas,

não é bem modelado pelo simulador, tornando difícil

prever a precisão da célula através de simulações.

Se considerarmos a célula de memória

previamente caracterizada, é possível utilizá-la como

um bloco de uma biblioteca, tal como um flip-flop ou

uma porta lógica, em um circuito standard cell. Tornase possível, desta forma, o projeto de circuitos mais

complexos (p. ex. um ADC) utilizando quase que

somente um simulador funcional (HDLA). Com isto,

há um aumento da probabilidade de sucesso de um

projeto na primeira tentativa, bem como uma redução

da complexidade e do tempo de projeto.

Para que seja viável criar uma biblioteca de

células de memória de corrente, seria necessário:

1.1) Investigar os problemas que acarretam erros na

memorização da corrente, definir alternativas para

minimizá-los e criar uma metodologia de projeto

(um conjunto de equações e recomendações), tal

que, dada uma série de especificações iniciais para

uma determinada célula, seja possível um projeto

rápido.

1.2) Uma vez projetada a célula, deve-se projetar e

montar um sistema de medição que permita a

completa caracterização da célula, para verificar se o

projeto atingiu as especificações iniciais.

O item 1.1 foi abordado em um outro trabalho,

também submetido ao XII Congresso da SBmicro.

Neste trabalho pretende-se abortar o item 1.2. Nos

itens posteriores, serão vistas as dificuldades de se

caracterizar uma célula de memória, bem como o

projeto e os resultados experimentais dos circuitos

adicionais (integrados) necessários na realização das

medições para a caracterização. Também será visto a

montagem do sistema de medição e os procedimentos

para a caracterização de células de memória de

corrente operando a frequência de até 3MHz e precisão

da ordem de 450ppm (~ 11 bits).

3-Settling time da célula de memória e soluções

para a medição das correntes de entrada e de

saída

A célula SI faz a memorização da corrente de

entrada através da carga do capacitor do gate do

transistor conectado como diodo. Se a carga do

capacitor não se completar durante a fase de

amostragem (chave S1 e S2 fechadas na Fig. 1), o

capacitor gate-source do transistor M1 armazenará um

valor de tensão errado e, consequentemente, gerará um

erro de corrente. Isto significa que, dado um valor de

erro máximo para a tensão de memorização do

capacitor, a duração da fase de amostragem (φ1 da Fig.

1) deve ser tal que permita não ultrapassar este erro. A

equação que relaciona a duração da fase de

amostragem (Tφ1), o erro de memorização (εT) e a

constante de tempo para a carga do capacitor (TS) é

mostrada abaixo [6].

Tφ1=[(ln(2/εT) + ln(1+ln(2/εT))].TS

(1)

Considerando-se a célula operando no regime

sobre-amortecido (relação de amortecimento maior

que 1), os polos da célula de memória serão reais e

podem ser aproximados pelas equações 2 e 3 [5,6].

gm

1

p 1 = – ---- ≅ -------------------τ d Cg + Cd

(2)

1 gx ⋅ ( Cg + Cd )p 2 = – ---- ≅ ------------------------------------Cg ⋅ Cd

τp

(3)

Referindo-se a Fig. 1, gx representa a

condutância da chave de amostragem fechada (S1),

sendo que gx é muito maior que a impedância de saída

da célula; gm é a transcondutância do transistor M1;

Cd é a soma de todas as capacitâncias parasitas no nó

de entrada da corrente amostrada (inclusive

capacitâncias das chaves) e Cg a soma das

capacitâncias no gate de M1. Considerando a soma

Cg+Cd igual CI (capacitância de entrada da célula), a

constante de tempo da célula pode ser aproximada pela

equação 4. A constante de tempo é que vai definir a

duração mínima do sinal φ1 para uma dada precisão da

célula SI, de acordo com a equação 1.

CI

Ts1 ≅ τ d ≅ -----gm

(4)

No projeto da célula SI, na fase de simulação

elétrica, são consideradas apenas as capacitâncias

intrínsecas aos transistores da célula e algumas

parasitas devido a layout, obtendo-se, desta forma, a

frequência de operação da célula especificada. No

entanto, na caracterização das células, são introduzidas

as capacitâncias dos instrumentos e pontas de prova, os

quais são utilizados para realizar as medições e definir

a precisão (AC e DC) da célula SI. Assim, na fase de

caracterização, é preciso tomar alguns cuidados para

aplicar ou medir a corrente de entrada ou de saída da

célula, evitando aumentar a constante de tempo. A Fig.

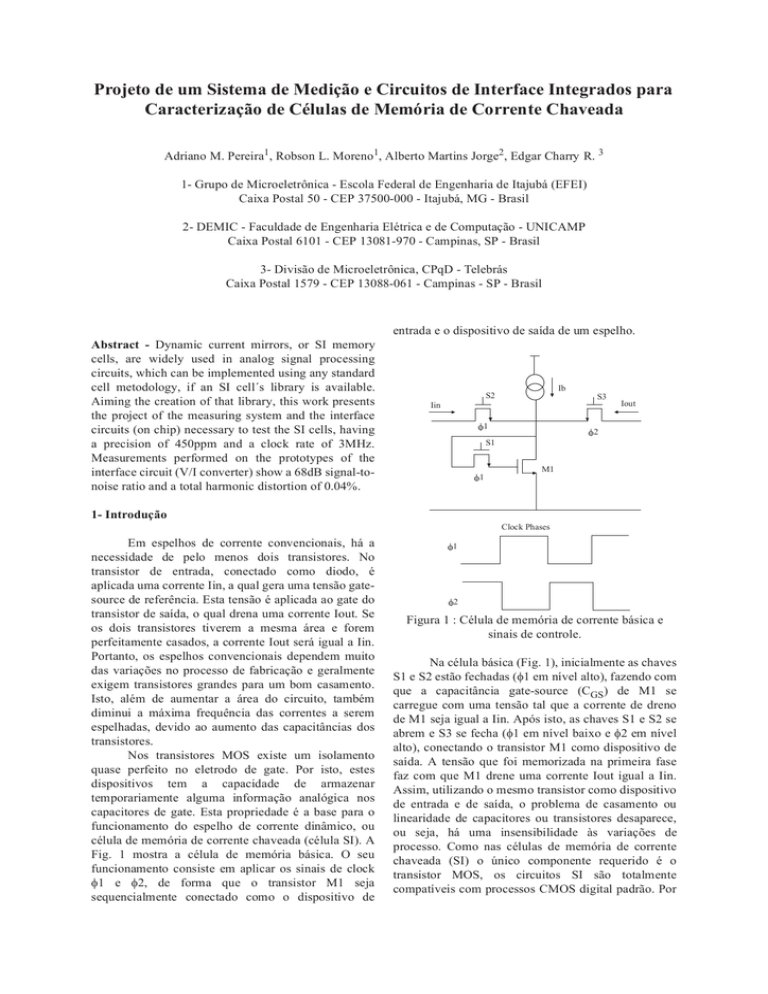

2 mostra o circuito equivalente de uma célula de

memória SI (em termos de capacitância e impedância)

na fase de amostragem, considerando que vai se

aplicar a corrente diretamente na célula.

Na Fig. 2, CF representa a capacitância de saída

da fonte Iin e CP as capacitâncias de conexões,

encapsulamento e do pad de entrada. Desta forma, a

constante de tempo passaria a ser:

C I + CP + C F

Ts 2 ≅ τ d ≅ ------------------------------gm

(5)

Vdd

Iin

CHIP

Pad

CF

CP

CI

1/gm

Figura 2: Circuito equivalente da célula de memória na

fase de amostragem

Esta nova constante de tempo inviabilizaria a

operação da célula a altas frequências. Por exemplo,

para uma precisão da célula de 250ppm, a duração da

fase φ1 seria de 11.5 vezes a constante de tempo Ts2

(equação 1). Adotando-se gm=100µA/V, CP=1pF,

CF=8pF e CI=2pF, a duração mínima de φ1 seria de

1.265µs. Para φ2 igual a φ1, a frequência máxima de

operação da célula seria de 395 KHz.

Para medir a corrente de entrada, poderia-se

utilizar um amperímetro, mas este aumentaria o nível

de ruído da célula . Uma solução melhor é a utilização

de um resistor no caminho da corrente de entrada.

Convertida para tensão, pode-se medi-la utilizando-se

voltímetros ou osciloscópios, altamente precisos,

calibrados e com a capacitade de fazer a média do

sinal de entrada, o que reduziria as variações do sinal

devido ao ruído. Apesar disso, ambas montagens

provocariam a redução da frequência máxima de

operação da célula, devido ao aumento da constante de

tempo.

A solução para não aumentar a constante de

tempo, quando se aplica ou se mede a corrente de

entrada, está na utilização de um conversor tensãocorrente (V/I) integrado, como mostrado na Fig. 3.

VM1

R1

VB

Vin

V/I

S4 φ2 Iin

IB

S3

S2

φ1

φ1

S1

Iout

φ2

MN

CHIP

VM2

R2

Figura 3: Solução para aplicar e medir a corrente de

entrada

Na Fig. 3, VM1 e 2 são voltímetros, R1 e R2

são resistores de precisão e MN, juntamente com as

chaves e IB, formam uma célula de memória de

corrente chaveada (SI). A célula SI opera com

correntes de entrada positivas e negativas, o que leva a

necessidade de projetar o conversor V/I com um

estágio de saída push-pull. Aplicada uma determinada

tensão DC na entrada do conversor V/I, para medir a

corrente de entrada basta subtrair a corrente de R1

(leitura de VM1 dividida por R1) da corrente de R2

(leitura de VM2 dividida por R2). Se os voltímetros

possuirem controle do tempo de integração, pode-se

reduzir a influência do ruído na medida. Deve-se notar

que, para utilização dos voltímetros ao invés de

osciloscópios, a corrente deve ser constante no estágio

push-pull, daí a necessidade de utilizar a chave S4 e o

bloco VB, que formam um caminho para a corrente

quando a chave de entrada da célula está aberta.

Para se medir a corrente de saída, pode-se

também utilizar um resitor, ligado entre a saída da

célula SI e uma fonte DC. A Fig. 4 ilustra o

procedimento.

Ao contrário da corrente de entrada, não há

como se manter a corrente de saída sempre fluindo, daí

a necessidade do osciloscópio para monitorar a

variação de tensão naquele ponto. Os efeitos das

capacitâncias parasitas discutidos até aqui, acarretam o

aumento da duração da fase de amostragem (φ1). De

forma análoga, elas afetam a duração da fase φ2 (fase

de retenção) na medição da corrente de saída. Se a

célula utiliza circuitos regulated cascode [7], a

impedância de saída da célula é muito maior que Rout

(Fig. 4). Desta forma, pode-se mostrar que a constante

de tempo que limita a fase φ2 é dada por:

Ts φ2 ≅ C P ⋅ Rout

(6)

IB

Iin

S3

S2

φ1

φ1

S1

φ2

MN

Iout

Rout

VoutDC

Osciloscópio

CHIP

Figura 4: Medição da corrente de saída

Principalmente para valores mais altos de Rout

(necessário para correntes menores), a constante de

tempo aumenta, fazendo com que a duração da fase φ2

aumente também (equação 1). Desta forma, é

necessário o projeto de um circuito de interface (como

um conveyor de corrente), para tornar possível medir a

corrente de saída. No entanto, este circuito não é tão

simples como o conversor V/I para a corrente de

entrada. Isto porque o circuito de interface para a

corrente de saída, deve operar na frequência de

chaveamento da célula (MHz) e não na frequência do

sinal de entrada (DC ou KHz). Como pretende-se

caracterizar células de memória operando a frequência

de até 3MHz e precisão de 11 bits (item 2), seria

extremamente complexo desenvolver um conveyor de

corrente para operar nestas condições, principalmente

em um processo CMOS digital padrão.

Nas aplicações onde a célula SI é utilizada, a

corrente é passada de uma célula para outra, ou seja, a

fase φ2 de uma é a fase φ1 da outra. Desta forma, a

duração das fases deve ser a mesma, sendo que esta

duração é definida pela fase φ1 (tempo de carga do

capacitor

de

memorização).

Portanto,

na

caracterização da célula, o importante é definir a

duração de φ1. Pode-se, então, dispensar a interface

para medição da corrente de saída e fazer a duração de

φ2 maior que φ1, sem comprometer a medição da

frequência máxima de operação da célula.

Infelizmente, esta simplificação na medição da

corrente de saída minimiza o erro devido a impedância

de saída da célula SI. Isto porque a impedância diminui

com o aumento da frequência do sinal de saída e a

frequência de φ1 é maior que a de φ2. Desta forma,

para não gerar um erro na medição da corrente de

saída, deve-se corrigi-la, somando o erro devido a

impedância da célula na frequência de φ1. Para isto,

basta levantar a curva do erro devido a impedância da

célula em função da frequência (item 4).

4- Sistema de medição

Para utilizar a célula como um bloco de uma

biblioteca, como visto no item 2, é preciso caracterizála através da medição de pelo menos as seguintes

grandezas: consumo, precisão DC, distorção

harmônica (THD), relação sinal/ruído, frequência

máxima de chaveamento (para um determinado erro),

impedância de saída e compliância da tensão de saída.

Para realizar estas medidas, é necessário realizar um

sistema de medição e seguir uma sequência de

procedimentos que serão descritos neste item. O

sistema de medição deverá ser capaz de caracterizar

células operando a frequência de até 3MHz e precisão

de 450ppm.

Para medição das correntes de entrada e de

saída da célula, deve-se utilizar as recomendações do

item 3. Um sistema que permite a medicão de todas as

grandezas necessárias para a caracterização da célula

de memória de corrente (mencionadas anteriormente),

é mostrado na Fig. 5. Na figura, VM1 e 2 são

voltímetros, Oscilos. 1 e 2 são osciloscópios, Gerador

1 e 2 são geradores de sinais senoidais e DC variáveis,

V/I é um conversor tensão-corrente integrado com

estágio de saída push-pull, R1 a R3 são resistores de

precisão de diversos valores e MN, juntamente com as

chaves e IB, representa a célula de memória de

corrente chaveada (SI) a ser caracterizada. A linha

pontilhada representa a separação dos elementos que

estão fora e dentro do chip a ser caracterizado.

VM1

R1

VB

Gerador

AC-DC

1

S4 φ2 Iin

V/I

IB

φ1

φ1

S1

CHIP

VM2

S3

S2

Iout

φ2

MN

R3

Gerador

AC-DC

2

Oscilos. 1

Buf

R2

Oscilos. 2

Figura 5: Sistema de medição para caracterização de

células de memória de corrente chaveada

Para medição de cada uma das grandezas para

caracterização da célula SI, deve-se seguir os

procedimentos abaixo.

- Erro devido à impedância de saída:

Mesmo com a utilização de circuitos regulated

cascode [7], a impedância de saída da célula não é

infinita e, portanto, as variações na tensão de saída da

célula, provocam um erro de corrente. Como a

impedância varia com a frequência, o erro deve ser

medido em função dela. A curva resultante desta

medida é também importante para correção da corrente

de saída (item 3). Este erro deve ser medido na fase de

retenção (φ2), mas não se pode travar a célula nesta

fase (para não descarregar o capacitor de

memorização). A solução é aumentar a duração da fase

φ2 e utilizar o Gerador 2 (Fig. 5) para variar a tensão

de saída em uma determinada frequência e medir a

corrente (Oscilos 1). Inicialmente, a frequência deve

ser menor que 1/Cp.Rout (equação 6). Aumentando-se

a frequência, a diferença observada na corrente de

saída é o erro devido a impedância da célula nesta nova

frequência. Pode-se, também, traçar a curva da

impedância da célula em função da frequência (a partir

de valores maiores que 1/Cp.Rout Hz). Se a amplitude

da tensão de saída for 1V (Gerador 2), a variação

observada na corrente de saída é a própria condutância

de saída da célula.

se ter a amplitude de corrente máxima na saída do

conversor V/I (voltímetros VM1 e 2). O Gerador 2

deve ser ajustado em 2.5V e o valor de R3 deve ser tal,

que a queda de tensão não seja maior que compliância

da tensão de saída. O osciloscópio 1 (Oscilos. 1 da Fig.

5) deve ser substituido por um analisador de sinais,

conectado ao mesmo ponto, para calcular as

harmônicas do sinal de saída da célula SI. Estas

harmônicas devem ser comparadas com o espectro da

corrente de saída ideal (sem erros), para calcular a

distorção introduzida pela célula SI. Isto ocorre porque

mesmo que a distorção introduzida pela célula fosse

zero, o analisador de sinais mostraria várias

harmônicas, pois a corrente de saída não é constante

(retorna para zero durante a fase φ1 alta).

- Compliância da tensão de saída:

A compliância da tensão, ou faixa dinâmica,

deve ser medida para valores DC. Portanto, pode-se

utilizar o mesmo procedimento descrito para medição

do erro devido a impedância da célula. Porém, no

Gerador 2, deve-se aplicar um valor DC e variar sua

amplitude de 0V a 5V. Dentro de uma faixa central, as

variações na corrente de saída devem ser praticamente

zero. Fora desta faixa, ocorrerá um aumento do erro. A

compliância será a faixa de valores para a tensão de

saída, na qual a variação da corrente é desprezível.

- Relação sinal/ruído:

A relação sinal/ruído (SNR), juntamente com a

distorção harmônica, definem a precisão AC da célula

SI. Assim como no caso da distorção harmônica, a

relação sinal/ruído do conversor V/I deve ser maior

que a relação a qual se pretende medir na célula SI, ou

seja, maior que 68dB. O procedimento para a medição

pode ser o mesmo utilizado para a distorção

harmônica, sendo que, neste caso a SNR pode ser

calculada diretamente do analisador de sinais.

- Precisão DC:

A precisão DC da célula, que é uma das

grandezas mais importantes a serem medidas, consiste

em se medir as correntes de entrada e saída da célula,

para calcular o erro entre elas. O cálculo do erro deve

ser feito para uma determinada frequência de

chaveamento e para toda a faixa da corrente de entrada

da célula. Conforme explicado do item 3, não é

possível aplicar uma fonte de corrente diretamente a

célula SI. Por isso a necessidade do conversor V/I

(dentro do chip) para fazer a interface de entrada.

Aplicando-se uma tensão DC no Gerador 1, pode-se

medir a corrente pelos voltímetros VM1 e 2. A

medição da corrente de saída deve ser corrigida,

conforme mencionado no item 3, somando-se o erro

devido a impedância de saída. O valor da tensão de

saída (Gerador 2), deve ser setado para cada valor da

corrente de entrada, de forma que as variações no

ponto de ligação do Oscilos. 1, fiquem em torno 2.5V.

A precisão (%) será: [(Iout-Iin)/Iin].100

- Distorção harmônica:

A distorção introduzida pela célula SI é um

fator importante em muitas aplicações [9,10,12].

Como pretende-se caracterizar células com precisão da

ordem de 450ppm, a distorção harmônica total (THD)

introduzida pelo conversor V/I, deve ser menor ou

igual a 0.04%, para não comprometer a medida da

THD da célula SI. Para medir a distorção da célula,

deve-se ajustar um nível DC no Gerador 1, de forma a

Outra medição interessante que pode ser

realizada é o erro devido a injeção de carga. Isto pode

ser válido para determinar a eficiência da compensação

utilizada. A medição pode ser feita utilizando-se um

seguidor de tensão de ganho AC unitário (Buf da Fig.

5). O offset do seguidor não causa problemas, pois o

importante é a variação AC observada em Oscilos. 2

(Fig. 5), portanto, o projeto deste circuito não é

complexo.

5- Projeto da interface para a corrente de entrada

Conforme visto nos itens anteriores, a interface

para a corrente de entrada é o circuito principal

necessário para a completa caracterização de células de

memória de corrente. Esta interface, basicamente,

consiste de um conversor tensão-corrente (V/I). Como

o sistema de medição será utilizado para caracterização

de células de corrente chaveada com precisão de até

450ppm (item 2), o conversor V/I terá as seguintes

especificações:

- Distorção harmônica total menor ou igual a 0.04%.

- Relação sinal/ruído (SNR) maior que 68dB.

- Operar com correntes de saída positias e negativas,

de até 150µA.

Para implementar este conversor V/I, optou-se

por utilizar um conveyor de corrente [13], pois ele

permite operar com correntes positivas e negativas

(estágio de saída push-pull). A Fig. 6 mostra um

conveyor de corrente básico.

O conveyor é um circuito, em termos ideais, no

qual a corrente aplicada no nó X é "seguida" pela

corrente do nó Z, da mesma forma que a tensão do nó

X segue a tensão aplicada ao nó Y. Esta última

propriedade pode ser melhorada no circuito da Fig. 6,

introduzindo-se um amplificador operacional no

circuito [13]. Desta forma, io é igual à -ii , sendo io

igual a id8 + id6 . A divisão da corrente de entrada

entre os transistores M2 e M4, considerando os

transistores casados, operando na região de saturação e

com transcondutâncias (quiecentes) iguais, pode ser

dada por [13] :

id4 = (4.IB + ii )2 / (16.IB) , para ii < 4.IB

(7)

id2 = (4.IB - ii )2 / (16.IB) , para ii < 4.IB

(8)

Neste circuito, se o ganho do operacional for

elevado, a corrente ii (que entra no nó X) é dada por

VIN/RREF , considerando Vdd/2 como o terra

analógico. De acordo com algumas simulações

realizadas, para que a corrente de saída apresente uma

distorção menor de 0,02%, o ganho de tensão em

malha aberta do operacional deve ser maior que 55dB

(na frequência do sinal Vin) e a impedância vista pelo

ponto X menor que 1KΩ,

No circuito completo do conversor V/I, os

transistores M5, M6, M7 e M8 (Fig. 7), foram

substituídos por circuitos regulated cascode [7]. Com

isto, a impedância de saída do conversor V/I ficou em

torno de 500MΩ. Os transistores M11 e M12 também

foram substituidos por circuitos regulated cascode,

para aumentar o ganho de tensão em malha aberta (Av)

do operacional.

Onde id2 e id4 são as correntes de dreno de M2

e M4, respectivamente. Quando a corrente de entrada é

maior que 4.IB , o circuito continua funcionando

corretamente, mas um dos espelhos passa a drenar toda

a corrente, enquanto o outro está cortado.

Vd

M9

VB2

M5

M6

IB

Vdd

Vdd

M2

M1

VB1

M15

Y

ISS

ii

M5

M13

M14

RC

VIN

CC

M7

Vdd/2

M2

M11

Y

X

M8

M10

M12

Z

ii

M3

M4

M6

RREF

M1

Z

io

M3

IB

X

io

M4

Figura 7: Circuito simplificado do conversor V/I

utilizado como interface para caracterização da célula

de memória SI.

Figura 6: Conveyor de corrente

O circuito regulated cascode possui uma

impedância de saída cerca de 70 vezes maior que os

circuitos cascode convencionais [7], com a vantagem

de poder operar com uma tensão de saída 35% menor

que a tensão mínima dos circuitos cascode

convencionais (no caso de circuito NMOS) [7]. A Fig.

8 mostra o circuito regulated cascode utilizado.

Dependendo da forma que é configurado, o

conveyor de corrente pode ser utilizado em diversas

outras aplicações além do conversor V/I, tais como

amplificador de corrente, buffer de corrente,

integrador, somador, etc. [13]. A Fig. 7 mostra o

conveyor de corrente configurado como um conversor

V/I. No circuito da Fig. 7, o amplificador operacional

para melhorar a propriedade de seguidor de tensão

(mencionado anteriormente), também é mostrado.

Como se deseja que o conversor V/I apresente baixa

distorção, torna-se necessário a utilização deste

amplificador operacional.

Figura 8: Circuito regulated cascode

M7

M8

IB

As dimensões dos transistores do amplificador

operacional foram definidas com base em [14] e [15],

que são estudos para se obter operacionais de baixo

ruído. Isto foi feito para não comprometer a relação

Sinal/Ruído do conversor V/I.

As correntes de polarização do operacional e do

conveyor (Iss e IB da Fig. 7), foram setadas para 80µA

e 50µA, respectivamente. Com isto, o operacional

apresentou as seguintes características nas simulações

elétricas realizadas: Av=92dB, Margem de Fase=590,

F-3dB = 1KHz e FT=16MHz. A relação de áreas dos

transistores M1, M2 e M3, M4 foi de 1 para 2. Com

isto, a impedância vista pelo ponto X foi de 770Ω e a

distorção harmônica total (THD) do conversor V/I foi

de 0,01% , para io (Fig. 7) variando de -150µA a

150µA (RREF =510Ω).

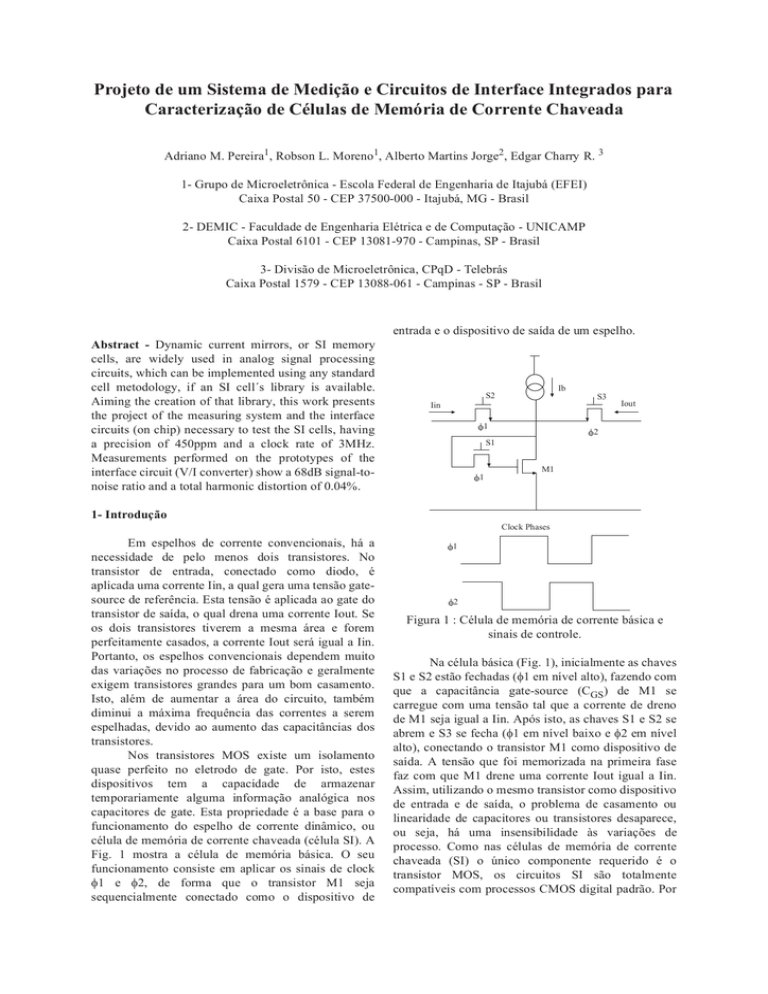

A Fig. 9 mostra o layout do circuito, o qual foi

enviado para fabricação na foundry AMS, utilizando

processo CMOS 1.2µm.

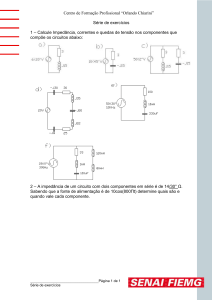

A amplitude da tensão de entrada foi ajustada

para uma corrente de saída de 300µA pico a pico.

Pode-se ver que as componentes harmônicas e o nível

do ruído estão mais de 70dB abaixo da fundamental, e

portanto, satisfazendo

a relação

sinal/ruído

especificada (> 68dB). A distorção harmônica total

(THD) média das amostras ficou em 0.04%, também

satisfazendo a THD especificada. Esta distorção

mantém-se aproximadamente constante até 200KHz.

Comparado com as simulações, a THD medida foi

bem superior, mas isto se deve ao equipamento

utilizado para gerar a tensão de entrada do conversor

V/I. Até o término deste trabalho, não tinha sido

possível utilizar um gerador que apresentasse mais que

70dB entre a fundamental e as componentes

harmônicas de distorção. O problema do aumento da

distorção para frequência superior a 200KHz, também

se deve, em parte, ao gerador.

7- Conclusão

Figura 9: Layout do conversor V/I utilizado como

interface para caracterização da célula de memória SI.

6-Resultados experimentais do conversor V/I

Foram analisadas vinte amostras do conversor

tensão corrente (V/I). A saída do conversor foi ligada a

um resistor (Rout) de mesmo valor de RREF (Fig. 7) e

Rout foi conectado a uma fonte DC de 2.5V. O

espectro medido do sinal de saída (Rout.io) é mostrado

na Fig. 10.

Foi visto que devido a enorme gama de

aplicações onde as células SI são empregadas, tais

como redes neurais [9], filtros[10], conversores D/A

[2] e A/D [6,9,11], torna-se interessante a

implementação de uma biblioteca de células de

memória de corrente chaveada. Considerando-se a

célula SI como um bloco de uma biblioteca, tal como

um flip-flop ou uma porta lógica, as aplicações onde

ela é utilizada podem ser implementadas empregandose uma metodologia “standard cell”. Além disso,

torna-se possível o projeto de circuitos mais

complexos utilizando quase que somente um

simulador funcional (HDLA). Para viabilizar a

implementação desta biblioteca, foi visto o projeto de

um sistema de medição e dos circuitos de interface

necessários para caracterização de células SI com

precisão de 450ppm e frequência de operação de

3MHz. Para realização deste sistema, concluiu-se que

era fundamental o projeto de uma interface de entrada

para caracterização das células. Medições realizadas

nos protótipos do circuito de interface (conversor V/I),

indicaram uma relação sinal/ruído maior que 68dB e

uma THD de 0.04%.

8- Bibliografia

[1] D. G. Nairn, C. A. T. Salama, “Current-Mode

Algorithmic Analog-to-Digital Converters”, IEEE

Journal of Solid-State Circuits, vol. 35, n. 4, August

1990.

Figura 10: Espectro do sinal de saída (io=300µApp)

para o sinal de entrada em 50KHz

[2] D. W. J. Groeneveld, H. J. Schouwenaars, H. A. H.

Termeer, C. A. A. Bastiaansen, “A Self-Calibration

Technique for Monolithic High-Resolution D/A

Converters”, IEEE Journal of Solid-State Circuits,

vol. 27, n. 5, December 1989.

[3] A. M. Cujec, D. G. Nairn, C. A. T. Salama, “An

Optimized Bit Cell Design for a Pipelined CurentMode Algorithmic A/D Converter”, Analog

Integrated Circuits and Signal Procesing, K. A. P.,

Vol. 3, n. 2, March 1993.

[4] G.Wegmann, E. A. Vittoz. "Charge Injection in

Analog MOS Switches". IEEE Journal of SolidState Circuits, vol. sc-22, n. 6, December 1987.

[5] Design and Analysis Techniques for Dynamic

Current Mirrors; These No. 890 (1990), George

Wegmann; EPFL, Suiça

[6] Convertisseurs Analogiques / Numeriques

Cycliques a Memoires de Courant CMOS; These

No. 1001 (1992); Philippe Deval; EPFL, Suiça

[7] E. Säckinger, W. Guggenbühl - "A High-Swing,

High-Impedance MOS Cascode Circuit" IEEE J.

Solid-State Circuits, Vol. 25, No./ 1, Feb. 1990.

[8] Klass Bult. "The CMOS Gain-Boosting

Technique" in Proc. Workshop on Advances in

Analogue Circuit Design, pp. 81-121, April 1992.

[9] C. Toumazou, J. B. Hughes, N. C. Battersby.

"Switched-Currents an Analogue Technique for

Digital Technology". April 93: P. Peregrinus Ltd.

[10] J. B. Hughes, K.W. Moulding, “Switched-Current

Signal Processing for Video Frequencies and

Beyond”, IEEE J. Solid-State Circuits, vol. 28, n. 3,

March 1993.

[11] D. Macq, P. G. A. Jespers, “A 10-Bit Pipelined

Switched-Current A/D Converter” , IEEE J. SolidState Circuits, vol. 29, n. 8, August 1994.

[12] P. J. Crawley, G. W. Roberts, “Predicting

Harmonic Distortion in Switched-Current Memory

Circuits”, IEE Trans. on Circuits and System-II:

Analog and Digital Signal Processing, vol. 41, n. 2,

February 1994.

[13] C. Toumazou, F. J. Lidgey, D. G. Haigh.

"Analogue IC Design: The Current-Mode

Approach". April 1990: Peter Peregrinus Ltd.

[14] Phillip E. Allen - "CMOS Analog Circuit Design"

Holt, Rinehart and Winston, Inc. - Series in

Electrical and Computer Engineering, 1987.

[15] R.D. Jolly, R. H. McCharles -"A Low Noise

Amplifier for Switched Capacitor Filters"- IEEE

Journal of Solid-State Circuits, Vol. SC-17, No. 6,

Dec. 1982.

![1. [5] Um circuito integrado precisa de uma tensão de alimentação](http://s1.studylibpt.com/store/data/000892095_1-927da8bea174b016f37ec8deb83e76f0-300x300.png)