Introdução ao Projeto de Circuitos

Integrados Analógicos

Fernando Antônio Pinto Barúqui

Departamento de eletrônica

Escola Politécnica

Universidade Federal do Rio de Janeiro

Material não disponível para publicação

Índice

1.

Transistor MOSFET ........................................................................................................................ 5

1.1

MOSFET de Canal N .............................................................................................................. 5

1.1.1

Características DC ........................................................................................................... 5

1.1.2

Efeito de Corpo ............................................................................................................... 8

1.1.3

Modulação de Canal ........................................................................................................ 8

1.1.4

MOSFET de Canal P ..................................................................................................... 12

1.1.5

Características DC ......................................................................................................... 12

1.1.6

Efeito de Corpo ............................................................................................................. 12

1.1.7

Modulação de Canal ...................................................................................................... 13

1.2

Tecnologia CMOS................................................................................................................. 13

1.3

Capacitâncias dos transistores MOSFET .............................................................................. 14

1.4

Análise de Pequenos Sinais (AC).......................................................................................... 16

1.4.1

1.5

Layout dos Transistores......................................................................................................... 20

1.5.1

2.

Layout Para transistores PMOS com Poço N................................................................ 21

Resistores ...................................................................................................................................... 22

2.1

3.

Modelo Para Altas Freqüências..................................................................................... 18

Formas de Implementação dos Resistores............................................................................. 22

2.1.1

Resistor de Difusão N.................................................................................................... 23

2.1.2

Resistor de Difusão p+ Sobre Poço N Polarizado ......................................................... 23

2.1.3

Resistor de Poço N ........................................................................................................ 23

2.1.4

Resistor de Poço Estrangulado (“Pinched Well”) ......................................................... 23

2.1.5

Resistor de Polysilício Sobre Substrato......................................................................... 24

2.1.6

Resistor de Polysilício Sobre Poço Polarizado.............................................................. 24

2.1.7

Resistor de POLY2 Sobre Difusão p+ e Poço N ........................................................... 24

2.2

Erros na Construção dos Resistores ...................................................................................... 25

2.3

Layout Para Resistores .......................................................................................................... 26

Capacitores .................................................................................................................................... 28

3.1

Tipos de Capacitores ............................................................................................................. 28

3.1.1

Capacitor de POLY Sobre Difusão ............................................................................... 28

3.1.2

Capacitor de POLY2 sobre POLY1 sobre Poço Polarizado.......................................... 28

3.2

Modelo dos Capacitores ........................................................................................................ 29

3.2.1

Precisão dos Capacitores ............................................................................................... 29

3.2.2

Erro nas Razões de Capacitores .................................................................................... 31

2

Material não disponível para publicação

4.

3.3

Layout dos Capacitores POLY1 Sobre POLY2 .................................................................... 33

3.4

Distribuição Física dos Capacitores ...................................................................................... 34

3.5

Montagem do Capacitor ........................................................................................................ 35

Chaves Analógicas ........................................................................................................................ 37

4.1

Chave Simples Tipo N .......................................................................................................... 37

4.2

Chave Simples Tipo P ........................................................................................................... 38

4.3

Chave Complementar ............................................................................................................ 39

4.4

Dimensionamento da Resistência da Chave .......................................................................... 41

4.5

Injeção de Cargas .................................................................................................................. 42

4.5.1

4.6

5.

6.

Caracterização do Problema .......................................................................................... 42

Compensação Para Injeção de Cargas ................................................................................... 44

4.6.1

Uso de Transistores Dummy ......................................................................................... 44

4.6.2

Uso de Chaves Gêmeas ................................................................................................. 45

4.6.3

Uso de Chave Complementar ........................................................................................ 46

4.6.4

Projeto da Chave Complementar................................................................................... 46

4.6.5

Uso de Redes de Compensação ..................................................................................... 47

4.6.6

Uso de Circuitos Totalmente Diferenciais..................................................................... 48

Espelhos de Corrente..................................................................................................................... 51

5.1

Espelho Simples .................................................................................................................... 51

5.2

Espelho de Corrente em Cascode .......................................................................................... 51

5.3

Espelho de Corrente em Cascode Regulado.......................................................................... 53

Amplificadores Operacionais ........................................................................................................ 56

6.1

OTA com Saída em Cascode Dobrado.................................................................................. 57

6.1.1

Dimensionamento dos Transistores em Função da Polarização.................................... 57

6.1.2

Análise AC para Baixas Freqüências ............................................................................ 59

6.1.3

Excursão de Sinal na Saída............................................................................................ 59

6.1.4

Análise AC para Altas Freqüências............................................................................... 60

6.2

OTA com Saída em Cascode Regulado ................................................................................ 61

6.3

OTA Diferencial com Saídas em Cascode Dobrado ............................................................. 63

6.3.1

Análise AC para Altas Freqüências............................................................................... 64

6.4

OTA Diferencial com Saídas em Cascode Regulado ............................................................ 65

6.5

Controle de Modo Comum.................................................................................................... 66

6.6

Critério de Projeto dos OTAS ............................................................................................... 69

6.7

Otimização Com Auxílio de Simuladores ............................................................................. 70

3

Material não disponível para publicação

Introdução

A eletrônica teve início ativamente no começo do século XX com a invenção da válvula

termiônica. A partir deste momento, foi possível desenvolver equipamentos como amplificadores,

rádios, televisores e até mesmo alguns computadores primitivos. Mas os dispositivos valvulados eram

grandes, consumiam muita energia e não se prestavam para aplicações em miniatura. A invenção dos

transistores deu um grande impulso à industria de consumo de eletrônicos, pois permitiu o

desenvolvimento de equipamentos portáteis e de baixo consumo. Com a crescente sofisticação do

mercado, sistemas transistorizados mais complexos foram desenvolvidos, até que novamente o

problema do tamanho e consumo se tornou uma barreira.

Os circuitos integrados surgiram como uma solução aparentemente definitiva para o problema da

miniaturização e do consumo. Uma ampla gama de componentes integrados passou a ser

disponibilizada aos projetistas e a eletrônica deu um salto quantitativo e qualitativo. Os equipamentos

aumentaram de complexidade e tornaram-se mais confiáveis. Neste contexto, a tecnologia de

computadores e microcomputadores teve um desenvolvimento assombroso, chegando-se a integrar

milhões de transistores em um único chip.

Os transistores foram relegados à aplicações em freqüências muito altas e elevadas potências, ou a

equipamentos com funções muito simples. Os projetistas de circuitos analógicos passaram a usar os

amplificadores operacionais (opamps) integrados como elemento básico de projeto. Muitas técnicas e

teorias foram desenvolvidas ao redor dos opamps.

Na atualidade, existe uma tendência e um objetivo claro de desenvolver equipamentos em um único

chip, que reúne tanto os circuitos digitais quanto os analógicos. Esta tendência tem gerado uma grande

necessidade de projetistas de circuitos integrados.

Os projetistas, de certa forma, retrocedem aos tempos áureos dos transistores, pois precisam

construir cada circuito e subcircuito a ser usado. Ainda de forma mais radical, cada componente

integrado, sejam eles transistores, resistores, capacitores e até mesmo indutores, precisam ser

dimensionados individualmente. Estes procedimentos resgatam muito do que foi desenvolvido na

época dos circuitos transistorizados discretos. Evidentemente, uma abordagem diferente e novas

técnicas de projeto são aplicadas à integração de circuitos.

O presente texto é uma breve introdução às técnicas de projeto de circuitos integrados analógicos,

com considerações teóricas e práticas sobre modelos e técnicas de layout para transistores, capacitores,

resistores e opamps.

4

Material não disponível para publicação

1. Transistor MOSFET

O transistor MOSFET (metal-oxide-semiconductor field-efect transistor) foi fabricado pela

primeira vez em 1960, um ano após o início da era do circuito integrado. O MOSFET encontra sua

maior aplicação nos circuitos integrados de larga escala (VLSI), onde se emprega a tecnologia CMOS

(complementar metal-oxide-semiconductor) que utiliza transistores de canal N e P. Os MOSFETS

também estão se tornando muito populares em aplicações discretas nas áreas de eletrônica de potência,

áudio, microondas e radio freqüência em geral. Por ser um dispositivo extremamente utilizado, muito

se tem feito para sua modelagem.

O objetivo deste capítulo é descrever o funcionamento do MOSFET e estudar suas características,

com base em um modelo simplificado, normalmente usado como ponto de partida para os projetos de

circuitos integrados.

1.1 MOSFET de Canal N

G

S

D

B

Fig. 1.1: Transistor MOSFET de canal N.

1.1.1 Características DC

Pode-se classificar o transistor MOSFET, segundo sua polarização, basicamente em quatro regiões

de operação:

• Corte

• Inversão fraca

• Triodo (ôhmica)

• Saturação

Na região de corte, a tensão entre Gate e Source ( Vgs ) é negativa ( Vgs < 0 ). Sob esta condição, as

junções Source-Substrato e Dreno-Substrato estão polarizadas reversamente e cercadas por região de

depleção. Não há portanto corrente elétrica significativa entre Dreno e Source ( I d ), somente a

corrente de saturação do diodo formado pela junção Dreno-Substrato. Considera-se neste caso que

Id = 0 .

5

Material não disponível para publicação

Fig. 1.2: Transistor MOSFET na região de corte.

Ao passo em que a tensão Vgs vai se tornando positiva, elétrons são atraídos para a região próxima

do Gate, devido ao campo elétrico induzido no Substrato pelas cargas positivas acumuladas na placa

de Gate. Estes elétrons recombinam-se com buracos, formando íons negativos, estendendo a região de

depleção, conforme a Fig. 1.3. A corrente I d é muito pequena e é basicamente a corrente de saturação

do diodo formado pela junção Dreno-Substrato. Entretanto, como a região de saturação diminui com o

aumento de Vgs , I d passa a depender também de Vgs . Esta região de trabalho é chamada de “inversão

fraca”. Na grande maioria das aplicações, assume-se que I d = 0 nesta região. A inversão fraca ocorre

para Vgs entre zero volts e a tensão de threshold ( VT ).

Fig. 1.3: MOSFET polarizado com Vgs ligeiramente positivo.

Com o aumento progressivo de Vgs , elétrons gerados termicamente na região de depleção próxima

ao Gate ganham energia suficiente para alcançar a banda de condução, e são aprisionados pelo campo

elétrico. Neste momento, esta região do Substrato se torna condutora, e com portadores de carga

negativa. Forma-se um canal N entre Dreno e Source, conforme mostrado na Fig. 1.4. Esta inversão do

canal ocorre para tensões Vgs ≥ VT , onde VT é a tensão de threshold. Esta região de operação é

chamada de triodo ou ôhmica. A equação simplificada que normalmente é usada para prever a corrente

de dreno nesta região é I d = W L µ Cox (Vgs − VT )Vds − Vds2 2 , onde µ é a mobilidade dos elétrons e

Cox a capacitância por unidade de área na região de Gate. A corrente I d é determinada pela diferença

de potencial Vds sobre o canal e a resistividade do mesmo.

Fig. 1.4: MOSFET polarizado na região de triodo.

6

Material não disponível para publicação

O aumento da tensão Vds eleva o campo elétrico existente entre Dreno e Gate, reduzindo o

potencial na superfície do substrato, logo abaixo do Gate. Com isto, o canal vai estreitando-se nas

proximidades do Dreno, até que é totalmente estrangulado (“pinch off”), conforme a Fig. 1.5. Neste

momento, a corrente I d não depende mais de Vds , e diz-se que o MOSFET está saturado. O

estrangulamento do canal ocorre quando a tensão entre Gate e Dreno é menor que a de threshold ou

seja, Vgd < VT . Como Vgd = Vgs − Vds , pode-se determinar a tensão Vds = Vsat a partir da qual o

MOSFET entra na região de saturação ou seja,

Vgd < VT → Vgs − Vds < VT → Vds > Vgs − VT → Vsat = Vgs − VT .

O MOSFET passa a atuar como uma fonte de corrente controlada pela tensão Vgs . A equação

simplificada que descreve a corrente de Dreno nesta região é I d = W L µ Cox (Vgs − VT ) 2 .

2

Fig. 1.5: MOSFET na região de saturação.

• Região de corte: Vgs ≤ 0

Id = 0

• Região de inversão fraca: 0 < Vgs < VT

(

q Vgs −VT

I d = I d 0e

ns kT

) −1

(1.1)

onde

Id 0 = k p

Vds2

W ns kT

V

−

ds

, para Vgd ≥ VT

2

L q

(1.2)

e

2

Id 0

k p W ns kT

=

, para Vgd < VT

2 L q

(1.3)

Obs: A constante ns é conhecida como coeficiente de emissão, e é um parâmetro de processo. Como

nesta região de operação I d é basicamente a corrente de saturação dos diodos Dreno-Substrato e

Source-Substrato, sua intensidade depende da profundidade X j das difusões de Source e Dreno,

conforme apresentado na Fig. 1.6. Portanto, ns tem dependência de X j em sua formulação.

• Região de triodo: Vgs ≥ VT , Vgd ≥ VT ou Vds ≤ Vsat , onde Vsat = Vgs − VT

Id =

V2

W

k p (Vgs − VT )Vds − ds

2

L

• Região de saturação: Vgs ≥ VT , Vgd < VT ou Vds > Vsat , onde Vsat = Vgs − VT

7

(1.4)

Material não disponível para publicação

Id =

2

W kp

Vgs − VT )

(

L 2

(1.5)

Fig. 1.6: Profundidade X j das difusões de Source e Dreno.

1.1.2 Efeito de Corpo

Quando uma tensão positiva Vsb é aplicada entre o Source e o Substrato, a região de depleção em

torno do Source aumenta, conforme a Fig. 1.7, aumentando também a tensão VT necessária para

formar o canal. Esta modulação na tensão de threshold, devida a Vsb , é conhecida como “efeito de

corpo”, e é expressa pela equação 1.6, onde VFB é a tensão de banda plana, Φ F é o potencial de Fermi

e γ é uma constante do processo de fabricação.

VT = VFB + 2Φ F + γ 2Φ F + Vsb

(1.6)

Fig. 1.7: Efeito de corpo.

1.1.3 Modulação de Canal

Quando ocorre o “pinch-off” (estrangulamento), a região de depleção invade o canal, diminuindo

seu comprimento efetivo, conforme indicado na Fig. 1.8. A diferença de potencial ao longo do canal

permanece Vsat , de forma que a corrente de Dreno passa a depender da resistência do canal resultante

I d = Vsat Rcanal . Pode-se estimar a corrente I d pela equação 1.5 substituindo-se L pelo seu valor

efetivo Lef = L − ∆L . Obtém-se então

Id =

2

W kp

Vgs − VT )

(

L − ∆L 2

(1.7)

A tensão sobre a região de depleção é ∆V = Vds − Vsat e a parcela ∆L podem ser estimadas pela

equação 1.8, onde q é a carga do elétron, ε á a constante dielétrica do óxido de silício e N A é a

concentração da dopagem do substrato.

∆L =

2ε

(Vds − Vsat )

qN A

Manipulando a equação 1.7 obtém-se

8

(1.8)

Material não disponível para publicação

Id =

2

2

W kp

W kp

L

Vgs − VT ) =

Vgs − VT )

(

(

L − ∆L 2

L 2

L − ∆L

(1.9)

Através da equação 1.8 e considerando ∆L L , o termo L ( L − ∆L ) pode ser aproximado por

L

1

∆L

=

≅ 1+

=1+

L

∆

L − ∆L 1 −

L

L

2ε

(Vds − Vsat ) = 1 +

L qN A

2

2ε

L qN A

2

(Vds − Vsat )

(1.10)

Uma aproximação rude para a equação 1.10 , mas muito utilizada para cálculos manuais, é

L

≅ 1+

L − ∆L

2ε

L qN A

2

(Vds − Vsat ) ≅ 1 + λVds

(1.11)

O parâmetro λ é uma constante que pode ser calculada empiricamente por

λ≅

107

L NA

(1.12)

onde L é medido em mícron e N A é a concentração da dopagem por centímetro cúbico.

Das equações 1.9 e 1.11, a corrente I d é melhor representada por

Id =

2

W kp

Vgs − VT ) (1 + λVds )

(

L 2

(1.13)

Verifica-se uma resistência finita entre Dreno e Source, na região de saturação, ditada pelo

parâmetro λ . Deve-se ter em mente que a tensão de threshold VT depende de Vsb , conforme previsto

pela equação 1.6.

Fig. 1.8: Modulação de canal.

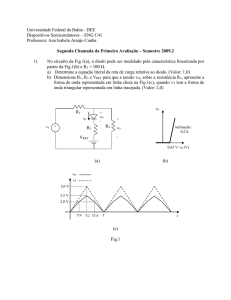

A Tabela 1.1 resume a corrente de Dreno para cada região de trabalho do MOSFET. Na Fig. 1.9

(a) e (b) são mostradas as formas das Curvas DC de um transistor MOSFET de canal N para os casos

sem e com modulação de canal respectivamente. Os gráficos da Fig. 1.10 (a) e (b) são simulações das

curvas DC para transistores de canal longo ( L = 50µ m ) e curto ( L = 1µ m ) respectivamente. Observe

que a corrente de Dreno sofre uma pequena inclinação na região de saturação, representando a

resistência finita entre Dreno e Source. Este efeito é muito menor para o transistor de canal longo.

9

Material não disponível para publicação

Tabela 1.1: Características DC do MOSFET de canal N.

REGIÃO DE OPERAÇÃO

CONDIÇÃO

CORRENTE DE DRENO

CORTE

Vgs ≤ 0

Id = 0

(

0 < Vgs < VT

INVERSÃO FRACA

Vgd ≥ VT

q Vgs −VT

I d = I d 0e

Id 0 = k p

Vgd < VT

Id 0

ns kT

) −1

V2

W ns kT

Vds − ds

2

L q

k p W ns kT

=

2 L q

2

Vgs ≥ VT , Vgd ≥ VT ou

TRIODO

Vds ≤ Vsat , onde

Vsat = Vgs − VT

Id =

V2

W

k p (Vgs − VT )Vds − ds

2

L

Id =

2

W kp

Vgs − VT ) (1 + λVds )

(

L 2

Vgs ≥ VT , Vgd < VT ou

SATURAÇÃO

Vds > Vsat , onde

Vsat = Vgs − VT

k p = µ Cox

VT = VFB + 2Φ F + γ 2Φ F + Vsb

(a)

(b)

Fig. 1.9: Curvas DC do transistor MOFET de canal N: a) Sem o efeito da modulação de canal

(resistência de saída infinita); b) com o efeito da modulação de canal (resistência de saída finita).

10

Material não disponível para publicação

1.2mA

0.8mA

0.4mA

0A

0V

ID(M1)

1.0V

2.0V

3.0V

4.0V

5.0V

3.0V

4.0V

5.0V

V_Vds

(a)

500uA

250uA

0A

0V

ID(M2)

1.0V

2.0V

V_Vds

(b)

Fig. 1.10: Curvas DC do MOSFET: a) Canal longo, W = 100 µ m e L = 50µ m ; b) Canal curto,

W = 2 µ m e L = 1µ m .

11

Material não disponível para publicação

1.1.4 MOSFET de Canal P

G

S

D

B

Fig. 1.11: Transistor MOSFET de canal P.

1.1.5 Características DC

As equações que descrevem o comportamento DC do transistor de canal P são as mesmas

empregadas para o de canal N. Neste caso, as tensões VT , Vgs , Vds e Vsb são negativas, e a corrente I d

é positiva mas no sentido Source-Dreno.

• Região de corte: Vgs ≥ 0

Id = 0

• Região de inversão fraca: VT < Vgs < 0

(

− q Vgs −VT

I d = I d 0e

ns kT

) −1

(1.14)

onde

I d 0 = −k p

V2

W ns kT

Vds + ds , para Vgd ≤ VT

2

L q

(1.15)

e

2

Id 0

k p W ns kT

=

, para Vgd > VT

2 L q

(1.16)

• Região de triodo: Vgs ≤ VT , Vgd ≤ VT ou Vds ≥ Vsat , onde Vsat = Vgs − VT

Id =

V2

W

k p (Vgs − VT )Vds − ds

2

L

(1.17)

• Região de saturação: Vgs ≤ VT , Vgd > VT ou Vds < Vsat , onde Vsat = Vgs − VT

Id =

2

W kp

Vgs − VT )

(

L 2

(1.18)

1.1.6 Efeito de Corpo

Os resultados são os mesmos obtidos para o MOSFET de canal N, mas que Φ F e Vsb são

negativos, é comum representá-los em módulo, conforme a equação 1.19.

VT = VFB − 2Φ F − γ

12

2Φ F + Vsb

(1.19)

Material não disponível para publicação

1.1.7 Modulação de Canal

As fórmulas tem a mesma forma que no caso do MOSFET tipo N, mas lembrando que Vds é

negativo, conforme a equação 1.21.

λ≅

Id =

107

(1.20)

L NA

2

W kp

Vgs − VT ) (1 + λVds )

(

L 2

(1.21)

A Tabela 1.1 resume as equações que modelam o MOSFET de canal P nas várias regiões de

operação.

Tabela 1.2: Curvas DC do MOSFET de canal P.

REGIÃO DE OPERAÇÃO

CONDIÇÃO

CORRENTE DE DRENO

CORTE

Vgs ≤ 0

Id = 0

(

0 < Vgs < VT

INVERSÃO FRACA

Vgd ≥ VT

q Vgs −VT

I d = I d 0e

Id 0 = k p

Vgd < VT

Id 0

ns kT

) −1

V2

W ns kT

Vds − ds

2

L q

k p W ns kT

=

2 L q

2

Vgs ≥ VT , Vgd ≥ VT ou

TRIODO

Vds ≤ Vsat , onde

Vsat = Vgs − VT

Id =

V2

W

k p (Vgs − VT )Vds − ds

2

L

Id =

2

W kp

Vgs − VT ) (1 − λVds )

(

L 2

Vgs ≥ VT , Vgd < VT ou

SATURAÇÃO

Vds > Vsat , onde

Vsat = Vgs − VT

k p = µ Cox

VT = VFB − 2Φ F − γ

2Φ F + Vsb

1.2 Tecnologia CMOS

A tecnologia CMOS consiste basicamente da implementação dos transistores MOSFET tipos N

(NMOS) e P (PMOS) em um mesmo substrato de silício. Tomando como exemplo um processo de

fabricação tipo N ou seja, os transistores NMOS são implementados diretamente no substrato P, para

que seja possível implementar os transistores PMOS, é necessário criar um poço tipo N (substrato),

conforme mostrado na Fig. 1.12.

A implementação de transistor sobre poço possui vantagens e desvantagens. Como aspecto

positivo, é possível implementar cada PMOS em poços separados, de forma que o terminal de Source

seja conectado ao poço (substrato), conforme a Fig. 1.13 (a), e desta forma evita-se o efeito de corpo.

Se o mesmo procedimento for aplicado aos transistores NMOS, obrigará todos os terminais de Source

serem comuns. Como aspecto negativo, pode-se citar a elevada capacitância entre poço e substrato,

para o PMOS.

13

Material não disponível para publicação

Fig. 1.12: Processo CMOS com poço N.

(a)

(b)

Fig. 1.13: Transistores MOS com terminas de Source e Dreno conectados: a) PMOS; b) NMOS.

1.3 Capacitâncias dos transistores MOSFET

Na Fig. 1.14 estão representadas as capacitâncias dos transistores MOS para um processo tipo N.

Os capacitores parasitas são basicamente os mesmos para o NMOS e o PMOS, sendo que para o

último existe o capacitor de poço para substrato Cwb .

Os capacitores parasitas são muito dependentes da polarização, e conseqüentemente da região de

operação. Como exemplo, considere o transistor NMOS. Na região de corte Vgs < VT , as cargas

negativas acumuladas no Gate atraem buracos para a região do canal, reforçando sua condutividade.

Identifica-se uma capacitância entre Gate e substrato C gb que depende da área efetiva do Gate e de sua

sobreposição sobre o substrato X ov , conforme mostrado na Fig. 1.15 (a). Verificam-se também as

capacitâncias entre Gate e Source C gs e Gate e Dreno C gd , devidas às sobreposições das difusões n+

( ∆L ), conforme a Fig. 1.15 (b). As junções Source-Substrato e Dreno-Substrato formam diodos

polarizados reversamente e portanto identificam-se duas capacitâncias de depleção Cdb e Csb .

Durante a inversão fraca 0 < Vgs < VT , devido à região de depleção no canal, a capacitância C gb

reduz muito seu valor, sendo dependente basicamente da sobreposição do Gate com o substrato. Os

capacitores C gs , C gd , Cdb e Csb não sofrem alterações apreciáveis.

Na região de triodo, forma-se um capacitor C gc entre Gate e canal que se divide igualmente entre

o Source e Dreno C gs = C gd = C gc 2 . Os demais capacitores não se alteram.

Ao entrar na saturação, a região de depleção formada ao redor do Dreno, devido ao

estrangulamento do canal, reduz drasticamente a capacitância C gd , que passa a depender da

sobreposição entre Gate e Dreno. O canal passa a ser uma extensão somente do Source e portanto, Cgs

aumenta. Os demais capacitores não alteram seus valores.

A Tabela 1.3 resume as equações que descrevem as capacitâncias parasitas, enquanto a Fig. 1.16

mostra o gráfico da variação dos capacitores com a polarização. Note que embora as capacitâncias de

14

Material não disponível para publicação

junção Csb e Cdb tenham sido consideradas constantes, elas variam com as dimensões do Source e do

Dreno, como também da tensão reversa aplicada às junções Source-Substrato e Dreno-Substrato.

Por analogia estende-se esta análise aos transistores PMOS, sendo que este último possui uma

capacitância de junção Poço-Substrato Cwb .

Fig. 1.14: Capacitâncias dos transistores MOSFET.

(a)

(b)

Fig. 1.15: Capacitâncias de sobreposição do Gate: a) Sobre Dreno e Source; b) Sobre o substrato.

15

Material não disponível para publicação

Tabela 1.3: Equações dos capacitores parasitas.

CORTE

INVERSÃO FRACA

TRIODO

SATURAÇÃO

C gd

C gdoW

C gdoW

1

C gdoWLef Cox + C gdoW

2

C gdoW

Cdb

Cdj

Cdj

Cdj

Cdj

C gb

CoxWLef + C gbo L

C gbo L

C gbo L

C gbo L

C gs

C gsoW

C gsoW

1

C gsoWLef Cox + C gsoW

2

2

C gsoWLef Cox + C gsoW

3

Csb

Csj

Csj

Csj

Csj

C gbo é a capacitância de sobreposição Gate-Substrato por comprimento de canal.

C gdo é a capacitância de sobreposição Gate-Dreno por largura de canal.

C gso é a capacitância de sobreposição Gate-Source por largura de canal.

Csj e Cdj são as capacitâncias das junções Source-Substrato e Dreno-Substrato.

Cox é a capacitância por unidade de área do Gate.

Fig. 1.16: Gráfico de variação dos capacitores parasitas no NMOS em função da polarização.

1.4 Análise de Pequenos Sinais (AC)

A análise de pequenos sinais é uma ferramenta muito útil no projeto de circuitos integrados (CI)

analógicos, principalmente no estudo do comportamento em altas freqüências, na análise de

estabilidade e ruído. Os transistores NMOS e PMOS possuem o mesmo modelo AC e portanto, será

estudado somente o transistor NMOS, e na configuração Source comum.

Considere o circuito da Fig. 1.17. Na região de saturação tem-se

Id =

2

W kp

Vgs − VT ) (1 + λVds )

(

L 2

e

VT = VFB + 2Φ F + γ 2Φ F + Vsb

Conforme pode ser visto, Vbs = −Vsb e portanto,

16

(1.22)

Material não disponível para publicação

VT = VFB + 2Φ F + γ 2Φ F − Vbs

(1.23)

Pode-se calcular a variação de pequenos sinais da corrente de Dreno id por

id =

∂I d

∂I

∂I

vgs + d vds + d vbs

∂Vgs

∂Vds

∂Vbs

ou de forma equivalente

id = gmvgs + Gds vds + gmb vbs

onde gm =

∂I d

∂I

∂I

, Gds = d e gmb = d .

∂Vgs

∂Vds

∂Vbs

Id

D

G

Vds

S

Vgs

Vbs

Fig. 1.17: Configuração Source comum.

• Cálculo de gm

gm =

∂I d

W

= k p (Vgs − VT ) (1 + λVds )

L

∂Vgs

(1.24)

2I d

(Vgs − VT )

(1.25)

De forma equivalente, tem-se

gm =

ou

gm =

2 I d k pW (1 + λVds )

L

(1.26)

• Cálculo de Gds

Gds =

kp W

2

∂I d

=λ

Vgs − VT )

(

2 L

∂Vds

(1.27)

pode-se considerar com boa aproximação que

Gds = λ I d

• Cálculo do gmb

Pela regra da cadeia, tem-se que

gmb =

∂I d

∂I ∂VT

= d

∂Vbs ∂VT ∂Vbs

Usando as equações 1.22 e 1.23 tem-se

17

(1.28)

Material não disponível para publicação

gmb = γ

k p W (Vgs − VT ) (1 + λVds )

Id

1

γ

γ

gm

=

=

2 L

2Φ F − Vbs

2Φ F − Vbs (Vgs − VT ) 2 2Φ F − Vbs

(1.29)

ou de forma mais sintética

gmb = η gm

(1.30)

1

γ

2 2Φ F − Vbs

(1.31)

onde

η=

A análise para os transistores PMOS é idêntica, bastando empregar as equações da Tabela 1.2. A

Tabela 1.4 resume os parâmetros de pequenos sinais.

Tabela 1.4: Parâmetros de pequenos sinais dos transistores NMOS e PMOS.

NMOS

gm

PMOS

2 I d k pW (1 + λVds )

2I d

ou

(Vgs − VT )

L

2I d

ou

Vgs − VT

2 I d k pW (1 − λVds )

L

Gds

λ Id

λ Id

gmb

η gm

η gm

η

1

γ

2 2Φ F − Vbs

1

2

γ

2Φ F + Vbs

1.4.1 Modelo Para Altas Freqüências

De posse dos parâmetros de pequenos sinais e das capacitâncias parasitas, obtém-se o modelo da

Fig. 1.18 para altas freqüências.

Id

Cgd

G

D

Cgs

gmVgs

Gds

gmbVbs

S

S

Cgb

Cdb

Csb

B

Fig. 1.18: Modelo de altas freqüências.

Ex: O circuito abaixo é um amplificador Source comum cuja carga é uma fonte de corrente ideal.

Nesta situação, o amplificador apresenta o maior ganho possível. Analise o circuito com respeito ao

ganho DC e AC.

18

Material não disponível para publicação

vo

vin

Id

Vgs

Substituindo o circuito pelo modelo de pequenos sinais tem-se

Cgd

iin

vo

vin

gm vin

Cgs

Cgb

Cdb

Gds

Aplicando-se a lei dos nós ao circuito tem-se

( vo − vin ) sCgd + gmvin + vo sCdb + voGds = 0

cuja solução para vo vin é

vo gm

=

vin Gds

s

C gd

−1

gm

( Cgd − Cdb )

s

Gds

+1

O ganho em baixas freqüências é dado por

vo

gm

=−

=−

vin

Gds

Usando a aproximação λ ≅ 107

(L

2I d

(Vgs − VT )

λ Id

=−

2

λ (Vgs − VT )

)

N A , obtém-se

2 NA L

vo

=− 7

vin

10 (Vgs − VT )

(1.32)

A freqüência de corte é dada por

ωc =

Gds

C gd + Cdb

Assumindo a constante C j como sendo a capacitância da difusão de Dreno por largura de canal, de tal

forma que Cdb = WC j , e utilizando as equações da Tabela 1.3, tem-se para a freqüência de corte

107 k p (Vgs − VT )

λ k p (Vgs − VT )

λ Id

ωc =

=

=

W ( C gdo + C j )

L ( C gdo + C j )

N A L2 ( C gdo + C j )

2

2

(1.33)

Verifica-se que para a mesma polarização (Vgs − VT ) , o ganho DC não depende (em primeira

análise) da largura do canal W , mas sim do comprimento L . A freqüência de corte é extremamente

19

Material não disponível para publicação

dependente do L e como regra, para aumentá-la (tornar o amplificador mais rápido) deve-se reduzir o

L e aumentar a tensão (Vgs − VT ) .

Outro parâmetro importante é a freqüência de transição ωT , onde o ganho de corrente é unitário

id iin = 1 , e considera-se que o transistor não atua mais como elemento ativo. A corrente id é

calculada com base no circuito abaixo

Cgd

id

vin

gm vin

iin

Cgs

Cgb

Cdb

Gds

Aplicando as equações de nós ao circuito, tem-se o sistema

iin = s ( Cgs + Cgb + Cgd ) vin

id = gmvin − sCgd vin

cuja solução para id iin é

id

gm

=−

iin

( Cgs + Cgb + Cgd )

s

C gd

gm

s

−1

Fazendo a substituição s = jω e forçando a condição id iin = 1 , obtém-se para ωT

ωT =

gm

(C

2

+ C gb + C gd ) − C gd

2

gs

≅

gm

C gs

Empregando a equação 1.24 e a Tabela 1.3, obtém-se

ωT =

3k p (Vgs − VT ) (1 + λVds )

2 L2Cox

onde também se verifica uma forte dependência com o comprimento de canal L .

1.5 Layout dos Transistores

A forma trivial de desenhar o transistor é como na Fig. 1.19. Entretanto, para transistores muito

largos, não é um bom procedimento de projeto, pois normalmente ocorrem variações no processo de

fabricação como gradiente de processo e imperfeições nas máscaras. Outro problema comum é o

gradiente de temperatura, que ocorre quando o CI possui uma fonte localizada de calor (um estágio de

potência por exemplo) provocando uma variação de temperatura ao longo da pastilha. Isto pode

promover variações nos parâmetros elétricos do transistor ao longo de suas dimensões. Deve-se tentar

usar a forma mais próxima possível do quadrado.

20

Material não disponível para publicação

Fig. 1.19: Layout para o transistor NMOS.

Em um array de dispositivos, uma regra prática diz que, quando se deseja um bom casamento,

deve-se evitar distâncias maiores que 50µ m entre os dispositivos casados.

No caso de transistores, pode-se construí-los pela associação de N transistores menores em paralelo

(interdigitados), com larguras W N conforme a Fig. 1.20. O layout é mostrado na Fig. 1.21. onde se

verifica que o transistor é mais compacto, ocupando uma área mais uniforme. Outro fator importante é

a diminuição das áreas efetivas de Dreno e Source, que leva a uma redução das capacitâncias Cdb e

Csb , melhorando a resposta em freqüência. Neste exemplo, considerando Ad e As as áreas de Dreno e

Source do transistor sem interdigitação, as novas áreas após a interdigitação serão A'′d = 3 Ad 4 e

A'′s = As 2 .

G

W = 1u

L = 1u

G

D

W = 4u

L = 1u

D

S

W = 1u

L = 1u

S

D

W = 1u

L = 1u

D

S

W = 1u

L = 1u

S

D

S

S

B

B

D

Fig. 1.20: Transistor interdigitado.

Fig. 1.21: Layout do transistor interdigitado.

1.5.1 Layout Para transistores PMOS com Poço N

Os transistores PMOS são construídos da mesma forma que os NMOS, mas deve-se considerar o

poço N, conforme a Fig. 1.22. Neste caso, pode-se ter o poço suspenso, conectado ao Source (evitando

o efeito de corpo), ou conectado ao Vdd . No primeiro caso, arca-se com o ônus de uma capacitância

parasita Source-Substrato muito grande. É altamente recomendável que o poço seja circundado por um

21

Material não disponível para publicação

anel de guarda polarizado, de forma a evitar o latchup1. Os transistores PMOS com poço N também

devem ser interdigitados, sempre que possível.

Fig. 1.22: Layout para o transistor PMOS com poço N.

2. Resistores

Os resistores integrados são implementados usando-se a resistência de superfície de algum material

(METAL, POLY ou DIFUSÃO).

Dado um material com forma quadrada, sua resistência é sempre a mesma, independente da área, e

definida pela constante R, . A Fig. 2.1 elucida esta propriedade. Portanto, um resistor R retangular,

com dimensões L e W possui resistência

R=

L

R,

W

(2.1)

Fig. 2.1: Resistência por quadrado de um material.

2.1 Formas de Implementação dos Resistores

As estruturas apresentadas a seguir consideram substrato tipo P e poço N, embora as formas se

aplicam também ao oposto.

1

Curto-circuito da fonte de alimentação, devido ao disparo de transistores parasitas no substrato.

22

Material não disponível para publicação

2.1.1 Resistor de Difusão N

O resistor é implementado por uma região de difusão n+ com dimensões L e W , e o valor

calculado pela equação 2.1. Neste caso, as resistências obtidas são baixas, devido à alta condutividade

da difusão n+. Este tipo de resistor é muito suscetível a ruídos do substrato, e seu valor é dependente

da polarização (não linear).

Fig. 2.2: Resistor de difusão n+.

2.1.2 Resistor de Difusão p+ Sobre Poço N Polarizado

Este tipo de resistor é essencialmente o mesmo que o anterior, mas conta com uma blindagem

extra, que é o poço N.

Fig. 2.3: Resistor de difusão p+ sobre poço N polarizado.

2.1.3 Resistor de Poço N

Este tipo de resistor é utilizado quando se deseja altas resistências ( kΩ ), devido à baixa

condutividade do poço. Entretanto, é muito suscetível a ruídos transmitidos por acoplamento entre

poço e substrato. O mesmo princípio se aplica ao processo com poço P.

Fig. 2.4: Resistor sobre de N.

2.1.4 Resistor de Poço Estrangulado (“Pinched Well”)

Este resistor possui uma difusão p+ em cima do poço, que o torna estrangulado, forçando a corrente

a passar por dentro do poço. Como a parte condutiva possui altura menor, este resistor apresenta

resistência maior que o anterior. Obtém-se também uma substancial redução do ruído flicker ( 1 f ),

essencialmente gerado na superfície do substrato. Esta configuração também sofre com ruídos

transmitidos por acoplamento de poço com substrato.

23

Material não disponível para publicação

Fig. 2.5: Resistor de poço estrangulado.

2.1.5 Resistor de Polysilício Sobre Substrato

Esta implementação utiliza-se da resistência de superfície do polysilício (POLY). Como a camada

de POLY está afastada do substrato, o ruído por acoplamento é menor. As resistências obtidas para R,

são da ordem das dezenas de ohms. Estes resistores são bastante lineares e muito pouco de pendentes

da tensão de polarização.

Fig. 2.6: Resistor de POLY sobre substrato.

2.1.6 Resistor de Polysilício Sobre Poço Polarizado

Esta implementação é basicamente a mesma que a anterior, mas o resistor encontra-se sobre poço

polarizado, que funciona como blindagem. Esta é a forma preferida para implementação de resistores.

Fig. 2.7: Resistor de POLY sobre poço polarizado.

2.1.7 Resistor de POLY2 Sobre Difusão p+ e Poço N

Esta forma é um aprimoramento do anterior, pois utiliza uma difusão p+ sob a placa resistiva,

oferecendo uma blindagem extra. Neste caso é utilizada a camada de POLY2, por estar mais afastada

da difusão p+, o que ajuda a reduzir a capacitância parasita.

24

Material não disponível para publicação

Fig. 2.8: Resistor de POLY2 sobre difusão p+ e poço N.

Pode-se obter uma blindagem superior, depositando uma camada de METAL2, conectada ao terra

do circuito, sobre a placa de POLY2. Desta forma, o resistor fica encapsulado.

Fig. 2.9: Resistor de POLY2 sobre difusão p+ e poço N, com blindagem de METAL2 no topo.

2.2 Erros na Construção dos Resistores

As variações do resistor em torno de seu valor nominal se devem basicamente aos erros associados

à geometria e às alterações das constantes físicas que determinam a resistividade do material.

Os principais erros de geometria são:

• Undercut - Corrosão lateral por baixo da máscara, que modifica as dimensões W e L .

Fig. 2.10: Undercut.

• Boundary Mismatch - A corrosão não se faz igual, devido às distâncias diferentes entre as

máscaras.

Fig. 2.11: Boundary mismatch.

• Difusão Lateral - A difusão estende-se por baixo do óxido de silício, aumentando a superfície do

resistor. Este erro afeta essencialmente os resistores n+, p+, N-Well e P-Well.

25

Material não disponível para publicação

Fig. 2.12: Difusão lateral.

Os erros associados às alterações de resistividade mais comuns são:

• Defeitos na Rede Cristalina.

• Stress - O stress na superfície do chip, causado pelo encapsulamento, altera o valor da resistividade.

• Temperatura - A resistividade depende da temperatura, e mais grave ainda, do gradiente térmico.

Este último provoca erros nas relações de resistores.

2.3 Layout Para Resistores

A Fig. 2.13 apresenta um layout muito usado para a implementação de resistores de POLY sobre

poço polarizado, conforme esquematizado na Fig. 2.7. Chama-se atenção para a estrutura dummy de

POLY, usada para manter o equilíbrio geométrico (simetria) do resistor. Deve-se observar também o

anel de polarização do substrato P ao redor do poço, que atua como uma blindagem extra.

Fig. 2.13: Layout para resistores de POLY sobre poço polarizado.

Quando se tem razões de resistores, deve-se optar pela configuração interdigitada e em centróide

comum, sempre que possível. A configuração em centróide comum será abordada em detalhes na

seção referente ao projeto de capacitores. Desta forma, minimiza-se o erro relativo provocado pelo

gradiente de processo. Este tema será melhor abordado na seção relativa aos capacitores. A Fig. 2.14

apresenta uma configuração para dois resistores.

26

Material não disponível para publicação

Fig. 2.14: Array de dois resistores.

27

Material não disponível para publicação

3. Capacitores

Os capacitores integrados são os elementos de maior precisão relativa disponíveis. Os capacitores

são formados por placas paralelas, cujo espaçamento é bem controlado, e os valores dados por:

C = CoxWL + C p P

(3.1)

onde

Cox =

ε

é a capacitância por unidade de área.

tox

P é o perímetro.

C p é a capacitância por unidade de comprimento.

Fig. 3.1: capacitor de placas paralelas.

3.1 Tipos de Capacitores

3.1.1 Capacitor de POLY Sobre Difusão

Este capacitor é simplesmente uma placa de POLY1, com dimensões definidas, sobre difusão n+

ou p+. Esta estrutura é muito sensível ao ruído no substrato, e apresenta capacitância não linear,

dependente da tensão de polarização.

Fig. 3.2: Capacitor de POLY sobre difusão.

3.1.2 Capacitor de POLY2 sobre POLY1 sobre Poço Polarizado

Esta é a forma preferida para implementar os capacitores, pois a capacitância é linear, e o poço

polarizado atua como blindagem. No esquema da Fig. 3.3, o poço é polarizado em Vdd .

28

Material não disponível para publicação

Fig. 3.3: Capacitor de POLY2 sobre POLY1 sobre poço polarizado.

3.2 Modelo dos Capacitores

Todo capacitor apresentará uma capacitância entre placas ( C ), outra entre a placa inferior e

substrato ( C pb ) e outra entre a placa superior e o substrato ( C pt ), conforme a Fig. 3.4. C pt

normalmente pode ser negligenciada, pois é muito menor que C . No caso dos capacitores de POLY

sobre difusão C pb é não linear, mas é pequeno quando comparado a C . Para os capacitores de PLOY1

sobre POLY2 C pb está sobre óxido grosso, e seu valor é pequeno quando comparado a C .

C

Botton

Top

Cpb

Cpt

Substrato

Fig. 3.4: Modelo dos capacitores.

3.2.1 Precisão dos Capacitores

Conforme mostrado anteriormente, o valor da capacitância é dado por C = CoxWL + C p P . Para o

cálculo da precisão serão feitas as considerações: a parcela da capacitância correspondente ao

perímetro será desprezada por ser consideravelmente menor que a parcela da área; os erros associados

a Cox , W e L são estatisticamente independentes; os desvios padrões são muito menores que os

valores médios ou seja, σ C2ox Cox 1 , σ W2 W 1 e σ L2 L 1 . Desta forma, tem-se C = CoxWL e o

valor médio

C = CoxWL

(3.2)

Calculando a variação de C em torno de seu valor médio tem-se

∂C

∂W

∂L

∆Cox +

∆W +

∆L

∂Cox

∂W

∂L

(3.3)

∆C = WL ∆Cox + Cox L ∆W + CoxW ∆L

(3.4)

∆C =

ou

A variação relativa é dada por

29

Material não disponível para publicação

∆C ∆Cox ∆W ∆L

=

+

+

C

Cox

W

L

(3.5)

Calculando o valor esperado de ( ∆C C ) tem-se

2

2

∆C

∆C 2

∆W ∆ L

ox

E

+

+

= E

W

L

Cox

C

(3.6)

que para variáveis estatisticamente independentes, é equivalente a

∆C 2

∆C 2

∆W 2

∆L 2

ox

E

+ E

= E

+ E

Cox

C

W

L

(3.7)

Sendo ∆Cox , ∆W e ∆L variações em torno dos valores médios, obtém-se finalmente

2

σ C2 σ Cox σ W2 σ L2

=

+

+

C 2 Cox2 W 2 L2

(3.8)

Os erros em Cox são em geral causados por impurezas e danos associados ao óxido, stress e

temperatura, enquanto ∆W e ∆L são devidos ao undercut.

Um cuidado especial deve ser tomado ao projetar capacitores onde a razão entre eles é importante.

Devido ao undercut, a área efetiva se torna menor, conforme a Fig. 3.5.

Fig. 3.5: Erros nas dimensões devido ao undercut.

Considerando um erro tendencioso para W e L ou seja, ∆W = ∆L = ∆x tem-se que

A′ = W ′L′ = (W − ∆x )( L − ∆x ) = WL − ∆x (W + L ) + ∆x 2

(3.9)

Como ∆x 2 é um erro de segunda ordem, pode ser desprezado. A área resultante é finalmente

A′ = WL − ∆x (W + L ) = A −

P∆x

2

(3.10)

ou

P ∆x

A′ = A 1 −

A 2

(3.11)

Quando se deseja estabelecer uma razão precisa entre capacitores, C1 C2 = A1 A2 , mesmo sob o

efeito do undercut, C1′ C2′ = A1′ A2′ , deve-se tomar o cuidado de fazer a razão perímetro-área ( P A )

constante nos dois capacitores. A melhor forma de realização é implementar os capacitores pela

30

Material não disponível para publicação

associação de capacitâncias menores (ditas unitárias). Desta forma, mantém-se a razão entre as áreas, e

também entre os perímetros, conservando as relações entre as capacitâncias de área e perímetro

constantes. Entretanto, este procedimento não permite realizar qualquer relação de capacitores, pois

está restrita a frações de números inteiros. Mas mesmo assim, deve-se usar o maior número possível de

elementos iguais.

Ex: Dois capacitores de POLY1 sobre POLY2 são construídos com as dimensões 10 × 10 µ m e

20 × 20 µ m respectivamente. O undercut é de 0.2 µ m com σ W = σ L = 0.04µ m . A capacitância por

unidade de área é Cox = 1.68 fF µ m 2 . Calcule as capacitâncias efetivas e os erros.

1º) As áreas nominais são:

A1 = 10 × 10 µ m 2 = 100 µ m 2

A2 = 20 × 20 µ m 2 = 400 µ m 2

As áreas efetivas são:

A1′ = (10 − 0.2 − 0.2 ) × (10 − 0.2 − 0.2 ) µ m 2 = 92.16 µ m 2

A2′ = ( 20 − 0.2 − 0.2 ) × ( 20 − 0.2 − 0.2 ) µ m 2 = 384.16 µ m 2

Os capacitores efetivos e nominais são:

C1′ = 154.8 fF

C2′ = 645.4 fF

C1 = 168 fF

erro = −8%

C2 = 672 fF

erro = −4%

2º) Tolerância:

σ C21′

C1′

2

=

σ w21

W1′

2

+

σ L21

1

1

= σ x2 2 + 2

L′

L1′

W1′

2

1

σ C1′

1

1

= σ x2 2 + 2 = 0.59%

C1′

L1′

W1′

σ C2′

1

1

= σ x2 2 + 2 = 0.29%

C2′

L2′

W2′

3.2.2 Erro nas Razões de Capacitores

Conforme estudado no exemplo anterior, o erro de undercut possui uma componente tendenciosa e

outra completamente aleatória. Numa razão de capacitores, o erro tendencioso pode ser compensado

mantendo a razão entre perímetro e área constante entre os capacitores, conforme a equação 3.11. Para

o cálculo da precisão na razão de dois capacitores R = C1 C2 , serão feitas as considerações: os erros

associados a C1 e C2 são estatisticamente independentes; os desvios padrões são muito menores que

os valores médios ou seja, σ C21 C1 1 e σ C22 C2 1 . Desta forma, é razoável aproximar a função

1 C2 pelos dois primeiros termos da série de Taylor em torno do valor médio de C2 , obtendo-se

1

1 C2 − C2

=

−

C2 C2

C22

(3.12)

1 C2 − C2

C1

≅ C1

−

C2

C22

C2

(3.13)

Obtém-se então para a razão

R=

31

Material não disponível para publicação

cujo valor esperado (médio) é

1 C2 − C2 C1

R = E C1

−

=

C22 C2

C2

(3.14)

O erro em torno de R pode ser estimado por

∆R =

∆C1 C1

∂R

∂R

∆C1 +

∆C2 =

−

∆C 2

C2 C22

∂C1

∂C2

(3.15)

e a tolerância calculada como

∆R ∆C1 ∆C2

=

−

R

C1

C2

(3.16)

Elevando a equação 3.16 ao quadrado e calculando o valor esperado obtém-se

2

2

σ R2 σ C1 σ C2

=

+

R 2 C12 C22

(3.17)

σ C21 σ C22

σR

=

+

R

C12 C22

(3.18)

cuja tolerância é

Quando os capacitores C1 e C2 são implementados pela associação de capacitâncias unitárias

C = CoxWef Lef ou seja, C1 = MC e C2 = NC , e considerando Cox idêntico para C1 e C2 , tem-se pela

equação 3.4 que

M

∆C1 = ∑ Cox Lef ∆Wi + CoxWef ∆Li

(3.19)

i =1

e

N

∆C2 = ∑ Cox Lef ∆Wi + CoxWef ∆Li

(3.20)

i =1

Assumindo que os erros ∆Wi e ∆Li são estatisticamente independentes, e que σ Wi = σ Li = σ x ,

elevando as equações 3.19 e 3.20 ao quadrado e calculando o valor esperado tem-se

σ C21 = MCox2 (Wef2 + Lef2 )σ x2

(3.21)

σ C22 = NCox2 (Wef2 + Lef2 )σ x2

(3.22)

e

Como C1 = MC = MCoxWef Lef e C2 = NC = NCoxWef Lef , pode-se calcular as tolerâncias de C1 e C2

por

σ C21

2

1

C

=

MCox2 (Wef2 + Lef2 ) σ x2

2

2

ox

2

ef

2

ef

M C W L

(W

=

+ Lef2

(W

+ Lef2

2

ef

2

ef

2

ef

MW L

)σ

2

x

(3.23)

)σ

2

x

(3.24)

e

σ C22

C

2

2

=

NCox2 (Wef2 + Lef2 )σ x2

2

2

ox

2

ef

2

ef

N C W L

=

2

ef

2

ef

2

ef

NW L

Utilizando as equações 3.18, 3.23 e 3.24 obtém-se finalmente para a tolerância da razão entre dois

capacitores

32

Material não disponível para publicação

Wef2 + L2ef

σR

=σx

R

Wef Lef

1

1

+

M N

(3.25)

É interessante observar que a tolerância tende para zero quando M e N tendem para infinito ou

seja, quanto maior o número de capacitores unitários mais precisa é a razão.

3.3 Layout dos Capacitores POLY1 Sobre POLY2

Neste tipo de capacitor, a placa de POLY1 deve ser maior que a de POLY2, de forma que a área

seja definida pela placa de POLY2. A melhor forma de implementação e colocar o contato no centro

da placa de POLY2, conforme a Fig. 3.6. Para evitar o acúmulo de cargas nas quinas do capacitor,

devido ao efeito de pontas, a placa de POLY2 deve possuir arestas em 135º.

Alguns processos exigem que, ao se colocar o contato no centro da placa de POLY2, a placa de

POLY1 deve ter um buraco exatamente abaixo do contato, conforme a Fig. 3.7. Desta forma, a área do

buraco deve ser subtraída do total, durante o cálculo da capacitância.

Fig. 3.6: Capacitor de POLY2 sobre POLY1 com contato no centro.

Fig. 3.7: Capacitor de POLY2 sobre POLY1 com contato no centro e buraco na placa de POLY1.

Outro procedimento muito empregado é colocar o contato fora da região de sobreposição das

placas. Isto é feito esticando-se uma tira de POLY2 para fora, conforme mostrado na Fig. 3.8. Um

problema comum à esta implementação é o erro na capacitância provocado pelo desalinhamento das

máscaras. Observa-se que a área correspondente à extensão x , da tira de POLY2 que se sobrepõe à

placa de POLY1, deve ser considerada no cálculo do capacitor. Caso haja um deslocamento horizontal

33

Material não disponível para publicação

da placa de POLY2, x pode aumentar ou diminuir, mudando o valor efetivo da área. Para resolver

este problema, mais três tiras são colocadas nos sentidos horizontais e verticais, no formato de catavento. Desta forma, deslocamentos horizontais e verticais na placa de POLY2 implicam em aumentos

e reduções equivalentes nas áreas sobrepostas pelas tiras, mantendo a área efetiva constante, e

conseqüentemente a capacitância.

Fig. 3.8: Capacitor de POLY2 sobre POLY1 com contato externo.

3.4 Distribuição Física dos Capacitores

Além dos erros provocados pela geometria, temos aqueles gerados por gradiente de processo e

temperatura, que alteram tendenciosamente as constantes físicas que determinam a capacitância. Desta

forma, quando se tem uma associação de capacitores unitários, estes podem ter valores diferentes

dependendo do posicionamento. Na implementação de uma razão de capacitores, estes erros podem

ser significativos. Uma forma de minimizar este efeito consiste em dispor os capacitores unitários

interdigitados e na configuração de centróide comum (mesmo cetro de massa). Nem sempre é possível

este procedimento, mas deve-se tentar chegar o mais próximo do ideal. O exemplo a seguir ilustra este

procedimento.

EX: Calcular o erro na razão de capacitores C1 C2 ( C1 = C2 ), das configurações abaixo. O gradiente

de processo na direção x é de 200 ppm µ m .

a) C1 e C2 são formados por dois capacitores unitários C . Entretanto, devido ao gradiente de

processo, tem-se dois conjuntos de capacitores unitários C e C ′ .

C1 = 2C

C2 = 2C ′ = 2 ( C + 0.02C ) = 2.04C

C1

= 0.98 → erro = 1.9%

C2

A razão ideal é C1 C2 = 1 , entretanto obtém-se C1 C2 = 0.98 com erro de 1.9% em relação ao

ideal.

b) Configuração em centróide comum.

34

Material não disponível para publicação

C1 = C + C ′

C2 = C + C ′

C1 C + C ′

=

= 1 → erro = 0

C2 C + C ′

Conclui-se que para um gradiente linear, o erro é zero quando se usa o centróide comum.

Entretanto, o gradiente de processo é em geral não linear. Desta forma, a interdigitação ajuda, pois

garante uma distância minimizada entre as componentes de C1 e C2 em grandes arrays.

3.5 Montagem do Capacitor

A montagem do capacitor é feita sobre um poço polarizado com anel de guarda e capacitores

dummy, para equilibrar geometricamente a estrutura, garantindo um undercut uniforme e uma

distribuição de linhas de campo elétrico idênticas nas componentes unitárias. A Fig. 3.9 ilustra este

procedimento.

C

B

C2=C

C1=C

A

Fig. 3.9: Array de capacitores.

Cada capacitor dummy deve ser metade de um real, pois considera-se que cada capacitor enxerga

metade do outro, conforme a Fig. 3.10.

Quando for indispensável a implementação de razão de números não inteiros, pode-se desenhar um

ou mais capacitores de tamanhos diferentes dos unitários, mas completando-se os espaços vazios com

dummys, e mantendo-se as razões entre áreas e perímetros idênticas para todos os capacitores,

conforme mostrado na Fig. 3.11. Este procedimento não é muito preciso.

35

Material não disponível para publicação

Fig. 3.10: Layout do capacitor dummy.

Fig. 3.11: Razão não inteira de capacitores.

36

Material não disponível para publicação

4. Chaves Analógicas

As chaves analógicas são os dispositivos integrados mais simples que existem, mas de grande

importância. Seu papel nos circuitos a capacitores chaveados é de fundamental importância, pois são

elas permitem a dinâmica do sinal.

4.1 Chave Simples Tipo N

A grande aplicação das chaves analógicas encontra-se nos circuitos a capacitores chaveados. Como

exemplo, considere o Sample-Hold da Fig. 4.1. A tensão Vg controla o fechamento e a abertura da

chave. Sendo o transistor NMOS, a chave abre com Vg < VT + Vo e fecha com Vg ≥ VT + Vo .

Normalmente utiliza-se Vg = 0 como sinal de controle para a abertura da chave, e Vg = Vdd para o

fechamento.

Vg

Vo

C

Vin

Fig. 4.1: Circuito básico de um Sample-Hold com um transistor NMOS.

Em primeiro lugar, deve-se considerar a região de trabalho do transistor. Se a chave permanecer

fechada por tempo suficiente, a tensão Vo no capacitor será igual a Vin . Para que isto seja verdade, em

Vo = Vin o transistor deve estar em condução ou seja,

Vg − Vo ≥ VT

Vdd − Vin ≥ VT

Vin ≤ Vdd − VT

(4.1)

Entretanto, esta é também a condição para o transistor estar na região de triodo.

Vgd ≥ VT

Vg − Vd ≥ VT

Vdd − Vin ≥ VT

Vin ≤ Vdd − VT

Na região de triodo, a equação da corrente de Dreno no transistor NMOS é

Id =

V2

W

k p (Vgs − VT )Vds − ds

2

L

e

∂I d W

= k p (Vgs − VT ) − Vds

∂Vds L

Com Vds = 0 tem-se para a resistência da chave fechada

37

(4.2)

Material não disponível para publicação

Ron =

1

(4.3)

W

k p (Vgs − VT )

L

Como Vgs = Vdd − Vin tem-se finalmente

Ron =

1

W

k p (Vdd − VT − Vin )

L

(4.4)

As dimensões W e L ajustam a resistência ON da chave, que deve ser determinada em função do

tempo de carregamento do capacitor. O gráfico de Ron pode ser visto na Fig. 4.2

Fig. 4.2: Gráfico da resistência Ron da chave NMOS em função de Vin .

A resistência é mínima em Vin = 0 e infinita em Vin = Vdd − VT . Esta variação de resistência é em

geral um grave inconveniente. A chave simples não permite a operação em “rail-to-rail”.

4.2 Chave Simples Tipo P

A chave tipo P tem o funcionamento essencialmente igual à N. Neste caso, utiliza-se Vg = Vdd

como sinal de controle para a abertura da chave, e Vg = 0 para o fechamento. Considerando o SampleHold da Fig. 4.3, verifica-se que a chave P também opera região de triodo, e sua faixa de atuação é

VT ≤ Vin ≤ Vdd

(4.5)

Vg

G

D

Vin

S

Vdd

Vo

C

Fig. 4.3: Circuito básico de um Sample-Hold com um transistor NMOS.

A resistência é calculada da mesma forma que a chave N, mas aplicando-se o sinal negativo à

equação 4.2, devido ao sentido inverso da corrente de Dreno.

∂I

1

W

= − d = − k p (Vgs − VT ) − Vds

Ron

L

∂Vds

38

(4.6)

Material não disponível para publicação

Portanto, com Vds = 0 tem-se

Ron =

1

W

k p (VT − Vgs )

L

(4.7)

Sendo Vgs = −Vin tem-se finalmente

Ron =

1

W

k p (Vin − VT

L

(4.8)

)

O gráfico de Ron encontra-se na Fig. 4.4.

Verifica-se que seu funcionamento é oposto ao da chave N. Pela associação em paralelo dos dois

tipos de chaves, pode-se obter o funcionamento “rail-to-rail”.

Fig. 4.4: Gráfico da resistência Ron da chave PMOS em função de Vin .

4.3 Chave Complementar

Com o objetivo de melhorar a resistência da chave, e permitir a operação em “rail-to-rail”, utilizase a chave complementar, que são simplesmente duas chaves N e P em paralelo, conforme a Fig. 4.5.

Os sinais de controle são: VgN = Vdd e VgP = 0 para o fechamento; VgN = 0 e VgP = Vdd para a abertura.

Vgn

Mn

Vo

Vdd

Vin

C

Mp

Vgp

Fig. 4.5: chave complementar.

Dependendo da tensão Vin , as chaves conduzem exclusivamente e simultaneamente. Os intervalos

de condução e as resistências estão na Tabela 4.1.

39

Material não disponível para publicação

Tabela 4.1: Intervalos de condução e resistência da chave complementar.

Vin

Chave N

Chave P

0 ≤ Vin ≤ VTP

ON

OFF

VTP ≤ Vin ≤ Vdd − VTN

ON

ON

Vin ≥ Vdd − VTN

OFF

ON

Gon = 1 Ron

Gon =

Gon =

WN

k pN Vdd − VTN − Vin

LN

(

(

)

)

W

WP

k pP Vin − VTP + N k pN Vdd − VTN − Vin

LP

LN

Gon =

(

WN

k pN Vdd − VTN − Vin

LN

(

)

)

Tentando-se estabelecer uma certa simetria no funcionamento da chave complementar, pode-se

forçar a resistência Ron ser constante quando as duas chaves estão em condução. Para isto, basta

igualar a derivada de Gon a zero ou seja,

∂Gon WP

W

k pP − N k p N = 0

=

∂Vin

LP

LN

(4.9)

Esta condição é satisfeita quando

WP

WN

LP

LN

=

k pN

(4.10)

k pP

Desta forma, tem-se para a resistência Ron

Ron =

1

WN

k pN

Vdd − VTN − VTP

LN

(

(4.11)

)

O gráfico de Ron em função de Vin encontra-se na Fig. 4.6.

Rmax =

RN =

RP =

1

WN

k pN

Vdd − VTN − VTP

LN

(

)

1

WN

k pN Vdd − VTN

LN

(

)

1

(

WN

k pN Vdd − VTP

LN

)

Fig. 4.6: Resistência da chave complementar.

A equação 4.10 estabelece a relação geométrica entre os transistores. Sendo k pP < k pN , e

considerando LP = LN , deve-se ter o transistor PMOS mais largo que o NMOS.

Deve-se observar que nesta análise não foi considerado o efeito de corpo. Para um resultado mais

preciso, poderia-se escolher Vdd 2 como sendo o ponto de maior resistência e fazer ∂Gon ∂Vin = 0 em

40

Material não disponível para publicação

Vdd 2 , considerando que VTN e VTP são funções também de Vin . A forma do gráfico de Ron é melhor

representada pela

Fig. 4.7: Gráfico de Ron considerando-se o efeito de corpo.

4.4 Dimensionamento da Resistência da Chave

Em um circuito a capacitores chaveados, deve-se ter em mente o tempo de carregamento e o erro ao

final deste, que um capacitor deve ser submetido. No Sample-Hold da Fig. 4.8, considere Test o tempo

de estabilização máximo com um erro relativo ε .

Vg

S

Vo

Vin

C

Fig. 4.8: Tempo de estabilização da chave.

Assumindo-se que a resistência máxima da chave quando fechada seja Rmax e definindo-se

ε = (Vo − Vin ) Vin , tem-se

t

−

Vo = Vin 1 − e Rmax C

T

− est

Rmax C

Vin 1 − e

ε=

Vin

ε =e

−

Test

Rmax C

− Vin

(4.12)

Ex: Calcular a resistência máxima de uma chave complementar, para um Sample-Hold com carga

capacitiva de 500fF, tempo máximo de estabilização de 2ns e erro relativo menor que 0.1%. O

processo de integração utilizado possui VTN = 0.84V , VTP = −0.73V , k pN = 103µ , k pP = 35.6 µ e

Vdd = 5V .

Da equação 4.12 obtém-se

41

Material não disponível para publicação

2n

−

0.1

= e Rmax 500 f → Rmax = 579Ω

100

A resistência máxima da chave complementar é dada pela equação 4.11, onde obtém-se para a

relação W L do transistor NMOS:

579 =

1

WN

103µ

( 5 − 0.73 − 0.84 )

LN

→

WN

= 4.9

LN

Finalmente, pela equação 4.10 calcula-se a relação W L do transistor PMOS:

WP

LP 103µ

=

4.9

35.6µ

→

WP

= 14.2

LP

Considerando-se comprimento mínimo de canal para os dois transistores, e sendo Lmin = 0.8µ m ,

tem-se WN = 3.9µ m e WP = 11.4µ m .

4.5 Injeção de Cargas

Tomando-se como exemplo o Sample-Hold com chave NMOS da Fig. 4.9, quando esta é cortada,

as cargas negativas acumuladas no canal escoam para as regiões de Dreno e Source. As cargas

introduzidas no capacitor C provocam uma variação de tensão, que se traduz em erro de

armazenamento. Este problema deve ser tratado com muita cautela, pois estes erros podem ser

inadmissíveis em um circuito analógico. A análise deste problema não é trivial, pois a quantidade de

cargas injetadas depende das impedâncias conectadas ao Dreno e ao Source e do tempo de

chaveamento. Este efeito é também conhecido como “clock feedthrough”.

Fig. 4.9: Sample-Hold com chave NMOS.

4.5.1 Caracterização do Problema

Assumindo que Vds = 0 , pode-se considerar que a quantidade de cargas acumuladas no canal é

Qch = −WLCox (Vgs − VT ) = −WLCox (Vdd − Vin − VT )

(4.13)

Lembrando que L e W são o comprimento e a largura efetiva do canal, já descontado o efeito do

undercut, e VT já assume o efeito de corpo, conforme a equação 1.6.

Pode-se dizer também que a quantidade de cargas acumuladas em cada capacitância de

sobreposição Cgsov e Cgdov é

Qov = −WC gsoVgs = −WC gdoVgs = −WCovVgs

42

(4.14)

Material não disponível para publicação

Na maioria das aplicações, é comum que C seja consideravelmente maior que a capacitância total do

Gate ou seja, C C gsov e C WLCox . Isto equivale a dizer que a variação de tensão em C são

pequenas quando comparadas às variações no capacitor de Gate. Para o cálculo das cargas injetadas,

será considerado que a tensão em C é constante. O corte do transistor se dá quando Vg = Vin + VT , e

neste momento o canal se desfaz. O tempo ∆T gasto para cortar o transistor determina a quantidade

de cargas que são injetadas em C, portanto:

Qinj = −αWLCox (Vdd − Vin − VT ) − β WCov (Vdd − Vin − VT )

(4.15)

Onde α e β são constantes que dependem de ∆T . Após este intervalo, Vg continua caindo até

chegar a zero. Entretanto, abaixo de Vdd − Vin − VT só existe Cgsov, pois o canal está desfeito. Em

Vg = Vdd − Vin − VT , a diferença de potencial entre Source e Gate é Vsg = −VT , e quando Vg = 0 tem-se

Vsg = Vin . Portanto, o capacitor Cgsov sofre uma variação de tensão ∆V = Vin + VT , e as cargas

introduzidas em Cgsov são retiradas de C. Neste intervalo, a quantidade de cargas injetadas em C é

Qinj = −WCov (Vin + VT )

(4.16)

O total de cargas injetadas em C pode ser estimado pela soma das equações 4.15 e 4.16 ou seja,

Qinj = −αWLCox (Vdd − Vin − VT ) − β WCov (Vdd − Vin − VT ) − WCov (Vin + VT )

(4.17)

Estudos teóricos e experimentais têm demonstrado que:

1. Para variações muito lentas de Vg (∆T grande) As cargas acumuladas no canal e em Cgsov têm

tempo para caminhar à região de impedância mais baixa. No caso do Dreno estar ligado a uma

fonte de tensão (opamp), tem-se α ≅ 0 e β ≅ 0 , resultando em Qinj = −WCov (Vin + VT ) .

2. Para transições rápidas de Vg, independentemente das terminações de Dreno e Source, metade

das cargas do canal e todas as cargas de Cgsov são injetadas em C. Desta forma, α = 1 2 e

β = 1 , sendo Qinj dada pela equação 4.18. Esta é a situação mais usual, considerada para o

cálculo da injeção de cargas.

1

Qinj = − WLCox (Vdd − Vin − VT ) − WCov (Vdd − Vin − VT ) − WCov (Vin + VT )

2

(4.18)

Uma vez tendo calculado a quantidade de cargas injetadas, pode-se estimar a variação de tensão em

C por:

∆VC =

Qinj

(4.19)

C

Para as chaves PMOS, a análise é idêntica à anterior, mas deve-se ter em mente que as cargas

injetadas são positivas neste caso. Tem-se então que

Qinj = αWLCox (Vin − VT ) + β WCov (Vin − VT ) + WCov (Vdd − Vin + VT

)

(4.20)

Com velocidade de chaveamento elevada tem-se, da mesma forma que na chave NMOS, que

α = 1 2 e β = 1 , e portanto

1

Qinj = WLCox (Vin − VT ) + WCov (Vin − VT ) + WCov (Vdd − Vin + VT

2

)

(4.21)

Ex: No Sample-Hold abaixo, calcular a variação de tensão em C, após o corte da chave. Considere:

Cox = 3 fF µ m 2

VT = 0.84V

43

Material não disponível para publicação

Cov = 0.35 fF µ m

C = 100 fF

LD = 0.2µ m

Vdd = 5V

W = 4µ m

α =1 2

L = 0.8µ m

β =1

Vg

Vo

C=100fF

Vin=2.5V

Solução:

O comprimento efetivo de canal é Lef = ( 0.8 − 0.4 ) µ m = 0.4 µ m , e as cargas injetadas são

calculadas aplicando-se os parâmetros acima na equação 4.18, obtendo-se

Qinj = −10.984 × 10−15 C

Pela equação 4.19 calcula-se a variação de tensão em C como

∆Vo = 109.84µV

4.6 Compensação Para Injeção de Cargas

As variações de tensão nos capacitores de armazenamento podem ser extremamente prejudiciais em

determinados circuitos. A injeção de cargas produz offset de tensão, que pode não ser grave.

Entretanto, conforme mostrado pelas equações 4.18 e 4.20, a quantidade de cargas injetadas dependem

do nível do sinal de entrada Vin e VT, o que inevitavelmente implica em distorção harmônica, podendo

até mesmo inviabilizar um circuito.

Com tudo isto, é fundamental adotar-se estratégias para compensação ou minimização do efeito de

injeção de cargas. Basicamente, os procedimentos usados para este fim são:

1. Uso de transistores dummy.

2. Uso de chaves gêmeas.

3. Uso de chaves complementares.

4. Uso de redes de compensação.

5. Uso de circuitos totalmente diferenciais.

4.6.1 Uso de Transistores Dummy

Este tipo de compensação utiliza um transistor, com área igual à metade da chave, ligado à carga C.

Admitindo que o sinal de controle da chave seja rápido, pode-se considerar α = 1 2 e β = 1 . Desta

forma, pode-se observar na Fig. 4.10 que durante o corte da chave, toda carga injetada pelo canal de

M1 será usada para formar o canal de M2, pois Vg1 e Vg2 são complementares. Isto é verdade somente se

a área do Gate de M2 for metade de M1, pois somente metade das cargas do canal de M1 são expulsas

pelo Source. De forma idealizada, a tensão Vo não sofre modificação, pois nenhuma carga será injetada

em C.

44

Material não disponível para publicação

Fig. 4.10: Compensação com transistor dummy.

Neste tipo de compensação, as tensões VT e as constantes Cox estão casadas. Deve-se tomar o

cuidado de gerar um pequeno atraso no sinal Vg2 em relação a Vg1, para garantir a correta transferência

de cargas.

Os transistores M1 e M2 devem possuir o mesmo L, mas M2 deve ter metade do W de M1. Na

prática, para garantir o melhor casamento entre os transistores, faz-se M1 composto por dois

transistores, de mesmas dimensões de M2, em paralelo.

É importante ter em mente que esta técnica funciona bem enquanto α = 1 2 e β = 1 , o que nem

sempre é verdade.

4.6.2 Uso de Chaves Gêmeas

Em muitas aplicações, os capacitores C são grandes e portanto, necessitam de chaves maiores que

as de dimensões mínimas para comutá-los. Neste caso, é possível empregar-se duas chaves em

paralelo, uma grande (principal) e outra pequena (secundária), com comandos diferentes, conforme

mostrado na Fig. 4.11.

Vgp

Cahve

Principal

Mp

Vo

Vin

C

Ms

Cahve

Secundária

Vgs

Fig. 4.11: Chaves gêmeas.

As duas chaves são ligadas ao mesmo tempo, sendo que a chave primária, por ser maior, é quem

efetivamente carrega o capacitor. Entretanto, a chave principal é cortada primeiro, injetando uma

grande quantidade de cargas no capacitor. Como a chave secundária permanece fechada, as cargas

injetadas são conduzidas à fonte Vin. Quando finalmente a chave secundária é cortada, a quantidade de

cargas injetadas é consideravelmente menor, pois suas dimensões são menores. Portanto, o objetivo da

chave secundária é simplesmente descarregar as cargas injetadas pela principal. O intervalo de tempo

que a chave secundária deve permanecer fechada a mais que a principal é pequeno, mas suficiente para

descarregar as cargas.

45

Material não disponível para publicação

4.6.3 Uso de Chave Complementar

Como as chaves complementares são compostas por transistores NMOS e PMOS, teoricamente é

possível realizar o cancelamento das cargas negativas injetadas pela chave NMOS com as cargas

positivas injetadas pela chave PMOS. A Fig. 4.12 mostra o esquema das chaves e a seqüência de

chaveamento.

Vgn

Mn

Vo

Vdd

Vin

C

Mp

Vgp

Fig. 4.12: Compensação com chave complementar.

Normalmente a fase Vgp, usada para controlar a chave PMOS, é obtida invertendo a fase Vgn. Desta

forma, um pequeno atraso de Vgp em relação a Vgn ocorre. Pode-se observar também que as tensões de

corte de Mn e Mp são diferentes. Isto faz a chave NMOS cortar antes da PMOS, e parte ou toda carga

injetada por Mn é conduzida para Vin por Mp, dificultando o cancelamento da injeção de cargas.

Mesmo que fossem ajustados as dimensões dos transistores e o atraso entre as fases Vgn e Vgp, para

um perfeito cancelamento da injeção de cargas, o mesmo só valeria para uma única tensão Vin. Vale

lembrar que os pontos de corte de Mn e Mp dependem de Vin, e conseqüentemente a quantidade de