ASSOCIAÇÃO EDUCACIONAL DOM BOSCO

FACULDADE DE ENGENHARIA

ENGENHARIA ELÉTRICA ELETRÔNICA

Laboratório de Eletrônica I – 3° Ano de Engenharia

1

Capítulo 2 – Transistores Bipolares (BJT)

CAPÍTULO 3

AMPLIFICADORES TRANSISTORES

EXPERIÊNCIA 2: ESTÁGIOS EM CASCATA DE AMPLIFICADORES E.C.

PROCEDIMENTO:

1.

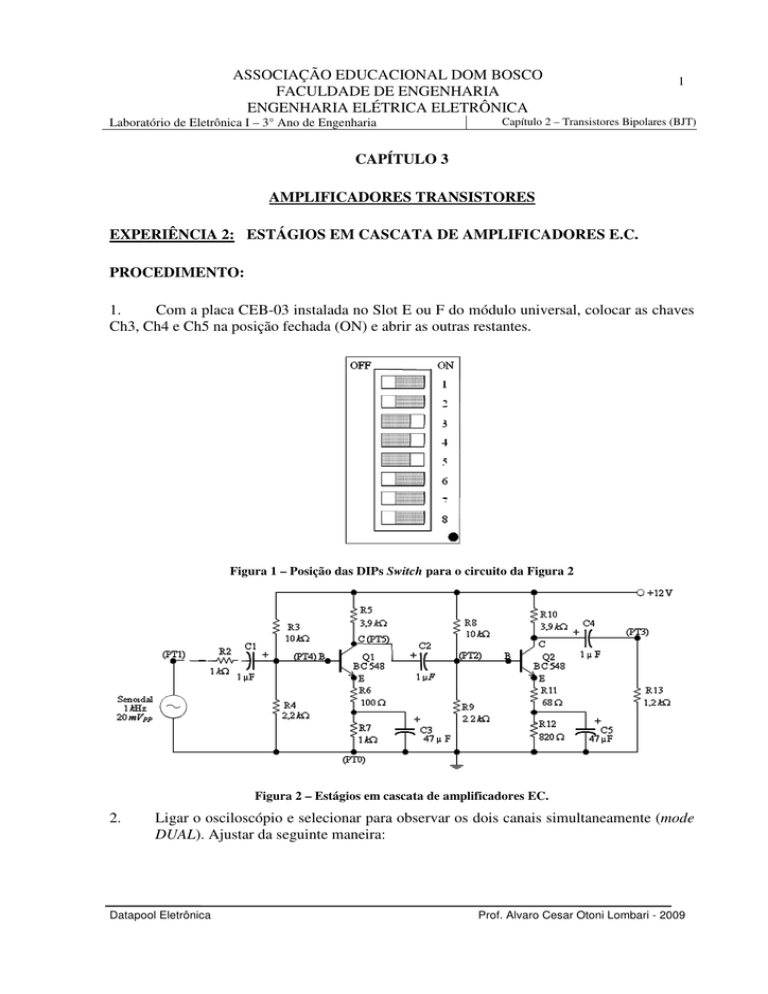

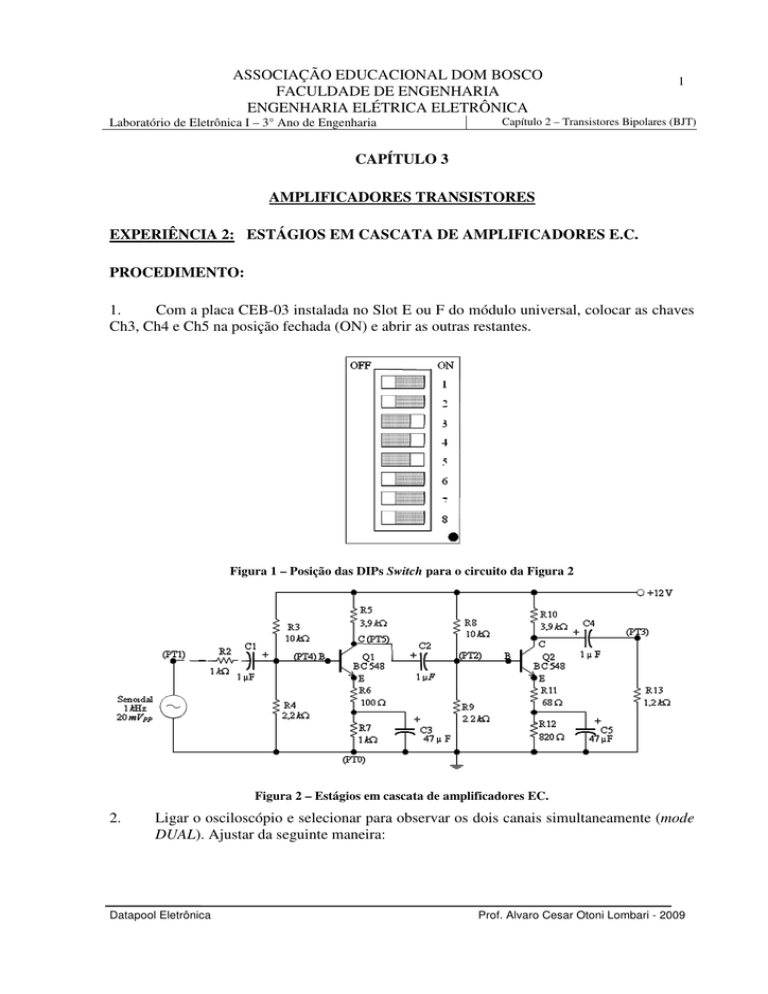

Com a placa CEB-03 instalada no Slot E ou F do módulo universal, colocar as chaves

Ch3, Ch4 e Ch5 na posição fechada (ON) e abrir as outras restantes.

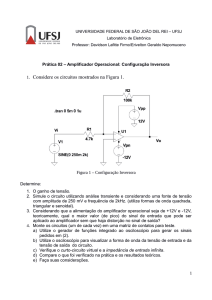

Figura 1 – Posição das DIPs Switch para o circuito da Figura 2

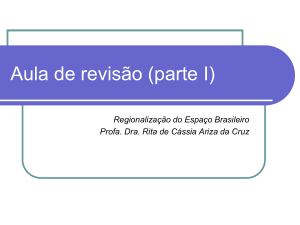

Figura 2 – Estágios em cascata de amplificadores EC.

2.

Ligar o osciloscópio e selecionar para observar os dois canais simultaneamente (mode

DUAL). Ajustar da seguinte maneira:

Datapool Eletrônica

Prof. Alvaro Cesar Otoni Lombari - 2009

ASSOCIAÇÃO EDUCACIONAL DOM BOSCO

FACULDADE DE ENGENHARIA

ENGENHARIA ELÉTRICA ELETRÔNICA

Laboratório de Eletrônica I – 3° Ano de Engenharia

3.

2

Capítulo 2 – Transistores Bipolares (BJT)

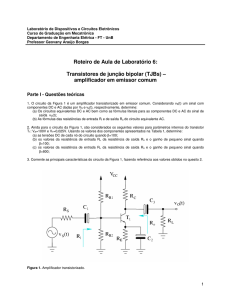

Conectar o gerador de funções na entrada de sinal da placa. O circuito equivalente do

amplificador emissor comum em cascata, para estas condições, está mostrado na

Figura 2

T/Div. = 0,5 ms/Div.

Canal 1:

V/Div. = 5 mV/Div. Acoplamento = AC

Canal 2:

V/Div. = 0.1 V/Div. Acoplamento = AC

4.

Colocar o terra do osciloscópio em PT0 e a ponta de prova (Canal 1) em PT1. Ajustar

o sinal de entrada em torno de 10 mVPP ou para a tensão de entrada que seja suficiente para

ler o máximo de sinal na saída (em PT3) sem distorção e a freqüência de 1 kHz

aproximadamente.

5.

Com o Canal 2, monitorar o sinal de saída de cada estágio. Medir o valor pico a pico

da tensão de saída do primeiro estágio em PT2 (diminuir o ajuste V/Div. para ter a melhor

leitura).

Ventrada = ____________[mV ]

Vsaída 1 = ____________[mV ]

•

AV 1 =

•

Calcular o ganho do primeiro estágio de amplificação.

Vsaida 1

= ____________

Ventrada

Qual o ângulo de defasagem entre a tensão de entrada e saída?

ϕ = _____________[º]

6.

Mudar o Canal 2 em PT3 e observar o sinal de saída do segundo estágio de

amplificação.

Ventrada = ____________[mV ]

Vsaída 2 = ____________[mV ]

•

Calcular o ganho total do amplificador:

Datapool Eletrônica

Prof. Alvaro Cesar Otoni Lombari - 2009

ASSOCIAÇÃO EDUCACIONAL DOM BOSCO

FACULDADE DE ENGENHARIA

ENGENHARIA ELÉTRICA ELETRÔNICA

Laboratório de Eletrônica I – 3° Ano de Engenharia

AV =

•

3

Capítulo 2 – Transistores Bipolares (BJT)

Vsaida 2

= ____________

Ventrada

Qual o ganho do segundo estágio?

AV 2 =

Vsaida 2

= ____________

Vsaida 1

•

Qual o ângulo de defasagem entre a tensão de saída do amplificador de dois estágios,

em relação à entrada?

ϕ = __________ [ 0 ]

EFEITO DA CARGA

7.

Abrir a chave Ch4, isto desliga o acoplamento entre o primeiro e o segundo estágio de

amplificação. Colocar o Canal 2 do osciloscópio no coletor do transistor Q1 (PT5),

correspondente ao 1º estágio de amplificação e observar o sinal em sua saída (mudar a escala

V/div. do Canal 2, para melhorar a visualização do sinal). Conectar novamente a chave Ch4 e

observar que o sinal de saída diminui significativamente.

•

Qual seria a causa desta diminuição de sinal na saída do estágio de amplificação?

___________________________________________________________________________

___________________________________________________________________________

___________________________________________________________________________

8.

Quais modificações deverão ser feitas no circuito da Figura 2, para que os transistores

NPN possam ser substituídos por transistores PNP?

___________________________________________________________________________

___________________________________________________________________________

___________________________________________________________________________

___________________________________________________________________________

___________________________________________________________________________

Datapool Eletrônica

Prof. Alvaro Cesar Otoni Lombari - 2009

ASSOCIAÇÃO EDUCACIONAL DOM BOSCO

FACULDADE DE ENGENHARIA

ENGENHARIA ELÉTRICA ELETRÔNICA

Laboratório de Eletrônica I – 3° Ano de Engenharia

4

Capítulo 2 – Transistores Bipolares (BJT)

DISCUSSÃO

Utilizando a saída do amplificador de um estágio como entrada de outro, pode-se construir um

amplificador de múltiplas etapas, conseguindo-se desta forma um ganho de tensão muito

elevado, com reduzido nível de distorção do sinal.

No amplificador EC em cascata de dois estágios, o sinal de entrada é amplificado no primeiro

transistor, a saída deste estágio é acoplada a outro amplificador EC e, então, o sinal é

amplificado novamente, para conseguir na saída do estágio final um sinal consideravelmente

maior que o sinal da fonte.

Considerando que cada estágio possui uma impedância de entrada e de saída, existe o efeito

de carga para o estágio precedente. Isto provoca uma queda de tensão (diminuição da

amplitude) do sinal de saída. Por esta razão, a amplitude do sinal com carga é sempre menor

do que a amplitude do sinal sem carga.

Como os estágios de amplificadores em emissor comum têm ganho invertido (defasagem de

180º), em dois estágios consecutivos, o sinal resultante de saída está em fase com o sinal de

entrada (defasagem de 360º).

Datapool Eletrônica

Prof. Alvaro Cesar Otoni Lombari - 2009