Introduç

Introdução

• O desempenho de um programa depende:

Organização e Arquitetura

de computadores

– Número de instruções (depende do set de instruções)

– Velocidade de clock (depende da implementação)

– CPI - Número de ciclos gastos por instrução (depende da

implementação do ISA)

• Implementação do MIPS simplificada:

O processador: o caminho de dados e o

controle

– Intruções de referência à memória (lw e sw)

– Instruções lógicas e aritméticas (add, sub, and, or, slt)

– Instruções de controle de fluxo (saltos) beq e j

• lw $t1, offset($t2)

– Load word

– $t1 = valor armazenado na posição de memória $t2 + offset

Prof. Dr. Luciano José Senger

• sw $t1, offset($t2)

– Store word

– posição de memória [$t2 + offset] = $t1

• Beq $t1, $t2, endereço

– Branch if equal (salte se igual)

Introduç

Introdução

Uma sinopse da implementaç

implementação

• Implementação simplificada

• Todas as instruções do conjunto de instruções têm os dois

primeiros passos idênticos:

– Diretrizes:

• Torne o caso comum mais rápido

• A simplicidade favorece a regularidade

– As demais instruções podem ser implementadas com

princípios semelhantes

– A arquitetura do conjunto de instruções influencia os

aspectos de implementação: instruções mais simples

necessitam de uma implementação também mais

simples

• Memória

– Inicialmente as memórias de programa e controle

separadas

Uma visão abstrata da implementaç

implementação do

subconjunto MIPS mostrando as unidades

funcionais principais e as conexões principais

– Enviar o valor armazenado no PC para a memória de programa e

buscar a instrução dessa memória

– Ler um ou dois registradores, usando os campos de instrução para

selecionar os registradores a serem lidos. Para a instrução load

word, precisamos ler apenas um registrador, mas a maioria das

outras instruções exige a leitura de dois registradores

• Mesmo entre diferentes classes de instruções, há algumas

semelhanças:

– Todas as classes utilizam a UAL após a leitura dos registradores:

• Instruções de referência à memória: efetuar o cálculo do endereço

• Instruções aritméticas e lógicas: efetuar a operação

• Desvios condicionais: efetuar comparação (subtração)

• Após usar a UAL, as ações necessárias diferem

– Referência a memória: escreve dado na memória

– Instrução aritmética: escreve dado no registrador

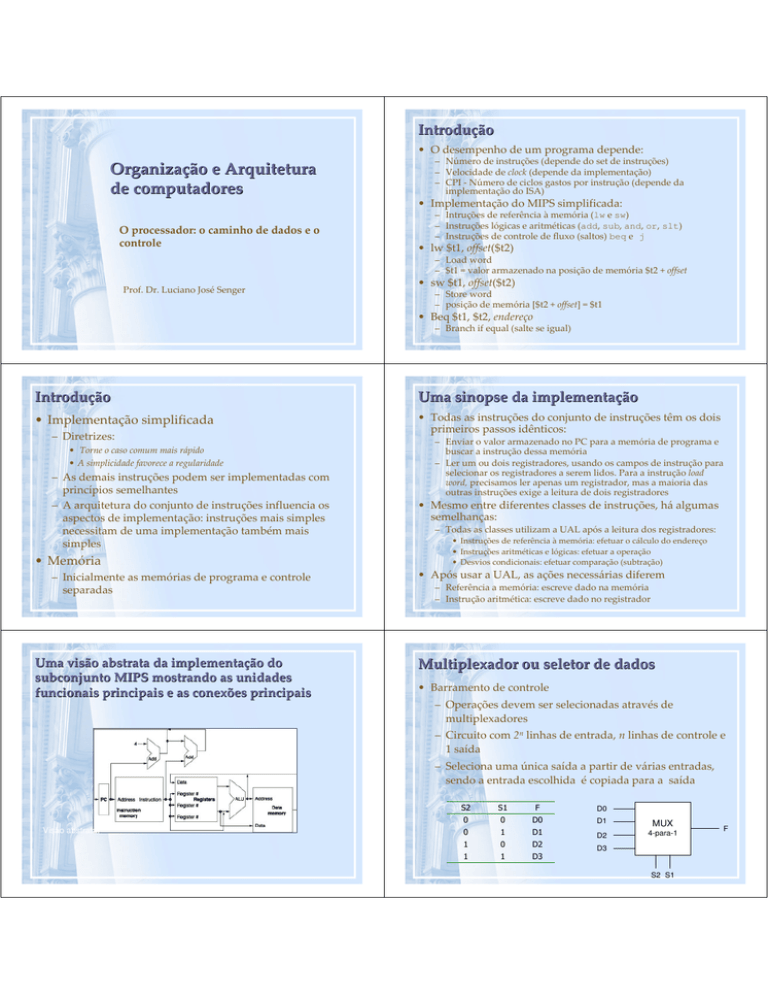

Multiplexador ou seletor de dados

• Barramento de controle

– Operações devem ser selecionadas através de

multiplexadores

– Circuito com 2n linhas de entrada, n linhas de controle e

1 saída

– Seleciona uma única saída a partir de várias entradas,

sendo a entrada escolhida é copiada para a saída

Visão abstrata:

S2

S1

F

D0

0

0

D0

D1

MUX

0

1

D1

D2

4-para-1

1

0

D2

1

1

D3

D3

S2 S1

F

A implementaç

implementação bá

básica do subconjunto MIPS

incluindo as linhas de controle e os multiplexadores

necessá

necessários

Método de temporizaç

temporização (clocking)

clocking)

• Clocking

– Define quando os sinais podem ser lidos e quando

podem ser escritos

– Evita circunstâncias onde um sinal é lido ao mesmo

tempo que o mesmo sinal foi escrito; a leitura pode

retornar o valor antigo, o valor recente ou uma

combinação entre os dois

• Sincronização acionada por transição

Visão abstrata:

A ló

lógica combinacional, os elementos de estado e o

clock relacionados

• Em um sistema digital síncrono, o clock determina quando os

elementos de estado escreverão valores no armazenamento interno.

Todos os elementos que apresentam um estado, como a memória, são

considerados acionados por transição

– Significa que quaisquer valores armazenados em um

elemento lógico seqüencial são atualizados apenas em

uma transição de clock

– Como apenas os elementos de estado podem armazenar

valores de dados, qualquer coleção de lógica

combinatória precisa ter suas entradas vindo de um

conjunto de elementos de estado e suas saídas escritas

em um conjunto de elementos de estado

Construindo o caminho de dados

• Elementos principais do caminho de dados

– PC, memória de instruções e somador

• O método acionado por transição permite que um elemento de estado

seja lido e escrito no mesmo ciclo de clock sem criar uma disputa que

poderia levar a valores de dados indeterminados. O período de clock

necessita ser longo o suficiente para que os valores de saída

estabilizem

Construindo o caminho de dados

• Banco de registradores

– Devido às instruções de formato R terem três operandos de registrador,

precisamos ler duas words de dados do banco de registradores e escrever

uma word de dados no banco de registradores.

– 3 entradas de 5 bits (32 registradores):

• 2 entradas com endereço dos registradores lidos

• 1 entrada com endereço do registrador escrito

– 2 saídas de 32 bits: operandos p/ a UAL

– 1 entrada de 32 bits: escrita do resultado

• As escritas são controladas pelo sinal de controle de escrita, que precisa estar

ativo para que um escrita ocorra na transição do clock

Construindo o caminho de dados

• Instruções do formato R

– Executa a operação (op and funct) utilizando como

operandos os valores em rs e rt

– Armazenam o resultado no banco de registradores (no

endereço rd)

– Todas as intruções do tipo R precisam

• Ler dois registradores

• Realizar uma operação na UAL com os conteúdos dos

registradores

• Escrever o resultado em um registrador

• Instruções aritméticas lógicas: ADD, SUB, AND, OR

• Ex: add $t1, $t2, $t3

31

R-type: op

25

rs

20

15

rt

rd

10

5

shamt funct

0

Construindo o caminho de dados

Construindo o caminho de dados

• Instruções de load/store

• A instrução beq

– lw $t1, offset($t2) e sw $t1, offset($t2)

– Calculam um endereço de memória somando o registrador base

($t2 no exemplo) ao número de 16 bits sem sinal estendido

– Para sw, o valor a ser armazenado na memória de dados é lido do

registrador; para lw: o valor é lido da memória de dados e escrito

no registrador

– É necessária uma unidade para estender o sinal de 16 para 32 bits e

uma memória para ler e escrever os dados

– Tem três operandos

• Dois registradores utilizados para a comparação

• Offset indicando o endereço de memória para o deslocamento

(PC + offset)

– Instruções de desvio

• O conjunto de instruções especifica que a base para o cálculo do

endereço de desvio é o endereço da instrução seguinte ao

desvio. Como calculamos PC + 4 no caminho de dados para a

busca de instruções, é fácil usar esse valor como a base para

calcular o endereço de destino do desvio.

• A arquitetura é especificada de forma que o campo offset é

deslocado 2 bits para a esquerda de modo que seja uma offset

de uma word; essa forma de cálculo aumenta a amplitude do

salto por um fator igual a 4

Construindo o caminho de dados

Construindo o caminho de dados

• A instrução beq

• Operações lógicas e de acesso à memória

– Além de calcular o endereço do desvio, é necessário verificar se o

desvio deve ser executado ou não, de acordo com a comparação

entre os dois registradores

– Assim, o caminho de dados do desvio precisa de duas operações:

• Calcular o endereço de destino do desvio

• Comparar o conteúdo do registrador (sinal zero da UAL)

– Semelhantes, com as diferenças principais:

• As instruções lógicas e aritméticas usam a ALU com as entradas

vindas de dois registradores; as instruções de acesso à memória

também podem usar a ALU para fazer o cálculo do endereço, embora

a segunda entrada seja o campo offset de 16 bits com o sinal estendido

da instrução

• O valor armazenado em um registrador de destino vem da ALU (para

um instrução do tipo R) ou da memória (para um load)

Construindo o caminho de dados

Um esquema de implementaç

implementação simples

• Integrando os caminhos de dados

• Projeto de ciclo único: a busca, decodificação e execução

das instruções ocorre em um único ciclo de clock

– Os caminhos de dados são unidos e linhas de controle são

adicionadas, assim como os multiplexadores necessários

– Nenhum recurso do caminho de dados pode ser usados mais de

uma vez por instrução, de forma que aqueles que necessitam ser

utilizados mais de uma vez devem ser replicados (p.e. memória de

instruções e de dados separados, mais de um somador)

– multiplexadores nsão necessários na entrada dos componentes

compartilhados para realizar a seleção

– Sinais de escrita para controlar a gravação no banco de

registradores e na memória de dados

• O tempo de ciclo é determinado pelo tamanho do caminho

mais longo (caminho com maior tempo de execução)

Um esquema de implementaç

implementação simples

Um esquema de implementaç

implementação simples

• Acrescentando o controle

• Acrescentando o controle

– O controle da ALU

– O controle de ALU

• Dependendo da instrução, uma das operações abaixo deverá

ser executada

• Aritméticas e lógicas (and, or, sub, add, slt)

• Load/store (add para cálculo do endereço)

• BEQ (subtração)

Entrada de controle da UAL

Função

0000

AND

0001

OR

0010

Soma

0110

Subtração

0111

Set less than

• Podemos gerar a entrada do controle da ALU de 4 bits usando

uma pequena unidade de controle que tenha como entradas o

campo funct da instrução e um campo control de 2 bits, que

chamamos de OpALU.

• OpALU indica:

– 00 : add para load/stores

– 01: sub para beq

– 10: determinada pela operação do campo funct

Um esquema de implementaç

implementação simples

Um esquema de implementaç

implementação simples

• Controle da ALU

• Controle da ALU

– Criar 2 bits de controle, que juntamente com o campo funct,

definem a função.

– Entradas UALOp1 e UALOp2:

– A partir dos valores de entrada e saída, pode-se criar

um sistema que mapeie o subconjunto de valores

possíveis para uma saída correta de controle para a

ALU

– Tabela verdade reduzida

• 00: loads e stores (soma endereços)

• 01: beq

• 10: a função é determinada pelo campo de função

Código de

operação da

instrução

UALOp

Operação da

Instrução

Campo

funct

Ação da ALU

desejada

Entrada de

controle da

ALU

LW

00

load word

XXXXXX

soma

0010

SW

00

store word

XXXXXX

soma

0010

BEQ

01

branch equal

XXXXXX

subtração

0110

Tipo R

10

add

100000

soma

0010

Tipo R

10

subtract

100010

subtração

0110

Tipo R

10

AND

100100

and

0000

Tipo R

10

OR

100101

or

0001

Tipo R

10

set less than

101010

set less than

0111

Campo funct

OpALU

Operação

OpALU1

OpALU2

F5

F4

F3

F2

F1

F0

0

0

X

X

X

X

X

X

0010

X

1

X

X

X

X

X

X

0110

1

X

X

X

0

0

0

0

0010

1

X

X

X

0

0

1

0

0110

1

X

X

X

0

1

0

0

0000

1

X

X

X

0

1

0

1

0001

1

X

X

X

1

0

1

0

0111

Um esquema de implementaç

implementação simples

Um esquema de implementaç

implementação simples

• Projetando a unidade de controle principal

• O caminho de dados com todos os

multiplexadores necessários e todas as linhas de

controle identificadas

– Formatos de instrução considerados

•

•

•

•

•

op

rs

rt

rd

shamt

funct

31-26

25-21

20-16

15-11

10-6

5-0

op

rs

rt

endereço

31-26

25-21

20-16

15-0

op

rs

rt

endereço

31-26

25-21

20-16

15-0

R

LW/SW

BEQ

Campo de opcode (bits 31-26)

Os dois registradores a serem lidos (rs e rt): posições 25-21 e 20-16 (tipo R, BEQ e store

word)

Registrador-base para instruções de load e store: está na posição 25-21 (rs)

16 bits de deslocamento do BE, lw e sw: 15-0

Registrador destino:

– Para lw: 20-16 (rt)

– Tipo R: 15-12 (rd)

– É necessário um multiplexador antes do banco de registradores

Um esquema de implementaç

implementação simples

Um esquema de implementaç

implementação simples

• Descrição dos sinais da unidade de controle

• Unidade de controle principal

– Os sinais podem ser definidos com base no campo

opcode, com exceção da linha de controle OrigPC

– Essa linha de controle dever ser ativada se a instrução

for beq e a ALU produzir o sinal Zero, usado para

comparação de igualdade

Instrução

RegDst

UALFonte

MemParaReg

EscReg

LerMem

EscMe

m

Branch

ALUOp1

ALUOp2

formato

R

1

0

0

1

0

0

0

1

0

lw

0

1

1

1

1

0

0

0

0

sw

X

1

X

0

0

1

0

0

0

beq

X

0

X

0

0

0

1

0

1

Um esquema de implementaç

implementação simples

Um esquema de implementaç

implementação simples

• Unidade de controle principal

• Exemplo 1: Add $t1, $t2, $t3

–

Passos para a execução de instruções R

1. Busca da instrução na memória de instruções e

incremento do PC

2. Dois registradores, $t0 e $t1, são lidos do banco de

registradores. A unidade de controle coloca valores

nas linhas de controle

3. A UAL opera sobre os dados lidos do banco de

registradores, usando o código da função (bits 5-0)

para gerar a função da UAL

4. O resultado da UAL é escrito no banco de

registradores usando-se os bits 15-11 da instrução

para selecionar o registrador-destino ($t1)

Um esquema de implementaç

implementação simples

Um esquema de implementaç

implementação simples

• Unidade de controle principal

• Exemplo 2: lw $t1, offset ($t2)

–

Passos para a execução de instruções LW/SW

1. Busca da instrução na memória de instruções e

incremento do PC

2. Leitura do conteúdo de um registrador ($t2) do

banco de registradores

3. Cálculo da soma do valor lido do banco de

registradores com o resultado da extensão do sinal

de 16 bits menos significativos da instrução

(deslocamento)

4. O resultado da soma é usado para endereçar a

memória de dados

5. O dado vindo da unidade de memória é escrito no

banco de registradores; o número do registradordestino é dado pelos bits 20-16 da instrução ($t1)

Um esquema de implementaç

implementação simples

Um esquema de implementaç

implementação simples

• Unidade de controle principal

• Exemplo 3: beq $t1, $t2, offset

–

Passos para execução de instruções BEQ

1. Busca da instrução na memória de instruções e

incremento do PC

2. Leitura do conteúdo dos registradores $t1 e $t2

3. Realização de uma subtração pela ALU sobre os

dois valores lidos do bando de registradores. O

valor de PC+4 é somado ao resultado da extensão

do sinal dos 16 bits menos significativos da

instrução (deslocamento) deslocado de dois bits à

esquerda. O resultado dessa soma é o endereço de

destino do desvio

4. A saída, Zero da ALU é usada para decidir se o PC

deve ser atualizado com o valor de PC+4 ou com o

valor do endereço de destino do desvio condicional

Um esquema de implementaç

implementação simples

Um esquema de implementaç

implementação simples

• Implementando jumps

• Implementando jumps

– A instrução jump se parece um pouco com uma

instrução branch, mas calcula o PC de destino de

maneira diferente e não é condicional

– Como um branch, os 2 bits menos significativos são

sempre 00; os próximos 26 bits mais significativos vem

do campo de 26 bits imediato da instrução

– Assim, pode-se implementar um jump armazenando no

PC a concatenação dos

• 4 bits superiores do PC atual + 4 (esses são bits 31:28 do

endereço da instrução imediatamente seguinte)

• O campo de 26 bits imediato da instrução jump

• Os bits 00

Um esquema de implementaç

implementação simples

Desempenho das má

máquinas de ciclo único

• Implementação de ciclo único

• Suponha os seguintes tempos de operação

– O projeto de ciclo único é ineficiente

– O clock precisa ter a mesma duração para cada instrução

nesse projeto e o CPI será sempre 1

– O tempo de ciclo é determinado pelo caminho mais

longo; esse caminho, certamente, é uma instrução lw,

que usa cinco unidades funcionais em série:

–

–

–

–

–

Memória de instruções

Banco de registradores

ALU

Memória de dados

Banco de registradores

– Embora o CPI seja 1, o desempenho geral de uma

implementação de ciclo único provavelmente não será

bom, já que outras instruções poderiam ficar em um

ciclo de clock mais simples

–

–

–

–

Unidade de memória: 200 ps

ALU e somadores: 100 ps

Banco de registradores: 50 ps

Considerando que os multiplexadores, a unidade de

controle, os acessos do PC, a unidade de extensão do

sinal e os fios não possuem atraso, qual das seguintes

implementações seria mais rápida e por quanto?

• Uma implementação em que toda instrução opera em 1 ciclo de

clock de uma duração fixa

• Uma implementação em que toda instrução é executada em 1

ciclo de clock usando um ciclo de clock com duração variável,

que para cada instrução, tem apenas a duração necessária

(método não prático)

Desempenho de má

máquinas de ciclo único

Desempenho de má

máquinas de ciclo único

• Solução

• Tempo exigido para cada classe de instruções

– Considerando o mix: 25% loads, 10% stores, 45% ALU,

15% desvios, 5% jumps

– Tempo de execução = Contagem instruções x CPI x Tempo de

ciclo

– Tempo de execução = Contagem instruções x 1 x Tempo de ciclo

– Tempo de execução = Contagem instruções x Tempo de ciclo

– Caminhos críticos

Desempenho de má

máquinas de ciclo único

Desempenho de má

máquinas de ciclo único

• Ciclo de clock

• Ciclo único

– determinado pela instrução mais longa, que leva 600ps

para ser executada:

Uma implementaç

implementação multiciclo

Uma implementaç

implementação multiciclo

• A visão de alto nível do caminho de dados multiciclo

• Problema da máquina de ciclo único

Cycle 1

Cycle 2

Clk

lw

– Como precisamos considerar que o ciclo de clock é

igual ao atraso de pior caso para todas instruções, não

podemos usar técnicas de implementação que reduzem

o atraso do caso comum: violação dos princípios de

projeto

– Na implementação de ciclo único, cada unidade

funcional precisa ser duplicada, o que eleva o custo de

implementação: o projeto de ciclo único é ineficiente no

desempenho e no custo

– Solução: utilizar uma implementação multiciclo, de

forma que as instruções possam utilizar mais de um

ciclo de clock para serem executadas, dependendo de

sua complexidade.

sw

Waste

• Na implementação multiciclo:

– Cada fase de execução da instrução em um ciclo

– Unidades funcionais podem ser compartilhadas, isto é, usadas

mais de uma vez por instrução

– Redução da quantidade de hardware necessário

• Principais vantagens do multiciclo:

– Instruções são executadas em quantidades diferentes de períodos

de clock (caso comum pode ser melhorado)

– Capacidade de compartilhar unidades funcionais (redução de

custo)

– Memória e ALU únicas

– Registradores RI e MDR (os dois valores são necessários no mesmo

ciclo de clock)

– Registradores A e B para armazenar os valores lidos no banco de

registradores (assim mais de uma leitura é possível por execução

de instrução)

– O registrador SaidaALU armazena a saída da ALU

Uma implementaç

implementação multiciclo

Uma implementaç

implementação multiciclo

• A visão de alto nível do caminho de dados multiciclo

• O caminho de dados multiciclo para o MIPS

manipular instruções básicas

– Como várias unidades funcionais são compartilhadas para

diferentes finalidades, multiplexadores adicionais devem ser

incluídos e os multiplexadores existentes devem ser expandidos

– A substituição das três ALUs do caminho de dados de ciclo único

por uma única ALU significa que esta precisa acomodar todas as

entradas que, antes, iam para as três ALUs diferentes:

• Um multiplexador adicional é incluído para a primeira entrada

da ALU, para escolher entre os registrador A e o PC

• O multiplexador na segunda entrada da ALU muda de duas

para quatro entradas: as duas entradas adicionais para o

multiplexador são a constante 4 (usada para incrementar o PC)

e o campo offset com sinal estendido e deslocado (usado no

cálculo do endereço do desvio)

Uma implementaç

implementação multiciclo

Uma implementaç

implementação multiciclo

• Unidade de controle principal

• O caminho de dados multiciclo com as linhas de

controle indicadas

– Implementação multiciclo exige um conjunto diferente de sinais de

controle:

•

•

•

•

•

PC, a memória, os registradores e o IR: sinal de escrita

Memória: sinal de leitura

UAL: mesmo controle da implementação monociclo

Multiplexador de 4 entradas: 2 linhas de controle

Todos os demais multiplexadores: uma linha de controle

– Para instruções jump e branch equal existem três fontes possíveis

para o PC:

• PC+4

• SaidaALU (desvio condicional)

• 26 últimos bits do IR acrescido de 2 zeros à direita, e concatenados

com os 4 MSB’s do PC

– Controle de escrita do PC:

• No incremento normal, e em um deslocamento incondicional, o PC é

escrito incondicionalmente

• Se for um desvio condicional, passa o valor de UALSaída, somente se

os registradores forem iguais

• Dois sinais de escrita: PCEsc e PCEscCond

Uma implementaç

implementação multiciclo

Uma implementaç

implementação multiciclo

• Unidade de controle principal

• Unidade de controle principal

– Ações dos sinais de controle de 1 bit:

– Ações dos sinais de controle de 1 bit:

– RegDst

– MemParaReg

• Inativo → O número do registrador-destino no banco de registradores vem do

campo rt

• Ativo → O número do registrador-destino no banco de registradores vem do

campo rd

– EscreveReg

• Inativo → Nenhum

• Ativo → O registrador de propósito geral selecionado pelo número do

registrador de escrita é atualizado com o valor da entrada Dado de Escrita

– OrigAALU

• Inativo → O primeiro operando da UAL é o PC

• Ativo → O primeiro operando da UAL vem do registrador A

– LerMem

• Inativo → Nenhum

• Ativo → O conteúdo da memória no endereço especificado na entrada

Endereço é colocado na saída Dado de saída

– EscreveMem

• Inativo → Nenhum

• Ativo → O conteúdo da memória no endereço especificado na entrada

Endereço é substituído pelo valor na entrada Dado a ser Escrito

• Inativo → O valor colocado na entrada Dado a ser Escrito do banco de

registradores vem de SaidaALU

• Ativo → O valor na entrada Dado a ser Escrito do banco de registradores do

MDR

– louD

• Inativo → O PC é usado para fornecer o endereço da unidade de memória

• Ativo → SaidaALU é usada para fornecer o endereço para a unidade de

memória

– IRWrite

• Inativo → Nenhum

• Ativo → A saída da unidade de memória é escrita no IR

– EscrevePC

• Inativo → Nenhum

• Ativo → O PC é atualizado. A fonte é controlada pelo sinal OrigPC

– EscrevePCCond

• Inativo → Nenhum

• Ativo → O PC é atualizado se a saída Zero da ALU também estiver ativa

Uma implementaç

implementação multiciclo

• Unidade de controle principal

– Ações dos sinais de controle de 2 bits:

– OpALU

Uma implementaç

implementação multiciclo

• Caminho de dados completo para a

implementação multiciclo juntamente com as

linhas de controle necessárias

• 00 – A UAL efetua uma operação de soma

• 01 – A UAL efetua uma operação de subtração

• 10 – O campo função da instrução determina a operação da UAL

– OrigBALU

• 00 – A segunda entrada da UAL vem do registrador B

• 01 – A segunda entrada da UAL é a constante 4

• 10 – A segunda entrada da UAL é a extensão de sinal dos 16 bits menos

significativos do IR

• 11 – A segunda entrada da UAL é a extensão de sinal dos 16 bits menos

significativos do IR deslocados 2 bits à esquerda

– OrigPC

• 00 – A saída da UAL (PC+4) é enviada ao PC para atualizar seu valor

• 01 – O conteúdo do UALSaída (o endereço-alvo do desvio condicional) é

enviado ao PC para atualizar seu valor

• 10 – O endereço-alvo do desvio condicional (IR[25-0]), deslocado 2 bits à

esquerda e concatenado com PC+4[31-28] é enviado ao PC para atualizar seu

valor

Uma implementaç

implementação multiciclo

Uma implementaç

implementação multiciclo

• Dividindo a execução da instrução em ciclos de

clock

• Dividindo a execução da instrução em ciclos de

– Ao organizar a execução em mais de um ciclo de clock

pode-se balancear a quantidade de trabalho realizada

em cada ciclo

– A organização da execução de cada instrução segue um

número de etapas, que depende do tipo da instrução

• As etapas deve ser realizadas de forma que cada passo

contenha apenas uma operação de ALU, um acesso à memória

ou um acesso ao banco de registradores

• Com essa restrição, o ciclo de clock pode ser tão curto quanto a

mais longa dessas operações

– Os registradores (p.e. A, B, MDR, SaidaALU)

armazenam dados para os próximos ciclos da mesma

instrução

clock

1. Busca da instrução

2. Decodificação da instrução e busca dos registradores

3. Execução, cálculo do endereço de memória ou

conclusão do desvio

4. Acesso à memória ou conclusão de instrução tipo R

5. Conclusão de leitura de memória

Uma implementaç

implementação multiciclo

Uma implementaç

implementação multiciclo

•

• Dividindo a execução da instrução em

ciclos de clock

Dividindo a execução da instrução em ciclos de clock

1.

Busca da instrução

•

•

•

2.

IR=Memória[PC]

PC=PC+4

Envio do PC para a memória como endereço, realização da leitura e

escrita da instrução no registrador de instruções.

Decodificação e busca dos registradores

•

•

•

•

•

•

Operações que podem depois ser descartadas após a decodificação

da instrução (ainda não se sabe qual instrução está no IR)

São executadas para evitar a perda de tempo durante a execução (por

exemplo ler rs e rt)

Carga dos registradores de entrada da ALU e do endereço de desvio

condicional (salvo em SaidaALU)

A = Reg[IR[25-21]];

B = Reg[IR[20-16]];

SaidaALU = PC + extensão de sinal (IR[15-0] << 2);

3. Execução, cálculo do endereço de memória ou

conclusão do desvio

a) Referência à memória

– SaidaALU = A + extensão de sinal IR[15-0]

b) Instrução aritmética ou lógica (tipo R)

– SaidaALU = A op B

c) Desvio condicional

– Se (A == B) PC = SaidaALU

d) Desvio incondicional

– PC = PC [31-28] || (IR[25-0]<<2

Uma implementaç

implementação multiciclo

Uma implementaç

implementação multiciclo

• Dividindo a execução da instrução em

ciclos de clock

4. Etapa de acesso à memória ou conclusão de

instrução tipo R

a) Referência à memória

MDR = Memória [SaidaALU];

ou

Memória [SaidaALU] = B;

b) Instruções aritméticas ou lógicas (tipo R)

Reg[IR[15-11]] = UALSaída;

5. Etapa de conclusão de acesso à memória (lw)

• Reg[IR[20-16]] = MDR

Definindo o controle

Definindo o controle

• Controle da implementação multiciclo pode ser

realizado

• O controle da máquina

de estados finitos

completo para o caminho

de dados

– Máquina de estados finitos (MEF)

– Microprogramação

• Máquina de estados finitos

– Visão de alto nível

Definindo o controle

• Os controles da máquina de estados finitos

normalmente são implementados usando um

bloco de lógica combinacional e um registrador

para conter o estado atual

Desempenho da implementaç

implementação multiciclo

Single Cycle Implementation:

Cycle 1

Cycle 2

Clk

lw

sw

Multiple Cycle Implementation:

Clk

Waste

multicycle clock

slower than 1/5th of

single cycle clock

due to state register

overhead

Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 Cycle 6 Cycle 7 Cycle 8 Cycle 9Cycle 10

lw

IFetch

sw

Dec

Exec

Mem

WB

IFetch

R-type

Dec

Exec

Mem

IFetch

Controle de Exceç

Exceções

Controle de Exceç

Exceções

• Controle

• Como as exceções são tratadas

– Partes difíceis do controle é implementar exceções e interrupções, eventos

diferentes de desvios que mudam o fluxo de execução das instruções

– Exceção: evento inesperado de dentro do processador

• Exemplo: overflow aritmético

– Interrupção: evento que causa uma mudança inesperada no fluxo de

execução mas vem de fora do processador

• Frequentemente, exceções também são chamadas de interrupções (IA-32)

Tipo de evento

Origem

Terminologia MIPS

Requisição de dispositivo

de E/S

Externa

Interrupção

Chamada ao sistema

operacional pelo programa

do usuário

Interna

Exceção

Overflow aritmético

Interna

Exceção

Uso de uma instrução não

definida

Interna

Exceção

Mal funcionamento do

hardware

Ambas

Exceção ou interrupção

– A ação básica que a máquina precisa realizar quando ocorre uma

exceção é salvar o endereço da instrução problemática no contador

de programa para exceções (EPC) e transferir o controle para o

sistema operacional em alguns endereços especificados

– O sistema operacional pode então tomar uma ação apropriada, que

pode envolver fornecer algum serviço ao programa do usuário,

tomar alguma ação predefinida em resposta a um overflow ou

interromper a execução do programa e retornar um erro

– Depois de realizar qualquer ação necessária devido à exceção, o

sistema operacional pode terminar o programa ou continuar sua

execução usando o EPC para determinar onde reiniciar a execução

do programa

– O motivo da exceção e a instrução que a causou devem ser

informados ao sistema operacional

• Registrador de status

• Interrupções vetorizadas (o sistema operacional sabe a causa da

exceção pelo endereço que ela foi tratada)

Mapeando o controle em hardware

Microprogramaç

Microprogramação

• Função de controle

• Projeto de controle com máquinas de estados

– Os sinais de controle são dependentes de:

• Que instrução está sendo executada

• Que passo está sendo realizada

– Usar as informações acumuladas para especificar uma

máquina de estado finito

• Especificar uma máquina de estado finito graficamente, ou

• usar microprogramação

– Adequado em processadores com um número de

estados moderado

– No caso de conjunto de instruções mais complexo,

torna-se difícil implementar o controle através de

máquinas de estado

• Muitos estados e muitas transições são necessárias, dependo do

conjunto de instruções e do número de ciclos de clock por

instrução

• Projeto do controle por microprogramação

– Cada microinstrução define o conjunto de sinais de

controle que são aplicados no caminho de dados

– Sequenciamento:

• Execução sequencial é a padrão (sequenciador)

• Subrotinas podem ser implementadas

Microprogramaç

Microprogramação

Microprogramaç

Microprogramação

• Projeto do controle por microprogramação

• Formato de uma microinstrução para o MIPS

– Idéia básica: representar simbolicamente os valores

ativos das linhas de controle, de modo que o

microprograma seja uma representação das

microinstruções

• Formato de uma Microinstrução

– Define quantos campos e quais sinais de controle são

afetados por cada campo

– Deve-se simplificar a representação (se possível) e

dificultar a escrita de microinstruções inconsistentes

– Para se obter as microinstruções, devem ser observadas

os sinais de controle no caminho de dados

– Os sinais que não estão ativos ao mesmo tempo

compartilham o mesmo campo

Microprogramaç

Microprogramação

Microprogramaç

Microprogramação

• Implementação do microprograma

• Implementação do microprograma

– as microinstruções são armazenadas em uma ROM ou uma PLA

– Assim, cada microinstrução tem um endereço (endereços são

sequenciais)

• Métodos para escolha da próxima microinstrução a ser

executada:

1. Incrementar o endereço da microinstrução corrente (indicado por

“seq”)

2. Desviar para a microinstrução que começa a execução da próxima

instrução (indicada por “Busca”, corresponde ao estado 0 da

versão FSM)

3. Escolher a próxima microinstrução com base na entrada do bloco

de controle (indicada por “despacho”)

– São necessárias duas tabelas de despacho:

• Uma para despachar a partir do estado 1

• Uma para despachar a partir do estado 2

• Formato de microinstrução (I)

• Em geral, as operação de “despacho” são implementadas a

partir de uma tabela que

–

–

–

–

Contém os endereços das microinstruções-alvo

indexada pela entrada do bloco do controle

pode ser implementada em uma ROM ou uma PLA

Podem existir diversas tabelas de “despacho”

Microprogramaç

Microprogramação

Microprogramaç

Microprogramação

• Formato de microinstrução (II)

• Implementação do microprograma

– Busca da Instrução, incremento do PC (PC+4),

decodificação e cálculo do endereço-alvo (beq)

Microprogramaç

Microprogramação

Microprogramaç

Microprogramação

• Implementação do microprograma

• Despacho 1

– Busca da Instrução, incremento do PC (PC+4), decodificação e

cálculo do endereço-alvo (beq)

– Despacho

• Analogia com uma instrução case ou switch com o campo opcode e a

tabela de despacho 1 usada para selecionar uma de quatro sequências

de microinstruções diferentes

–

–

–

–

Mem1 para instruções de acesso a memória

Rformat1 para instruções do tipo R

BEQ1 para a instrução branch on equal

JUMP1 para a instrução jump

Microprogramaç

Microprogramação

Microprogramaç

Microprogramação

• Implementação do microprograma

• Implementação do microprograma

– Execução de LW/SW

– Tipo R

Microprogramaç

Microprogramação

Microprogramaç

Microprogramação

• Implementação do microprograma

• Microprograma completo

– Tipo R

Microprogramaç

Microprogramação

Microprogramaç

Microprogramação

• Implementação do microprograma

• Implementação

Microprogramaç

Microprogramação

Leituras recomendadas

• Vantagens:

Patterson, David A. e Hennessy, John L.

Organização e Projeto de Computadores: A

Interface Hardware/Software. Ed. LTC, 802. Ed.,

2004, Rio de Janeiro.

– Facilidade no projeto

– flexiblidade:

• Adaptável as mudanças na organização, temporização e tecnologia

• Pode ser modificada no final do ciclo de projeto ou mesmo em campo

– Pode implementar conjuntos de instruções bastante complexos:

apenas mais memória de microcontrole é necessária

– Generalidade:

• Pode implementar vários conjuntos de instruções na mesma máquina

• Pode ajustar o conjunto de instruções a aplicação

– Compatibilidade: muitas organizações, mesmo conjunto de

instruções

• Desvantagens

– Geralmente mais lento que o controle por máquinas de estados

– Atualmente, microprograma é armazenado internamente no CI

• Processadores modernos: hardwired para instruções

simples e microprograma para instruções complexas

(Pentium 4)