Processadores – Aula 3

Professor: André Luis Meneses Silva

E-mail/msn: [email protected]

Página: www.dcomp.ufs.br/index.php/docentes:Andre

Agenda

Introdução

Implementação Multiciclo

Etapas de uma instrução MIPS

Definindo o Controle

Implementação de uma máquina de estados

finitos.

Máquina de Moore

Exceções

Como as Exceções são Tratadas

Implementação Multiciclo

Podemos elaborar uma implementação cujo

tempo de execução das instruções apresente

variações a depender do tipo de instrução a

ser executado.

Este tipo de implementação é denominado de

Implementação Multiciclo.

Implementação Multiciclo

Algumas características:

Cada etapa (passo) na execução de uma instrução

levará 1 ciclo de clock.

Uma unidade funcional pode ser compartilhada, ou

seja, uma instrução pode utilizá-la mais de uma vez.

Devido a isso, alguns elementos de hardware podem

ser eliminados.

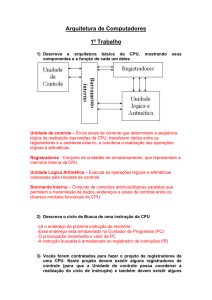

Implementação anterior

Implementação Multiciclo

O que mudou?

Existe uma única unidade de memória que é

usada para instruções e para dados.

Existe uma única ALU, em vez de uma ALU e

dois somadores.

Um ou mais registradores são adicionados após

cada unidade funcional para conter a saída

dessa unidade. Este valor é armazenado até o

seu uso em um ciclo de clock subseqüente.

O que mudou?

Lógica para inserção dos registradores

Dados usados pelas instruções subseqüentes, em um

ciclo de clock posterior, são armazenados em

elementos de estado visíveis ao programador.

Dados utilizados pela mesma instrução em um ciclo

posterior, são armazenados nos registradores

adicionais (não visíveis ao programador).

O que mudou?

Logo,

são

introduzidos

registradores temporários:

os

seguintes

O registrador de instrução IR e o registrador de

memória MDR.

Os registradores A e B

O registrador ALUOut

Todos os registradores citados, com exceção

do IR, contém dados apenas entre um par de

ciclos de clock adjacentes.

IR precisa conter a instrução até o fim da execução

dessa instrução, logo, ele precisa ter um sinal de

controle de escrita.

O que mudou?

Novos multiplexadores também precisam ser

adicionados.

O que mudou?

Decide entre

deslocamento e

acesso a memória

Decide entre PC+4 e

o Reg A.

Decide entre:

Reg. B

O valor 4

Instrução

Instrução deslocada de 2

O que mudou?

Unidade de Controle

Novos sinais de controle para:

PC, memória, registradores e IR precisarão de sinais

de controle de escrita.

Memória precisará de um sinal de leitura.

Controle da ALU sofre mudanças pois ALU atual,

também desempenha a função dos outros dois

somadores.

Etapas de uma Instrução Mips

Cada etapa leva 1 ciclo de clock para ser

realizada.

O tempo deste ciclo de clock é calculado a

partir da etapa que possui maior tempo para

execução.

Com relação a leitura/escrita em registradores,

observar:

Se registrador simples (PC, IR, MDR, etc) a

leitura/escrita é parte de um ciclo de clock.

Se registrador pertencer ao banco de registradores, é

necessário um ciclo de clock adicional para efetuar

a transação.

Etapas de uma Instrução Mips

Etapa de busca da instrução

Etapa de decodificação da instrução e busca

dos registradores.

Execução, cálculo do endereço de memória

ou conclusão do desvio.

Etapa de acesso a memória ou conclusão de

instrução tipo R.

Etapa de conclusão da Leitura da Memória

Etapas de uma Instrução Mips

Etapa de busca da instrução

Busca a instrução da memória e calcula o endereço

da próxima instrução seqüencial.

Etapas de uma Instrução Mips

Etapa de decodificação da instrução e busca

dos registradores.

Nesta etapa, ainda não sabemos qual a instrução a

ser executada, mas enquanto a instrução é

decodificada, podemos fazer algumas funções em

paralelo:

Já podemos ler os dois registradores indicados pelo

campo rs e rt e armazená-los nos regs. A e B.

Podemos calcular o endereço de desvio com a ALU e

salvá-lo em ALUOut.

Realizar

estas

operações

antecipadamente,

diminuem o número de ciclos de clock necessário

para execução da instrução.

Etapas de uma Instrução Mips

Execução, cálculo de endereço de memória

ou conclusão de desvio.

Se operação de desvio

Se a operação for de desvio incondicional o valor de

PC é substituído pelo valor do desvio.

Se a operação for de desvio condicional, utilizamos a

ALU para verificar a igualdade dos dois operandos

(Regs A e B) em seguida, a depender da igualdade

passamos o valor do desvio ao PC.

Fim da execução da instrução de desvio

Etapas de uma Instrução Mips

Execução, cálculo de endereço de memória

ou conclusão de desvio.

Se operação de referência a memória

Utilizamos a ALU para calcular o endereço de

memória e o salvamos em ALUout.

Se operação de instrução lógica ou aritmética

Utilizamos a ALU para efetuar a operação aritmética.

Salvamos o resultado em ALUout.

Etapas de uma Instrução Mips

Etapa de acesso à memória ou conclusão de

instrução R.

Se a instrução é do tipo R.

O valor de AluOut será colocado no banco

registradores.

Fim da execução da instrução do tipo R.

Se instrução de referência à memória.

Fazemos acesso à memória com o valor presente

AluOut.

Se leitura, o endereço acessado é escrito

registrador de dados da memória (MDR).

Se escrita, o valor é escrito na memória e fim

execução.

de

em

no

da

Etapas de uma Instrução Mips

Etapa de conclusão de leitura da memória

Os loads são completados, escrevendo novamente o

valor da memória para o banco de registradores.

Definindo o Controle

Para definirmos o controle, utilizaremos uma máquina

de estados finitos.

Uma máquina de estados finito consiste em um

conjunto de estados e diretrizes sobre como mudar o

estado.

As diretrizes são definidas por uma função de próximo

estado, que mapeia o estado atual e as entradas para

um novo estado.

Cada estado também especifica um conjunto de

saídas ativadas quando a máquina está neste estado.

Quando a saída não está explicitamente ativada, dizemos

que a mesma está inativa (0).

Não confundir com don’t care

O controle dos estados finitos corresponde às cinco

etapas de execução mostradas anteriormente.

Visão de Alto Nível da máquina de

estados finitos.

Máquina de estados finitos para

Busca e decodificação de instrução

Máquina de estados finitos para

controlar as instruções de referência à

memória.

Máquina de estados finitos para as

instruções tipo R.

Máquina de estados finitos para

desvios condicionais

Máquina de estados finitos para

desvios incondicionais

Máquina de estados finitos

da unidade de controle:

versão completa

Implementação de uma máquina

de estados finitos

Para implementar a unidade controladora

baseada em uma máquina de estados finitos,

podemos utilizar uma máquina de Moore.

Sua característica fundamental é que a saída

depende apenas do estado atual.

Em uma máquina de Moore a lógica de

controle é dividida em duas partes:

Uma parte possui a saída do controle e saída para o

próximo estado

Uma parte possui a entrada do opcode e a entrada

para o próximo estado (que agora, representa o

estado atual).

Máquina de Moore

Exceções

Exceções x Interrupções

Exceção

Um evento inesperado de dentro do processador

Exemplo: Overflow aritmético

Interrupção

Um evento inesperado cuja origem é externa.

Ex: Interrupção gerada pelos dispositivos de E/S

Exceções X Interrupções

Exceções X Interrupções

Como as Exceções são Tratadas

Etapas:

Salvar o endereço da instrução no registrador (EPC)

Transferir o controle para o sistema operacional em algum

endereço especificado.

O sistema operacional então, a depender da exceção,

toma a ação apropriada, que pode ser:

Fornecer algum serviço ao programa usuário.

Tomar alguma ação predefinida em resposta a um

overflow.

Interromper a execução do programa e retornar um erro.

Após executar qualquer ação necessária devido à

exceção, o sistema operacional pode terminar o

programa ou continuar sua execução usando o EPC.

Como as Exceções são Tratadas

Para comunicar o motivo da interrupção,

podem ser utilizados dois métodos:

Utilizar um esquema de interrupções vetorizadas.

O endereço para qual o controle é desviado sinaliza

a causa da interrupção.

Os endereços que indicam os tipos de interrupção

são separados por um espaço constante, por

exemplo, 32 bytes.

Este espaço é preenchido pelo S.O com as instruções

necessárias para o tratamento da interrupção.

Como as Exceções são Tratadas

Incluir um registrador de status

Só possui um único ponto de entrada para todas as

exceções, logo o processador necessita de uma

estrutura auxiliar para descobrir o tipo da exceção

Em geral, emprega-se um registrador auxiliar.

Método utilizado no MIPS. (Registrador Cause)

Rotina de tratamento pode possuir um maior

tamanho.

No nosso exemplo/implementação ilustraremos

apenas duas exceções:

Instrução indefinida.

Overflow Aritmético.

Processador com EPC e Cause

O que muda no controle?

Introduz mais dois estados na máquina de

estados finitos:

O estado 10, cuja origem é o estado 1 que é o

estado onde é realizado a avaliação do opcode.

O estado 11, cuja origem é o estado 7 que é o

estado onde avaliamos o resultado da operação

aritmética.

Unidade de

Controle com os

novos estados

Referências

Hennessy & Patterson

Seções 5.5 e 5.6