Arquitetura e Organização de

Computadores

Fernando Fonseca Ramos

Faculdade de Ciência e Tecnologia de Montes Claros

Fundação Educacional Montes Claros

1

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Índice

•

•

•

•

•

•

123456-

Introdução

Exemplo de Microarquitetura

Exemplo de Nível ISA: O IJVM

Exemplo de Implementação

Melhora de Performance

Exemplos de Níveis de Microarquitetura

2

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

1 - Introdução:

•

•

•

É o nível 1, que fica acima do nível da lógica digital.

Sua principal função é implementar o nível ISA (Instruction Set

Arquitecture).

O projeto deste nível deve considerar os seguintes elementos:

– arquitetura do conjunto de instruções a ser implementada (ISA).

– objetivos de custos e desempenho do computador a ser projetado.

3

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

1 - Introdução:

•

A maioria das ISA’s modernas, em particular os projetos RISC, tem

instruções simples que podem ser executadas em um único ciclo de

clock.

•

As ISA’s mais complexas, como a do Pentium, precisam de mais

ciclos para executar uma única instrução. E necessário ter

metodologias de seqüenciamento de instruções mais otimizadas

para melhorar o desempenho da maquina em termos de tempo.

4

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

•

•

•

•

•

Não existem princípios gerais para projeto de microarquitetura, para

estudo utiliza-se exemplos de microarquitetura.

Exemplo de microarquitetura: IJVM.

IJVM e a arquitetura de uma maquina virtual Java – JVM (Java

Virtual Machine).

Executa apenas um subconjunto de instruções com inteiros da JVM.

Objetivos:

– Descrição da microarquitetura sobre a qual será implementada a

IJVM.

– Descrição do controle e do seqüenciamento de execução das

instruções.

5

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

•

Requisitos:

– Desenvolvimento de um microprograma (em ROM) cuja função e

buscar, decodificar e executar as instruções IJVM.

– O microprograma deve ser pequeno e deve alimentar

diretamente as portas do hardware da maquina.

– Considera-se que cada instrução do nível ISA e uma função a

ser chamada pelo programa principal.

6

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

Caminho de Dados

• É a parte do processador que

contém a UAL e todas as suas

entradas e saídas.

• Conteúdo do Caminho de Dados:

– Conjunto de registradores de

32bits

• (PC, SP, MDR, etc.)

– UAL

• Controle de Função: F0 e F1

• Controle de Habilitação: ENA,

ENB

• Complemento de A: INVA

• Incremento: INC

7

– 3 Barramentos: A, B e C

– Deslocadores

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

Caminho de Dados

• Funções da ULA:

– Todas as funções executadas pela ULA são determinadas por

6 linhas de controle:

•

•

•

•

F0 e F1 para determinação da operação.

ENA e ENB para habilitar individualmente suas entradas A e B.

INVA para inverter a entrada A.

INC que forca um vai - um para o bit menos significativo,

efetivamente adicionando 1 ao resultado (incremento de 1).

8

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

Caminho de Dados

• Combinações úteis de sinais de controle da ULA com as funções

executadas por cada uma delas.

9

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

10

Caminho de Dados

• É possível escrever em um mesmo registrador no mesmo ciclo de

clock: leitura e escrita são feitas em momentos diferentes em um

mesmo ciclo.

• A saída da UAL pode ser armazenada em mais de um registrador.

Contudo, no barramento B apenas o conteúdo de um dos

registradores pode ser transferido por vez.

• O registrador H pode ser carregado com o valor presente no

barramento B, realizando-se uma soma com o sinal ENA

desabilitado (ENA=0).

• Deslocamentos a direita e a esquerda podem ser comandados

pelos sinais de controle do deslocador.

– SLL8 (shift left logical) – desloca a saída da UAL 1 byte a

esquerda, deixando 0s no byte da direita.

– SRA (shift right arithmetic): desloca a saída da UAL 1 bit para

Arq. e Org. de Comp.– Fernando Ram

a direita, sem modificar o bit mais significativo.

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

Temporização

11

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

12

Temporização

• O primeiro ciclo (explicito, do caminho de dados, apresentado na

figura), pode ser visto como um conjunto de subciclos implícitos.

• O inicio do primeiro subciclo e marcado pela transição negativa

do clock.

• Cada subciclo corresponde a execução de uma atividade em um

determinado intervalo de tempo (Δw, Δx, Δy e Δz).

• Atividades que ocorrem durante os subciclos

– 1. Os sinais de controle são ativados (Δw).

– 2. O barramento B e carregado a partir dos registradores ( Δx).

– 3. A UAL e o deslocar operam (Δy).

– 4. O resultado da operação da UAL e do deslocador se

propaga através do barramento C em direção aos

registradores (Δz).

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

Temporização

• O resultado e armazenado nos registradores na transição positiva

do próximo clock.

• E de responsabilidade dos engenheiros de projeto assegurar que

essa transição positiva ocorra somente apos passado o tempo

Δw+Δx+Δy+Δdz.

• Caso contrario a carga dos registradores não é realizada.

• Dessa forma, é possível ler e escrever num mesmo registrador,

sem produzir “lixo” (ex.: incremento do registrador PC).

13

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

Operações de Memória

• A comunicação da máquina com a memória utiliza duas “portas”:

– Porta de 32 bits (palavra):

• MAR (memory address register)

• MDR (memory data register)

– Porta de 8 bits (byte):

• PC (program counter)

• MBR (memory buffer register)

• Essa porta só pode ler dados da memória.

• Par de registradores MAR/MDR: usado para ler/escrever

endereço da palavra

• Par de registradores PC/MBR: usado para ler instruções do

programa executável

14

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

Operações de Memória

• MAR armazena o endereço de uma palavra, de maneira que os

valores 0, 1, 2, etc. referenciam palavras consecutivas.

– Ex.: MAR=2, na leitura da memória , serão lidos os bytes 8 a

11 (os bytes que compõem a palavra 2), sendo esses 32 bits

guardados no MDR.

• PC guarda o endereço de um byte, de modo que os valores 0, 1,

2, etc. referenciam bytes consecutivos.

– Ex.: PC=2, na uma leitura da memória , o byte 2 será lido da

memória e seus 8 bits serão guardados nos 8 bits menos

significativos do MBR.

15

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

Microinstruções

• De acordo com a figura do caminho de dados, são necessários 29 sinais

para controle:

– 9 sinais para controlar escrita no barramento B

– 9 sinais para controlar escrita nos registradores a partir do

barramento C

– 8 sinais para controlar UAL e deslocador

– 2 sinais para leitura e escrita em memória (MAR /MDR)

– 1 sinal para busca em memória via PC /MBR

• Os valores dos 29 sinais definem as operações a serem executadas

durante um ciclo do caminho de dados

16

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

Microinstruções

• De acordo com a figura do caminho de dados, são necessários 29 sinais

para controle:

– 9 sinais para controlar escrita no barramento B

– 9 sinais para controlar escrita nos registradores a partir do

barramento C

– 8 sinais para controlar UAL e deslocador

– 2 sinais para leitura e escrita em memória (MAR /MDR)

– 1 sinal para busca em memória via PC /MBR

• Os valores dos 29 sinais definem as operações a serem executadas

durante um ciclo do caminho de dados

17

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

Microinstruções

• Observação quanto ao acesso à memória:

– Uma solicitação de acesso ao conteúdo da memória é feita no ciclo

1

– a informação solicitada só estará disponível no ciclo 3 (pelo menos)

• Redução do número de sinais de controle:

– 9 sinais para controlar escrita em B → 4 sinais, usando

decodificador (não faz sentido o acesso a B por mais de um

registrador simultaneamente)

18

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

Microinstruções

• Estrutura e ordenação de uma possível microinstrução

19

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

Microinstruções

•

Endereço: contém o endereço da próxima microinstrução a ser

potencialmente ativada

•

Desvio: determina a próxima microinstrução a ser executada

•

UAL: especifica as funções da UAL e do deslocador

•

Barramento C: seleciona qual dos registradores serão carregados com o

valor que estiver no barramento C

•

Memória: especifica as funções da memória

•

Barramento B: seleciona a entrada do barramento B

20

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

O MIC-1: Elementos

21

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

O MIC-1: Elementos

•

Seqüenciador

– Realiza todos os passos necessários para execução de uma

instrução ISA

– A cada ciclo: estado de cada sinal de controle; e o endereço da

próxima microinstrução

•

Memória de controle: armazena o microprograma completo

•

MPC (MicroProgram Counter): endereço da próxima microinstrução

•

MIR (Micro Instruction Register): armazena microinstrução corrente

22

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

O MIC-1: Elementos

•

•

Campo JAM

– 000: nada a fazer

– JAMN == 1: O valor de N deve ser submetido a um OR com bit de

maior ordem do MPC

– JAMZ == 1: O valor de Z deve ser submetido a um OR com bit de

maior ordem do MPC

– F=(JAMN AND N) OR (JAMZ AND Z) OR NEXT_ADDRESS[8]

Só há duas possibilidades para conteúdo de MPC:

– NEXT_ADDRESS

– NEXT_ADDRESS com bit de mais alta ordem submetido à

operação OR com 1

23

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

2 – Exemplo de Microarquitetura:

O MIC-1: Elementos

•

Campo JAM

•

JMPC:

– 1: MPC=(8 bits de MBR) OR (8 bits menos significativos do

NEXT_ADDRESS)

– JMPC=1: NEXT_ADDRESS = 0x000 ou 0x100

– Em geral, MBR contém um código de operação (opcode) ISA

24

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

3 – Exemplo de Nível ISA: O IJVM

Pilhas

•

Armazenamento de variáveis locais

•

Só há duas possibilidades para conteúdo de MPC:

25

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

3 – Exemplo de Nível ISA: O IJVM

O Modelo de memória da IJVM

•

•

•

Duas opções de visualização:

– Vetor de 232 bytes = 4 GB

– Vetor de 230 palavras (cada palavra = 4 bytes)

As instruções da IJVM só podem ter acesso à memória indexando-a

com ponteiros

Pool de Constantes

– Programas IJVM não podem escrever nessa área que armazena

constantes, strings e ponteiros para outras áreas da memória

– CPP aponta para o endereço da primeira palavra

26

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

3 – Exemplo de Nível ISA: O IJVM

O Modelo de memória da IJVM

•

•

•

1. Quadro de Variáveis Locais

– Armazena variáveis locais (procedimentos)

– LV aponta para a base do quadro de variáveis locais corrente

2. Pilha de Operandos

– Localiza-se imediatamente acima do quadro de variáveis locais

– SP aponta para o endereço de mais alta ordem

3. Área de Procedimento

– Armazena o programa

– PC armazena o endereço da instrução a ser executada

27

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

3 – Exemplo de Nível ISA: O IJVM

O Modelo de memória da IJVM

•

•

•

•

Área de Procedimento: vetor de bytes

Pool de Constantes: vetor de palavras

Pilha de Operandos: vetor de palavras

Quadro de Variáveis Locais: vetor de palavras

28

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

3 – Exemplo de Nível ISA: O IJVM

Conjunto de instruções da IJVM

•

Manipulação de pilha

– BIPUSH byte (0x10): coloca byte na pilha

– DUP (0x59): copia topo e coloca no topo

– ILOAD varnum (0x15): coloca uma variável local no topo da pilha

– ISTORE varnum (0x36): retira palavra do topo e armazena numa

variável local

– LDC_W índice (0x13): coloca no topo uma constante vinda do Pool

de Constantes

– POP (0x57): retira da pilha a palavra do topo

– SWAP (0x5F): troca de posição as duas palavras do topo da pilha

29

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

3 – Exemplo de Nível ISA: O IJVM

Conjunto de instruções da IJVM

•

•

Operações aritméticas

– IADD (0x60): retira as duas palavras do topo, soma-as e armazena

o resultado no topo

– ISUB (0x64): retira as duas palavras do topo, subtrai-as e armazena

o resultado no topo

Operações lógicas

– IAND (0x7E): retira as duas palavras do topo, realiza um AND e

armazena o resultado no topo

– IOR (0x80): retira as duas palavras do topo, realiza um OR e

armazena o resultado no topo

30

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

3 – Exemplo de Nível ISA: O IJVM

Conjunto de instruções da IJVM

•

Desvios

– GOTO desl (0xA7): desvio incondicional

– IFEQ desl (0x99): retira o topo e desvia se for igual a zero

– IFLT desl (0x9B): retira o topo e desvia se for menor que zero

– IF_ICMPEQ desl (0x9F): retira as duas palavras do topo e desvia se

forem iguais

•

Chamadas de procedimentos

– INVOKEVIRTUAL desl (0xB6): chama um procedimento

– IRETURN (0xAC): retorna de um procedimento trazendo um inteiro

31

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

3 – Exemplo de Nível ISA: O IJVM

Compilação de JAVA para IJVM

32

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

4 – Exemplo de Implementação

Main 1 ) PC=PC+1; fetch; goto(MBR)

nop1 ) goto Main 1

iadd1) MAR=SP=SP-1; rd

iadd2) H=TOS

iadd3) MDR=TOS=MDR+H; wr; goto Main 1

isub1 ) MAR=SP=SP-1; rd

isub2 ) H=TOS

isub3 ) MDR=TOS=MDR-H; wr; goto Main 1

dup1 ) MAR=SP=SP+1

dup2 ) MDR=TOS; wr; goto Main 1

33

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

4 – Exemplo de Implementação

bipush1 ) SP=MAR=SP+1

bipush2 ) PC=PC+1; fetch

bipush3 ) MDR=TOS=MBR; wr; goto Main 1

iload1 ) H=LV

iload2 ) MAR=MBRU+H; rd

iload3 ) MAR=SP=SP+1

iload4 ) PC=PC+1; fetch; wr

iload5 ) TOS=MDR; goto Main 1

34

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

5 – Melhora da Performace

Velocidade x Custo

•

Metodologias para aumentar a velocidade de execução

– Reduzir o número de ciclos necessários à execução das instruções

– Simplificar a organização da máquina, de modo a reduzir o período

de clock

– Sobrepor a execução de instruções

Redução do caminho de execução

35

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

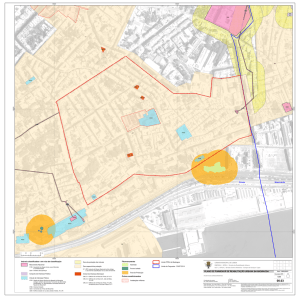

5 – Melhora da Performace

Redução do caminho de execução

•

•

•

Arquitetura com três barramentos: inclusão de um barramento A para a

entrada esquerda da UAL

Unidade de busca de instruções: busca de instruções a cargo de uma

unidade independente;

UAL restrita à execução de instruções propriamente dita

36

Arq. e Org. de Comp.– Fernando Ram

Arq. e Org. de Computadores

Nível da Microarquitetura

5 – Melhora da Performace

Redução do caminho de execução

37

Arq. e Org. de Comp.– Fernando Ram