Memória

Gestão do espaço lógico

Paginação

Segmentação com paginação

Paginação

Divide-se a memória física em pequenos blocos de

tamanho fixo chamados de páginas físicas (ou

frames) – o tamanho é uma potência de 2 entre 512

bytes e 8192 bytes.

Divide-se o espaço de endereçamento lógico em

blocos do mesmo tamanho chamados de páginas (ou

páginas virtuais).

A memória física de um processo não necessita de

ser contígua – atribui-se páginas de memória física

ao processo onde quer que estas estejam disponíveis

Não há fragmentação externa

Há fragmentação interna (em média ½ página)

Arquitectura de Computadores (2008/2009): Memória

562

Tabela de páginas

MMU usa um tabela de páginas que traduz

endereços virtuais do programa nos endereços

físicos atribuídos

O SO manterá informação sobre todas as frames

livres e ocupadas

Para executar um programa com n páginas, precisa de

encontrar n frames livres e carregar lá o programa

Gere, para cada programa, uma tabela de páginas que

traduz endereços virtuais nos endereços físicos que lhe

foram atribuídos

Arquitectura de Computadores (2008/2009): Memória

563

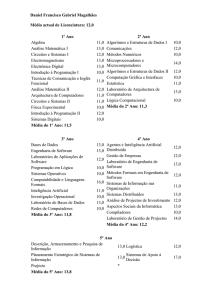

Paginação: atribuição não contígua

O processo B termina e inicia-se o processo D:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

A.0

A.1

A.2

A.3

B.0

B.1

B.2

C.0

C.1

C.2

C.3

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Arquitectura de Computadores (2008/2009): Memória

A.0

A.1

A.2

A.3

C.0

C.1

C.2

C.3

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

A.0

A.1

A.2

A.3

D.0

D.1

D.2

C.0

C.1

C.2

C.3

D.3

D.4

564

Gestão de memória física por páginas

Transformação de endereços: A MMU converte

endereços virtuais em endereços físicos através de

um tabela gerida pelo SO (a tabela de páginas)

0:

1:

Endereços

virtuais

0:

1:

Endereços

físicos

CPU

P-1:

Tabela de páginas

Arquitectura de Computadores (2008/2009): Memória

N-1:

Memória central

565

Transformação de endereços

Parâmetros

P = 2p = tamanho da página (usa p bits).

N = 2n = espaço virtual (endereço tem n bits)

M = 2m = espaço físico (endereço tem m bits)

n–1

Número de página virtual

p p–1

deslocamento

0

Endereço virtual

Note-se que os bits

correspondentes ao

deslocamento (dentro da página)

Tabela de páginas

não mudam durante a

transformação

0

m–1

p p–1

Endereço físico

Número da página física

deslocamento

Arquitectura de Computadores (2008/2009): Memória

566

Suporte da tabela de páginas

Onde se guarda a tabela de páginas de um processo?

No caso do Pentium a tabela tem 220 entradas; se cada

uma tiver 4 bytes, são 4 Mbytes!

E há uma tabela de páginas por processo …

Não é tecnicamente viável guardar a tabela de páginas

na MMU

Solução:

Guardar a tabela de páginas em memória central (RAM)

Page-table base register (PTBR) base da tabela

Page-table length register (PTLR) tamanho da tabela

Arquitectura de Computadores (2008/2009): Memória

567

Suporte da tabela de páginas

RAM

Endereço virtual:

Página virtual

Endereço físico:

Desloc.

x

Interrupção

Página física

Desloc.

Tamanho de

uma entrada

Tabela de páginas

<

Page table lengthregister

+

Page table base register

Arquitectura de Computadores (2008/2009): Memória

568

Suporte da tabela de páginas

Neste esquema, cada acesso a dados ou código

obriga a dois acessos à memória:

1. Ler a tabela de páginas obtendo a página física

2. Ler/escrever o dado ou ler a instrução.

O problema dos dois acessos à memória pode ser

resolvido por hardware especial de consulta rápida

chamado translation look-aside buffer (TLB) que

se baseia numa memória associativa

Funciona como uma cache da tabela de páginas

Arquitectura de Computadores (2008/2009): Memória

569

TLB - Memória associativa

Transformação de

endereços: A A’

MMU

Se A está na

memória

associativa, TLB

responde logo com

o número da

frame A’

Senão está, obtém

o número da

frame da tabela

de páginas na

memória

Arquitectura de Computadores (2008/2009): Memória

570

Tempo de acesso efectivo

Pesquisa associativa = ε unidades de tempo

Tempo de acesso à RAM é T unidades de tempo

Hit rate (α) – percentagem das vezes em que o

número da frame está numa entrada do TLB

Tempo de acesso efectivo (TAE)

TAE = αε + (1 – α)(T + ε) + T

tempo para obter o endereço real

Nota: sem cache de memória

Arquitectura de Computadores (2008/2009): Memória

571

Exemplo

T de 50ns

TLB de 5ns e supondo um hit-rate de 95%

αε + (1 – α)(T + ε) + T = 0.95x5 + 0.05x55 + 50 = 57.5ns

Considerando a cache de memória….?

αε + (1 – α)(T + ε) + Tc

Tc: Tempo médio tendo em conta a cache

Supondo Tc=0.9x5+0.1x50=9.5ns

0.95x5 + 0.05x55 + 9.5 = 17ns

Arquitectura de Computadores (2008/2009): Memória

572

Memória virtual

A separação de espaços permite que o programa use

um espaço virtual:

Endereços independentes da localização física do

programa

Cada programa tem o seu espaço de endereços (0 … etc )

Pode usar endereços que não existem na memória física

Só ocupa na memória física o espaço realmente necessário

Não precisa de ter tudo carregado na memória física carrega só as páginas usadas

Espaço virtual pode ser maior que o físico (real)

A arquitectura está limitada pela memória virtual não pela

física possibilidade de expansão

Permite partilha de partes do espaço de endereçamento

entre processos

Arquitectura de Computadores (2008/2009): Memória

573

Paginação a pedido

VM pode ser suportada através de paginação a

pedido

Todas as páginas virtuais da imagem do processo estão

em disco, chamado disco de paginação ou disco de

swap

As páginas só vêm para memória central (RAM) quando

são referenciadas, i.e. quando há um endereço virtual

emitido pelo CPU correspondente a essa página virtual

Procura-se manter as páginas mais usadas em memória

real Working Set

É completamente transparente para o

utilizador/programador

Arquitectura de Computadores (2008/2009): Memória

574

Motivações para a memória virtual

Simplificar a gestão de memória

Múltiplos processos residem em memória central cada um

com o seu próprio espaço de endereçamento – cada um

tem a sua tabela de páginas

Fornece protecção – só o SO pode alterar as tabelas de

páginas

Só o código e dados “activos” (working set) é que estão

em RAM; mais RAM pode ser atribuída ao programa se

necessário

Usar a RAM como Cache para o Disco

A soma dos espaços de endereçamento dos vários

processos pode exceder o tamanho da memória física

O espaço de endereçamento de um processo pode

exceder a dimensão da memória física

Arquitectura de Computadores (2008/2009): Memória

575

Tabela de páginas

Arquitectura de Computadores (2008/2009): Memória

576

Tabela de páginas

Número de

página virtual

Memória física

resident

1

1

0

1

1

1

0

1

0

1

Tabela de páginas (em memória)

indica qual a página física

ou o endereço em disco

Arquitectura de Computadores (2008/2009): Memória

Armazenamento em disco

(partição dedicada ou

ficheiro de sistema)

577

Falta de página (Page Fault)

A primeira referência a uma página P provoca uma

excepção (page fault) e o SO intervém

SO olha para a tabela de páginas para decidir se é:

Referência inválida ⇒ aborta o programa

Obtém uma “frame” (página física) vazia F

Se a página está em disco:

Carrega a página nessa “frame”

Actualiza a tabela de páginas:

Tab_paginas[P].frame = F

Tab_paginas[P].residente = 1

F

P

Retoma a execução da instrução que provocou a

excepção

Arquitectura de Computadores (2008/2009): Memória

578

Hardware/Software na paginação a pedido

Hardware: trata das operações mais críticas:

Obter o endereço real a cada acesso

Software: o SO trata os casos excepcionais e que

exigem politicas mais complicadas:

Caso a página referenciada não esteja em memória o

SO avalia qual dos casos seguintes se trata:

Referência inválida abortar a execução do programa

Página em disco é preciso trazer a página virtual para

RAM

O SO gere a memória, que páginas ocupadas por

que programas

Arquitectura de Computadores (2008/2009): Memória

579

Exemplo de arquitectura com paginação

Características duma arquitectura (ISA)

16 bits de endereços (virtuais e reais)

páginas de 2KBytes

Endereços:

endereço virtual 16bits espaço de 216 = 64K

supondo uma RAM instalada 32KBytes, então o espaço

real está limitado a esse valor

Endereços de 16 bits, páginas de 2KBytes (11bits):

Espaço de endereços tem 64K/2K = 32 páginas

Na realidade a RAM tem 32K/2K = 16 páginas

Arquitectura de Computadores (2008/2009): Memória

580

Interpretação dos endereços

Endereços de 16 bits, páginas de 2KBytes (11bits)

RAM instalada de 32KBytes

65535

5 bits

Número de página

32 páginas

32767

Espaço real

instalado

16 páginas

instaladas

0

Arquitectura de Computadores (2008/2009): Memória

2K

Espaço Virtual

211 2K

25 32

11 bits

deslocamento na página

0

581

Tabela de páginas

65535

31

30

29

válido

residente

dirty

Tabela de páginas

(32 entradas)

0

0

0

0

1

0

0

0

2

0

0

0

32767

15

14

13

pág. física (5bits)

3

2

1

0

0

3

2

1

0

30 0

0

0

31 0

0

0

Arquitectura

de Computadores (2008/2009): Memória

0

582

Exemplo de um programa

65535

pilha

Tabela de páginas

residente

dirty

32767

válido

31

30

29

0

1

0

0

1

1

0

0

2

1

0

0

3

1

0

0

4

0

0

0

5

0

0

0

15

14

13

pág. física (5bits)

3

2

1

0

SO

0

3

2

1

0

dados

30 1

0

0

31 1

0

0

código

Arquitectura de Computadores (2008/2009): Memória

disco

(memória secundária)

583

Exemplo de um programa

65535

pilha

dirty

32767

residente

0

fetch Mem[10]

PC = 10

válido

31

30

29

0

1

0

1

0

1

1

0

0

2

1

0

0

3

1

0

0

4

0

0

0

5

0

0

0

10

pág. física (5bits)

10

10

10

20490

15

14

13

12

11

10

3

2

1

0

SO

0

3

2

1

0

dados

código

30 1

0

0

31 1

0

0

Tabela de páginas

Arquitectura de Computadores (2008/2009): Memória

disco

(memória secundária)

584

Exemplo de um programa

65535

pilha

mov [6145], 5

1

dirty

3

residente

6145

32767

válido

31

30

29

0

1

1

0

10

1

1

1

0

11

2

1

1

0

12

3

1

0

1

0

1

14

4

0

0

0

5

0

0

0

15

14

13

12

11

10

pág. física (5bits)

14

1

28673

3

2

1

0

SO

0

3

2

1

0

dados

código

30 1

1

1

31 1

0

0

13

Tabela de páginas

Arquitectura de Computadores (2008/2009): Memória

disco

(memória secundária)

585

Resumo

Mapear o espaço virtual de um programa em

memória:

Criar tabela de páginas

Resolução de endereço

Cache de endereços na TLB

Carregamento dinâmico a pedido

Tabela de páginas preenchida durante a execução

Memória Virtual usando memória física e o disco

Memória Física como cache do espaço virtual

Arquitectura de Computadores (2008/2009): Memória

586

CPU com paginação e cache interna

dados

modo de

endereçamento

cálculo

do

endereço

efectivo

endereço

virtual

cálculo do

endereço real

(MMU)

endereço

real

endereço

real

BUS

interface

Cache

L1

dados

TLB

Arquitectura de Computadores (2008/2009): Memória

587

Segmentação vs. paginação

Segmentação define porções lógicas de tamanho

variável que são visíveis para o programador

Exemplo: o segmento da pilha e do código

No caso do IA-32 pode-se aceder a um endereço usando

o SS ou CS como base

Paginação é transparente para o programador.

Consiste em dividir a memória e o espaço de

endereçamento dos programas e porções do mesmo

tamanho.

Paginação é mais fácil de gerir pelo sistema

Segmentação permite introduzir partilha e

protecção de memória de uma forma simples

Arquitectura de Computadores (2008/2009): Memória

588

Segmentação com paginação

O programa é dividido em segmentos

Cada segmento é dividido em páginas

Com a sua tabela de páginas

O programa tem então várias tabelas de páginas

O endereço é dividido em 3 partes

1. Indica a tabela de páginas a utilizar: define o

segmento

2. Número da página

3. Deslocamento

Útil porque permite segmentação do ponto de vista

do utilizador e paginação do ponto de vista do

sistema

Arquitectura de Computadores (2008/2009): Memória

589

Memória virtual no Intel Pentium 4

Páginas de 4KBytes

Endereço de 32 bits 20 bits (página) + 12 bits

(deslocamento)

Tabela de páginas 1M entradas (cada 4 Bytes)

TLB para acessos a dados de 64 entradas

TLB para acessos a código de 64/128 entradas

Também permite páginas de 4MBytes e segmentação

com paginação

Arquitectura de Computadores (2008/2009): Memória

590