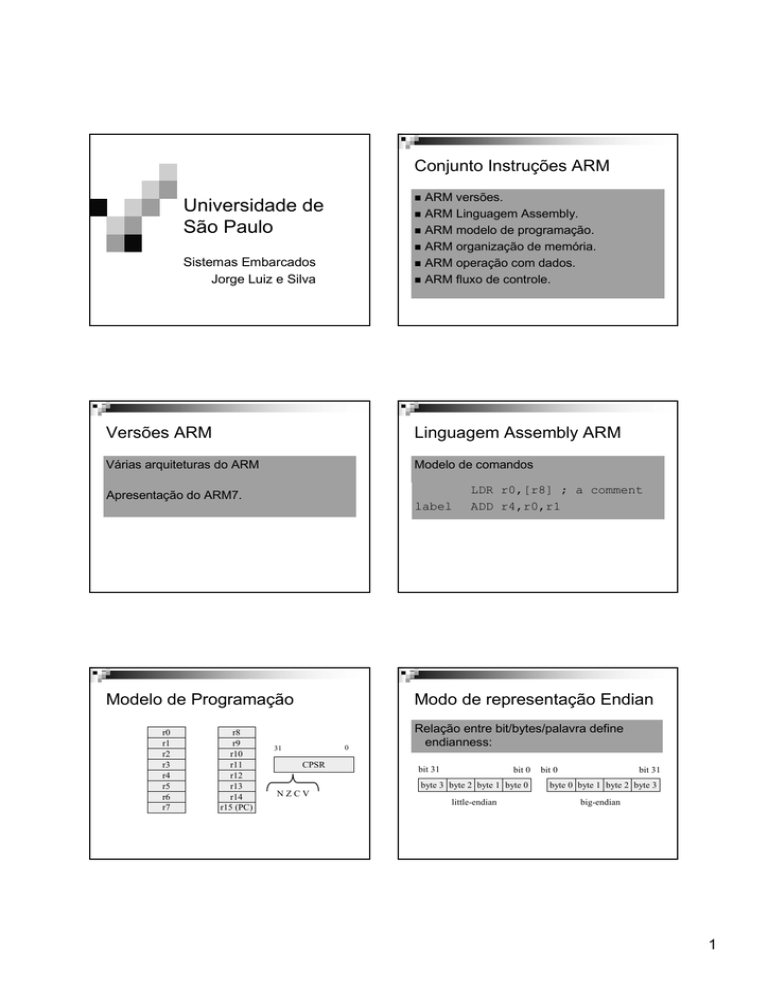

Conjunto Instruções ARM

ARM versões.

ARM Linguagem Assembly.

ARM modelo de programação.

ARM organização de memória.

ARM operação com dados.

ARM fluxo de controle.

Universidade de

São Paulo

Sistemas Embarcados

Jorge Luiz e Silva

Versões ARM

Linguagem Assembly ARM

Várias arquiteturas do ARM

Modelo de comandos

Apresentação do ARM7.

label

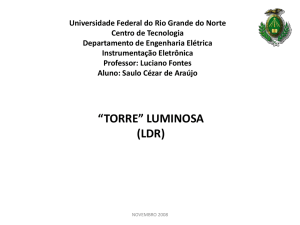

Modelo de Programação

r0

r1

r2

r3

r4

r5

r6

r7

r8

r9

r10

r11

r12

r13

r14

r15 (PC)

LDR r0,[r8] ; a comment

ADD r4,r0,r1

Modo de representação Endian

0

31

CPSR

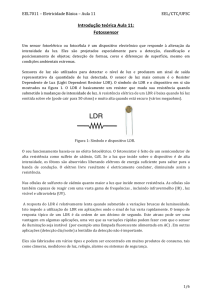

Relação entre bit/bytes/palavra define

endianness:

bit 31

bit 0

byte 3 byte 2 byte 1 byte 0

bit 0

bit 31

byte 0 byte 1 byte 2 byte 3

NZCV

little-endian

big-endian

1

Tipos de Dados ARM

Bit Status ARM

Palavras de 32 bits.

Cada operação aritimética, logica, ou de

deslocamento gera um flag CPSR:

Palavra pode ser dividida em 4 bytes

Endereço do ARM pode ter 32 bits.

Endereço referenciado por bytes

Endereço 4 se inicia no byte 4.

N (negativo), Z (zero), C (carry), V (overflow).

Exemplos:

-1 + 1 = 0: NZCV = 0110.

232-1+1 = -231: NZCV = 1001.

No power-up pode-se configurar o modo

little- ou bit-endian.

Instruções de Dados ARM

Formato Básico:

ADD r0,r1,r2

Operando Imediato:

ADD r0,r1,#2

Instruções p/ dados no ARM

ADD, ADC : soma (w. carry)

SUB, SBC : subtrai (w. carry)

MUL, MLA : multiplica (and accumulate)

AND, ORR, EOR

BIC : clear bit

LSL, LSR : Deslocamento left/right

ASL, ASR : Deslocamento arithmetico left/right

ROR : rotate right

RRX : rotate right com C

Instruções de Comparação ARM

Instruções MOV no ARM

CMP : compara

CMN : compara negado

TST : bit-wise AND

TEQ : bit-wise XOR

Alteram apenas os bits NZCV do CPSR.

MOV, MVN : move (negado)

MOV r0, r1 ; sets r0 to r1

2

Instruções load/store ARM

ARM ADR pseudo-op

LDR, LDRH, LDRB : load (half-word, byte)

STR, STRH, STRB : store (half-word, byte)

Não se pode referenciar um endereço direto

em uma instrução

Modos de endereçamento:

Valor gerados a partir de uma análise no

PC

register indirect : LDR r0,[r1]

com segundo registrador : LDR r0,[r1,-r2]

com constante: LDR r0,[r1,#4]

ADR é pseudo-op que calcula endereço

ADR r1,FOO

Example: Atribuições em C

Example: Comandos C

C:

x = (a + b) - c;

Assembler:

ADR r4,a

; endereço de a

LDR r0,[r4]

; valor de a

ADR r4,b

; endereço de b, reusando r4

LDR r1,[r4]

; valor de b

ADD r3,r0,r1

; computa a+b

ADR r4,c

; endereço de c

LDR r2,[r4]

; valor de c

SUB r3,r3,r2

; completa calculo de x

ADR r4,x

; endereço de x

STR r3,[r4]

; valor de x

C:

y = a*(b+c);

Assembler:

ADR r4,b ; get address for b

LDR r0,[r4] ; get value of b

ADR r4,c ; get address for c

LDR r1,[r4] ; get value of c

ADD r2,r0,r1 ; compute partial result

ADR r4,a ; get address for a

LDR r0,[r4] ; get value of a

MUL r2,r2,r0 ; compute final value for y

ADR r4,y ; get address for y

STR r2,[r4] ; store y

Example: Comandos C

C:

z = (a << 2) | (b & 15);

Assembler:

ADR r4,a ; get address for a

LDR r0,[r4] ; get value of a

MOV r0,r0,LSL 2 ; perform shift

ADR r4,b ; get address for b

LDR r1,[r4] ; get value of b

AND r1,r1,#15 ; perform AND

ORR r1,r0,r1 ; perform OR

ADR r4,z ; get address for z

STR r1,[r4] ; store value for z

Modos de Endereçamento

Adicionais

Base + deslocamento:

LDR r0,[r1,#16]

Base + auto indexado com incremento

LDR r0,[r1,#16]!

Pós-indexado seguido de offset:

LDR r0,[r1],#16

3

Comandos de fluxo ARM

Exemplo: comando if

Baseados em CPSR:

C:

EQ, NE, CS, CC, MI, PL, VS, VC, HI,

LS, GE, LT, GT, LE

Operação de Desvio:

B #100

Pode ser executado condicionalmente

Comando If…..

if (a > b) { x = 5; y = c + d; } else x = c - d;

if (a > b) { x = 5; y = c + d; } else x = c - d;

Assembler:

; testar condição

ADR r4,a ; endereço a

LDR r0,[r4] ; valor de a

ADR r4,b ; endereço b

LDR r1,[r4] ; valor de b

CMP r0,r1 ; compare a < b

BLE fblock ; if a ><= b, desvia para falso

Comando If …..

; bloco true

MOV r0,#5 ; gera valor de x

ADR r4,x ; endereço de x

STR r0,[r4] ; store x

ADR r4,c ; endereço de c

LDR r0,[r4] ; valor de c

ADR r4,d ; endereço de d

LDR r1,[r4] ; valor de d

ADD r0,r0,r1 ; gera y

ADR r4,y ; endereço de y

STR r0,[r4] ; store y

B after ; desvia final

; bloco false

fblock ADR r4,c ; endereço de c

LDR r0,[r4] ; valor de c

ADR r4,d ; endereço de d

LDR r1,[r4] ; valor de d

SUB r0,r0,r1 ; gera a-b

ADR r4,x ; endereço de x

STR r0,[r4] ; store valor de x

after ...

Exemplo: Implementação de

Condições

Exemplo: Implementação de

Condições…..

if (a > b) { x = 5; y = c + d; } else x = c - d;

; bloco true

; bloco true

MOVLT r0,#5 ; valor de x

MOV r0,#5 ; gera valor de x

ADR r4,x ; endereço de x

ADRLT r4,x ; endereço de x

STR r0,[r4] ; store x

STRLT r0,[r4] ; store x

ADR r4,c ; endereço de c

ADRLT r4,c ; endereço de c

LDR r0,[r4] ; valor de c

LDRLT r0,[r4] ; valor de c

ADR r4,d ; endereço de d

ADRLT r4,d ; endereço de d

LDR r1,[r4] ; valor de d

LDRLT r1,[r4] ; valor de d

ADD r0,r0,r1 ; gera y

ADDLT r0,r0,r1 ; gera y

ADR r4,y ; endereço de y

ADRLT r4,y ; endereço de y

STR r0,[r4] ; store y

STRLT r0,[r4] ; store y

B after ; desvia final

if (a > b) { x = 5; y = c + d; } else x = c - d;

; bloco false

ADRGE r4,c ; endereço de c

LDRGE r0,[r4] ; valor de c

ADRGE r4,d ; endereço de d

LDRGE r1,[r4] ; valor de d

SUBGE r0,r0,r1 ; gerar a-b

ADRGE r4,x ; endereço de x

STRGE r0,[r4] ; store valor de x

4

Exemplo: Filtro FIR

Filtro FIR …..

for (i=0, f=0; i<N; i++) f = f + c[i]*x[i];

C:

for (i=0, f=0; i<N; i++) f = f + c[i]*x[i];

Assembler

; Inicio do loop

MOV r0,#0 ; use r0 para I

MOV r8,#0 ; usar índices separados para arrays

ADR r2,N ; endereço de N

LDR r1,[r2] ; valor de N

MOV r2,#0 ; use r2 para f

ADR r3,c ; endereço de c

ADR r5,x ; endereço de x

; corpo do loop

loop LDR r4,[r3,r8] ; valor de c[i]

LDR r6,[r5,r8] ; valor de x[i]

MUL r4,r4,r6 ; gerar c[i]*x[i]

ADD r2,r2,r4 ; acumular

ADD r8,r8,#4 ; incrementa uma palavra offset ao índice

ADD r0,r0,#1 ; soma 1 em i

CMP r0,r1 ; final?

BLT loop ; if i < N, continue

Subrotinas no ARM

Chamadas aninhadas de

subrotinas

Desvio e link:

Requer conversão de código

BL foo

Copia PC atual em r14.

Para retornar :

MOV r15,r14

f1

LDR r0,[r13] ; load arg into r0 from stack

; call f2()

STR r14,[r13]! ; store f1’s return adrs

STR r0,[r13]! ; store arg to f2 on stack

BL f2 ; branch and link to f2

; return from f1()

SUB r13,#4 ; pop f2’s arg off stack

LDR r13!,r15 ; restore register and return

Resumo

Arquitetura Load/store

Maioria das instruções são RISC, operam

em um único ciclo.

Algumas operações multi-registradores são

longas

Todas as instruções podem ser executadas

condicionalmente

5