ACONFORTO,

rtigo de Revisão

/ Review A

rticle

J.; VALLIM

M.B.R.

Estudo Comparativo das Tecnologias de Lógica Reconfigurável Altera e Xilinx

Comparative Study of Altera and Xilinx Reconfigurable Logic Technologies

Júlio Confortoa*; Marcos Banheti Rabello Vallima

Curso de Engenharia Elétrica - Universidade Tecnológica Federal do Paraná, Campus Cornélio Procópio, PR, Brasil.

a

*E-mail: [email protected]

Resumo

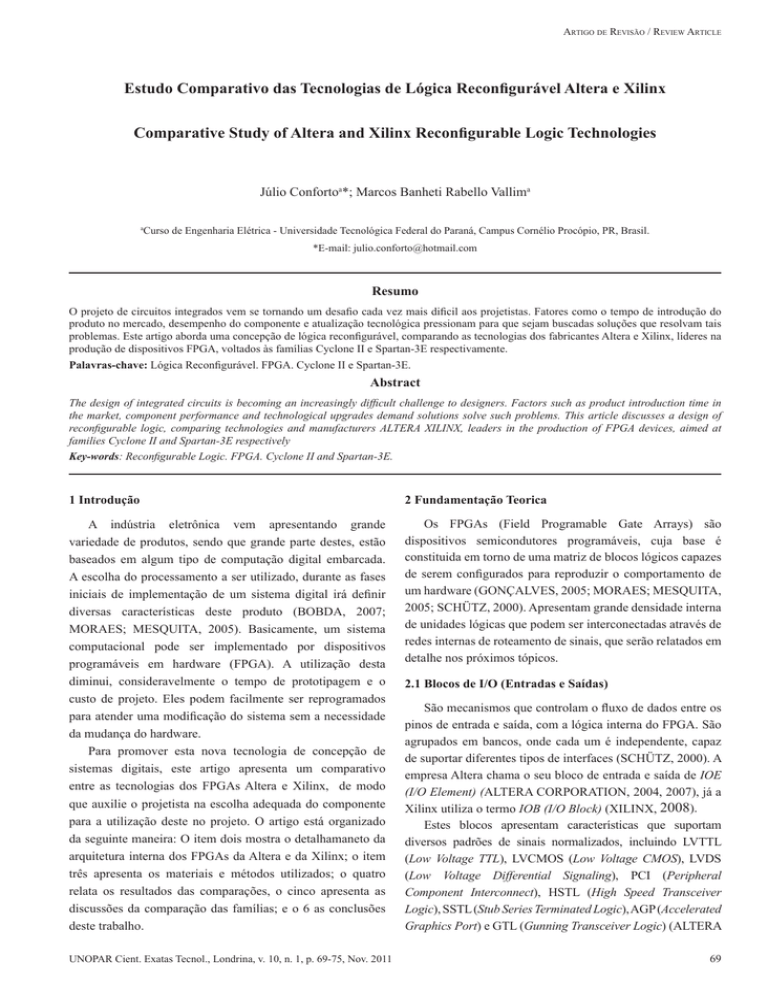

O projeto de circuitos integrados vem se tornando um desafio cada vez mais dificil aos projetistas. Fatores como o tempo de introdução do

produto no mercado, desempenho do componente e atualização tecnológica pressionam para que sejam buscadas soluções que resolvam tais

problemas. Este artigo aborda uma concepção de lógica reconfigurável, comparando as tecnologias dos fabricantes Altera e Xilinx, líderes na

produção de dispositivos FPGA, voltados às famílias Cyclone II e Spartan-3E respectivamente.

Palavras-chave: Lógica Reconfigurável. FPGA. Cyclone II e Spartan-3E.

Abstract

The design of integrated circuits is becoming an increasingly difficult challenge to designers. Factors such as product introduction time in

the market, component performance and technological upgrades demand solutions solve such problems. This article discusses a design of

reconfigurable logic, comparing technologies and manufacturers ALTERA XILINX, leaders in the production of FPGA devices, aimed at

families Cyclone II and Spartan-3E respectively

Key-words: Reconfigurable Logic. FPGA. Cyclone II and Spartan-3E.

1 Introdução

2 Fundamentação Teorica

A indústria eletrônica vem apresentando grande

variedade de produtos, sendo que grande parte destes, estão

baseados em algum tipo de computação digital embarcada.

A escolha do processamento a ser utilizado, durante as fases

iniciais de implementação de um sistema digital irá definir

diversas características deste produto (BOBDA, 2007;

MORAES; MESQUITA, 2005). Basicamente, um sistema

computacional pode ser implementado por dispositivos

programáveis em hardware (FPGA). A utilização desta

diminui, consideravelmente o tempo de prototipagem e o

custo de projeto. Eles podem facilmente ser reprogramados

para atender uma modificação do sistema sem a necessidade

da mudança do hardware.

Para promover esta nova tecnologia de concepção de

sistemas digitais, este artigo apresenta um comparativo

entre as tecnologias dos FPGAs Altera e Xilinx, de modo

que auxilie o projetista na escolha adequada do componente

para a utilização deste no projeto. O artigo está organizado

da seguinte maneira: O item dois mostra o detalhamaneto da

arquitetura interna dos FPGAs da Altera e da Xilinx; o item

três apresenta os materiais e métodos utilizados; o quatro

relata os resultados das comparações, o cinco apresenta as

discussões da comparação das famílias; e o 6 as conclusões

deste trabalho.

Os FPGAs (Field Programable Gate Arrays) são

dispositivos semicondutores programáveis, cuja base é

constituida em torno de uma matriz de blocos lógicos capazes

de serem configurados para reproduzir o comportamento de

um hardware (GONÇALVES, 2005; MORAES; MESQUITA,

2005; SCHÜTZ, 2000). Apresentam grande densidade interna

de unidades lógicas que podem ser interconectadas através de

redes internas de roteamento de sinais, que serão relatados em

detalhe nos próximos tópicos.

UNOPAR Cient. Exatas Tecnol., Londrina, v. 10, n. 1, p. 69-75, Nov. 2011

2.1 Blocos de I/O (Entradas e Saídas)

São mecanismos que controlam o fluxo de dados entre os

pinos de entrada e saída, com a lógica interna do FPGA. São

agrupados em bancos, onde cada um é independente, capaz

de suportar diferentes tipos de interfaces (SCHÜTZ, 2000). A

empresa Altera chama o seu bloco de entrada e saída de IOE

(I/O Element) (ALTERA CORPORATION, 2004, 2007), já a

Xilinx utiliza o termo IOB (I/O Block) (XILINX, 2008).

Estes blocos apresentam características que suportam

diversos padrões de sinais normalizados, incluindo LVTTL

(Low Voltage TTL), LVCMOS (Low Voltage CMOS), LVDS

(Low Voltage Differential Signaling), PCI (Peripheral

Component Interconnect), HSTL (High Speed Transceiver

Logic), SSTL (Stub Series Terminated Logic), AGP (Accelerated

Graphics Port) e GTL (Gunning Transceiver Logic) (ALTERA

69

Estudo Comparativo das Tecnologias de Lógica Reconfigurável Altera e Xilinx

CORPORATION, 2004, 2007; XILINX, 2008).

Podemos destacar o padrão LVDS, pois possui pinos com

características diferenciadas em relação aos outros pinos

do dispositivo. Esses pinos possuem taxas de transferência

de dados extremamente elevadas e circuitos internos que

auxiliam na retirada de ruídos (ALTERA CORPORATION,

2004, 2007; XILINX, 2008). São geralmente utilizados para

leituras de sensores.

Todos os blocos são protegidos contra danos causados

por descargas eletrostáticas (EDS) e por transientes de

sobretensões. Adicionalmente, todos os blocos I/O da

Altera e da Xilinx suportam o padrão de teste normalizado

internacional IEEE 1149.1 (ALTERA CORPORATION,

2004, 2007; MARQUES, 2002).

2.2 Unidades lógicas

Os blocos lógicos são circuitos idênticos, com fácil acesso

a todas as estruturas de apoio e de roteamento. São constituidos

por uma lógica Carry ou lógica de controle, LUT (“tabela

verdade”), alguns circuitos de seleção (Multiplexadores)

e flip-flops, que podem ser configurados para lidar com a

lógica combinacional (GONÇALVES, 2005; MARQUES,

2002; SCHÜTZ, 2000). Utilizando esses blocos, um usuário

pode construir aplicações envolvendo funções aritméticas

como: somadores; subtratores; acumuladores; comparadores;

contadores; entre outros.

Os nomes das unidades lógicas variam de acordo com o

fabricante, por exemplo, os FPGAs fabricados pela Altera

recebem a denominação de LAB (Logic Array Blocks)

(ALTERA CORPORATION, 2004, 2007), mas também

podem ser denominadas de CLB (Configurable Logic Block)

(XILINX, 2008), de acordo com a empresa XILINX.

2.2.1 Estrutura de uma matriz de blocos lógicos (LAB)

Cada LAB possui dezesseis elementos lógicos

interligados, através do “barramento” das interconexões.

Cada elemento lógico (LE) é composto por: um gerador de

função com quatro entradas (LUT); lógica de propagação;

lógica carry; e um elemento de registro (ALTERA

CORPORATION, 2004, 2007). Os recursos mencionados

podem ainda ser utilizados na interconexão de unidades

lógicas para se implementar, por exemplo, multiplicadores,

contadores, somadores e memórias.

Os elementos lógicos são organizados em colunas e

agrupados de forma que no final formem uma estrutura da

LAB.

A figura 1 retrata a estrutura interna de uma LAB.

Roteamentos entre LEs no LAB

LE 1

LE 2

“Barramento” das

interconexões

Comunicação entre os

elementos lógicos

LE 3

LE 4

LE 5

LE 6

LAB Entradas

Entrada 0

LE 7

LE 8

LE 9

LE 10

Entrada 1

Dados 1

Dados 2

LUT

Soma

LUT

LUT

LE 11

LUT

LE 12

LE 13

LE 14

LE 15

Saida 0

Saida 1

LE 16

Fonte: Altera (2004)

Figura 1: Arquitetura de uma LAB Cyclone II

70

UNOPAR Cient. Exatas Tecnol., Londrina, v. 10, n. 1, p. 69-75, Nov. 2011

CONFORTO, J.; VALLIM M.B.R.

2.2.2 Estrutura de blocos Lógicos Configuráveis (CLB)

Cada CLB possui nove células lógicas, formando quatro

slices interligados. Os slices são agrupados em pares e

organizados em coluna, de forma que transmita os seus dados

independentes. Cada um possui duas LUTs de quatro entradas,

Par esquerdo SLICEM

(Lógica ou memória)

para implemento lógico e dois elementos de armazenamento

dedicados, que podem ser utilizados como flip-flops. As LUTs

podem ser utilizadas como uma memória 16x1 (RAM16) ou

como um registrador de deslocamento de 16 bits (SRL16)

(XILINX, 2008).

A figura 2 retrata a estrutura interna de um CLB.

Par direito SLICEL

(Única Lógica)

Solicitar

CLB

MATRIZ

DE

CHAVES

SLICE

X1Y1

Solicitar

SLICE

X0Y1

SLICE

X1Y0

Interconexão de

vizinhos (CLB)

CIN

Entrada e saída de

informações

SLICE

X0Y0

CIN

FIMUX

SRL 16

RAM 16

LUT4 (G)

Lógica

Carry

FIMUX

Registro

LUT4 (G)

F5MUX

SRL 16

RAM 16

LUT4 (F)

Lógica

Carry

Lógica

Carry

Registro

F5MUX

Registro

LUT4 (F)

Lógica aritmética

Lógica

Carry

Registro

Lógica aritmética

SLICEM

SLICEL

Fonte: Xilinx (2008)

Figura 2: Arquitetura de um CLB Spartan-3E

2.3 Roteamento da família Cyclone II

O dispositivo que tem a arquitetura do tipo PLD hierárquico

é constituído por uma matriz de blocos lógicos, denominados

Logic Array Blocks, sendo os mesmos interligados pelo

recurso de roteamento conhecido como matriz programável

de Interconexão (PIA). Esse tipo de dispositivo é dito

hierárquico porque os blocos lógicos podem ser agrupados

entre si, criando assim, as macros-células. O roteamento é

UNOPAR Cient. Exatas Tecnol., Londrina, v. 10, n. 1, p. 69-75, Nov. 2011

bastante simplificado neste tipo de arquitetura, pois a cada

nível de hierarquia utiliza-se basicamente uma rede do tipo

crossbar (MARQUES, 2002).

Em uma rede crossbar cada entrada é conectada a uma

saída através de um ponto de conexão (crosspoint switch). É

uma rede com apenas um estágio construído com elementos

de conexão que permitem o cruzamento de diversas linhas

(MARQUES, 2002).

A figura 3 demonstra esse roteamento.

71

Estudo Comparativo das Tecnologias de Lógica Reconfigurável Altera e Xilinx

Interconexão

de condução

à esquerda

LAB

Fonte: Altera Corporation (2004)

Coluna de

interconexão

Comunicação entre

os LBAs

LAB

Interconexão de

condução à

direita

LAB

Figura 3: Roteamento da Altera

2.4 Roteamento da família Spartan-3E

A arquitetura do tipo matriz simétrica é flexível

no requisito roteamento, pois possui canais verticais e

horizontais de roteamento. Deve-se observar que, para a área

do circuito não ser completamente dominada pelo roteamento,

a granularidade do bloco lógico dever ser alta. A arquitetura

desse tipo é largamente utilizada na indústria (MARQUES,

2002).

Os recursos de roteamento dos dispositivos da família

Spartan-3E possuem três tipos de segmentos de fio: linhas

de propósito geral (Single - length lines), linhas longas (long

lines), linhas globais e matrizes de chaves (MARQUES,

2002).

As linhas globais atravessam toda a extensão do dispositivo

na vertical possuindo apenas chaves de conexão com as

linhas de propósito geral (single length lines) (ALTERA

CORPORATION, 2004; GONÇALVES, 2005).

A matriz de chaves (Figura 4) consiste de 10 chaves

de interconexão, sendo que cada uma possui 6 pontos de

interconexão programável (PIP). O PIP é um conjunto de

transistores de passagem controlado por células de memória

RAM, configuradas pelo CAD de síntese física. Essa matriz

de chaves conecta as linhas de propósito geral. Observa-se que

cada ponto de interconexão é muito caro em termos de área

de silício, pois possui seis chaves (transistores) e ao menos 6

transistores para armazenar o estado de cada uma das chaves.

Com o objetivo de reduzir a área de silício, a matriz de chaves

limita a possibilidade de conexões (MARQUES, 2002).

Na figura 4 observamos que cada conexão que entra

na matriz de chaves só pode se conectar com outros três

segmentos de fio, um em cada borda. O ideal seria uma

conexão completa, mas o custo seria proibitivo.

Seis Transistores de

Passagem por ponto de

conexão na matriz de chaves

Fonte: Marques (2002)

Figura 4: Matriz de chaves da família Spartan-3E

72

UNOPAR Cient. Exatas Tecnol., Londrina, v. 10, n. 1, p. 69-75, Nov. 2011

CONFORTO, J.; VALLIM M.B.R.

3 Material e Métodos

A linha de propósito forma uma rede de interconexão em

linhas e colunas de cinco fios de metal cada, que se ligam

através de matriz de chaves. Estas redes circundam os

blocos lógicos e as I/O. As linhas longas percorrem todo o

comprimento ou largura do dispositivo, sendo utilizadas para

transmitir sinais globais do circuito, diminuindo assim o skew1

destes sinais. Cada linha longa possui uma chave programável

no centro, a qual separa a linha em duas partes independentes.

As entradas e as saídas dos blocos lógicos podem conectarse às linhas longas. As saídas do bloco que utilizarem este

recurso podem ser realizadas através de buffers tri-state ou das

linhas de propósito geral (MARQUES, 2002).

CLB

CLB

CLB

CLB

CLB

CLB

CLB

CLB

CLB

Para a elaboração desse estudo, foram utilizadas duas

placas embarcadas, fabricadas respectivamente pelas empresas

Altera e Xilinx. A fonte primária para analise comparativa

foram os manuais dos fabricantes.

Além disso, foram desenvolvidos dois ensaios práticos

com finalidade de comparar compatibilidade, portabilidade,

performance e quantidades de unidades lógicas consumidas

numa atividade por cada FPGA.

3.1 Método empregado para avaliar o primeiro ensaio

prático

O primeiro ensaio consiste em verificar a portabilidade,

compatibilidade e performance dos FPGAs. Foi elaborado

um programa igual para as duas tecnologias, escrito em

VHDL e compilado para os processadores. Esse programa

tem a finalidade de ler pulsos de entrada, realizar um

processamento simples e gerar pulsos similares ao da leitura.

Os pulsos de entrada são fornecidos por um gerador de

função numa frequência de 15kHz e de amplitude de 3 Volts.

Foi necessário desenvolver um circuito eletrônico para isolar

as fontes de tensão (gerador de função e placa embarcada)

e tratar o sinal que entra no processador. Utilizou-se um

osciloscópio para verificar o atraso dos pulsos de saída em

relação aos pulsos de entrada.

A figura 6 apresenta o esquema montado e o circuito

eletrônico para efetuar o ensaio.

Comutadores

Programáveis

Fonte: Gomes; Charão e Velho (2009)

Figura 5: Interruptor de roteamento da Xilinx

XDG1

+

-

GND_FPGA

VCC_FPGA

Osciloscópio

U2

6

XSC2

4

GND_FPGA

GND_FPGA

D1

1N4148

1N4148

C1

74HC14-SO14

100pF/50V

1

TM

PTJC04CA595

D1234567A

4C

4N25

VCC_FPCA

U1:A

2

14

XC8325

®

2

3

D2

7

Spartan

10k

VCC_FPGA

FPGA ALTERA/XILINX

1M

-

R2

+

R1

-

GND_FPGA

-

B

A

+

1

5

Ed Trig

+

220R

R3

1M

R4

10k

R5

Gerador de Função

GND_FPGA

GND_FPGA

Figura 6: Esquema elaborado para comparar performance de cada FPGA

1 Diferença no tempo de propagação do sinal entre sua origem e seus destinos. Em linhas longas o sinal pode chegar nos destinos em tempos diferentes,

comprometendo o comportamento de circuitos síncronos. Este parâmetro pode ser traduzido como “escorregamento” do sinal.

UNOPAR Cient. Exatas Tecnol., Londrina, v. 10, n. 1, p. 69-75, Nov. 2011

73

Estudo Comparativo das Tecnologias de Lógica Reconfigurável Altera e Xilinx

3.2 Método empregado para avaliar o segundo ensaio

prático

Já o segundo ensaio consiste em verificar a quantidade de

células lógicas em que cada FPGA irá utilizar para realizar um

conjunto de atividades. Foi elaborado um programa igual para

as duas tecnologias, escrito em VHDL e compilado para os

processadores. Esse programa tem a finalidade de controlar a

velocidade e rotação de dois motores independentes, realizar a

leitura dos sensores dos motores e mostrar esses valores num

display LCD. A identificação da quantidade de células lógicas

consumidas foi através dos compiladores de cada empresa

Altera e Xilinx.

Figura 7: Comparação do pulso que entra (sinal 1) e o pulso que

sai (sinal 2) do FPGA da família Cyclone II

4 Resultados

Os resultados obtidos na comparação dos datasheets das

duas tecnologias são apresentados nas tabelas 1 e 2. A tabela

1 mostra a quantidade de pinos de I/O e os pinos diferenciais.

Tabela 1: Quantidade de pinos

Diferenciais

Entradas e Saídas

ALTERA

Fabricante

Cyclone II

Família

59 a 274

85 a 622

XILINX

Spartan-3E

40 a 156

108 a 376

A tabela 2 apresenta a quantidade de unidades lógicas

disponível pelo FPGA (ALTERA CORPORATION, 2004,

2007; XILINX, 2008).

Tabela 2: Quantidade de unidades lógicas

Fabricante

Família

Elementos lógicos/

LAB / CLB

Células lógicas

ALTERA

Cyclone II

4608 a 68416

288 a 4276

XILINX

Spartan-3E

2160 a 33192

240 a 3688

Figura 8: Comparação do pulso que entra (sinal 1) e o pulso que

sai (sinal 2) do FPGA da família SPARTAN - 3E

4.2 Resultado o segundo ensaio prático

Do segundo ensaio prático, observa-se na tabela 3 que a

família Cyclone II utilizou 6798 elementos lógicos enquantos

a família Spartan-3E utilizou 4674 células lógicas. Podese inferir que o modelo Spartan-3E possui uma rede de

interconexão mais compacta que o modelo Cyclone II.

Tabela 3: Células lógicas que cada processador consumiu para

realizar a mesma função

Cyclone II

Células lógicas /

Elementos lógicos

6798

Pinos

utilizados

24

Spartan-3E

4674

24

Família

Com as informações citadas nas tabelas 01 e 02, é

evidente que a família Cyclone II possui mais pinos de entrada

e saída e blocos lógicos quando comparada com a família

Spartan-3E. A quantidade de portas de I/O e unidades lógicas

são importantes quando se está desenvolvendo um projeto

complexo, de grande porte, que exija uma alta performance.

No entanto, quando comparado performance a Spartan-3E é

mais eficiente.

4.1 Resultado do primeiro ensaio prático

Observa-se no primeiro ensaio prático que a família

Spartan-3E possui uma velocidade de processamento maior

quando comparada com a família Cyclone II. A figura 7 indica

o atraso de 49,2 nano segundos do processador da empresa

ALTERA. Já na figura 08 apresenta um atraso de 42 nano

segundos do processador da empresa XILINX.

74

A compilação dos códigos fonte escritos em VHDL,

permitiu a verificação da compatibilidade entre as duas

tecnologias. Este resultado é interessante do ponto de vista do

projetista, pois essa compatibilidade permite ao desenvolvedor

mudar a plataforma tecnologica sem modificações

significativas na estrutura do hardware.

5 Discussão

Por meio dos resultados apresentados, observa-se que a

família Cyclone II possui mais atributos quando comparada

com a Spartan-3E. No entanto, avaliando valores comerciais,

torna-se mais onerosa alta produção de produtos que incluam

UNOPAR Cient. Exatas Tecnol., Londrina, v. 10, n. 1, p. 69-75, Nov. 2011

CONFORTO, J.; VALLIM M.B.R.

o FPGA da família Cyclone II. Seus valores comerciais

variam entre $14.08 para o modelo mais simples até

$422.40 (ALTERA CORPORATION, 2010) para modelos

sofitiscados, enquanto a Spartan-3E oferece dispositivos entre

$9.88 e $122.13 (AVNET PARTBUILDER, 2010).

6 Conclusão

O estudo comparativo entre os FPGAs descrito neste

artigo, baseou-se em grande parte na descrição da arquitetura

interna presente nestes dispositivos, sendo estes as unidades

lógicas que armazenam a função de cada parte do chip, os

blocos de entrada e saída que fazem a interface com o meio

externo e a arquitetura de interconexão entre os módulos.

Verificou-se que a importância da computação

reconfigurável é notável em vários segmentos do mercado

de componentes eletrônicos, pois com a utilização destes

dispositivos, a prototipação de sistemas digitais permite

economias de tempo e dinheiro, tendo a sua realização

facilitada pela grande evolução tecnológica presenciada

atualmente.

Como proposta de continuidade, visa-se estudar com

mais profundidade o desempenho de cada processador,

desenvolvendo programas complexos que exija alta velocidade

de comunicação de dados.

Agradecimentos

Este trabalho é financiado pela FINEP – Financiadora

de Estudos e Projetos (REF 4971/2006). O mesmo

conta com o apoio da Fundação de Apoio à Educação,

Pesquisa e Desenvolvimento Científico e Tecnológico da

UTFPR (FUNTEF), da Fundação Araucária de Apoio ao

Desenvolvimento Científico e Tecnológico do Paraná e

do Conselho Nacional de Desenvolvimento Científico e

Tecnológico - CNPq Brasil.

UNOPAR Cient. Exatas Tecnol., Londrina, v. 10, n. 1, p. 69-75, Nov. 2011

Referências

ALTERA CORPORATION. 2010. Cátalogo de preços dos

FPGAs da família Spartan-3E. Disponível em: <http://www.

buyaltera.com/scripts/partsearch.dll?Cat=2556262&PV-5=3>.

Acesso em: 24 ago. 2010.

ALTERA CORPORATION. 2007. Cyclone II, Device Family

Data Sheet. Disponível em: <http://www.altera.com/literature/

hb/cyc2/cyc2_cii5v1_01.pdf>. Acesso em: 12 jul. 2010.

ALTERA CORPORATION. 2004. Section IV. I/O Standards.

Disponível em: http://pdf1.alldatasheet.com/datasheet-pdf/

view/146756/ALTERA/EP2C35.html>. Acesso em: 12 jul. 2010.

AVNET PARTBUILDER, 2010. Cátalogo de preços dos FPGAs

da família Spartan-3E. Disponível em: <http://avnetexpress.

avnet.com/store/em/EMController?langId=-1&storeId=50020

1&catalogId=500201&action=products&N=0&mfr=XLX&hr

f=http://www.xilinx.com/onlinestore/silicon/online_store_s3e.

htm&term=XC3S100E-4TQ144C>. Acesso em: 24 ago. 2010.

BOBDA, C. Introduction

Alemanha: Springer, 2007.

to

reconfigurable

computing.

GOMES, V.C.F.; CHARÃO, A.S.; VELHO, H.F.C. Field

programmable gate array mini-curso de computação híbrida

reconfigurável 2009. Disponível em: <http://www.vconrado.

com/chr/fpga.pdf>. Acesso em: 23 ago. 2010.

GONÇALVES, F.A.S. Pré-regulador retificador entrelaçado

(Interleaved) ZCS-FM Boost, com controle digital através

de dispositivo FPGA e linguagem VHDL. 2005. 277 f. Tese

(Doutorado Engenharia Elétrica) – Universidade Estadual

Paulista Julio de Mesquita Filho. Ilha Solteira, 2005.

MARQUES, P.C.F. Algoritmo de roteamento maze para

dispositivos programáveis FPGA. 2002. 88 f., Dissertação

(Mestrado Ciência da computação) – Pontífica Universidade

Católica, Porto Alegre, 2002.

MORAES F.; MESQUITA D. Tendências em reconfiguração

dinâmica de FPGAs, 2005. Disponível em: <http://sites.google.

com/site/juancalegu/Tendenciasenreconfiguraciondinamicad.

pdf>. Acesso em: 25 jul. 2010.

SCHÜTZ, F. Estudos de FPGA. 128. f. Monografia (Graduação

Informática) - Universidade Estadual do Oeste do Paraná, 2000.

XILINX INC. Spartan-3E FPGA family: complete data sheet.

2008. Disponível em: <http://pdf1.alldatasheet.com/datasheetpdf/view/202147/XILINX/XC3S500E.html>. Acesso em: 12 jul.

2010.

75

Estudo Comparativo das Tecnologias de Lógica Reconfigurável Altera e Xilinx

76

UNOPAR Cient. Exatas Tecnol., Londrina, v. 10, n. 1, p. 69-75, Nov. 2011