Hardware digital

• Álgebra booleana e portas ló

lógicas

Introdução à Organização de

Computadores

Prof. Dr. Luciano José

José Senger

Aula 7

Hardware digital

• Permitem modelar o comportamento do circuito,

mas não é completa

• Para uma implementação prática, é necessário

utilizar níveis de voltagens diferentes e devem ser

considerados os atrasos dos componentes do

circuito

• Assim, a lógica booleana é uma aproximação do

que ocorre nos circuitos digitais; sua deficiência

mais importante é a incapacidade de tratar os

atrasos de propagação do sinal pelo circuito

Hardware digital

Hardware digital

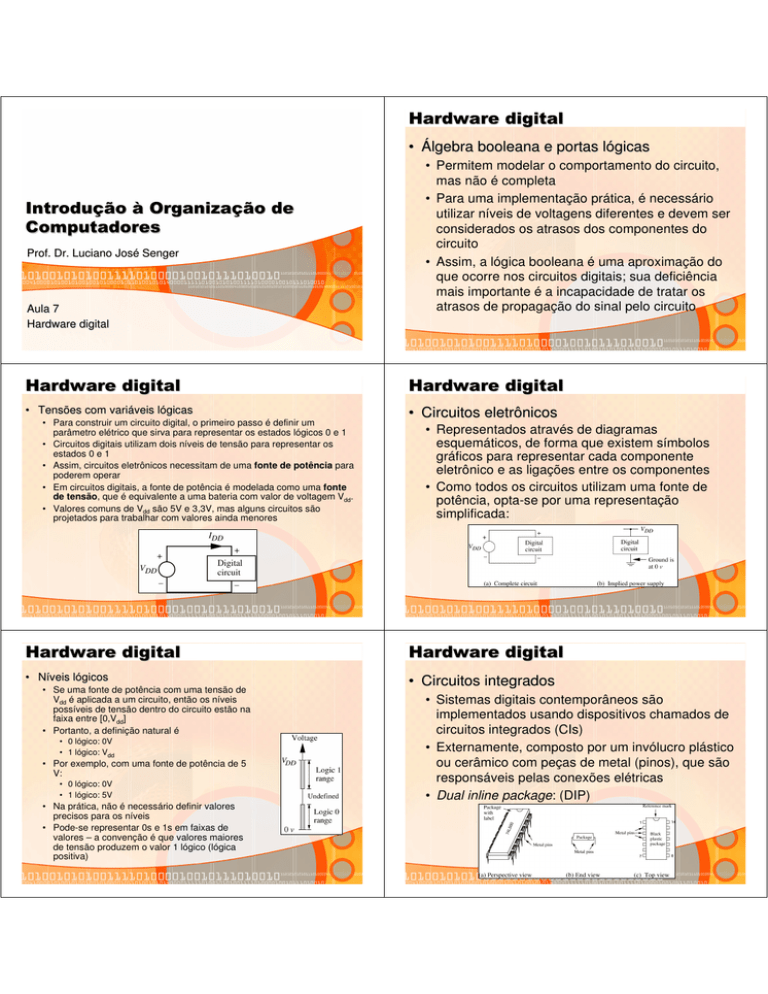

• Tensões com variá

variáveis ló

lógicas

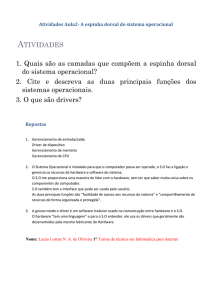

• Circuitos eletrônicos

• Para construir um circuito digital, o primeiro passo é definir um

parâmetro elétrico que sirva para representar os estados lógicos 0 e 1

• Circuitos digitais utilizam dois níveis de tensão para representar os

estados 0 e 1

• Assim, circuitos eletrônicos necessitam de uma fonte de potência para

poderem operar

• Em circuitos digitais, a fonte de potência é modelada como uma fonte

de tensão, que é equivalente a uma bateria com valor de voltagem Vdd.

• Valores comuns de Vdd são 5V e 3,3V, mas alguns circuitos são

projetados para trabalhar com valores ainda menores

• Representados através de diagramas

esquemáticos, de forma que existem símbolos

gráficos para representar cada componente

eletrônico e as ligações entre os componentes

• Como todos os circuitos utilizam uma fonte de

potência, opta-se por uma representação

simplificada:

Hardware digital

Hardware digital

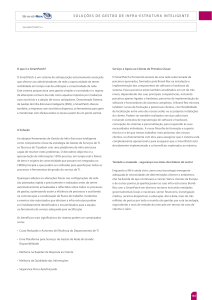

• Níveis ló

lógicos

• Circuitos integrados

• Se uma fonte de potência com uma tensão de

Vdd é aplicada a um circuito, então os níveis

possíveis de tensão dentro do circuito estão na

faixa entre [0,Vdd]

• Portanto, a definição natural é

• 0 lógico: 0V

• 1 lógico: Vdd

• Por exemplo, com uma fonte de potência de 5

V:

• 0 lógico: 0V

• 1 lógico: 5V

• Na prática, não é necessário definir valores

precisos para os níveis

• Pode-se representar 0s e 1s em faixas de

valores – a convenção é que valores maiores

de tensão produzem o valor 1 lógico (lógica

positiva)

• Sistemas digitais contemporâneos são

implementados usando dispositivos chamados de

circuitos integrados (CIs)

• Externamente, composto por um invólucro plástico

ou cerâmico com peças de metal (pinos), que são

responsáveis pelas conexões elétricas

• Dual inline package: (DIP)

Hardware digital

Hardware digital

• Circuitos integrados

• Níveis de integraç

integração

Hardware digital

Hardware digital

• Implementaç

Implementação eletrônica de portas ló

lógicas

• Implementaç

Implementação eletrônica de portas ló

lógicas

• A integração de um circuito mede o número de portas

lógicas implementadas em um CI

• SSI (Small scale integration): têm um número reduzido de

portas, que servem para a prototipação rápida de circuitos

digitais ou para glue logic

• MSI (Medium scale integration): descrevem blocos digitais

mais complexos, como somadores; algumas centenas de

portas lógicas

• LSI (Large scale integration): até 100 mil portas; exemplos

são calculadoras e pequenos processadores

• VLSI (Very large scale integration): milhões de transistores;

microprocessadores modernos de 16 a 32 bits

• ULSI (Ultra large scale integration): bilhões de transistores!

• Nota: VLSI x ULSI confundem-se na literatura

• Eletricamente, portas lógicas têm terminais de

energia que não são normalmente mostrados

• Portas lógicas são compostas de dispositivos

eletrônicos chamados de transistores, que tem uma

propriedade fundamental que os permite controlar

Terminais de

energia

Símbolo do

transistor

Transistor usado

como inversor

Funcão de transferência

Para um inversor

um sinal elétrico forte a partir de um sinal fraco

Hardware digital

Hardware digital

• Implementaç

Implementação eletrônica da ló

lógica

• Implementaç

Implementação eletrônica da ló

lógica

• Quando não existe uma voltagem positiva na base, a corrente não fluirá

de Vcc para GND. Dessa forma, para um inversor, um 0 lógico na base

irá produzir um 1 lógico no terminal no coletor

• Se uma voltagem positiva for aplicada em Vin, então a corrente fluirá de

Vcc para GND, o que impedirá que Vout produza um sinal suficiente para

a saída do inversor ser igual ao 1 lógico

• O relacionamento de entrada e saída do transistor segue uma curva não

linear.

• Desde que sempre haverá uma corrente fluindo em Vout

mesmo quando temos um 0 lógico, é necessário a utilização

de margens de segurança

• Faixas de segurança variam entre as tecnologias

Hardware digital

Hardware digital

• Implementaç

Implementação eletrônica da ló

lógica

• Tempos de atraso ló

lógico

• Portas podem ser implementadas utilizando a

propriedade de chaveamento do transistor

• Porta ideal

• Situação real e tempo de chaveamento de saída

Hardware Digital

Hardware digital

• Tempos de atraso ló

lógico

• Tempos de atraso ló

lógico

• Tlh: tempo de subida

• Thl: tempo de descida

• Por convenção, os intervalos de tempo não são medidos

entre 0 e Vdd, mas representam a transição necessária

entre 10 e 90% dos níveis de tensão

• O valor mínimo absoluto de tempo para um porta alternar

o valor de saída

A

td

td

• Tempo de chaveamento de saída

1

A

Out

B

B

Out

td

• Tmin = Tlh+ thl

• Frequência máxima de chaveamento (Hz)

• Fmax = 1 / (Tmin)

Efeito do tempo de atraso lógico em portas

• Circuitos atuais operam na faixa de nanossegundos

Hardware digital

Hardware digital

•

• Tempos de atraso ló

lógico

Tempos de atraso ló

lógico

•

Tempo de chaveamento de saída

•

•

Exemplo: Considere um inversor calculado para ter

Tlh=7,2ns e Thl=3,9ns

A máxima frequência do sinal é dada por:

•

•

•

Fmax = 1 / ((7,2 x 10^-9) + (3,9 x 10^-9))

Fmax = 90,09 MHz

Questões

1. Calcular a frequência máxima de operação de um

inversor com Tlh=8,0 ns e Thl=2,0 ns

2. Calcular o tempo de chaveamento de saída de um

inversor que trabalha com uma frequência máxima de

100 MHz e tem os valores de Tlh e Thl iguais.

• Atraso de propagação

• Apesar da borda de descida e de subida de uma forma de onda de saída de

uma porta lógica ser caracterizada pelo intervalo de tempo de Tlh e Thl, estas

medidas são incômodas de realizar em toda porta lógica

• No nível de projeto lógico, é mais simples representar um atraso único que

corresponde a média dos tempos de chaveamento

• O atraso lógico da propagação (tp) de entrada é definido com a utilização

de dois intervalos básicos:

• Tp = ½ ( pHL + pLH)

• Ou ainda: tp = max(PHL, PLH)

Hardware Digital

Hardware digital

•

• FanFan-in e FanFan-out

FanFan-in e fanfan-out

•

•

•

•

Se considerarmos que a quantidade de água num balde corresponde ao seu valor de

tensão, ou seja “0” = pouca água no balde e “1” = muita água, então considerando o

primeiro caso, verifica-se que uma só torneira, escoando uma taxa de água fixa, poderá

apenas encher um número limitado de baldes e por isso quantos mais baldes, pior será o

seu desempenho

Verifica-se ainda que se a torneira escoar uma quantidade fixa por segundo, então

quantos mais baldes, mais tempo (maior atraso) demorará a encher esses mesmos

baldes. A este fenômeno chama-se de fan-out

No segundo caso, temos a situação para a qual queríamos ter a quantidade mínima de

água nos baldes, se as torneiras precedentes escoarem em paralelo, então quantas mais

torneiras, mais água irá existir no balde até se poder atingir a situação de balde cheio

A este fenômeno chama-se de fan-in, que é o número máximo de torneiras que podem

escoar água do balde, mantendo o balde o mais vazio possível de modo a não atingir o

valor de comutação (valor de limiar de ativação do transistor)

• O tempo de chaveamento de uma porta lógica depende do

número de portas alimentadas pela saída

• O Fan-out de uma porta é o número de portas que pode ser

alimentado na saída e depende de como a porta é utilizada

na sequência lógica

• Também denominado de fator de acionamento de carga, o

FAN-OUT é o número máximo de entradas lógicas que uma

saída pode acionar com segurança.

• Se o valor estabelecido pelo FAN-OUT for excedido, a

tensão de nível lógico de saída não poderá ser mais

garantida.

• O fan-out ocorre devido ao consumo de energia das portas ligadas

na saída

• O valor de fan-out depende da tecnologia empregada:

• TTL: 2 a 10

• CMOS: 50 a 100

Hardware digital

Hardware Digital

• FanFan-in e FanFan-out

• Fan-out causa atraso de propagação

proporcionalmente ao número de portas

conectadas

Hardware digital

Hardware digital

• FanFan-in e fanfan-out

• Extensão para outras portas ló

lógicas

• Fan-out

• Traçada em função do fan-out, a linha pontilhada mostra

que o atraso de propagação aumenta linearmente com o

número de fan-out (N). Isto significa que projetos que

utilizam grandes fan-outs apresentam atrasos maiores

• Toda porta digital é caracterizada por um conjunto de

atrasos de tempo intrínsecos

• O atraso depende (1) da porta e (2) da carga que ela alimenta

• Quando projeta-se circuitos lógicos na prática, devemos considerar

tanto a formação da lógica quanto o comportamento temporal do

hardware

Hardware digital

Hardware digital

• Lógica em seqü

seqüência

• Lógica em seqü

seqüência

• O atraso de propagação de cada porta contribui para o

atraso de um sinal lógico através de uma cascata de portas

• Td = td1 + td2 + td3 + td4

• As primeiras três portas têm fan-out de 1:

• Tdn = tp0,NOT + TpL, NOT (n=1,2,3)

• Td4 = Tp0,NOT + TL (TL é o atraso devido carga em B)

• Td = 4.tp0,NOT + 3.tpL,NOT + tL

• Td1 = tp0,NOT + 3.tpL,NOT

• Td3 = tp0,NOT + 2.tpL,NOT

• Td = 4.tp0,NOT + 6.tpL,NOT + TL

Hadware Digital

Hardware digital

• Lógica em sequência

• Lógica em seqü

seqüência

• Cada tipo de porta necessita de um tempo para ser

ativada, e assim, a contribuição no atraso de

propagação é diferente para cada tipo de porta

• Obtem-se o atraso total pelo

somatório dos atrasos parciais:

• Output

• Td = td1 + td2 + td3

• Td = (tp0,NOT + TpL,NOR) + (tp0,NOR +

tpL,NOT) + (tp0,NOT + tL)

• Out1

• Td,Out1 = td1 + td3

• (Tp0,NAND + TpL,NOR + tpL,NOT) +

(tp0,NOT + TL)

• Out2

• Td,Out1 = td1 + td2

• (Tp0,NAND + TpL,NOR + tpL,NOT) +

(tp0,NOR + TL)

Hardware digital

Hardware digital

• Outros atrasos

• Outros atrasos

• Como os componentes (portas) necessitam ser

interligados, existem atrasos causados pelo meio

de propagação

• Linha de transmissão

• Velocidade = (3 x 10^8 m/s) / n

• N >= 1, constante que leva em conta as propriedades de

armazenamento de energia pelo cabo

• Crosstalk: energia do sinal é transmitido para um

outro fio vizinho

Hardware digital

Hardware digital

• Famí

Famílias ló

lógicas

• Famí

Famílias ló

lógicas

•

•

Sistemas digitais são construídos a partir de portas lógicas.

Até 1955 utilizavam-se diodos, válvulas e resistores para construção de circuitos digitais, que:

•

•

•

•

•

Com a invenção do transistor e sua disponibilização comercial tal situação modificou-se.

Portas lógicas montadas com transistores e resistores caracterizam-se por:

•

•

•

•

•

•

fisicamente grandes,

consumirem muita potência e

serem caros.

serem relativamente compactas,

consumirem pouca potência e

terem baixo custo.

A partir de 1965 diversos transistores, diodos e até resistores passaram a ser integrados numa única

pastilha de silício, denominada Circuito Integrado (CI).

A consequência direta desta evolução foi a redução das dimensões, consumo e custo das portas

lógicas.

O microprocessador Pentium 4 da Intel tem 42 milhões de transistores, usando uma arquitetura de

fabricação de 130 nanômetros: cada transistor fica distanciado dos outros por 130 milionésimos de um

milímetro.

• Portas lógicas implementadas com a mesma tecnologia são

pertencentes a mesma família

• CMOS (semicondutor complementar de metal-óxido)

• Transistores de efeito de campo, altíssimo fan-out (centenas)

• Fonte de alimentação: Vdd = 5V, podem operar de 5 a 15V, ou em faixas

menores (3,3 V)

• Níveis lógicos entre [0, Vdd]

• Atraso de propagação da ordem de 0,1 nanossegundo

• TTL (Lógica transistor-transistor)

•

•

•

•

•

Glue-logic

Fonte de alimentação de Vdd=5V

Transistores bipolares, grandes, aquecem com mais facilidade, rápidos

Níveis lógicos entre [0,3; 3,6]

Atraso de 9 ns

• ECL (lógica de acoplamento de emissor)

•

•

•

•

Hardware digital

• Leituras recomendadas

• Uyemura

• http://www.intel.com/technology/silicon

• http://www.inf.ufrgs.br/gme/education/posgraduaca

o/cmp115/

Rápida, geram muito calor, consomem bastante potência, fan-out de 25

Fonte de alimentação entre 0 e -5,2 V (lógica negativa)

Níveis lógicos com diferenças de 0,2 V (tempo de chaveamento rápido)

Atraso de propagação de 50 picossengundos