SISTEMAS DIGITAIS

MEMÓRIAS E

CIRCUITOS DE

LÓGICA PROGRAMÁVEL

H. Neto, N. Horta, J.P. Carvalho

Sistemas Digitais

1

MEMÓRIAS - 2

! SUMÁRIO:

! MEMÓRIAS INTEGRADAS

!

RAMs

!

ROMs

! LÓGICA PROGRAMÁVEL

!

PROMs

!

PLAs

!

PALs

!

FPGAs

! IMPLEMENTAÇÃO DE MÁQUINAS DE ESTADO UTILIZANDO LÓGICA

PROGRAMÁVEL

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

2

MEMÓRIAS - 3

! MEMÓRIAS

• Flip-Flops: Elementos básicos de memória; 1 bit.

• Registos: Armazenamento de 1 palavra de N bits;

• Memórias: Armazenamento de K palavras de N bits;

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

3

MEMÓRIAS - 4

! TIPOS

de MEMÓRIAS

• RAMs – Random Access Memory

• ROMs

• ROMs (Read Only Memory): Memória apenas de leitura, sendo o conteúdo

definido durante o fabrico.

• PROM (Programable Read Only Memory): Memória programável pelo

utilizador uma única vez.

• EPROMs

(Erasable Programable ROM): ROM com capacidade de

reprogramação; a memória pode ser apagada através de radiação ultravioleta

intensa.

• EEPROMs (Electrically Erasable Programable ROM): ROM reprogramável

que pode ser apagada electricamente.

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

4

MEMÓRIAS - 5

! RAM (Random Access Memory) - MODELO LÓGICO DA ESTRUTURA

BASE

Linha_0

C1

1D

Linha_1

C1

DMUX

A0

A1

}

0

1

G

_

0

3

0

2

ChipSelect

EN

1D

1

Linha_2

3

C1

1D

Linha_3

C1

1D

Entrada_Dados

Saída_Dados

Selecciona

Coluna

WriteEnable_H

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

5

MEMÓRIAS - 6

! RAM - MODELO SIMPLIFICADO

RAM – “Random Access Memory”

74189

RAM 16x4

Endereço

A0

0

A1

1

A2

2

A3

3

CS_L

G1

WE_L

1 EN [READ]

A

Operação de Escrita:

(1) Colocar endereço nas linhas de endereço;

(2) Colocar dados nas linhas de entrada de dados (Ds);

(3) Activar CS_L e WE_L (L - Escrita).

0

15

1C2 [WRITE]

D0

1, 2D

A,2D

D1

Entrada de

Dados

1,A

Q0

Q1

D2

Q2

D3

Q3

H. Neto, N. Horta, J.P. Carvalho

Operação de Leitura:

(1) Colocar endereço nas linhas de endereço;

(2) Activar CS_L e Desactivar WE_L (H – Leitura);

(3) Ler dados pretendidos nas linhas de saída (Os).

Saída de

Dados

SISTEMAS DIGITAIS

6

MEMÓRIAS - 7

! RAM - ESTRUTURA TIPO

EXEMPLO:

RAM 16x1 (16

linhas de 1 bit

cada), organizada

segundo uma

matriz de 4x4 bits.

DMUX

}

A2

0

A3

1

0

_

0

G

3

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

1

2

3

ChipSelect

EN

Descodificador

de Linha

Entrada_Dados

WriteEnable_H

Saída_Dados

DMUX

}

A0

0

A1

1

ChipSelect

EN

0

_ 1

0

G

3

2

3

Descodificador

de Coluna

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

7

MEMÓRIAS - 8

! RAM - ESTRUTURA TIPO

EXEMPLO:

Uma RAM 8x2 (8 linhas

de 2 bits cada),

organizada segundo a

mesma matriz de 4x4

bits.

DMUX

}

A1

0

A2

1

0

_

0

G

3

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

1

2

3

ChipSelect

EN

Descodificador

de Linha

Entrada_Dados 0

Entrada_Dados 1

WriteEnable_H

Saída_Dados 0

Saída_Dados 1

DMUX

A0

ChipSelect

0

0 G_

1

0

1

EN

Descodificador

de Colunas

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

8

MEMÓRIAS - 9

! RAM - ASSOCIAÇÃO

Aumento da Dimensão das Palavras (de 4 para 8 bits):

74189

RAM 16x4

74189

RAM 16x4

A0

0

A1

1

A2

2

A3

3

3

CS_L

G1

G1

WE_L

1 EN [READ]

1 EN [READ]

1C2 [WRITE]

1C2 [WRITE]

D0

H. Neto, N. Horta, J.P. Carvalho

0

A

0

1

15

2

A

0

15

Q0

D4

D1

Q1

D5

Q5

D2

Q2

D6

Q6

D3

Q3

D7

Q7

1, 2D

A,2D

1,A

SISTEMAS DIGITAIS

1, 2D

A,2D

1,A

Q4

9

MEMÓRIAS - 10

! RAM - ASSOCIAÇÃO

Aumento do Número de Palavras (de 16 para 32 palavras):

74189

RAM 16x4

74189

RAM 16x4

A0

0

A1

1

A2

2

A3

3

A4

G1

WE_L

1 EN [READ]

1 EN [READ]

1C2 [WRITE]

1C2 [WRITE]

D0

0

A

0

1

15

2

A

0

15

3

A4

G1

Q0

D0

D1

Q1

D1

Q1

D2

Q2

D2

Q2

D3

Q3

D3

Q3

1, 2D

A,2D

1,A

1, 2D

A,2D

1,A

Q0

Nota: Por simplicitade omitiram-se as ligações das entradas D e das saídas Q

das duas memórias ao BUS de Dados

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

10

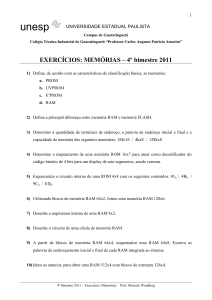

MEMÓRIAS - 11

! ROM - SIMBOLOGIA

ROM 32x8

A0

0

A1

1

A2

2

A3

3

A4

4

RE_L

EN

A

1, 2D

0

31

A

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

11

MEMÓRIAS - 12

! ROM – ESTRUTURA TIPO

EXEMPLO: ROM 4x3 que armazena os 4 primeiros números primos:

A1 A0

"0"

A1 A0 Q2 Q1 Q0

0

0

0

1

0

Plano OR

m0

2

0

1

0

1

1

3

1

0

1

0

1

5

1

1

1

1

1

7

m1

m2

m3

Plano AND

Q2

Q1

Q0

A programação da ROM é concretizada pela efectivação das ligações entre as saídas das

ANDs e as entradas das ORs.

Nota: As linhas sem ligação são, por defeito, ligadas a “0” (elemento neutro da OR).

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

12

MEMÓRIAS - 13

! LÓGICA PROGRAMÁVEL

Nesta secção referem-se algumas estruturas, derivadas da estrutura básica de uma

ROM, cujo objectivo está centrado na sua programação para implementação de funções

combinatórias e não na sua utilização como memória.

PLDs - Programmable Logic Devices

PROM

Ligações

Programáveis

"Array" de ORs

Programável

Saídas

PLA-"Programmable Logic Array"

Ligações

"Array" de ANDs Programáveis

Entradas

Programável

"Array" de ORs

Programável

Saídas

PAL-"Programmable Array Logic"

Ligações

"Array" de ANDs Programáveis

Entradas

Programável

"Array" de ORs

Fixo

Saídas

Entradas

H. Neto, N. Horta, J.P. Carvalho

"Array" de ANDs

Fixo

(Descodificador)

SISTEMAS DIGITAIS

13

MEMÓRIAS - 14

! FPGAs – “FIELD PROGRAMMABLE GATE-ARRAYS”

As FPGAs são circuitos programáveis que permitem realizar circuitos de complexidade

equivalente a até algumas centenas de milhar de portas lógicas.

O tipo de programação usado nas FPGAs mais populares baseia-se na utilização de

memórias RAM distribuídas para realizar as funções lógicas e controlar as interligações do

circuito.

Bloco lógico

Zona de interligações

Célula de entrada/saída

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

14

MEMÓRIAS - 15

! BLOCO LÓGICO BÁSICO DE UMA FPGA

O bloco lógico básico de uma FPGA é constituído tipicamente por uma LUT – “Look-Up

Table” e um FF D.

A LUT é simplesmente uma pequena RAM (são habitualmente utilizadas LUTs de 4

entradas = RAM de 16 bits) que, para efeitos de utilização do circuito, funciona apenas

em modo de leitura (a escrita corresponde à programação da função lógica).

A programação da lógica consiste no armazenamento na LUT da tabela de verdade da

função lógica a realizar.

O controlo (programável) do MUX permite incluir/excluir o FF no/do circuito.

}

RAM 16X1

X0

X1

X2

X3

0

1

2

__

0

A

15

3

R

1D

MUX

G1

Q

0

1

C1

S

CLK

S/R

Controlo

S/R

Bloco Básico – Modelo simplificado

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

15

MEMÓRIAS - 16

! MÁQUINAS DE ESTADO E MEMÓRIAS

A estrutura de uma máquina de estados permite que se utilizem memórias (para implementar

o circuito combinatório) conferindo a possibilidade de tornar os sistemas de controlo

programáveis, ou seja, mais versáteis, e permitindo o desenvolvimento de sistemas

funcionalmente mais complexos sem o aumento correspondente da complexidade do

hardware.

Qual o preço a pagar por esta solução em relação à implementação clássica?

Máquina Sequencial (Sincrona)

Modelo Geral

Entradas

Actuais (x)

C.C.

(Circuito

Combinatório)

*

*

*

*

*

*

Saídas

Actuais (z)

Estado

Seguinte

(ES)

Estado

Actual

(EA)

*

*

*

Memória

(Flip-Flops)

*

*

*

CP

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

16

MEMÓRIAS - 17

! MÁQUINAS DE ESTADO E MEMÓRIAS (cont.)

EXEMPLO: Máquina de Distribuição de Pastilhas

(conforme analisada no capítulo dos Circuitos Sequenciais Síncronos)

Reset

Entradas: m5,m10

Saída: abre

00

S0/0

10

00

00

S5C

0

1

S10C

1

0

S15C

1

1

S5/0

10

01

Estado Actual

Q1 Q0

S0C

0

0

01

S10/0

01,10

S15/1

H. Neto, N. Horta, J.P. Carvalho

XX

Entradas

m5

m10

0

0

0

1

1

0

1

1

0

0

0

1

1

0

1

1

0

0

0

1

1

0

1

1

0

0

0

1

1

0

1

1

SISTEMAS DIGITAIS

Estado Seguinte

Q1 Q0

S0C

0

0

S10C

1

0

S5C

0

1

X

X

X

S5C

0

1

S15C

1

1

S10C

1

0

X

X

X

S10C

1

0

S15C

1

1

S15C

1

1

X

X

X

S0C

0

0

S0C

0

0

S0C

0

0

X

X

X

Saída

ABRE

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

17

MEMÓRIAS - 18

! MÁQUINAS

DE ESTADO E

MEMÓRIAS (cont.)

Tabela de Memória

EXEMPLO: Máquina de Distribuição de Pastilhas

(cont.)

Tendo por base a Tabela de Transição de Estados e a

memória RAM apresentada anteriormente utiliza-se

esta memória para implementar a função do circuito

combinatório, i.e., determinar o Estado Seguinte e a

Saída.

Nas variáveis de endereço de Memória (A3 A2 A1 A0)

representam-se as variáveis de estado (Q1 Q0) e as

entradas (M5 M10). Assim, as linhas de endereço

deverão conter todas as combinações possíveis de

Estado Presente e entradas possíveis nesse estado.

A Palavra de Memória de cada endereço deverá conter

a informação do Estado Seguinte, Q1 Q0 (n+1) e Saída,

Z (n).

Nota: A cinzento indicam-se os endereços não

utilizados e as saídas não consideradas (bit mais

significativo).

H. Neto, N. Horta, J.P. Carvalho

Endereço

Conteúdo

A3

A2

A1

A0

Q3

Q2

Q1

Q0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

1

1

0

1

1

1

0

0

0

0

0

0

0

1

0

1

1

0

0

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

SISTEMAS DIGITAIS

18

MEMÓRIAS - 19

! MÁQUINAS DE ESTADO E MEMÓRIAS (cont.)

EXEMPLO: Máquina de Distribuição de Pastilhas (cont.)

RAM 16x4

ENTRADAS

M10

0

M5

1

2

A 0

15

3

RESET_L

CP

R

'0'

G1

'1'

1 EN [READ]

C1

1D

1C2 [WRITE]

Q0(n)

1, 2D

A,2D

Q1(n)

SAÍDA

Z

1,A

Q0(n+1)

ESTADO

PRESENTE

Q1(n+1)

ESTADO

SEGUINTE

Nota: Existem outras formas alternativas para este tipo de implementação “microprogramada”,

mais complexas, mas mais eficientes.

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

19

MEMÓRIAS - 20

BIBLIOGRAFIA

[1] Arroz,G., Monteiro,J.C., Oliveira,A., “Arquitectura de Computadores, dos Sistemas Digitais aos

Microprocessadores”, Secções 6.8 e 7.5.3, 2ª Edição, 2009

[2] M. Morris Mano, Charles R. Kime, Logic and Computer Design Fundamentals , Prentice-Hall

International, Inc. (Capítulo 6, Secções 6.1 a 6.9)

H. Neto, N. Horta, J.P. Carvalho

SISTEMAS DIGITAIS

20