Técnicas de Projeto de

Compatibilidade Eletromagnética (CEM)

no desenvolvimento de

Placas de Circuito Impresso

Prof. Rodrigo Cutri

2005

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

2

Índice :

1 . Introdução ................................................................................... 5

2. Comportamento não-ideal dos componentes ..................................... 6

2.1 Efeito Pelicular .................................................................................... 6

2.2 Espaçamento entre os terminais dos componentes.............................. 6

2.3 Análise da influência da variação da freqüência no comportamento

dos Resistores ............................................................................................ 8

2.4 Análise da influência da variação da freqüência no comportamento

dos Capacitores ........................................................................................ 10

2.5 Análise da influência da variação da freqüência no comportamento

dos Indutores............................................................................................ 12

3. PROBLEMAS DE EMC x LAYOUT ............................................ 13

3.1 Desacoplamento................................................................................. 14

3.2 Impedância de Plano de Terra e Trilhas num PCB ........................... 18

3.3 Crosstalk ............................................................................................ 23

3.4 Efeitos de Linhas de Transmissão ..................................................... 25

3.5 Descargas Eletrostáticas .................................................................... 27

4. Observações sobre a elaboração de um layout de PCB....................... 29

5. Bibliografia ................................................................................ 30

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

3

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

4

1 . Introdução

A Eletrônica de Potência é o campo da engenharia que usa a eletrônica para processar a

energia utilizada em diversos equipamentos elétricos, utilizando freqüências maiores

que as da rede (50/60 Hz) e processando sinais elevados de tensões e correntes não

senoidais. Geram-se assim sinais elétricos e campos eletromagnéticos, conduzidos ou

irradiados, que podem vir a afetar prejudicialmente outros equipamentos próximos.

Além de emitir interferências eletromagnéticas, os circuitos de controle podem ser

afetados por interferências provenientes de outros circuitos ou fenômenos naturais.

Estes fenômenos são casos de estudo de compatibilidade eletromagnética. A

Compatibilidade Eletromagnética é a capacidade de sistemas elétricos e eletrônicos,

equipamentos e dispositivos de operar num ambiente eletromagnético sem sofrer ou

causar degradações inaceitáveis devidas à interferência magnética. A energia

eletromagnética

pode se propagar pelo espaço, sendo este fenômeno chamado de

Emissão Irradiada, ou pelos cabos e conexões, chamado Emissão Conduzida.

As etapas relevantes ao estudo da Interferência Eletromagnética na Eletrônica de

Potência dividem-se aproximadamente em 1/3 no desenvolvimento do esquema elétrico;

1/3 na escolha dos componentes e 1/3 no layout e montagem dos componentes na placa

de circuito impresso.

A importância de um bom layout na confecção de placas de circuito impresso é de

fundamental importância a fim de evitar/atenuar as interferências eletromagnéticas no

circuito. Deve-se utilizar com parcimônia as rotinas de auto-roteamento dos softwares

de confecção de placas, pois geralmente estes apenas fazem as conexões dos nós não se

preocupando com outros aspectos como as influências e interferências eletromagnéticas

entre os componentes.

Este trabalho expõe e analisa, sob um ponto de vista qualitativo, as causas e

conseqüências das interferências eletromagnéticas quando da concepção de um layout

de uma placa de circuito impresso, conhecida simplesmente por PCB (Printed Circuit

Board).

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

5

Primeiramente analisa-se o comportamento de alguns dos principais

componentes

eletrônicos sob a influência de altas freqüências. A seguir destacam-se alguns dos

principais problemas encontrados e as soluções adotadas.

2. Comportamento não-ideal dos componentes

Neste item, primeiramente discute-se qual a influência da freqüência e do espaçamento

entre os terminais no comportamento dos componentes. A seguir, é apresentado

sucintamente qual o comportamento dos principais componentes eletrônicos (resistor,

indutor e capacitor) quando da variação da freqüência do sinal aplicado sobre os

mesmos.

2.1 Efeito Pelicular

Os condutores de um sistema (vias e ilhas de uma PCB) apresentam um comportamento

longe do ideal, (ou seja, o comportamento do sinal transmitido pode sofrer influências

que não estavam previstas) quando sujeitos a trabalhar em altas freqüências. O efeito

pelicular é uma das causas desse desvio de comportamento. Ele consiste na

transmissão do sinal apenas na camada mais externa do condutor. A transmissão do

sinal pela da área do condutor vai diminuindo conforme se aumenta a freqüência do

sinal transmitido, ou seja, quanto maior a freqüência, menor área útil da secção do

condutor estará sendo utilizada para a transmissão do sinal. Caso o sinal produza uma

corrente do tipo contínua ou com baixas freqüências a distribuição do sinal é

praticamente uniforme sobre todas as seções das vias e ilhas.

2.2 Espaçamento entre os terminais dos componentes

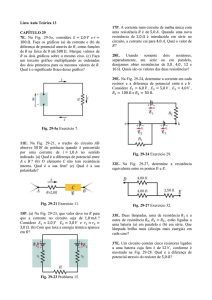

O espaçamento entre os terminais dos componentes é uma outra causa no desvio do

comportamento ideal dos componentes. O aumento do espaçamento entre os

componentes provoca em altas freqüências a adição de efeitos indutivos e capacitivos

que devem ser considerados para a análise dos componentes (Figs.2-1 e 2-2). Uma

solução para evitar/atenuar o aparecimento destas indutâncias e capacitâncias parasitas é

a utilização de componentes que permitem sua soldagem diretamente a placa,

minimizando-se ao máximo o tamanho de seus terminais.

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

6

(a)

comprimento

do terminal

i

Componente

Terminais

(b)

comprimento

do terminal

L

Componente

Terminais

Fig.2-1 Modelamento dos efeitos dos campos magnéticos devido aos terminais dos

componentes: (a) modelo físico (b) circuito equivalente

(a)

comprimento

do terminal

+++++++

+

Terminais

V

Componente

- - - - - - -

(b)

Terminais

comprimento

do terminal

C

Componente

Fig.2-2 Modelamento dos efeitos dos campos elétricos devido aos terminais dos

componentes: (a) modelo físico (b) circuito equivalente

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

7

2.3 Análise da influência da variação da freqüência no

comportamento dos Resistores

Os resistores são basicamente construídos de três formas: com carbono, com fio

enrolado e com filme. A resposta em freqüência ideal de um resistor é dada pela Fig.23.

R

(b)

(a)

Z

Z

R

0

f

f

Fig.2-3 Resposta em freqüência da impedância de um resistor ideal: (a) módulo (b) fase

Na maioria dos circuitos eletrônicos, os resistores de carbono são os mais utilizados,

pois não estão sujeitos a alterações com altas freqüências, apresentando como

desvantagem a alta tolerância. Resistores de fio enrolado apresentam uma precisão de

resistência maior, mas devido à sua forma construtiva apresentam uma indutância em

série com o elemento resistivo. Esta indutância tem seu efeito acentuado em altas

freqüências de chaveamento e rápidos tempos de subida e descida do sinal (di/dt

elevados). Além da indutância própria devido ao processo construtivo, contribui a

indutância e a capacitância devido ao espaçamento dos terminais conforme visto no

item 2.2. A curva de resposta em freqüência do resistor é apresentada na Fig.2-4 .

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

8

(a)

L(terminal)

Terminais

R

C(terminal)

C(terminal)

L(terminal)

(b)

R

(c)

Z

Z

90

R

0

-90

f

f1

f

f2

f1

f2

FIG.2.4 – Comportamento não ideal do Resistor

Observa-se nas Figs. 2-4 e 2-5 que sob determinadas freqüências o resistor passa a

apresentar comportamento mais capacitivo (f1<f<f2) ou indutivo (f>f2).

(a) Dc

R

C(terminal)

(b)

R

b) f =

1

2πR.Cter min al

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

9

C(terminal)

L(terminal)

(c)

R

c) f =

1

2π Lter min al .Cter min al

(d)

R

→ ∞

d) f

FIG.2-5 – Comportamento do Resistor p/ várias freqüências

2.4 Análise da influência da variação da freqüência no

comportamento dos Capacitores

A resposta em freqüência ideal de um capacitor é dada pela Fig.2-6.

C

(b)

(a)

Z

Z

-20 dB/dec

-90

f

f

Fig.2-6 Resposta em freqüência da impedância de um capacitor ideal:

(a) módulo (b) fase

Onde sua impedância é dada por Z=1/(wC) Fase : -90º .

Segue abaixo seu modelo levando em conta suas não idealidades :

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

10

L(terminal)

Terminais

Rplacas

C(terminal)

Rdielétrico

C

L

Área A

Dielétrico

FIG.2-7 – Aspectos construtivos do Capacitor

C(terminal)

L(terminal)

(a)

R

(b)

Z

Z

90

0

-90

f

fo

f

fo

FIG.2.8 – Comportamento não ideal do Capacitor

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

11

fo =

1

2π Lter min al .C

2.5 Análise da influência da variação da freqüência no

comportamento dos Indutores

O comportamento ideal de um indutor seria :

L

(b)

(a)

Z

Z

+20 dB/dec

+90

f

f

Fig.2-9 Resposta em freqüência da impedância de um indutor ideal:

(a) módulo (b) fase

Onde sua impedância é dada por Z=wL Fase : 90º .

Segue abaixo seu modelo levando em conta suas não idealidades :

C(paralelo)

L(terminal)

(a)

Rparalelo

(b)

Z

Z

90

0

-90

Rparalelo

f1

f2

f

f

f1

f2

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

12

f1 =

R paralelo

2πL

f2 =

1

2π L .C paralelo

FIG.10 – Comportamento do Indutor p/ várias frequências

Observa-se na Figs. 2-10 que sob determinadas freqüências o indutor passa a apresentar

comportamento mais resistivo (f<f1) ou capacititvo (f>f2).

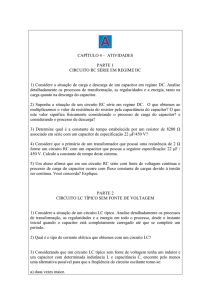

3. PROBLEMAS DE EMC x LAYOUT

Muitos problemas de EMC podem ser minimizados no projeto de uma placa de circuito

impresso pela atenção dispensada ao layout . Abaixo se seguem alguns procedimentos

que devem ser utilizados e sua posterior explicação :

- Desacoplamento

- Impedância de Plano de Terra e Trilhas num PCB

- CROSSTALK

- Efeitos de Linhas de Transmissão

- Descargas Eletrostáticas

- Emissões irradiadas

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

13

3.1 Desacoplamento

O desacoplamento é necessário quando o gate de um semicondutor, ou outro dispositivo

(chaves), necessita de uma demanda de corrente que ocorre com um tempo de

comutação muito rápido (alto di/dt) . Se a fonte de tensão deve manter o nível de tensão

durante a demanda de corrente, então, uma baixa impedância é necessária . Entretanto, é

ainda indesejável permitir que a fonte de tensão sozinha gerar pulsos rápidos de corrente

que estarão presentes nas vias do PCB podendo ocorrer crosstalks (acoplamento

eletromagnético) nas trilhas . Um capacitor de desacoplamento colocado próximo ao

dispositivo é utilizado para suprir a demanda necessária de corrente, o capacitor deve ter

capacidade suficiente para manter a tensão acima de um nível mínimo mas crucialmente

também deve ter baixa auto-indutância (Fig.11 e 12) .

FIG.11 – Desacoplamento

FIG.12 – Capacitor de Desacoplamento

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

14

No chaveamento dos circuitos (nível alto para nível baixo ou nível baixo para nível alto

– Fig.13) há a formação de loops de corrente que aumentam a possibilidade de

interferências eletromagnéticas. Loops de corrente são prejudiciais, pois os campos

magnéticos induzidos na região intermediária ao loop estão no mesmo sentido (as

correntes estão em sentidos contrários (regra da mão direita)). O ideal é diminuir as

áreas internas ao loop minimizando possíveis induções em outros ramos do circuito.

Uma das formas de se diminuir loops de corrente em CIs é através da adição de um

capacitor de desacoplamento em paralelo com o mesmo (Fig.14).

(a)

+5V

Terra

(b)

+5V

Terra

FIG.14 – Loops de corrente quando os gates da chave mudam de estado : (a) alto-parabaixo; (b) baixo-para-alto

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

15

(a)

+5V

C

C

Terra

(b)

+5V

C

C

Terra

FIG.15 – Loops de corrente quando os gates da chave mudam de estado com capacitor

de desacoplamento : (a) alto-para-baixo; (b) baixo-para-alto

Capacitores de desacoplamento devem suportar correntes de alta freqüência e possuir

baixa indutância, por essa razão capacitores de disco cerâmicos ou capacitores

multicamadas cerâmicos são preferidos . Ele deve suportar toda a corrente requerida

pelo CI durante o chaveamento, assim, o valor mínimo da capacitância pode ser

calculado por : C =

dI .dt

.

dV

Onde dV é o transitório de tensão na tensão fornecida causada pelo transitório de

corrente ocorrido no tempo dt. Por exemplo, se um CI requere uma corrente transitória

de 50 mA por 2 ns e deseja-se limitar o transitório da fonte de tensão em menos de 0.1

V, o capacitor deve ter um valor de no mínimo 0.001 uF .

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

16

A maioria dos projetistas tende a utilizar capacitores de desacoplamento que são

maiores que os necessários.

Todos os capacitores possuem indutâncias em série com sua capacitância. A indutância

é resultado da estrutura do capacitor, dos terminais do capacitor e dos caminhos

externos utilizados para conectar o capacitor aos terminais do CI. Por causa desta

combinação de capacitância e indutância, o capacitor em alguma freqüência se tornará

auto-ressonante. A auto freqüência de ressonância do capacitor tem uma impedância

muito baixa e representa um efetivo caminho de passagem para a corrente . Acima da

freqüência de auto ressonância o circuito se torna indutivo e sua impedância cresce com

a freqüência e conseqüentemente sua performance piora como capacitor de

desacoplamento. A freqüência de ressonância de um circuito LC série pode ser

calculada pela equação f =

1

2.π . L.C

.

Apresenta-se a seguir um exemplo:

Considere o caso de um capacitor de desacoplamento de 0.001 uF com uma indutância

interna de 1 nH. Se a indutância dos segmentos que conectam o capacitor ao CI for

próxima de 30 nH, o circuito será auto-ressonante em aproximadamente 29 MHz.

Para a mesma indutância um capacitor de maior valor terá uma freqüência de

ressonância menor. Assim um capacitor de desacoplamento com maior capacitância não

é a saída quando se tem baixa indutância. Da mesma forma, um capacitor menor não

teria capacidade de corrente necessária para o transitório não resolvendo assim o

problema da freqüência de ressonância. Na prática, existe um valor ótimo para cada

aplicação determinado empiricamente. Muitos experimentos foram efetuados com CIs

de 14 e 16 pinos para encontrar esse valor ótimo. Geralmente o ruído mínimo na tensão

ocorre para valores de 470 a 1000 pF . O melhor tipo (ou valor) pode ser encontrado

medindo-se o ruído de tensão considerando-se vários tipos de capacitor. O menor

capacitor que realizar a tarefa será a escolha mais adequada.

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

17

A seguir apresenta-se uma tabela com valores típicos de capacitores de desacoplamento

em aplicações com circuitos lógicos :

Família

Corrente Requerida (mA)

dV=20%

dt=

C (capacitor de

Lógica

Chaveamento

de NIR**

tempo

desacoplamento)

(mV)

subida

(pF)

Drive *

(ns)

CMOS

1

1

200

50

500

TTL

16

8

80

10

3000

STTL

30

20

60

3

2500

LSTTL

8

11

60

8

2500

ECL-10K

1

6

20

2

700

* Para um fanout de 5 gates

** Nível de Imunidade ao Ruído (V=L.di/dt) onde L = indutância dos terminais do capacitor , das trilhas

e dos terminais do CI (loop).

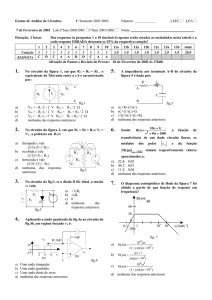

3.2 Impedância de Plano de Terra e Trilhas num PCB

Abaixo são apresentados dois possíveis layouts de circuitos analógicos :

FIG.16 – Mudança de referência de aterramento

No primeiro (Fig.16-1), a referência a terra faz com que a corrente flua através de um

caminho que inclui a impedância Zb, provocando assim uma queda de tensão em série

com o sinal, que pode causar uma instabilidade e uma distorção ao mesmo. Como pode

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

18

ser observado na figura ao lado (Fig.16-2), o simples ato de modificar o ponto de

referência remove o problema.

FIG.17 – Referência de aterramento

No circuito superior (Fig.17) , o potencial de cada aterramento (A,B,C) é afetado pelas

correntes dos outros circuitos. O que provoca um acoplamento de impedância comum,

que pode vir a se tornar um problema quando houver diferenças significativas entre as

correntes dos circuitos. O melhor arranjo seria o qual tivéssemos múltiplos pontos de

aterramento , minimizando significamente

as interferências de modo comum e

diferencial .

A redução da impedância de terra diminui as chances de instabilidade ou distorções nos

sinais transmitidos nas vias. Um plano contínuo de terra oferece uma significativa

redução da impedância comparada com a de uma única trilha do PCB . As baixas

resistência e indutância do plano de terra reduzem a impedância da fonte reduzindo o

ruído associado ao loop de terra. Deve-se lembrar que em altas freqüências, aparece

ainda o efeito pelicular que aumenta a impedância de terra. Em situações em que um

não é possível a obtenção de um plano de terra a melhor solução é fazer ao menos uma

malha (grid) de terra no PCB (Fig.18) .

FIG.18 – Grid de Terra

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

19

Uma boa solução para a construção de um plano de terra é a utilização da tecnologia

multi-layer. O uso da construção multi-layer melhora a performance do PCB em relação

aos problemas de EMC. A impedância e a indutância do plano de terra nesta

configuração são muito menores do que a de uma série de trilhas, além de que os

crosstalks entre clocks e sinais são reduzidos devido a proximidade com o plano de terra

(Figs.19 e 20).

a)

+5V

CI

CI

Terra

Área de Loop

condutor do sinal

b)

+5V

CI

CI

Terra

Terra

c)

Plano de sinais

Plano de terra

Plano +5V

PCB

FIG.19 – Redução das áreas de loop devido ao aterramento – (a) Uma configuração com

grande área de interferência; (b) uma área de interferência menor usando um retorno

exclusivo; (c) uso de planos intermediários (multilayer) para reduzir o loop de área do

caminho de retorno do sinal

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

20

FIG.20 – Multilayer

O controle do aterramento das PCBs é muito importante e deve ser contemplado na

etapa de layout. Uma solução é apresentada no exemplo a seguir:

No primeiro layout (Fig.21-a) não são levadas em consideração a influência do sinal

digital, geralmente com grandes pulsos de corrente,

sobre o CI analógico, mais

sensível, devido a impedância comum de aterramento. No segundo layout (Fig.21-b)

esta questão é considerada provendo-se um terra separado para o CI analógico e o CI

digital.

a)

b)

FIG.21 – Necessidade de terras separados – (a) layout sem separação (b) layout com

separação de terras

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

21

Loops de corrente são potenciais emissores e receptores de interferências causadas por

fontes de tensão que possuem geralmente grande conteúdo harmônico em suas

correntes. A diminuição das áreas de loop, através da aproximação das vias de ida e

retorno do sinal, ajudam a diminuir a possibilidade destas interferências (Fig.22).

FIG.22 – Diminuição de Loops aproximando as vias

Os loops de área causados pelas distâncias entre as vias de clock e sinais e seus

respectivos retornos podem ser minimizados pelo uso de terras intercalados (retornos)

adjacentes aos mesmos (Figs.23 e 24).

FIG.23 – O uso de terras intercalados (retornos) nos planos reduzem os loops de área

(a) grandes loops de área

(b) pequenos loops de área

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

22

FIG.24 – Vias de Clock e sinais e seus respectivos retornos

(a) grandes loops de área

(b) pequenos loops de área

3.3 Crosstalk

Crosstalk é o nome dado ao acoplamento eletromagnético entre ilhas do PCB que

estejam muito próximas umas das outras causando interferências internas ao próprio

sistema. Veja um caso típico:

Para evitar problemas causados por eletricidade estática é importante que o PCB esteja

próximo e paralelo ao plano de terra do chassi ou da caixa metálica que envolve o

equipamento, bem como colocar as conexões dos cabos num lugar do PCB (Fig.25), por

exemplo, considere uma descarga eletrostática se propagando através de uma base

metálica onde o equipamento esteja apoiado, o campo elétrico da onda próximo a

superfície da base deve ser perpendicular para satisfazer as condições de contorno de

campo elétrico tangencial nulo na superfície de um condutor perfeito. Colocar o PCB na

posição vertical significa que o campo magnético da descarga eletrostática estará

possivelmente perpendicular ao plano do loop do circuito. O apropriado layout de

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

23

acondiconamento do PCB em estruturas metálicas ou não metálicas ajuda a previnir o

acoplamento do campo elétrico (capacitivo) ou magnético (indutivo) para os circuitos

de qualquer descarga eletrostática induzida no interior do equipamento .

Cabo em área periférica

+

V

-

FIG.25 – Importância do Terra local

Crosstalk entre vias paralelas

O circuito mostrado abaixo (Fig.26) representa o modelo para a análise do crosstsalk, as

resistências da carga e da fonte tanto as que produzem a interferências como as que

sofrem com ela devem ser definidas. Consideráveis reduções no acoplamento capacitivo

devido ao crosstalk são obtidas com a proximidade ao plano de terra.

FIG.26 – Crosstalk devido ao acoplamento entre os condutores (Fonte do campo

induzido e Vítima do campo induzido) e o plano de terra (acoplamento capacitivo).

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

24

3.4 Efeitos de Linhas de Transmissão

Quando o tempo de propagação de uma trilha de PCB é similar em magnitude ao tempo

de transição de um dispositivo podem ocorrer oscilações, distorções do sinal e aumento

do crosstalk nas adjacências do mesmo. Nestas condições a trilha deve ser tratada como

uma linha de transmissão e determinada qual sua impedância característica para impedir

reflexões . São apresentadas a seguir duas tabelas, a primeira relaciona os tempos de

subida dos sinais típicos das principais famílias de circuitos integrados, a segunda, os

tempos de chaveamento.

Tempo de subida do sinal para CIs de acordo com as Famílias Lógicas (estimativa)

Família

Tempo de subida

Comprimento da trilha para efeitos de linha de

(ns)

Transmissão (cm)

4000B

40

365

74HC

6

53

74LS

6

53

74ALS

3,5

30

74AC

3

25

74AS

1,5

12

Imunidade das Famílias Lógicas (estimativa)

Família

Largura mínima de chaveamento (ns) para

um pulso de 3V

74HC

5,5

74LS

8

74ALS

5

74AC

2,5

74AS

1

Em virtude de termos diversos blocos de um circuito operando em freqüências distintas,

é recomendado que se faça um zoneamento (Figs.27 e 28) da área total do PCB,

distribuindo os circuitos em regiões separadas de acordo com a velocidade de trabalho

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

25

do mesmo. Isso ajuda a minimizar possíveis interferências causadas por efeitos de

linhas de transmissão em trilhas. Além do zoneamento, a blindagem eletromagnética de

determinadas regiões pode ajudar a minimizar os efeitos eletromagnéticos.

FIG.27 – Zoneamento

CABO

CONECTOR

CABO

C

O

N

E

C

T

O

R

Componentes

de alta

velocidade

Componentes

de média velocidade

C

O

N

E

C

T

O

R

CABO

Componentes

de baixa velocidade

CONECTOR

CABO

FIG.28 – Zoneamento do PCB de acordo com a velocidade dos circuitos.

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

26

3.5 Descargas Eletrostáticas

O corpo humano é uma das fontes mais comuns de eletricidade estática . A pele possui

condutividade e distribui as cargas através da superfície do corpo. A capacitância total

do corpo humano está por volta de 100 pF entre os pés e a terra , 50 pF para outros

objetos aterrados e 50 pF em contato com o espaço. A tensão pode variar de poucos kV

até 25 kV. A resistência em série pode variar de poucas centenas de ohms a milhares de

ohms. O simples contato de um corpo carregado eletrostaticamente com componentes

de uma PCB pode vir a causar uma descarga eletrostática nos mesmo danificando-os. O

correto manuseio e um ambiente de trabalho bem aterrado são as melhores

recomendações para evitar maiores conseqüências, por exemplo:

Plugar ou desplugar placas são uma das causas comuns de descargas eletrostáticas. A

placa abaixo (Fig.29-a) tem trilhas que são tocadas pela mão do usuário que transfere

sua descarga eletrostática para as trilhas da placa podendo danificá-la. Uma solução é

apresentada na placa (Fig.29-b) que tem em sua periferia um “anel de guarda” que é

conectado a terra, se o usuário for pegar a placa com a mão, a descarga eletrostática é

então transferida a terra .

(a)

(b)

FIG.29 – Descarga Eletrostática(2)

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

27

3.6 Emissões irradiadas

A circulação de correntes elétricas em condutores provoca o aparecimento de campos

eletromagnéticos que podem vir a causar interferências em outras partes do circuito.

Nas etapas de observação de possíveis causas deve ser analisada a forma de conexão

entre as placas, pois o cabo de conexão pode ser também a fonte de emissões irradiadas

(Fig.30-a). Uma solução empregada neste caso é a diminuição da corrente de

interconexão através de um buffer visando minimizar esse efeito (Fig.30-b) .

FIG.30 – Conexão entre placas

(a) corrente de interconexão elevada pode ser fonte de grandes emissões irradias (figura superior)

(b) a diminuição da corrente de interconexão minimiza a fonte de possíveis emissões irradias (figura

inferior)

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

28

4. Observações sobre a elaboração de um layout de PCB

Após a breve análise das diversas causas de interferências que devem ser observadas na

elaboração de um layout (Fig.31), apresenta-se abaixo uma lista com algumas

recomendações gerais:

-Loops áreas contendo altas correntes devem ser minimizados;

-Cada circuito integrado deve possuir um capacitor de desacoplamento;

-Vias de força devem ser separadas das vias de sinais;

-O layout do PCB deve ser demarcado para separar os circuitos ruidosos dos sensíveis;

-Os pontos de terra dos circuitos digitais devem ter a menor indutância possível;

-preferencialmente deve-se utilizar planos de terra;

-Vias de clock devem possuir linhas de terras adjacentes de retorno .

Seguem abaixo algumas recomendações específicas para a redução de problemas

associados a compatibilidade eletromagnética :

- Cabos devem estar próximos dos planos de terra;

- As áreas de Loop devem ser minimizadas;

- Deve-se utilizar blindagem localizada quando possível;

- Deve-se prover o desacoplamento dos CIs;

- Deve-se procurar na fase de projeto prover meios para que a transição de nível lógico

seja mais lenta.

- Deve-se prever o uso de planos de terra e força;

- Deve-se planejar cuidadosamente caminhos de terra;

- As fontes causadoras de possíveis ruídos devem ser previamente identificadas e

isoladas;

FIG.31 – Correção de Problemas de EMI

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

29

5. Bibliografia

•

Considerations in Designing the Printed Circuits Boards of Switching Power

Supplies ; Muriel Bittencourt de Liz

•

Introduction to Electromagnetic , Clayton R. Paul , 1992

•

Engineering Electromagnetic Compatibility , V. Prasad Kodali , 1996

•

Noise Reduction Techniques in Electronic Systems , Henry W.Ott , 1988

•

EMI Control in the Design of PCB ands Backplanes , Donald R.J. White , 1982

Técnicas de Projeto de Compatibilidade Eletromagnética (CEM) no desenvolvimento de Placas de

Circuito Impresso – Prof. Rodrigo Cutri

30