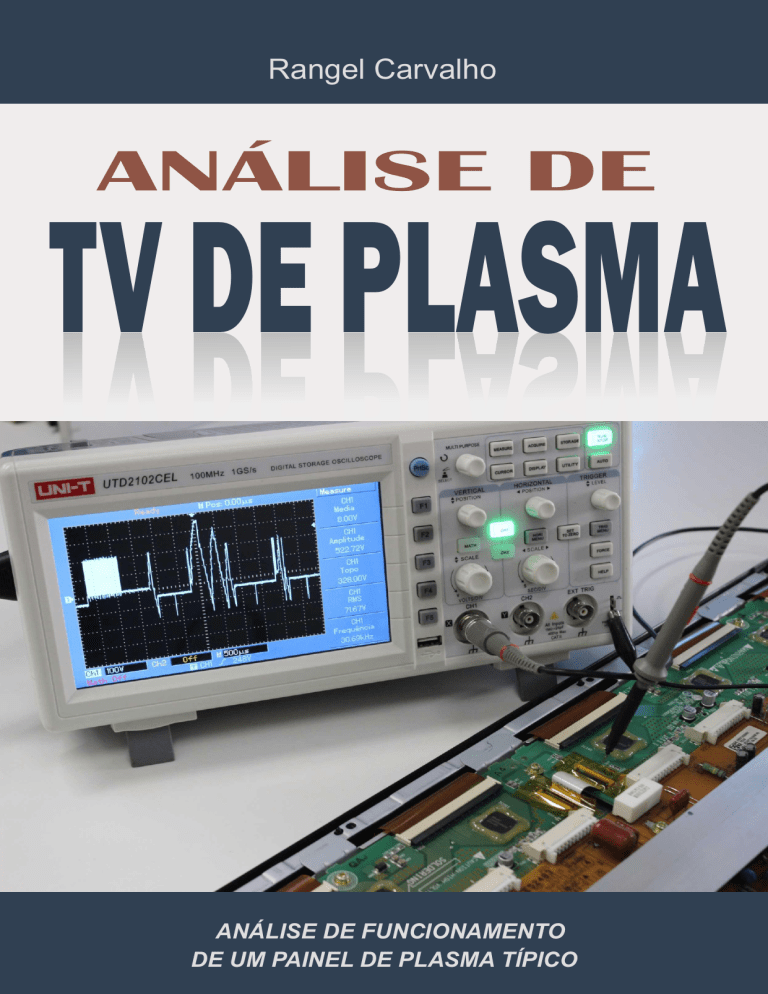

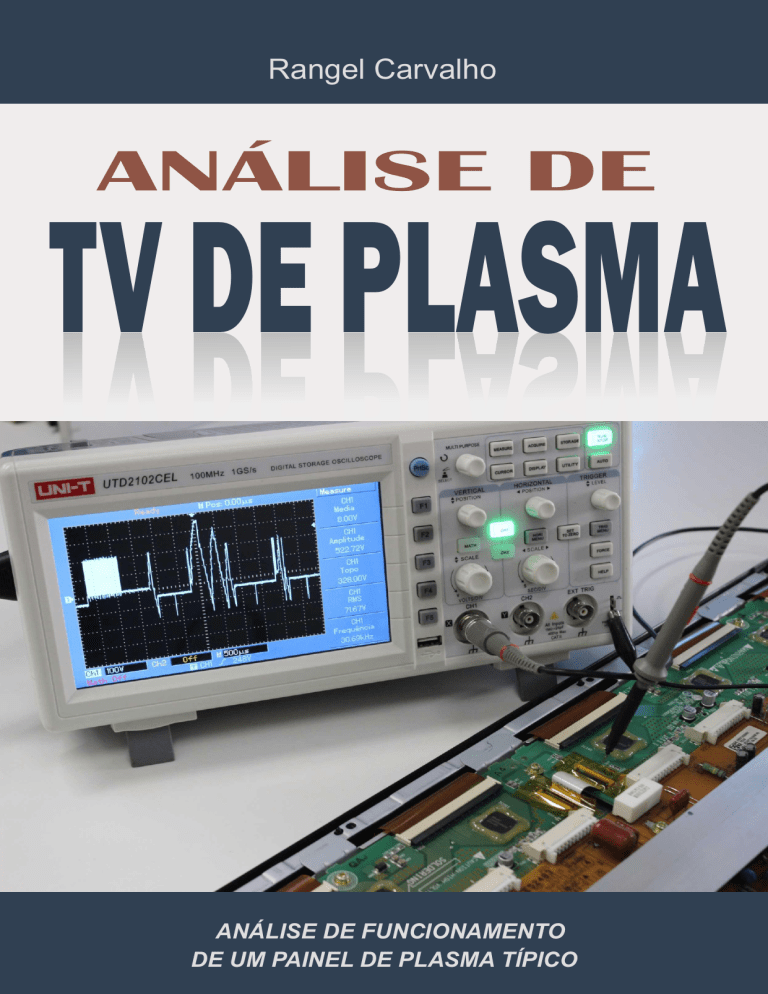

Rangel Carvalho

ANÁLISE DE

TV DE PLASMA

ANÁLISE DE FUNCIONAMENTO

DE UM PAINEL DE PLASMA TÍPICO

Análise de TV de Plasma

10

ESTADO DE PLASMA

Já é de nosso conhecimento que na natureza a matéria encontra-se em três

estados: sólido, líquido e gasoso. Para o estudo do display de plasma

interessa-nos somente o estado gasoso que é representado pelos gases. Os

gases quando não sofrem nenhuma influência externa permanecem em

estado neutro, onde seus átomos possuem a mesma carga elétrica, em outras

palavras, onde seus átomos possuem o mesmo número de elétrons e de

prótons, como mostra a figura 1.1.

Figura 1.1 Ilustração didática mostrando um gás em estado

neutro, onde os átomos possuem a mesma carga elétrica.

Energia como calor e tensão, pode “arrancar” elétrons dos átomos criando

diferenças de cargas entre os átomos. Quando os átomos de um gás estão

com diferenças de cargas diz-se que o gás está ionizado ou que o gás está no

“estado de plasma”, como mostra a figura 1.2. O estado de plasma é

considerado o quarto estado da matéria. Gases como o xênon e neon tem

grande facilidade de liberar elétrons, portanto são largamente empregados

para se obter o estado de plasma.

Análise de TV de Plasma

13

Estrutura do Display de Plasma

A figura 1.5 mostra a estrutura de um display de plasma. É formado

basicamente por duas placas de vidro, uma frontal e uma traseira. Na face

interna da placa de vidro traseira são colocados eletrodos verticais chamados

de eletrodos de endereço. Sobre os eletrodos de endereço é colocada uma

grade com divisões horizontais e verticais formando milhares de células de

descargas, de modo que cada coluna de célula fique exatamente sobre um

eletrodo de endereço. O interior de cada célula é revestido com uma camada

de fósforo vermelho, verde ou azul.

Na face interna da placa de vidro frontal são colocados eletrodos

transparentes chamados de eletrodos de sustentação. Esses eletrodos são

posicionados em sentido horizontal de modo que cada dois eletrodos fiquem

exatamente sobre uma linha de células. Sobre os eletrodos de sustentação é

colocado um dielétrico transparente que isola os eletrodos das células de

descargas.

As duas placas de vidro são unidas e hermeticamente vedadas e em seguida

as cavidades das células são preenchidas com gás neon e xênon.

PLACA DE

VIDRO FRONTAL

CONDUTORES PARA

LIGAR OS ELETRODOS

AO CIRCUITO EXTERNO

DIELÉTRICO

(TRANSPARENTE)

CONDUTORES PARA

LIGAR OS ELETRODOS

AO CIRCUITO EXTERNO

ELETRODOS DE

ENDEREÇO

ELETRODOS DE

SUSTENTAÇÃO

(TRANSPARENTES)

PLACA DE

VIDRO TRASEIRA

CÉLULAS DE DESCARGA COM

CAMADA DE FÓSFORO RGB

Figura 1.5 Estrutura do display de plasma.

Análise de TV de Plasma

16

Sustentação das descargas UV

Como as descargas UV ocorrem somente durante a formação das cargas de

parede, para “sustentar” a descarga UV, ou seja, para gerar seguidas

descargas UV é necessário alimentar os eletrodos Y e Z com uma tensão que

muda de polaridade constantemente e, além disso, a mudança de polaridade

tem que ser “abrupta” para provocar fortes descargas UV. Portanto para gerar

seguidas descargas UV os eletrodos de sustentação são alimentados com

pulsos, chamados de pulsos de sustentação. Os pulsos de sustentação são

fornecidos por um circuito comutador chamado de circuito de sustentação

que é mostrado na figura 1.7.

QUANDO S1 E S4 FECHAM, S2 E S3 ABREM. S1 LIGA O ELETRODO Y NA

TENSÃO VS ENQUANTO S4 LIGA O ELETRODO Z NO GND. QUANDO S2 E S3

FECHAM, S1 E S4 ABREM. S3 LIGA O ELETRODO Z NA TENSÃO VS

ENQUANTO S2 LIGA O ELETRODO Y NO GND. ASSIM OS ELETRODOS Y E Z

RECEBEM PULSOS DE SUSTENTAÇÃO VARIANDO DO GND A TENSÃO VS

VS

VOLTAGE SUSTAIN

PULSOS DE SUSTENTAÇÃO

VS

S1

Y

S3

Y

Z

GND

VS

S2

S4

X

Z

GND

Figura 1.7 Representação do circuito de sustentação.

Apagamento das cargas de parede

Devido o efeito memória as cargas de parede permanecem por um longo

período. Para apagar as cargas de parede é necessário aplicar nos eletrodos Y

e Z uma tensão que varia lentamente, em forma de rampa. Tensão em forma

de rampa atraí ou repele os elétrons lentamente que acabam retornando aos

átomos do gás e com isso o gás volta ao estado neutro. As figuras 1.8 e 1.9

mostram a sequência de funcionamento da célula de descarga.

Análise de TV de Plasma

19

PROCESSO DE VARREDURA

NO DISPLAY DE PLASMA

A figura 1.10 mostra o diagrama em blocos de um painel de plasma incluindo

os circuitos Y-SUS, Y-BUFFER, Z-SUS e DATA DRIVER. Os eletrodos X são

dispostos em colunas e os eletrodos Y e Z são dispostos em linhas. Note que

os eletrodos Z são ligados ao mesmo ponto formando eletrodos comuns

enquanto os eletrodos Y são ligados separadamente em cada linha de células.

Isso é necessário porque os eletrodos Y, além da função de sustentação,

também tem a função de varredura. Nos cruzamentos dos eletrodos Y e X

estão as células de descargas, sendo que cada célula é um subpíxel R, G ou B e

cada grupo com três células RGB forma um pixel.

As imagens no display de plasma são formadas utilizando um processo de

varredura precisamente controlado onde cada célula é acessada

individualmente. O processo de varredura é dividido em três períodos: período

de reset, período de endereço e período de sustentação.

TRÊS CÉLULAS

UM PIXEL

UMA CÉLULA

UM SUBPIXEL

DISPLAY DE PLASMA

Y1

Z2

Z3

Y4

Z4

Y5

Z5

Yn

Xn

X17

X16

X15

X14

X13

X12

X11

X10

X9

X8

X7

X6

X5

X4

X3

X2

Zn

DATA DRIVER

Figura 1.10 Diagrama em blocos de um painel de Plasma.

Z-SUS

Y3

X1

Y-SUS & Y-BUFFER

Z1

Y2

Análise de TV de Plasma

26

Circuitos didáticos Ysus, Ybuffer, Zsus e Data Driver

A figura 1.14 mostra os circuitos didáticos Ysus, Ybuffer,

Zsus e Data Driver. O circuito Ysus alimenta os eletrodos Y

através do circuito Ybuffer, o circuito Zsus alimenta os

eletrodos Z e o circuito Data Driver alimenta os eletrodos X.

Esses circuitos são basicamente chaves eletrônicas que

selecionam as tensões VS, VA, VZB, -Vy e VSC para

alimentar os eletrodos. A fonte VSC está representada pela

bateria B1 de 200V, cujo negativo está ligado na saída Yout.

Vamos analisar o funcionamento em cada período: reset

(set-up/set-down), endereço e sustentação.

Y-BUFFER

Y-SUS

DISPLAY DE PLASMA

Z1

S3

YSUS-DN

-Vy

SYn

SET-DN

-Vy (-200V)

S8

ZSUS-UP

VZB

Zn

S7

Yn

ZSUS-DN

-Vy (-200V)

Xn

SET-DN

S2

X1

S5

Y5

S6

Z-OUT

Z5

SXn

SY5

Y4

X5

Y-OUT

Z4

SX5

SY4

Y3

X4

YSUS-UP

VZB (100V)

Z3

SX4

SET-UP

SY3

VS (200V)

Y2

X3

S1

B1

200V

Z2

SX3

S4

SY2

Z-SUS

Y1

X2

VS (200V)

SY1

SX1

SET-UP

VSC

SX2

VS (200V)

VA

60V

DATA DRIVER

Figura 1.14 Representação didática dos circuitos Ysus, Ybuffer, Zsus e Data Driver.

Análise de TV de Plasma

44

ANÁLISE DA PLACA

CONTROLADORA

A placa controladora tem a função de gerar sinais de controle para os circuitos

Ysus, Ybuffer, Zsus e Data Driver. Além de gerar sinais de controle, a placa

controladora também recebe os sinais LVDS fornecidos pela placa principal e

converte em sinais RSDS divididos em subcampos.

A figura 2.3 mostra o aspecto físico de uma placa controladora típica incluindo

um CI de controle (IC Control) e duas memórias (SDRAM e Flash). Devido ao

baixo custo dessa placa, em caso de defeito pode ser mais conveniente

substituir a placa, entretanto conhecer seu funcionamento é fundamental para

entender e analisar as demais placas. Além disso, em caso de falta de imagem

ou distorção de imagem é importante conhecer os sinais de vídeo

processados na placa controladora.

PARA A

PLACA X LEFT

XD

TxC-N

TxC-P

Tx0-N

Tx0-P

Tx1-N

Tx1-P

PARA A

PLACA Z-SUS

MEMÓRIA

FLASH

PARA A

PLACA PRINCIPAL

CONTROL

MEMÓRIA

SDRAM

PARA A

PLACA Y-SUS

RESISTORES DE

TERMINAÇÃO DE 100R

Rx3-N

Rx3-P

RxC-N

RxC-P

Rx2-N

Rx2-P

Rx1-N

Rx1-P

Rx0-N

Rx0-P

CANAIS LVDS

PARA A

PLACA X RIGHT

CANAIS RSDS

Figura 2.3 Aspecto físico de uma placa controladora típica.

Análise de TV de Plasma

49

Os sinais LVDS podem ser visualizados em tempo horizontal (5us) ou em

tempo vertical (5ms). Com o osciloscópio em 5ms cada pacote LVDS possui

todos os bits para formar um quadro de imagem e com o osciloscópio em 5us

cada pacote LVDS possui todos os bits para formar uma linha de imagem.

Para vermos os sinais LVDS nos canais Tx0, Tx1, Tx2 e Tx3 é necessário que

tenha sinal de vídeo, pois sem sinal de vídeo esses canais ficam somente com

uma tensão em torno de 1V, já o sinal CLK permanece normal mesmo sem

sinal de vídeo.

Osciloscópio 1

1

2

CH1 500mV

CH2 500mV

SEC

5us

SEC

5us

CH1 - LVDS-P / CH2 - LVDS-N

Osciloscópio 2

1

2

CH1 500mV

CH2 500mV

CH1 - CLK-P / CH2 - CLK-N

Análise de TV de Plasma

52

ANÁLISE DA PLACA X

A placa X é somente uma interface para conectar os CIs data drivers ao display

de plasma. O CI data driver (também chamado de address driver) é um CI do

tipo TCP (Taped Carrier Package) montado diretamente nos flats cables que

ficam conectados na placa X e no display, e em caso de defeito é necessário

substituir o display. Embora não seja possível substituir um TCP, entender o

funcionamento do CI data driver é muito importante para que possamos

entender os circuitos envolvidos no controle do display de plasma. A figura 2.8

mostra parte da placa X destacando o CI data driver.

A figura 2.9 mostra o diagrama simplificado da placa X onde podemos ver a

disposição dos CIs data drivers. Cada CI alimenta 256 eletrodos X e como são

usados 12 CIs é possível alimentar 3072 eletrodos X (12 x 256 = 3072) que pode

formar 1024 pixels (3072 / 3 = 1024). Os CIs data drivers são alimentados com a

tensão VA de 60V e com a tensão VDD de 3,3V. Cada CI data driver recebe o

sinal RSDS e converte para dados RGB com amplitude de 60V para alimentar

os eletrodos X.

CADA CI DATA DRIVER RECEBE TRÊS

CANAIS RSDS, SENDO UM CANAL DE

CLOCK E DOIS CANAIS DE DADOS RGB.

CANAIS RSDS PARA

TRANSMISSÃO DOS DADOS RGB

FLAT CABLE CONECTADO

A PLACA CONTROLADORA

PLACA X ESQUERDA

TENSÃO VA

471

470

2R2

470

2R2

470

2R2

470

2R2

470

2R2

2R2

2R2

2R2

FITA TÉRMICA PARA

DISSIPAR O CALOR

DATA DRIVER

TCP - TAPED CARRIER PACKAGE

Figura 2.8 Parte da placa X destacando o CI Data Driver.

Análise de TV de Plasma

59

ANÁLISE DA PLACA Y-BUFFER

A figura 2.13 mostra parte da placa Ybuffer onde podemos ver em detalhes o

CI Ybuffer, o conector do display e as trilhas entre o CI e o conector.

2

1

CI Y-BUFFER

COM 128 PINOS

(96 SAÍDA)

R2A20292BFT

JAPAN

SILICONE PARA EVITAR

CENTELHAMENTO

ENTRE OS PINOS

128

127

TENSÃO VSC

PARA ALIMENTAR

O ESTÁGIO DE

SAÍDA DO CI

Y-BUFFER

FGND

FLOUNTING

GROUND

TERRA FLUTUANTE

470

470

2

1

R2A20292BFT

JAPAN

5V PARA ALIMENTAR O

ESTÁGIO LÓGICO DO CI

CONECTOR

COM 128 PINOS

(64 DE CADA LADO)

PONTO DE TESTE PARA

MEDIR O SINAL Y-OUT

R2A20292BFT

JAPAN

128

127

470

470

2

1

Figura 2.13 Placa Ybuffer.

Análise de TV de Plasma

68

ANÁLISE DAS

PLACAS Y-SUS E Z-SUS

A figura 2.17 mostra parte do painel de plasma destacando as placas Ysus e

Zsus. Essas são as placas com maior incidência de defeitos, devido as

elevadas tensões e as altas correntes usadas para alimentar os eletrodos Y e Z.

A maioria dos componentes utilizados nessas placas podem ser encontrados

no mercado especializado possibilitando a reparação dessas placas em

quase todos os casos, mas devido a falta de informações dos circuitos, muitos

técnicos optam pela substituição das placas.

PLACA Y-SUS

PLACA

Y-SUS

PLACA Z-SUS

ER-UP

ER-DN

SUS-DN SUS-UP SUS-UP

ER-UP

ER-DN

SET-UP

SET-DN

SUS-DN SUS-DN

BLOCK

SUS-UP SUS-UP

-Vy

Figura 2.17 Parte do painel de Plasma destacando as placas Ysus e Zsus.

Análise de TV de Plasma

69

Análise do diagrama

simplificado Ysus e Zsus

A figura 2.18 mostra o diagrama simplificado Ysus e Zsus incluindo os

seguintes circuitos:

Circuito Set-Up/Set-Down - gera as rampas Set-Up e Set-Down durante o

período de reset.

Circuitos Ysus e Zsus - fornece pulsos de sustentação aos eletrodos Y e Z

durante o período de sustentação.

Circuito Yblocking - bloqueia a tensão negativa que surge na saída Yout

durante o período set-down e período de endereço, evitando que essa tensão

chegue ao diodo D5.

Circuito VZB - fornece a tensão VZB aos eletrodos Z durante o período de

endereço.

Circuito ERC - recupera a tensão acumulada nos eletrodos Y e Z para auxiliar

na formação dos pulsos de sustentação.

As saídas dos circuitos possuem transistores MOSFETs ou IGBTs que devem

ter características de tensão e corrente adequadas conforme a aplicação.

Cada transistor recebe no gate um sinal de controle fornecido pela placa

controladora. Os sinais de controle passam por circuitos drivers que

amplificam o sinal em tensão e corrente para polarizar os gates dos

transistores. Os transistores que tem o source (emissor) ligados a uma tensão

diferente do terra é polarizado por drivers com foto acoplador.

A figura 2.19 mostra o diagrama de tempo com os sinais Yout, Zout e os sinais

de controle fornecidos pela placa controladora. Vamos analisar os circuitos da

figura 2.18 acompanhando as formas de ondas da figura 2.19 que está dividida

nos períodos de reset, endereço e sustentação.

Análise de TV de Plasma

ERC

70

15VZ

15VF

L1

IC1

Y-ER-UP

Q1

Y-ER

Y-SUS

D1

D2

VS

15VF

Y-SUS-UP

Z-SUS

15VZ

VSC

Q3

YSUS-UP

Z-ER-UP

Q2

Z-ER

Y-BUFFER

VS

IC3

IC2

Q6

ZSUS-UP

IC6

Z-SUS-UP

Y-BUFFER

D6

D3

+5VF

Q-UP

OC2

15VZ

DISPLAY

Z Z-OUT

Y

LOGIC

OC1

15V

15V

DATA

CLK

Y-BLOKCING

Q7

ZSUS-DN

Q-DN

C3

D12

IC7

Z-SUS-DN

D7

Y-OUT / FGND

IC4

Y-BLOCK

R1

VS

Q4

Y-BLOCK

C1

VZB

15VF

VZB

Q8

VZB

Q9

SET-UP

15VF

IC8

IC9

R2

Y-SUS

15V

IC5

Y-SUS-DN

VZB

C2

Q5

YSUS-DN

D5

15VZ

15Vy

R3

IC10

Q10

SET-DN

-VY

Figura 2.18 Diagrama simplificado dos circuitos Ysus e Zsus.

SET-DN

SET-UP

SET-UP / SET-DOWN

Análise de TV de Plasma

100

ANÁLISE DA FONTE PFC

(circuito genérico)

A figura 3.7 mostra um circuito genérico de uma fonte PFC incluindo somente

os componentes relevantes para analisarmos o funcionamento, entre eles, o

indutor PFC (L21), o CI gerador de PWM (IC21) e o transistor chaveador (Q21).

A fonte PFC é um conversor DC/DC do tipo step-up (elevador de tensão) que

através de um PWM converte a tensão da rede em uma tensão em torno de

400VDC para alimentar a fonte standby e a fonte VS. O indutor PFC é

alimentado com tensão DC pulsante “semi senoidal positiva” obtida pela

retificação da tensão da rede. Como a DC pulsante varia regularmente entre os

picos e vales, para manter a tensão de saída estabilizada o PWM deve ser

corrigido conforme as variações da DC pulsante.

PWM

DC PULSANTE

DC

AC

BD21

A

B

L21

D21

C

PFC400V

C21

C22

AC

D22

IC21

OUT

DRV

ZCD

ZCD

VCC

VCC15V

VCC

UVLO

R22

Q21

OCP

PWM

R23

OVP

UVP

R24

FB

COMP

2.5V

C23

Figura 3.7 Diagrama simplificado da fonte PFC.

R25

Análise de TV de Plasma

111

O osciloscópio 28 mostra o PWM sobre o primário do transformador T31,

medido com o terra do osciloscópio de um lado do primário e a ponta de prova

do outro lado e o osciloscópio 29 mostra as tensões nos extremos do

enrolamento secundário que gera a tensão VS.

Osciloscópio 28

1

CH1

100V

CH2

OFF

2us

SEC

PWM sobre o primário do transformador T31

Osciloscópio 29

2

1

CH1

200V

CH2

200V

SEC

2us

PWM simétrico no secundário do transformador T31