Notas da terceira edição

Nota: essas notas normalmente são complementadas por

outros materiais, como problemas do texto que podem

ser trabalhados em sala de aula. É provável que você

queira personalizar esse material para que se ajuste às

necessidades dos seus alunos. Essas notas foram

prepararadas com base em uma turma de alunos que

já aprendeu sobre desenvolvimento com lógica e

freqüentou um laboratório prático de programação de

linguagem assembly que não segue um formato de

aula comum.

1

Capítulo 1

2

Introdução

• O objetivo deste curso é mostrar como os computadores funcionam

• Mas o que queremos dizer com a palavra “computador”?

• Diferentes tipos: desktop, servidores, dispositivos embutidos

– Diferentes usos: automóveis, design gráfico, finanças, genética...

– Diferentes fabricantes: Intel, Apple, IBM, Microsoft, Sun...

– Diferentes tecnologias subjacentes e diferentes custos!

• Analogia: Pense em um curso sobre “veículos automotivos”

– Muitas semelhanças de um veículo para outro (por exemplo, volantes)

– Grandes diferenças de um veículo para outro (por exemplo, gasolina, álcool)

• Melhor maneira de aprender:

– Concentrar em um exemplo específico e aprender como ele funciona

– Abordar princípios gerais e perspectivas históricas

3

Por que aprender esse assunto?

• Você deseja se tornar um “cientista da computação”

• Você deseja desenvolver softwares utilizáveis (precisam de desempenho)

• Você precisa tomar uma decisão em relação a uma compra ou oferecer conselhos

de “especialista”

• Tanto o hardware quanto o software afetam o desempenho:

– O algoritmo determina o número de instruções na origem

– Linguagem/compilador/arquitetura determinam as instruções da máquina

(Capítulos 2 e 3)

– Processador/memória determinam a velocidade com que as instruções são

executadas (Capítulos 5, 6 e 7)

• Avaliando e entendendo o desempenho no Capítulo 4

4

O que é um computador?

• Componentes:

– entrada (mouse, teclado)

– saída (monitor, impressora)

– memória (unidades de disco, DRAM, SRAM, CD)

– rede

• Nosso foco principal: o processador (caminho de dados e controle)

– Implementado usando milhões de transistores

– Impossível de entender olhando para os transistores

– Precisamos...

5

Abstração

• Uma boa dica para obter mais informações

é aprofundar-se nos componentes

Programa

em linguagem

de alto nível

(em C)

• Uma abstração omite detalhes desnecessários

swap (int v[], int k)

{int temp;

temp = v[k];

v[k] = v[k+1];

v[k+1] = temp;

}

e ajuda a entender a complexidade

Compilador

Programa

em linguagem

assembly

(para MIPS)

Quais são alguns dos detalhes que aparecem

nestas abstrações familiares?

swap:

muli

add

lw

lw

sw

sw

jr

$2, $5, 4

$2, $4, $2

$15, 0($2)

$16, 4($2)

$16, 0($2)

$15 4($2)

$31

Assembler

Programa em

linguagem de

máquina binária

(para MIPS)

000000001010000100000000000000011000

000000000001100110000001100000100001

100011000110001000000000000000000000

100011001111001000000000000000000100

101011001111001000000000000000000000

101011000110001000000000000000000100

000000111110000000000000000000000100

6

Como os computadores funcionam?

• É preciso entender abstrações como:

–

–

–

–

–

–

–

–

–

–

–

Software de aplicações

Software de sistemas

Linguagem assembly

Linguagem de máquina

Aspectos de arquitetura, como caches, memória virtual, canalização

Lógica seqüencial, máquinas de estado finito

Lógica combinatória, circuitos aritméticos

Lógica booleana, 1s e 0s

Transistores usados para construir portões lógicos (CMOS)

Semicondutores/silício usados para construir transistores

Propriedades dos átomos, elétrons e dinâmica quantitativa

• Muito o que aprender!

7

Arquitetura do conjunto de instruções

• Uma abstração muito importante

– interface entre o hardware e o software de baixo nível

– padroniza instruções, padrões de bits de linguagem de máquina etc.

– vantagem: diferentes implementações da mesma arquitetura

– desvantagem: algumas vezes impede o uso de inovações

Verdadeiro ou falso: A compatibilidade binária é extremamente importante?

• Arquiteturas de conjunto de instruções modernas:

– IA-32, PowerPC, MIPS, SPARC, ARM e outras

8

Perspectiva histórica

• O ENIAC, construído na Segunda Guerra Mundial, foi o primeiro computador de

finalidade geral

– Usado para calcular tabelas de disparo de artilharia

– 24 metros de comprimento por 2,5 metros de altura e dezenas de centímetros de

profundidade

– Cada um dos 20 registradores de 10 dígitos tinha 60 centímetros de comprimento

– Usava 18.000 válvulas

– Efetuava 1.900 adições por segundo

– Desde então:

Lei de Moore:

A capacidade dos transistores

dobra a cada 18 a 24 meses

9

Capítulo 2

10

Instruções

• Linguagem da máquina

• Vamos trabalhar com a arquitetura do conjunto de instruções MIPS

– Semelhante a outras arquiteturas desenvolvidas desde a década de 1980

– Quase 100 milhões de processadores MIPS fabricados em 2002

– Usada pela NEC, Nintendo, Cisco, Silicon Graphics, Sony...

1400

1300

1200

Milhões de processadores

1100

1000

Outro

SPARC

Hitachi SH

PowerPC

Motorola 68K

900

MIPS

IA-32

800

ARM

700

600

500

400

300

200

100

0

1998

1999

2000

2001

2002

11

Aritmética MIPS

• Todas as instruções possuem três operandos

• A ordem do operando é fixa (destino primeiro)

Exemplo:

Código C:

a = b + c

Código MIPS:

add a, b, c

(falaremos sobre registradores em breve)

“O número natural de operandos para uma operação como adição é

três... Exigir que cada instrução tenha exatamente três operandos, nem

mais nem menos, está de acordo com a filosofia de manter o hardware

simples.”

12

Aritmética MIPS

• Princípio de projeto: a simplicidade favorece a regularidade.

• É claro, isso complica algumas coisas...

Código C:

a = b + c + d;

Código MIPS:

add a, b, c

add a, a, d

• Os operandos precisam ser registradores, apenas 32 registradores fornecidos

• Cada registrador contém 32 bits

• Princípio de projeto: quanto menor, melhor.

Por quê?

13

Registradores versus memória

• Os operandos das instruções aritméticas precisam ser registradores

– apenas 32 registradores fornecidos

• O compilador associa variáveis com registradores

• E quanto aos programas com muitas variáveis?

Entrada

Controle

Memória

Caminho

de dados

Processador

Saída

E/S

14

Organização da memória

• Vista como um array grande e unidimensional, com um endereço.

• Um endereço de memória é um índice para o array.

• “Endereçamento de byte” significa que o índice aponta para um byte da memória.

0 8 bits de dados

1 8 bits de dados

2 8 bits de dados

3 8 bits de dados

4 8 bits de dados

5 8 bits de dados

6 8 bits de dados

...

15

Organização da memória

• Os bytes são bons, mas a maioria dos itens de dados usam “words” maiores

• Para o MIPS, uma word possui 32 bits ou 4 bytes.

0

4

32 bits de dados

8

12

32 bits de dados

32 bits de dados

Os registradores armazenam 32 bits de dados

32 bits de dados

• 232 bytes com endereços de byte de 0 a 232–1

• 230 words com endereços de byte 0, 4, 8, ... 232–4

• As words são alinhadas

Por exemplo, quais são os 2 bits menos significativos

de um endereço de word?

16

Instruções

• Instruções load e store

• Exemplo:

Código C:

A[12] = h + A[8];

Código MIPS:

lw $t0, 32($s3)

add $t0, $s2, $t0

sw $t0, 48($s3)

• Pode se referir aos registradores por nome (por exemplo, $s2, $t2) em vez do

número

• A instrução store word tem o destino por último

• Lembre-se de que os operandos são registradores, não memória!

Não podemos escrever:

add 48($s3), $s2, 32($s3)

17

Nosso primeiro exemplo

• Você pode descobrir o código?

swap(int v[ ], int k);

{ int temp;

temp = v[k]

v[k] = v[k+1];

v[k+1] = temp;

}

swap:

muli $2, $5, 4

add $2, $4, $2

lw $15, 0($2)

lw $16, 4($2)

sw $16, 0($2)

sw $15, 4($2)

jr $31

Æ

18

Até agora, aprendemos:

• MIPS

– carga de words mas endereçamento de bytes

– aritmética apenas em registradores

• Instrução

add $s1, $s2, $s3

sub $s1, $s2, $s3

lw $s1, 100($s2)

sw $s1, 100($s2)

Significado

$s1 = $s2 + $s3

$s1 = $s2 – $s3

$s1 = Memory[$s2+100]

Memory[$s2+100] = $s1

19

Linguagem de máquina

• Instruções, como registradores e words de dados, também possuem 32 bits de

tamanho

– Exemplo: add $t1, $s1, $s2

– Registradores têm números, $t1=9, $s1=17, $s2=18

• Formato da instrução:

000000

10001

10010

01000

00000

100000

op

rs

rt

rd

shamt

funct

• Você sabe o significado dos nomes de campo?

20

Linguagem de máquina

• Pense nas instruções load-word e store-word

– O que o princípio da regularidade nos levaria a fazer?

– Novo princípio: Um bom projeto exige comprometimento

• Introduza um novo tipo de formato de instrução

– Tipo I para instruções de transferência de dados

– Outro formato era o tipo R para o registrador

• Exemplo: lw $t0, 32($s2)

35

18

9

op

rs

rt

32

número de bit 16

• Qual é o compromisso?

21

Conceito do programa armazenado

• Instruções são bits

• Programas são armazenados na memória

– para serem lidos ou escritos exatamente como os dados

Memória para dados, programas,

compiladores, editores etc.

Processador

Memória

• Ciclo de execução e busca

– As instruções são buscadas e colocadas em um registrador especial

– Os bits no registrador “controlam” as ações subseqüentes

– Busca a próxima instrução e continua

22

Controle

• Instruções de tomada de decisão

– altera o fluxo de controle

– por exemplo, mudar a “próxima” instrução a ser executada

• Instruções de desvio condicionais do MIPS:

bne $t0, $t1, Label

beq $t0, $t1, Label

• Exemplo:

if (i==j) h = i + j;

bne $s0, $s1, Label

add $s3, $s0, $s1

Label:

....

23

Controle

• Instruções de desvio incondicionais do MIPS:

j label

• Exemplo:

if (i!=j)

h=i+j;

else

h=i-j;

beq $s4, $s5, Lab1

add $s3, $s4, $s5

j Lab2

Lab1: sub $s3, $s4, $s5

Lab2: ...

• Você pode construir um “loop for” simples?

24

Até agora:

• Instrução

Significado

add $s1,$s2,$s3

sub $s1,$s2,$s3

lw $s1,100($s2)

sw $s1,100($s2)

bne $s4,$s5,L

beq $s4,$s5,L

j Label

$s1 = $s2 + $s3

$s1 = $s2 – $s3

$s1 = Memory[$s2+100]

Memory[$s2+100] = $s1

Next instr. is at Label if $s4 ¹ $s5

Next instr. is at Label if $s4 = $s5

Next instr. is at Label

• Formatos:

R

op

rs

rt

rd

I

op

rs

rt

endereço de 16 bits

J

op

shamt

funct

endereço de 26 bits

25

Fluxo de controle

• Temos: beq e bne; e branch-if-less-than?

• Nova instrução:

if

slt $t0, $s1, $s2

$s1 < $s2 then

$t0 = 1

else

$t0 = 0

• Podemos usar essa instrução para construir “blt $s1, $s2, Label”

– agora podemos construir estruturas de controle gerais

• Note que o assembler precisa de um registrador para fazer isso

– existe uma política das convenções de uso para registradores

26

Política das convenções de uso

Nome

Número do registrador

$zero

0

Uso

O valor constante 0

$v0-$v1

2-3

Valores para resultados e

avaliação de expressões

$a0-$a3

4-7

Argumentos

$t0-$t7

8-15

Temporários

$s0-$s7

16-23

Valores salvos

$t8-$t9

24-25

Mais temporários

$gp

28

Ponteiro global

$sp

29

Pointeiro de pilha

$fp

30

Pointeiro de quadro

$ra

31

Endereço de retorno

Registrador 1 ($at) reservado para o assembler, 26-27 para o sistema operacional

27

Constantes

• Constantes pequenas são usadas muito freqüentemente (50% dos operandos)

Por exemplo:

A = A + 5;

B = B + 1;

C = C - 18;

• Soluções? Por que não?

– coloque “constantes típicas” na memória e carregue-as.

– crie registradores “hard-wired” (como $zero) para constantes como um.

• Instruções MIPS:

addi $29, $29, 4

slti $8, $18, 10

andi $29, $29, 6

ori $29, $29, 4

• Princípio de projeto: Torne o caso comum rápido. Que formato?

28

E quanto às constantes maiores?

• Gostaríamos de ser capazes de carregar uma constante de 32 bits em um

registrador

• Precisamos usar duas instruções; nova instrução “load upper immediate”:

lui $t0, 1010101010101010

1010101010101010

preenchido com zeros

0000000000000000

• Depois, precisamos acertar os bits de ordem inferior, por exemplo:

ori $t0, $t0, 1010101010101010

1010101010101010

0000000000000000

0000000000000000

1010101010101010

1010101010101010

1010101010101010

ori

29

Linguagem assembly versus linguagem de máquina

• O assembly fornece uma representação simbólica conveniente

– muito mais fácil do que escrever números

– por exemplo, destino primeiro

• A linguagem de máquina é realidade subjacente

– por exemplo, o destino não é mais o primeiro

• O assembly pode fornecer “pseudoinstruções”

– por exemplo, “move $t0, $t1” existe apenas no assembly

– seria mais bem implementada usando “add $t0,$t1,$zero”

• Ao considerar o desempenho, você deve contar as instruções reais

30

Outras questões

• Abordadas em seu laboratório de programação de linguagem assembly:

– suporte para procedimentos

– linkers, carregadores, layout da memória

– pilhas, quadros, recursão

– manipulação de strings e ponteiros

– interrupções e exceções

– chamadas de sistema e convenções

• Veremos alguns desses mais adiante

• Estudaremos as otimizações de compilador no Capítulo 4.

31

Visão geral do MIPS

• instruções simples, todas com 32 bits

• muito estruturado, nenhuma bagagem desnecessária

• apenas três formatos de instrução

R

op

rs

rt

rd

I

op

rs

rt

endereço de 16 bits

J

op

shamt

funct

endereço de 26 bits

• nos baseamos no compilador para obter desempenho

– quais são os objetivos do compilador?

• ajudamos o compilador onde podemos

32

Endereços em desvios e jumps

• Instruções:

bne $t4,$t5,Label

A próxima instrução está em Label se $t4 ° $t5

beq $t4,$t5,Label

A próxima instrução está em Label se $t4 = $t5

j Label

A próxima instrução está em Label

• Formatos:

I

op

J

op

rs

rt

endereço de 16 bits

endereço de 26 bits

• Os endereços não são de 32 bits

– Como manipular isso com instruções load e store?

33

Endereços em desvios

• Instruções:

bne $t4,$t5,Label

beq $t4,$t5,Label

A próxima instrução está em Label se $t4¹$t5

A próxima instrução está em Label se $t4=$t5

• Formatos:

I

op

rs

rt

endereço de 16 bits

• Poderíamos especificar um registrador (como lw e sw) e acrescentá-lo ao endereço

– use o registrador de endereço de instrução (PC = contador do programa)

– a maioria dos desvios é local (princípio da localidade)

• As instruções jump usam apenas bits de ordem superior do PC

– limites de endereço de 256 MB

34

Resumindo

Operandos MIPS

Nome

Exemplo

Comentários

32

registradores

$s0-$s7, $t0-$t9, $zero,

$a0-$a3, $v0-$v1, $gp, $fp, $sp,

$ra, $at

Memória[0],

Memória[4].....

Memória[4294967292]

Locais rápidos para dados. No MIPS, os dados precisam estar em registradores para a realização de

operações aritméticas. O registrador MIPS $zero sempre é igual a 0. O registrador $at é reservado para o

assembler tratar de constantes grandes.

Acessadas apenas por instruções de transferência de dados. O MIPS utiliza endereços em bytes, de modo

que os endereços em words seqüenciais diferem em 4 vezes. A memória contém estruturas de dados, arrays

e spilled registers, como aqueles salvos nas chamadas de procedimento.

30

2 words na

memória

Assembly do MIPS

Categoria

Instrução

Exemplo

Significado

Comentários

Aritmética

add

subtract

add immediate

load word

[TD]add $s1,$s2,$s3[TN]

[TD]sub $s1,$s2,$s3[TN]

addi $s1,$s2,100[TN]

[TD]lw $s1,100($s2)[TN]

[TD]$s1 = $s2 + $s3[TN]

[TD]$s1 = $s2- $s3[TN]

[TD]$s1=$s2 + 100[TN]

$s1 = Memória[$s2 + 100

Três operandos; dados nos registradores

Três operandos; dados nos registradores

Usada para somar constantes

Dados da memória para o registrador

store word

load byte

store byte

load upper immed.

branch on equal

[TD]sw $s1,100($s2)[TN]

lb $s1,100($s2)[TN]

sb $s1,100($s2)[TN]

[TD]lui $s1,100[TN]

beq $s1,$s2,25

Dados do registrador para a memória

Byte da memória para o registrador

Byte de um registrador para a memória

Carrega constante nos 16 bits mais altos

Testa igualdade; desvio relativo ao PC

branch on not equal

set on less than

bne $s1,$s2,25

slt $s1,$s2,$s3

set less than

immediate

jump

slti $s1,$s2,100

Memória[$s2 + 100] = $s1

$s1 = Memória[$s2 + 100

Memória[$s2+100] = $s1

[TD]$s1 = 100 * 216[TN]

if ($s1 == $s2) go to

PC + 4 + 100

if ($s1 != $s2) go to PC + 4 + 100

if ($s2 < $s3) $s1 = 1; else $s1 =

0

if ($s2 < 100) $s1 = 1; else $s1 = 0

j 2500

go to 10000

Desvia para endereço de destino

jump register

jump and link

jr $ra

jal 2500

go to [TD]$ra[TN]

[TD]$ra[TN] = PC + 4. go to 10000

Para switch e retorno de procedimento

Para chamada de procedimento

Transferência

de dados

Desvio

condicional

Desvio

incondicional

Testa desigualdade; relativo ao PC

Compara menor que; usado com beq, bne

Compara menor que constante

35

1. Endereçamento imediato

op

rs

rt

Imediato

2. Endereçamento em registrador

op

rs

rd

rt

...

Registradores

funct

Registrador

3. Endereçamento de base

op

rs

rt

Memória

Endereço

+

Registrador

Byte

Halfword

Word

4. Endereçamento relativo ao PC

op

rs

Endereço

rt

PC

Memória

Word

5. Endereçamento pseudodireto

op

Endereço

PC

Memória

Word

36

Arquiteturas alternativas

• Alternativa de projeto:

– forneça operações mais poderosas

– o objetivo é reduzir o número de instruções executadas

– o risco é um tempo de ciclo mais lento e/ou uma CPI mais alta

— “O caminho em direção à complexidade da operação é, portanto,

repleto de perigos. Para evitar esses problemas, os projetistas passaram

para instruções mais simples.

• Vejamos (brevemente) o IA-32

37

IA-32

•

•

•

•

•

•

•

•

•

•

1978: O Intel 8086 é anunciado (arquitetura de 16 bits)

1980: O coprocessador de ponto flutuante 8087 é acrescentado

1982: O 80286 aumenta o espaço de endereçamento para 24 bits; mais instruções

1985: O 80386 estende para 32 bits; novos modos de endereçamento

1989-1995: O 80486, Pentium e Pentium Pro acrescentam algumas instruções

(especialmente projetadas para um maior desempenho)

1997: 57 novas instruções “MMX” são acrescentadas; Pentium II

1999: O Pentium III acrescenta outras 70 instruções (SSE)

2001: Outras 144 instruções (SSE2)

2003: A AMD estende a arquitetura para aumentar o espaço de endereço para 64

bits; estende todos os registradores para 64 bits, além de outras mudanças (AMD64)

2004: A Intel se rende e abraça o AMD64 (o chama EM64T) e inclui mais extensões

de mídia

• Essa história ilustra o impacto das “algemas douradas” da compatibilidade

“adicionando novos recursos da mesma forma que se coloca roupas em uma

sacola”, uma arquitetura “difícil de explicar e impossível de amar”.

38

Visão geral do IA-32

• Complexidade:

– instruções de 1 a 17 bytes de tamanho

– um operando precisa agir como origem e destino

– um operando pode vir da memória

– modos de endereçamento complexos, por exemplo, “índice base ou escalado

com deslocamento de 8 ou 32 bits”

• Graça salvadora:

– as instruções mais usadas não são difíceis de construir

– os compiladores evitam as partes da arquitetura que são lentas

“O que o 80x86 perde em estilo é compensado na

quantidade, tornando-o belo, do ponto de vista

apropriado”

39

Registradores e endereçamento de dados do IA-32

• Registradores no subconjunto de 32 bits que surgiram com o 80386

Nome

Uso

31

0

EAX

GPR0

ECX

GPR1

EDX

GPR2

EBX

GPR3

ESP

GPR4

EBP

GPR5

ESI

GPR6

EDI

GPR7

EIP

EFLAGS

CS

Ponteiro do segmento de código

SS

Ponteiro do segmento de pilha (topo da pilha)

DS

Ponteiro do segmento de dados 0

ES

Ponteiro do segmento de dados 1

FS

Ponteiro do segmento de dados 2

GS

Ponteiro do segmento de dados 3

Ponteiro de instrução (PC)

Códigos de condição

40

Restrições de registrador do IA-32

• Os registradores não são de “finalidade geral” — observe as restrições abaixo

Modo

Registrador indireto

Descrição

Restrições de registrador

Equivalente MIPS

Endereço está em um registrador.

não ESP ou EBP

lw $s0,0($s1)

Modo base com 8 ou 32 bits de

deslocamento

Endereço é o conteúdo do registrador base

mais deslocamento.

não ESP ou EBP

lw $s0,100($s1)#deslocamento

£ 16 bits

Base mais índice escalado

x Índice), onde

O endereço é Base + (2

Escala tem o valor 0, 1, 2 ou 3.

Base: qualquer GPR

Índice: não ESP

mul $t0,$s2,4

add $t0,$t0,$s1

lw $s0,0($t0)

Escala

x Índice) +

O endereço é Base + (2

deslocamento, onde Escala tem o valor 0, 1, 2

ou 3.

Base: qualquer GPR

Índice: não ESP

mul $t0,$s2,4

add $t0,$t0,$s1

lw $s0,100($t0)#deslocamento

£ 16 bits

Base mais índice escalado com 8 ou

32 bits de deslocamento

Escala

FIGURA 2.42 Modos de endereçamento de 32 bits do IA-32 com restrições de registrador e o código MIPS equivalente. O modo de endereçamento Base mais Índice Escalado, que não aparece no MIPS ou no PowerPC, foi incluído para evitar as multiplicações por quatro (fator de escala 2) para

transformar um índice de um registrador em um endereço em bytes (ver Figuras 2.34 e 2.36). Um fator de escala 1 é usado para dados de 16 bits, e um fator

de escala 3 para dados de 64 bits. O fator de escala 0 significa que o endereço não é escalado. Se o deslocamento for maior do que 16 bits no segundo ou

quarto modos, então o modo MIPS equivalente precisaria de mais duas instruções: um lui para ler os 16 bits mais altos do deslocamento e um add para

somar a parte alta do endereço ao registrador base $s1 (a Intel oferece dois nomes diferentes para o que é chamado modo de endereçamento com base com base e indexado -, mas eles são basicamente idênticos, e os combinamos aqui).

41

Instruções típicas do IA-32

• Quatro tipos principais de instruções de inteiro:

– Movimento de dados, incluindo move, push, pop

– Aritmética e lógica (registrador de destino ou memória)

– Fluxo de controle (uso de códigos de condição/flags)

– Instruções de string, incluindo movimento e comparação de strings

Instrução

JE nome

JMP nome

CALL nome

MOVW EBX,[EDI+45]

PUSH ESI

POP EDI

ADD EAX,#6765

TEST EDX,#42

MOVSL

Função

se for igual(códigos de condição) {EIP=nome};

EIP-128 nome < EIP+128

EIP=nome

SP=SP-4; M[SP]=EIP+5; EIP=nome;

EBX=M[EDI+45]

SP=SP-4; M[SP]=ESI

EDI=M[SP]; SP=SP+4

EAX= EAX+6765

Define códigos de condição (flags) com EDX e 42

M[EDI]=M[ESI];

EDI=EDI+4; ESI=ESI+4

FIGURA 2.43 Algumas instruções IA-32 típicas e suas funções. Uma lista de operações

freqüentes aparece na Figura 2.44. O CALL salva na pilha o EIP da próxima instrução (EIP é o PC da Intel).

42

Formatos de instruções IA-32

• Formatos típicos: (observe os diferentes tamanhos)

a. JE EIP + deslocamento

4

4

8

CondiDeslocamento

ção

JE

b. CALL

8

32

Deslocamento (offset)

CALL

c. MOV EBX, [EDI + 45]

6

1 1

8

8

MOV

d w

Pós-byte r/m

Deslocamento

d. PUSH ESI

5

3

PUSH

Reg

e. ADD EAX, #6765

4

3 1

32

Imediato

ADD Reg w

f. TEST EDX, #42

7

1

TEST

w

8

Pós-byte

32

Imediato

43

Resumo

• A complexidade da instrução é apenas uma variável

– instrução mais baixa versus CPI mais alta/velocidade de clock mais baixa

• Princípios de projeto:

– a simplicidade favorece a regularidade

– menor é mais rápido

– um bom projeto exige comprometimento

– torne o caso comum rápido

• Arquitetura do conjunto de instruções

– uma abstração muito importante!

44

Capítulo 3

45

Números

• Bits são apenas bits (nenhum significado inerente)

— convenções definem a relação entre bits e números

• Números binários (base 2)

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001...

decimal: 0...2n–1

• Obviamente, torna-se mais complicado:

números são finitos (overflow)

frações e números reais

números negativos

por exemplo, nenhuma instrução subi do MIPS; addi pode somar

um número negativo

• Como representamos os números negativos?

Por exemplo, que padrões de bit representarão esses números?

46

Representações possíveis

• Sinal e magnitude:

000 = +0

001 = +1

010 = +2

011 = +3

100 = –0

101 = –1

110 = –2

111 = –3

Complemento a um

000 = +0

001 = +1

010 = +2

011 = +3

100 = –3

101 = –2

110 = –1

111 = –0

Complemento a dois

000 = +0

001 = +1

010 = +2

011 = +3

100 = –4

101 = –3

110 = –2

111 = –1

• Questões: equilíbrio, número de zeros, facilidade de operações

• Qual é o melhor? Por quê?

47

MIPS

• Números de 32 bits com sinal:

0000

0000

0000

...

0111

0111

1000

1000

1000

...

1111

1111

1111

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000

0000 0000

0000 0000

0000bin = 0dec

0001bin = + 1dec

0010bin = + 2dec

1111

1111

0000

0000

0000

1111

1111

0000

0000

0000

1110bin

1111bin

0000bin

0001bin

0010bin

1111

1111

0000

0000

0000

1111

1111

0000

0000

0000

1111

1111

0000

0000

0000

1111 1111 1111 1111

1111 1111 1111 1111

1111 1111 1111 1111

1111

1111

0000

0000

0000

1111 1111

1111 1111

1111 1111

=

=

=

=

=

+

+

-

2,147,483,646dec

2,147,483,647dec

2,147,483,648dec

2,147,483,647dec

2,147,483,646dec

maxint

minint

1111bin = - 3dec

1111bin = - 2dec

1111bin = - 1dec

48

Operações de complemento a dois

• Negar um número de complemento a dois: inverta todos os bits e some 1

– lembre-se: “negar” e “inverter” são muito diferentes!

• Converter números de n bits em números com mais de n bits:

– o campo imediato de 16 bits do MIPS é convertido em 32 bits para aritmética

– copie o bit mais significativo (o bit de sinal) para os outros bits

0010 –> 0000 0010

1010 –> 1111 1010

• “extensão de sinal” (lbu versus lb)

49

Adição e subtração

• Exatamente como aprendemos na escola (emprestar/subir 1s)

0111

+ 0110

0111

– 0110

0110

– 0101

• Facilidade de operações do complemento a dois

– subtração usando adição para números negativos

0111

+ 1010

• Overflow (resultado muito grande para a word finita do computador):

– por exemplo, somar dois números de n bits não produz um número de n bits

0111

+ 0001

1000

note que o termo overflow é um pouco confuso;

ele não significa que um carry “transbordou”

50

Detectando overflow

• Nenhum overflow quando somar um número positivo com um negativo

• Nenhum overflow quando sinais são iguais para subtração

• O overflow ocorre quando o valor afeta o sinal:

– overflow ao somar dois positivos produz um negativo

– ou, somar dois negativos produz um positivo

– ou, subtraia um negativo de um positivo e obtenha um negativo

– ou, subtraia um positivo de um negativo e obtenha um positivo

• Considere as operações A + B e A – B

– Pode ocorrer overflow se B for 0?

– Pode ocorrer overflow se A for 0?

51

Efeitos do overflow

• Uma exceção (interrupção) ocorre

– O controle salta para um endereço predefinido para exceção

– O endereço interrompido é salvo para uma possível retomada

• Detalhes baseados na linguagem/sistema de software

– exemplo: controle de vôo versus dever de casa

• Nem sempre desejamos detectar overflow – novas instruções MIPS: addu, addiu,

subu

– Nota: addiu

– Nota: sltu, sltiu

ainda com extensão de sinal

para comparações sem sinal

52

Multiplicação

• Mais complexa do que a adição

– realizada através de deslocamento e adição

• Mais tempo e mais área

• Vejamos três versões baseadas em um algoritmo da escola

0010

x 1011

(multiplicando)

(multiplicador)

• Números negativos: converta e multiplique

– existem técnicas melhores mas não as veremos

53

Multiplicação: Implementação

Início

Multiplicador0 = 1

Multiplicando

1. Testar

Multiplicador0

Multiplicador0 = 0

1a. Soma multiplicando ao produto e

coloca o resultado no registrador Produto

Deslocar

à esquerda

64 bits

Multiplicador

Deslocar

à direita

ALU de 64 bits

2. Deslocar registrador Multiplicando 1 bit à esquerda

32 bits

Produto

Escrever

Teste de

controle

3. Deslocar registrador Multiplicador 1 bit à direita

64 bits

Não: < 32 repetições

32ª repetição?

Caminho de dados

Sim: 32 repetições

Controle

Fim

54

Versão final

• O multiplicador inicia na metade direita do produto

Início

Produto0 = 1

1. Testar

Produto0

Produto0 = 0

Multiplicando

32 bits

ALU de 32 bits

Deslocar à direita

Produto

Escrever

Teste de

controle

3. Desloque o registrador Produto 1 bit para a direita

64 bits

32ª repetição?

O que entra aqui?

Não: < 32 repetições

Sim: 32 repetições

Fim

55

Ponto flutuante (um breve exame)

• Precisamos de uma maneira de representar

– números com frações, por exemplo, 3,1416

– números muito pequenos, por exemplo, 0,000000001

– números muito grandes, por exemplo, 3,15576 × 109

• Representação:

– sinal, expoente, significando: (–1)sinal × significando × 2expoente

– mais bits para o significando fornece mais precisão

• mais bits para o expoente aumenta a faixa

• Padrão de ponto flutuante IEEE 754:

– precisão única: expoente de 8 bits, significando de 23 bits

– precisão dupla: expoente de 11 bits, significando de 52 bits

56

Padrão de ponto flutuante IEEE 754

• O bit “1” inicial do significando está implícito

• O expoente é “desviado” para facilitar a classificação

– todos os 0s são o menor expoente, todos os 1s são o maior

– desvio do 127 para precisão única e do 1023 para precisão dupla

– resumo: (–1)sinal × (1 + significando) × 2expoente – desvio

• Exemplo:

– decimal: –0,75 = – ( ½ + ¼ )

– binário: –0,11 = – 1,1 × 2–1

– ponto flutuante: expoente = 126 = 01111110

– precisão única IEEE: 10111111010000000000000000000000

57

Adição de ponto flutuante

Expoente

Sinal

Fração

Expoente

Sinal

Fração

1. Compare os expoentes dos dois números.

Desloque o menor número para a direita até

que seu expoente combine com o expoente maior.

ALU pequena

Diferença

do expoente

0

Início

2. Some os significandos

0

1

0

1

3. Normalize a soma, deslocando para a direita

e incrementando o expoente, ou deslocando para

a esquerda e decrementando o expoente.

Desloca

à direita

Controle

1

Overflow ou

underflow?

ALU grande

Sim

Não

0

0

1

Exceção

1

4. Arredonde o significando para

o número de bits apropriado

Incrementa ou

decrementa

Desloca para

esquerda ou direita

Não

Hardware de

arredondamento

Ainda

normalizado?

Sim

Sinal

Expoente

Fração

Fim

58

Complexidades do ponto flutuante

• As operações são um pouco mais complicadas (veja o texto)

• Além do overflow podemos ter o “underflow”

• A precisão pode ser um grande problema

– O IEEE 754 mantém dois bits extras, guarda e arredondamento

– quatro modos de arredondamento

– positivo dividido por zero produz “infinidade”

– zero dividido por zero não produz um número

– outras complexidades

• Implementar o padrão pode ser arriscado

• Não usar o padrão pode ser ainda pior

– veja no texto a descrição do 80x86 e o bug do Pentium!

59

Resumo do Capítulo 3

• A aritmética de computador é restrita por uma precisão limitada

• Os padrões de bit não têm um significado inerente mas existem padrões

– complemento a dois

– ponto flutuante IEEE 754

• As instruções de computador determinam o “significado” dos padrões de bit

• O desempenho e a precisão são importantes; portanto, existem muitas

complexidades nas máquinas reais

• A escolha do algoritmo é importante e pode levar a otimizações de hardware

para espaço e tempo (por exemplo, multiplicação)

• Você fazer uma revisão pode ser uma boa idéia (a Seção 3.10 é uma ótima leitura!)

60

Capítulo 4

61

Desempenho

• Meça, informe e resuma

• Faça escolhas inteligentes

• Veja através da propaganda de marketing

• Vital para entender a motivação organizacional subjacente

Por que alguns hardwares são melhores do que outros

para diferentes programas?

Que fatores do desempenho de sistema são relacionados

ao hardware? (por exemplo, precisamos de uma nova

máquina ou de um novo sistema operacional?)

Como o conjunto de instruções da máquina afeta o

desempenho?

62

Qual destes aviões possui o melhor desempenho?

Avião

Passageiros

Autonomia

(milhas)

Velocidade

(milhas por hora)

Boeing 737-100

101

630

598

Boeing 747

470

4150

610

BAC/Sud Concorde

132

4000

1350

Douglas DC-8-50

146

8720

544

• O quanto mais rápido é o Concorde comparado com o 747?

• O quanto maior é o 747 do que o Douglas DC-8?

63

Desempenho do computador: TEMPO, TEMPO, TEMPO

• Tempo de resposta (latência)

– Quanto tempo leva para meu trabalho ser realizado?

– Quanto tempo leva para realizar um trabalho?

– Quanto tempo preciso esperar para a consulta ao banco de dados?

• Vazão (throughput)

– Quantos trabalhos a máquina pode realizar ao mesmo tempo?

– Qual é a velocidade de execução média?

– Quanto trabalho está sendo feito?

• Se atualizarmos uma máquina com um novo processador, em que melhoramos?

• Se acrescentarmos uma máquina ao laboratório, em que melhoramos?

64

Tempo de execução

• Tempo decorrido

– conta tudo (acessos a disco e a memória, E/S etc.)

– um número útil, mas normalmente não é ideal para fins de comparação

• Tempo de CPU

– não conta E/S ou tempo gasto executando outros programas

– pode ser dividido em tempo de sistema e tempo de usuário

• Nosso foco: tempo de CPU do usuário

– tempo gasto executando as linhas de código que estão “em” nosso programa

65

Definição de desempenho do livro

• Para um programa sendo executado na máquina X,

DesempenhoX = 1 / Tempo_execuçãoX

• “X é n vezes mais rápido do que Y”

DesempenhoX / DesempenhoY = n

• Problema:

– a máquina A executa um programa em 20 segundos

– a máquina B executa o mesmo programa em 25 segundos

66

Ciclos de clock

• Em vez de informar o tempo de execução em segundos, normalmente usamos

ciclos

segundos

programa

=

ciclos

programa

x

segundos

ciclos

• As marcações de clock indicam quando iniciar as atividades (uma abstração):

tempo

• tempo de ciclo = tempo entre as marcações = segundos por ciclo

• velocidade de clock (freqüência) = ciclos por segundo (1 Hz. = 1 ciclo/segundo)

Um clock de 4 Ghz possui um tempo de ciclo de

1

x 1012 =250 picosegundos (ps)

9

4 x 10

67

Como melhorar o desempenho

segundos

programa

=

ciclos

programa

x

segundos

ciclos

• Portanto, para melhorar o desempenho (tudo mais sendo igual), você

pode (aumentar ou diminuir?)

o número de ciclos necessários para um programa, ou

o tempo de ciclo de clock ou, dito de outra maneira,

a velocidade de clock.

68

Quantos ciclos são necessários para um programa?

. . .

6ª instrução

5ª instrução

4ª instrução

3ª instrução

2ª instrução

1ª instrução

• Poderíamos considerar que o número de ciclos é igual ao número de instruções

Tempo

Essa suposição é incorreta;

diferentes instruções levam diferentes períodos de tempo em

diferentes máquinas.

Por quê? Dica: lembre-se de que essas são instruções de máquina,

não linhas de código C.

69

Diferentes números de ciclos para diferentes instruções

tempo

• A multiplicação leva mais tempo do que a adição

• As operações de ponto flutuante levam mais tempo do que as operações de inteiros

• Acessar a memória leva mais tempo do que acessar os registradores

• Importante: Mudar o tempo de ciclo normalmente muda o número de ciclos

necessários para várias instruções (veja mais posteriormente)

70

Exemplo

• Nosso programa favorito é executado em 10 segundos no computador A, que

possui um clock de 4 GHz. Estamos tentando ajudar um projetista de computador

a construir uma nova máquina B, que execute esse programa em 6 segundos.

O projetista determinou que um aumento substancial na velocidade de clock é

possível, mas esse aumento afetará o restante do projeto da CPU, fazendo com que

o computador B exija 1,2 vez mais ciclos de clock do que o computador A para esse

programa. Que velocidade de clock devemos pedir para que o projetista almeje?

• Não entre em pânico! Podemos resolver isso facilmente usando os princípios

básicos

71

Agora que entendemos os ciclos

• Um determinado programa exigirá

– um determinado número de instruções (instruções de máquina)

– um determinado número de ciclos

– um determinado número de segundos

• Temos um vocabulário que relaciona essas quantidades:

– tempo de ciclo (segundos por ciclo)

– velocidade de clock (ciclos por segundo)

– CPI (ciclos por instrução)

uma aplicação com excessivo uso de ponto flutuante pode

ter uma CPI mais alta

– MIPS (milhões de instruções por segundo)

isso seria mais alto para um programa usando instruções simples

72

Desempenho

• O desempenho é determinado pelo tempo de execução

• Qualquer uma das outras variáveis igualam o desempenho?

– número de ciclos para executar o programa?

– número de instruções no programa?

– número de ciclos por segundo?

– número médio de ciclos por instrução?

– número médio de instruções por segundo?

• Armadilha comum: pensar que uma das variáveis é indicadora do desempenho,

quando na realidade não é.

73

Exemplo de CPI

• Suponha que tenhamos duas implementações da mesma arquitetura do conjunto de

instruções (ISA)

Para um determinado programa,

A máquina A tem um tempo de ciclo de clock de 250 ps e uma CPI de 2,0

A máquina B tem um tempo de ciclo de clock de 500 ps e uma CPI de 1,2

Que máquina é mais rápida para esse programa e quão mais rápida ela é?

• Se duas máquinas possuem a mesma ISA, qual de nossas quantidades (por

exemplo, velocidade de clock, CPI, tempo de execução, número de instruções,

MIPS) será sempre idêntica?

74

Exemplo de número de instruções

• Um projetista de compilador está tentando decidir entre duas seqüências de código

para um determinada máquina. Com base na implementação de hardware, existem

três classes diferentes de instruções: Classe A, Classe B e Classe C, e elas exigem

um, dois e três ciclos, respectivamente.

A primeira seqüência de código possui 5 instruções: 2 de A, 1 de B e 2 de C.

A segunda seqüência possui 6 instruções: 4 de A, 1 de B e 1 de C.

Que seqüência será mais rápida? O quanto mais rápida? Qual é a CPI para cada

seqüência?

75

Exemplo de MIPS

• Dois compiladores diferentes estão sendo testados para uma máquina de 4 GHz

com três classes diferentes de instruções: Classe A, Classe B e Classe C, e elas

exigem um, dois e três ciclos, respectivamente. Ambos os compiladores são usados

para produzir código para um grande software.

O código do primeiro compilador usa 5 milhões de instruções da Classe A, 1 milhão

de instruções da Classe B e 1 milhão de instruções da Classe C.

O código do segundo compilador usa 10 milhões de instruções da Classe A, 1

milhão de instruções da Classe B e 1 milhão de instruções da Classe C.

• Que seqüência será mais rápida de acordo com o MIPS?

• Que seqüência será mais rápida de acordo com o tempo de execução?

76

Benchmarks

• A melhor forma de determinar desempenho é executando uma aplicação real

– Usa programas típicos do workload esperado

– Ou, típico da classe de aplicações esperada — por exemplo,

compiladores/editores, aplicações científicas, design gráfico etc.

• Benchmarks pequenos

– ótimos para arquitetos e projetistas

– fácil de padronizar

– pode ser forçado

• SPEC (System Performance Evaluation Cooperative)

– as empresas concordaram sobre um conjunto de programas e entradas reais

– valioso indicador do desempenho (e da tecnologia do compilador)

– ainda pode ser forçado

77

Jogos de benchmark

• A Intel reconheceu, envergonhada, na sexta-feira que um bug em um programa de

software conhecido como um compilador levou a empresa a anunciar uma

velocidade 10 por cento maior dos seus chips microprocessadores em um

benchmark da área. Entretanto, os analistas do setor disseram que o erro de

codificação foi um comentário infeliz sobre uma prática comum de “mentir” nos

testes de desempenho padronizados. O erro foi atribuído à Intel dois dias atrás pela

concorrente Motorola, em um teste conhecido como SPECint92. A Intel reconheceu

que havia “otimizado” seu compilador para melhorar suas pontuações de teste.

A empresa também havia dito que não gostava da prática, mas que foi forçada

a fazer as otimizações porque seus concorrentes estavam fazendo o mesmo.

No coração do problema da Intel está a prática de “ajustar” os programas de

compilador para reconhecerem certos problemas de computação no teste e, então,

substituir por partes especiais do código escritas a mão.

Sábado, 6 de janeiro de 1996 — New York Times

78

SPEC ‘89

• “Melhorias” e desempenho de compilador

800

700

Taxa de desempenho SPEC

600

500

400

300

200

100

0

gcc

espresso

spice

doduc

nasa7

li

Benchmark

eqntott

matrix300

fpppp

tomcatv

Compilador

Compilador melhorado

79

SPEC CPU2000

Benchmarks de inteiros

Nome

gzip

vpr

gcc

mcf

crafty

parser

eon

perlbmk

gap

vortex

bzip2

twolf

Descrição

Compactação

Posicionamento e roteamento de circuitos FPGA

O compilador C Gnu

Otimização combinatória

Programa de xadrez

Programa de processamento de textos

Visualização por computador

Aplicação Perl

Teoria de grupo, interpretador

Banco de dados orientado a objetos

Compactação

Simulador de posicionamento e roteamento de circuitos

Benchmarks de ponto flutuante

Nome

Wupwise

Swim

Mgrid

Applu

Mesa

Galgel

Art

Equake

Facerec

Ammp

Lucas

Fma3d

Sixtrack

Apsi

Tipo

Cromodinâmica Quântica

Modelo de água rasa

Solver multigrade no campo 3D potencial

Equação diferencial parcial parabólica/elíptica

Biblioteca de gráficos tridimensionais

Dinâmica computacional de fluidos

Reconhecimento de imagem usando redes neurais

Simulação de propagação de ondas sísmicas

Reconhecimento de imagem de rostos

Química computacional

Teste de primalidade

Simulação de choque usando método de elementos finitos

Projeto de acelerador de física nuclear de alta energia

Meteorologia: distribuição de poluentes

FIGURA 4.5 Os benchmarks SPEC CPU2000. Os 12 benchmarks de inteiros no lado esquerdo da tabela são escritos em C e C++, enquanto os benchmarks de ponto flutuante no lado direito são escritos em Fortran (77 ou 90) e em C. Para obter mais informações sobre o SPEC e os benchmarks SPEC,

veja www.spec.org. Os benchmarks SPEC CPU usam o tempo de relógio como métrica, mas, como há pouca E/S, eles medem o desempenho da CPU.

80

SPEC 2000

Dobrar a velocidade de clock dobra o desempenho?

Uma máquina com uma velocidade de clock mais lenta pode ter um desempenho melhor?

81

Experiência

• Telefone para um grande vendedor de computadores e diga que você está com

dificuldade de decidir entre dois computadores diferentes, especificamente, que

está confuso quanto aos pontos fortes e fracos dos processadores

(Por exemplo, entre Pentium 4 2Ghz e Celeron M 1.4 Ghz)

• Que tipo de resposta você provavelmente receberá?

• Que tipo de resposta você poderia dar a um amigo com a mesma dúvida?

82

Lei de Amdahl

Tempo de execução após melhoria = Tempo de execução não afetado

+ (Tempo de execução afetado / Quantidade de melhoria)

• Exemplo:

“Suponha que um programa seja executado em 100 segundos em uma

máquina, com multiplicação responsável por 80 segundos desse tempo. O quanto

precisamos melhorar a velocidade da multiplicação se queremos que o programa

seja executado 4 vezes mais rápido?”

Que tal torná-lo 5 vezes mais rápido?

• Princípio: torne o caso comum rápido

83

Exemplo

• Suponha que melhoramos uma máquina fazendo todas as instruções de ponto

flutuante serem executadas cinco vezes mais rápido. Se o tempo de execução de

algum benchmark antes da melhoria do ponto flutuante é 10 segundos, qual será o

aumento de velocidade se metade dos 10 segundos é gasta executando instruções

de ponto flutuante?

• Estamos procurando um benchmark para mostrar a nova unidade de ponto

flutuante descrita acima e queremos que o benchmark geral mostre um aumento de

velocidade de 3 vezes. Um benchmark que estamos considerando é executado

durante 100 segundos com o hardware de ponto flutuante antigo. Quanto do tempo

de execução as instruções de ponto flutuante teriam que considerar para produzir

nosso aumento de velocidade desejado nesse benchmark?

84

Lembre-se

• O desempenho é específico a um determinado programa

– O tempo de execução total é um resumo consistente do desempenho

• Para uma determinada arquitetura, os aumentos de desempenho vêm de:

• aumentos na velocidade de clock (sem efeitos de CPI adversos)

– melhorias na organização do processador que diminuem a CPI

– melhorias no compilador que diminuem a CPI e/ou a contagem de instruções

– escolhas de algoritmo/linguagem que afetam a contagem de instruções

• Armadilha: esperar que a melhoria em um aspecto do desempenho de uma máquina

afete o seu desempenho total

85

Vamos construir um processador

• Estamos quase prontos para entrar no Capítulo 5 e iniciar a construção de um

processador

• Primeiro, vamos revisar a lógica booleana e construir a ALU de que precisaremos

(material do Apêndice B)

operação

a

32

ALU

resultado

32

b

32

86

Revisão: Álgebra booleana e portões

• Problema: Considere uma função lógica com três entradas: A, B e C.

A saída D é verdadeira se pelo menos uma entrada for verdadeira

A saída E é verdadeira se exatamente duas entradas forem verdadeiras

A saída F é verdadeira apenas se todas as três entradas forem verdadeiras

• Mostre a tabela de verdade para essas três funções.

• Mostre as equações booleanas para essas três funções.

• Mostre a implementação consistindo de portões inversores, AND e OR.

87

Uma ALU (unidade lógica aritmética)

• Vamos construir uma ALU para dar suporte às instruções andi e ori

– construiremos apenas uma ALU de 1 bit e usaremos 32 deles

operação

a

op a

b

res

resultado

b

• Implementação possível (soma-dos-produtos):

88

Revisão: o multiplexador

• Seleciona uma das entradas para ser a saída, com base em uma entrada de controle

S

Nota: chamamos isso de um mux de duas entradas, mesmo

que ele tenha três entradas!

A

0

B

1

C

• Vamos construir nossa ALU usando um MUX:

89

Diferentes implementações

• Não é fácil decidir a “melhor” maneira de construir algo

– não queremos entradas demais em um único portão

– não queremos ter que atravessar muitos portões

– para nossos objetivos, a facilidade de compreensão é importante

• Vejamos uma ALU de 1 bit para adição:

CarryIn

a

Sum

cout = a b + a cin + b cin

sum = a xor b xor cin

b

CarryOut

• Como poderíamos construir uma ALU de 1 bit para add, and e or?

• Como poderíamos construir uma ALU de 32 bits?

90

Construindo uma ALU de 32 bits

Operação

CarryIn

a0

b0

CarryIn

ALU0

CarryOut

Resultado0

CarryIn

ALU1

CarryOut

Resultado1

CarryIn

ALU2

CarryOut

Resultado2

Operação

CarryIn

a1

a

b1

0

1

Resultado

a2

b2

b

+

CarryOut

2

..

.

a31

b31

..

.

CarryIn

ALU31

..

.

Resultado31

91

E quanto à subtração (a – b)?

• Método do complemento a dois: simplesmente negue b e some.

• Como negamos?

• Uma solução muito inteligente:

Binvert

Operação

CarryIn

a

0

1

b

0

+

Resultado

2

1

CarryOut

92

Acrescentando uma função NOR

• Também podemos escolher inverter a. Como obtemos um “a NOR b”?

Operação

Ainvert

Binvert

a

CarryIn

0

0

1

1

b

0

+

Resultado

2

1

CarryOut

93

Adequando a ALU ao MIPS

• Precisamos oferecer suporte à instrução set-on-less-than (slt)

• lembre-se: slt é uma instrução aritmética

– produz um 1 se rs < rt e produz um 0 em caso contrário

– use subtração: (a–b) < 0 implica a < b

• Precisamos aceitar teste de igualdade (beq $t5, $t6, $t7)

• use subtração: (a–b) = 0 implica a = b

94

Suporte a slt

• Podemos imaginar a idéia?

Binvert

Binvert

CarryIn

CarryIn

a

a

Operação

Ainvert

Operação

Ainvert

0

0

0

0

1

1

1

1

Resultado

Resultado

b

0

+

b

0

+

2

2

1

1

Less

Less

3

3

Set

CarryOut

Detecção

de overflow

Overflow

Todos os outros bits

Use esta ALU para o bit mais significativo

95

Suporte a slt

Operação

Binvert

Ainvert

CarryIn

a0

b0

CarryIn

ALU0

Less

CarryOut

Resultado0

a1

b1

0

CarryIn

ALU1

Less

CarryOut

Resultado1

a2

b2

0

CarryIn

ALU2

Less

CarryOut

Resultado2

..

.

.

..

. . ..

..

a31

b31

0

..

. CarryIn

CarryIn

ALU31

Less

..

.

Resultado31

Set

Overflow

96

Teste de igualdade

• Observe as linhas de controle:

Operação

Bnegate

Ainvert

0000

0001

0010

0110

0111

1100

=

=

=

=

=

=

and

or

add

subtract

slt

NOR

a0

b0

CarryIn

ALU0

Less

CarryOut

a1

b1

0

CarryIn

ALU1

Less

CarryOut

CarryIn

ALU2

Less

CarryOut

a2

b2

0

• Nota: zero é um 1 quando o

resultado é zero!

..

.

.

..

. .. ..

.

a31

b31

0

Result0

Result1

..

.

Result2

..

. CarryIn

CarryIn

ALU31

Less

Zero

..

.

..

.

Result31

Set

Overflow

97

Conclusão

• Podemos construir uma ALU para aceitar o conjunto de instruções MIPS

– idéia básica: usar um multiplexador para selecionar a saída que desejamos

– podemos realizar subtração eficientemente usando o complemento a dois

– podemos duplicar uma ALU de 1 bit para produzir uma ALU de 32 bits

• Pontos importantes sobre hardware

– todos os portões estão sempre operando

– a velocidade de um portão é influenciada pelo número de entradas do portão

– a velocidade de um circuito é influenciada pelo número de portões na série (no

“caminho crítico” ou no “nível mais profundo da lógica”)

• Nosso foco principal: compreensão; entretanto,

– Mudanças inteligentes na organização podem melhorar o desempenho

(semelhante a usar melhores algoritmos no software)

– Vimos isso na multiplicação; agora vejamos na adição

98

Problema: o somador com carry ripple é lento

• Uma ALU de 32 bits é tão rápida quanto uma ALU de 1 bit?

• Existe mais de uma maneira de fazer adição?

– dois extremos: carry ripple e soma-de-produtos

Você consegue ver o ripple? Como você se livraria dele?

c1

c2

c3

c4

=

=

=

=

b 0 c0

b 1 c1

b 2 c2

b 3 c3

+

+

+

+

a 0 c0

a 1 c1

a 2 c2

a 3 c3

+

+

+

+

a0b0

a1b1c2 =

a2b2 c3 =

a3b3 c4 =

Inviável! Por quê?

99

Somador com carry look-ahead

• Um método intermediário entre nossos dois extremos

• Motivação:

– Se não soubéssemos o valor do carry-in, o que poderíamos fazer?

– Quando sempre geraríamos um carry?

g i = a i bi

– Quando propagaríamos o carry?

p i = ai + bi

• Nos livramos do ripple?

c1

c2

c3

c4

=

=

=

=

g0

g1

g2

g3

+

+

+

+

p 0 c0

p 1 c1

p 2 c2

p 3 c3

c2 =

c3 =

c4 =

Viável! Por quê?

100

Use princípio para construir somadores maiores

CarryIn

a0

b0

a1

b1

a2

b2

a3

b3

a4

b4

a5

b5

a6

b6

a7

b7

a8

b8

a9

b9

a10

b10

a11

b11

a12

b12

a13

b13

a14

b14

a15

b15

CarryIn

Resultado0–3

ALU0

P0

G0

pi

gi

C1

ci + 1

CarryIn

Unidade de carry lookahead

Resultado4–7

• Não podemos construir um somador de

16 bits dessa maneira... (grande demais)

ALU1

P1

G1

pi + 1

gi + 1

C2

• Poderíamos usar o carry ripple dos

ci + 2

CarryIn

somadores CLA de 4 bits

Resultado8–11

• Melhor ainda: use o princípio CLA

novamente!

ALU2

P2

G2

pi + 2

gi + 2

C3

ci + 3

CarryIn

Resultado12–15

ALU3

P3

G3

pi + 3

gi + 3

C4

CarryOut

ci + 4

101

Resumo da ALU

•

•

•

•

Podemos construir uma ALU para aceitar adição MIPS

Nosso foco está na compreensão, não no desempenho

Processadores reais usam técnicas mais sofisticadas para aritmética

Onde o desempenho não é vital, as linguagens de descrição de hardware permitem

que os projetistas automatizem completamente a criação do hardware!

module MIPSALU (ALUctl, A, B, ALUOut, Zero);

input [3:0] ALUctl;

input [31:0] A,B;

output reg [31:0] ALUOut;

output Zero;

assign Zero = (ALUOut==0); // Zero é verdadeiro se ALUOut é 0; vai para algum lugar

always @(ALUctl, A, B) // reavalia se estes mudarem

case (ALUctl)

0: ALUOut <= A & B;

1: ALUOut <= A | B;

2: ALUOut <= A + B;

6: ALUOut <= A - B;

7: ALUOut <= A < B ? 1:0;

12: ALUOut <= ~(A | B); // resultado é nor

default: ALUOut <= 0; // default é 0, não deverá acontecer;

endcase

endmodule

FIGURA B4.3 Uma definição comportamental em Verilog de uma ALU MIPS. Isso poderia ser sintetizado por meio

de uma biblioteca de módulos contendo operações aritméticas e lógicas básicas.

102

Capítulo 5

103

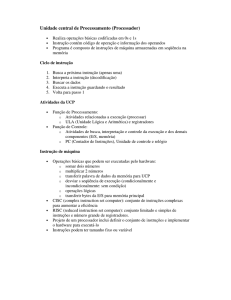

O processador: caminho de dados e controle

• Estamos prontos para ver uma implementação do MIPS

• Simplificada para conter apenas:

– instruções de referência à memória: lw, sw

– instruções lógicas e aritméticas: add, sub, and, or, slt

– instruções de fluxo de controle: beq, j

• Implementação genérica:

– use o contador de programa (PC) para fornecer endereço de instrução

– obtenha a instrução da memória

– leia os registradores

– use a instrução para decidir exatamente o que fazer

• Todas as instruções usam a ALU após lerem os registradores

Por quê? Referência à memória? Aritmética? Fluxo de controle?

104

Mais detalhes de implementação

• Visão abstrata/simplificada:

4

Add

Add

Dados

PC

Endereço

Instrução

Memória

de instruções

Nº do Registrador

Registradores

Nº do Registrador

Nº do Registrador

ALU

Endereço

Memória

de dados

Dados

Dois tipos de unidades funcionais:

– elementos que operam nos valores de dados (combinacionais)

– elementos que contêm estado (seqüenciais)

105

Elementos de estado

• Sem clock versus com clock

• Clocks usados na lógica síncrona

– quando um elemento que contém estado deve ser atualizado?

Transição de descida

Período de clock

Transição de subida

tempo de ciclo

106

Um elemento de estado sem clock

• O trinco set-reset

– a saída depende das entradas presentes e também das entradas passadas

R

Q

Q

S

107

Trincos e flip-flops

• A saída é igual ao valor armazenado dentro do elemento (não é necessário pedir

permissão para olhar o valor)

• A mudança do estado (valor) é baseada no clock

• Trincos: sempre que as entradas mudarem e o clock for afirmado

• Flip-flop: o estado muda apenas em uma transição

de clock (metodologia de acionamento por transição)

“Logicamente verdadeiro”

— poderia significar eletricamente baixo

Uma metodologia de clocking define quando os sinais podem ser lidos e quando

podem ser escritos — não desejaríamos ler um sinal ao mesmo tempo em que ele

estivesse sendo escrito

108

Trinco D

• Duas entradas:

– o valor de dados a ser armazenado (D)

– o sinal de clock (C) indicando quando ler e armazenar D

• Duas saídas:

– o valor do estado interno (Q) e seu complemento

C

Q

D

C

Q

Q

D

109

Flip-flop D

• A saída muda apenas na transição do clock

D

Q

D

C

Q

D

D

latch

D

latch

C

Q

Q

Q

C

D

C

Q

110

Nossa implementação

• Uma metodologia de acionamento por transição

• Execução típica:

– ler conteúdo de alguns elementos de estado,

– enviar valores através de alguma lógica combinacional

– escrever os resultados em um ou mais elementos de estado

Elemento

de estado

1

Lógica combinacional

Elemento

de estado

2

Ciclo de clock

111

Arquivo de registrador

• Construído usando flip-flops D

Registrador de

leitura número 1

Registrador 0

Registrador 1

...

Registrador de

leitura número 1

Registrador de

leitura número 2

Banco de registradores

Registrador

para escrita

Dados para

escrita

Registrador n – 2

Dados da

leitura 1

Dados da

leitura 2

M

u

x

Dados da

leitura 1

M

u

x

Dados da

leitura 2

Registrador n – 1

Registrador de

leitura número 2

Write

Você entende? Qual é o “Mux” acima?

112

Abstração

• Certifique-se de ter entendido as abstrações!

• Algumas vezes é fácil achar que entendeu, quando não entendeu

Select

A31

Select

B31

A

B

M

u

x

C31

32

32

M

u

x

32

C

A30

B30

M

u

x

C30

..

.

..

.

A0

B0

M

u

x

C0

113

Arquivo de registrador

• Nota: ainda usamos o clock real para determinar quando escrever

Escrita

C

0

1

Número do

registrador

Decodificador

n-para-2n

Registrador 0

..

.

D

C

Registrador 1

n –1

n

D

..

.

C

Registrador n – 2

D

C

Registrador n – 1

Dados para

o registrador

D

114

Implementação simples

• Inclui as unidades funcionais de que precisamos para cada instrução

Endereço

de instrução

EscreveMem

Instrução

Add Soma

PC

Memória

de instruções

a. Memória de instruções

b. Contador de programa

c. Somador

Endereço

Dados

para

escrita

Dados

da

leitura

Memória

de dados

16

Extensão

de sinal

32

LeMem

a. Unidade de memória de dados b. Unidade de extensão de sinal

5

Números dos

registradores

5

5

Dados

Registrador

de leitura 1

4

Dados da

leitura 1

Registrador

de leitura 2

Registradores

Registrador

para escrita

Dados da

leitura 2

Dados

para escrita

Dados

Operação da ALU

Zero

ALU

Resultado

da ALU

Por que precisamos disso?

EscreveReg

a. Registradores

b. ALU

115

Construindo o caminho de dados

• Use multiplexadores para uni-los

OrigPC

M

u

x

Add

Add

4

Deslocamento

de 2 à

esquerda

PC

Endereço

de Leitura

Instrução

Memória de

instruções

Registrador

de leitura 1

OrigALU

Dados

da leitura 1

Operação da ALU

EscreveMem

Registrador

de leitura 2

Registradores

Dados

Registrador

da

leitura

2

para escrita

M

u

x

Dados

para escrita

Zero

ALU

Resultado

da ALU

MemparaReg

Endereço

Dados

da leitura

M

u

x

Memória

Dados

de dados

para escrita

EscreveReg

16

4

Resultado

da ALU

Extensão

de sinal

32

LeMem

116

Controle

• Selecionar as operações a serem realizadas (ALU, leitura/escrita etc.)

• Controlar o fluxo de dados (entradas do multiplexador)

• Informações vêm dos 32 bits da instrução

• Exemplo:

add $8, $17, $18

Formato de instrução:

000000

10001

10010

01000

00000

100000

op

rs

rt

rd

shamt

funct

• Operação da ALU com base no tipo de instrução e código de função

117

Controle

• Por exemplo, o que a ALU deve fazer com essa instrução

• Exemplo: lw $1, 100($2)

35

2

1

op

rs

rt

100

offset de 16 bits

• Entrada do controle da ALU

0000

0001

0010

0110

0111

1100

AND

OR

add

subtract

set-on-less-than

NOR

• Por que o código para subtrair é 0110 e não 0011?

118

Controle

• Precisa descrever hardware para calcular entrada de controle da ALU de 4 bits

– tipo de instrução dada

00 = lw, sw

01 = beq,

OpALU calculado do tipo de instrução

10 = aritmética

– código de função para aritmética

• Descreva-o usando uma tabela verdade (pode se tornar portões):

OpALU

Campo func.

OpALU1

OpALU 0

F5

F4

F3

F2

F1

F0

Operação

0

X

1

1

1

1

1

0

1

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

0

0

0

0

1

X

X

0

0

1

1

0

X

X

0

1

0

0

1

X

X

0

0

0

1

0

0010

0110

0010

0110

0000

0001

0111

FIGURA 5.13 A tabela verdade para os três bits de controle da ALU (chamados Operação). As entradas são OpALU e o campo de código func.

Apenas as entradas para as quais o controle da ALU é ativado são mostradas. Algumas entradas “don’t care” foram incluídas. Por exemplo, como OpALU

não usa a codificação 11, a tabela verdade pode conter entradas 1X e X1, em vez de 10 e 01. Além disso, quando o campo func é usado, os dois primeiros

bits (F5 e F4) dessas instruções são sempre 10; portanto, eles são termos don’t care e são substituídos por XX na tabela verdade.

119

Add

4

Instrução [31:26]

PC

Endereço

de Leitura

RegDst

Branch

LeMem

MemparaReg

OpALU

EscreveMem

OrigALU

EscreveReg

Instrução [25:21]

Registrador

de leitura 1

Instrução [20:16]

Registrador

de leitura 2

Instrução

[31:0]

Memória de

instruções

Controle

Instrução [15:11]

Instrução [15:0]

0

M

u

x

1

Registrador

para escrita

Dados

da

leitura 1

Dados

da

leitura 2

1

M

u

x

0

Dados

para

escrita Registradores

16

Extensão

de sinal

Resultado

Add da ALU

Deslocamento

de 2 à

esquerda

Zero

ALU

Resultado

da ALU

0

M

u

x

1

Endereço

Dados

da

leitura

1

M

u

x

0

Dados Memória

para

de dados

escrita

32

Controle

da ALU

Instrução [5:0]

Instrução

formato R

lw

sw

beq

RegDst

1

0

X

X

OrigALU

0

1

1

0

Mempara

Reg

0

1

X

X

Escreve

Reg

1

1

0

0

Le

Mem

0

1

0

0

Escreve

Mem

0

0

1

0

Branch

0

0

0

1

ALUOpl

1

0

0

0

ALUOp0

0

0

0

1

120

Controle

• Lógica combinacional simples (tabelas verdade)

Entradas

Op5

Op4

Op3

Op2

OpALU

Op1

Bloco de controle da ALU

Op0

OpALU0

OpALU1

Saídas

F3

F2

F (5–0)

Operação 1

Operation

Iw

sw

beq

RegDst

OrigALU

MemparaReg

F1

Operação 0

F0

Formato R

Operação 2

EscreveReg

LeMem

EscreveMem

Branch

OpALU1

OpALU0

121

Nossa estrutura de controle simples

• Toda a lógica é combinacional

• Esperamos que tudo se acalme e a coisa certa seja feita

– a ALU pode não produzir a “resposta certa” imediatamente

– usamos sinais de escrita junto com o clock para determinar quando escrever

• Tempo de ciclo determinado pela duração do caminho mais longo

Elemento

de estado

1

Lógica combinacional

Elemento

de estado

2

Ciclo de clock

Estamos ignorando alguns detalhes como tempos de setup e hold

122

Implementação de ciclo único

• Calcule o tempo de ciclo considerando os retardos insignificantes, exceto:

– memória (200ps),

ALU e somadores (100ps)

acesso ao arquivo de registrador (50ps)

OrigPC

M

u

x

Add

Add

4

Deslocamento

de 2 à

esquerda

PC

Endereço

de Leitura

Instrução

Memória de

instruções

Registrador

de leitura 1

OrigALU

Dados

da leitura 1

Operação da ALU

EscreveMem

Registrador

de leitura 2

Registradores

Dados

Registrador

da leitura 2

para escrita

M

u

x

Dados

para escrita

Zero

ALU

Resultado

da ALU

MemparaReg

Endereço

Dados

da leitura

M

u

x

Memória

Dados

de dados

para escrita

EscreveReg

16

4

Resultado

da ALU

Extensão

de sinal

32

LeMem

123

Nosso direcionamento

• Problemas de ciclo único:

– e se tivéssemos uma instrução mais complicada, como ponto flutuante?

– desperdício de área

• Uma solução:

– usar um tempo de ciclo “menor”

– fazer com que diferentes instruções usem diferentes números de ciclos

– um caminho de dados “multiciclo”:

PC

Endereço

Registrador

de instrução

A

Nº do Registrador

Registradores

Nº do Registrador

Instrução

Memória ou dados

Dados

Dados

Registrador

de dados

da memória

ALU

SaídaALU

B

Nº do Registrador

124

Método multiciclo

• Vamos reutilizar unidades funcionais

– ALU usada para calcular endereço e incrementar o PC

– Memória usada para instrução e dados

• Nossos sinais de controle não serão determinados diretamente pela instrução

– por exemplo, o que a ALU deve fazer para uma instrução “subtração”?

• Usaremos uma máquina de estado finito para controle

125

Método multiciclo

• Divida as instruções em etapas, cada uma durando um ciclo

– equilibre a quantidade de trabalho a ser feito

– restrinja cada ciclo para usar apenas uma unidade funcional

• No final de um ciclo

– armazene os valores para uso em ciclos posteriores (a coisa mais fácil a fazer)

– introduza registradores “internos” adicionais

PC

0

M

u

x

1

Endereço

Memória

DadosMem

Dados

para escrita

Instrução

[25:21]

Instrução

[20:16]

Instrução

[15:0]

Registrador

de instrução

Instrução

[15:0]

Registrador

de dados

da memória

0

M

u

x

1

Registrador

de leitura 1

Instrução

[15:11]

0

M

u

x

1

0

M

u

x

1

16

Dados

da

Registrador leitura 1

de leitura 2

Registradores

Registrador Dados

da

para escrita