Transistor de Efeito de Campo

de Junção - JFET

Prof. Dr. Ulisses Chemin Netto ([email protected])

ET74C – Eletrônica 1

11 de Novembro de 2015

Objetivo da Aula

Conhecer a estrutura e operação do Transistor

de efeito de campo de junção.

ET74C – Eletrônica 1

2

Conteúdo Programático

Estrutura do JFET;

Funcionamento;

Curva Característica de saída.

ET74C – Eletrônica 1

3

Construção de Conhecimento

esperado

Familiarizar-se com as características estruturais

e operacionais do transistor de efeito de campo

de junção (JFET).

ET74C – Eletrônica 1

4

Divisão dos Transistores

NPN

Tipo de portador

majoritário

Bipolar

PNP

Transistor

Canal N

Unipolar

JFET

Canal P

Junction Field-Effect Transistor

ET74C – Eletrônica 1

5

Principal Diferença entre

Transistores

Bipolar

Unipolar

ET74C – Eletrônica 1

• Dois tipos de portadores envolvidos

no processo de condução de

corrente;

• Elétrons e Lacunas.

• Um único tipo de portador envolvido

no processo de condução de

corrente;

• Elétrons para o JFET de canal n;

• Lacunas para o JFET de canal p.

6

Principal Diferença entre

Transistores

O TBJ é controlado por corrente (IB);

IC=f(IB);

O JFET é controlado por tensão (VGS);

ID=F(VGS).

ET74C – Eletrônica 1

7

Principal Diferença entre

Transistores

A corrente de saída depende de um parâmetro da entrada

ET74C – Eletrônica 1

8

Principal Diferença entre

Transistores

O JFET possui uma impedância de entrada elevada;

– Valor típico com ordem de grandeza de M;

O ganho de tensão CA é menor do que aquele obtido

com o TBJ;

– Variação da corrente de saída é maior no TBJ.

• Em função da impedância de entrada elevada.

Menos suscetível a variações de temperatura do que o

TBJ;

Menores dimensões em relação ao TBJ → mais

adequado para construção de Circuitos Integrados.

ET74C – Eletrônica 1

9

Sugestão de Aplicação

Usa-se TBJ para grandes ganhos de tensão;

Usa-se JFETS para altas impedâncias de entrada;

Desenvolvimento de amplificadores de múltiplos

estágios combinando os dois tipos de transistores.

– JFET no primeiro estágio → alta impedância de entrada;

– TBJ, como Emissor-Comum, no segundo estágio → alto

ganho de tensão.

ET74C – Eletrônica 1

10

Similaridades entre transistores

Elemento com três terminais;

– Regiões análogas (emissor, base e coletor com fonte,

porta e dreno).

Aplicado para amplificação de sinais;

Construído com materiais do tipo n e p;

Aplicado como chave.

ET74C – Eletrônica 1

11

Similaridades entre transistores

Analogia entre os Terminais do TBJ e do JFET

TBJ

JFET

E

B

C

IE

IB

IC

S

G

D

IS

IG

ID

O conhecimento construído para o TBJ será aplicado ao JFET.

ET74C – Eletrônica 1

12

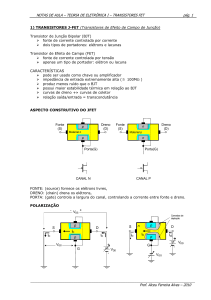

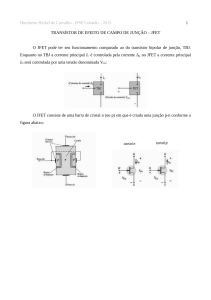

Construção do JFET

Características iniciais

– Há dois tipos de JFETS:

• de canal n;

• de canal p.

– JFETs têm três terminais:

• O Dreno – Drain – (D) e a Fonte – Source – (S) são

conectados pelo canal n;

• A porta – gate – (G) é conectada ao material do tipo p.

ET74C – Eletrônica 1

13

Construção do JFET

Ideia inicial

• Pedaço de material tipo n;

• Extermidade superior: Dreno (Drain);

• Extermidade inferior: Fonte (Source);

• A tensão VDD força os elétrons a

fluírem da Fonte para o Dreno através

do canal de material do tipo n.

Não se trata de um JFET ainda e sim do primeiro passo para

construção de um.

ET74C – Eletrônica 1

14

Construção do JFET

JFET canal n

• A maior parte do material é do tipo n;

• O material do tipo n forma o canal

entre os materiais do tipo p e possui

dopagem inferior ao material do tipo

p;

• Os materiais do tipo p estão

conectados entre si e ao terminal

Porta (G);

• Na ausência de potencial aplicado, o

JFET possui duas junções p-n não

polarizadas duas regiões de

depleção similares àquela do diodo.

ET74C – Eletrônica 1

15

Construção do JFET

JFET canal p

Porta (Gain)

Dreno

n

p

n

Fonte (Source)

ET74C – Eletrônica 1

16

Construção do JFET

Tensões importantes:

– VDS

• Tensão entre dreno e fonte;

– VGS

• Tensão aplicada entre a porta e a fonte.

ET74C – Eletrônica 1

17

Construção do JFET

Dreno - terminal a partir do qual os portadores

majoritários saem. A corrente no sentido

convencional que entra é designada por ID. A

tensão VDS é positiva se o potencial em D é mais

positivo que S.

ET74C – Eletrônica 1

18

Construção do JFET

Porta - Em ambos os lados do canal N, (no caso

do JFET canal N), são dispostas duas regiões

fortemente dopadas por impurezas aceitadoras

(material tipo P). É aplicada uma tensão VGS

para polarizar reversamente a junção pn entre

as regiões de porta e fonte.

Controle da

corrente ID

ET74C – Eletrônica 1

19

Construção do JFET

Fonte - terminal em que a corrente devida aos

portadores majoritários (elétrons) penetra no

canal. Designada por IS.

ET74C – Eletrônica 1

20

Construção do JFET

Analogia para o mecanismo de controle do JFET:

– Fonte: Pressão d’água comparada a tensão aplicada

entre o dreno e a fonte (VDS);

– Fluxo de água = fluxo de elétrons a partir da fonte em

direção ao dreno;

– Porta – controla o fluxo de elétrons por meio de um

sinal de controle (VGS) para o dreno.

ET74C – Eletrônica 1

21

Efeito de Campo

Significado:

– O caminho de circulação de corrente ID é controlado

pela tensão VGS;

• Essa tensão modifica a largura do canal n;

• O campo elétrico estabelecido entre a junção do material

p e n;

ET74C – Eletrônica 1

22

Construção do JFET

Símbolo:

Canal n

ET74C – Eletrônica 1

Canal p

23

Análise do JFET

Considerando VGS = 0V e VDS > 0

p

ET74C – Eletrônica 1

n

p

24

Análise do JFET

Considerando VGS = 0V e VDS > 0

Dreno

iD

• Fluxo

de

elétrons

(portadores

majoritários)

induzidos por VDS da fonte

para o dreno;

• Alteração forçada da zona

de depleção;

p

n

p

• Estabelece

o

sentido

convencional de corrente;

• ID=IS.

Fonte S

ET74C – Eletrônica 1

iS

25

Análise do JFET

Considerando VGS = 0V e VDS > 0

iD

Dreno

• Aumentando

aumenta-se

depleção.

a

VDS,

zona

de

• A região de depleção é mais

larga na parte superior do

material p;

p

n

p

• Por qual razão a zona de

depleção se modifica?

Fonte S

ET74C – Eletrônica 1

iS

26

Análise do JFET

Considerando VGS = 0V e VDS > 0

– Considerar a resistência do canal n uniforme;

– A corrente ID estabelece quedas de tensão ao longo

do canal – Distribuição de tensões ao longo do

canal;

– A região de depleção varia de acordo com a tensão

reversa aplicada (maior tensão – aumento da região

de depleção);

ET74C – Eletrônica 1

27

Análise do JFET

Considerando VGS = 0V e VDS > 0

– Como a junção pn porta-fonte está reversamente

polarizada, a corrente de porta é igual a zero (IG=0);

ET74C – Eletrônica 1

28

Análise do JFET

Considerando VGS = 0V e VDS > 0

• Se VGS = 0 V e VDS aumenta continuamente

para uma tensão mais positiva, um ponto é

alcançado onde a região de depleção fica tão

grande que “estrangula” o canal.

• Isso sugere que a corrente no canal (ID) cai

para 0 A, mas isso não acontece: à medida que

a VDS aumenta, a ID também aumenta.

Entretanto, uma vez que o pinch-off ocorre,

aumentos subsequentes na VDS não fazem com

que a ID aumente.

ET74C – Eletrônica 1

29

Análise do JFET

Considerando VGS = 0V e VDS > 0

No ponto do pinch-off:

o Qualquer aumento adicional da

VDS não produz nenhum aumento na

ID. No pinch-off, a VDS recebe o

nome de Vp.

o A ID está em saturação ou em seu

valor máximo, e é referida como

IDSS..

Corrente máxima de dreno quando VGS = 0V e VDS > |VP|

ET74C – Eletrônica 1

30

Análise do JFET

Considerando VGS = 0V e VDS > 0

• Ou seja, para VDS > VP o JFET se comporta como uma fonte de

corrente;

• ID=IDSS

• VDS é determinada pela carga.

ET74C – Eletrônica 1

31

Análise do JFET

Considerando VGS < 0V e VDS > 0

• À medida que a VGS se torna mais

negativa, a região de depleção

aumenta.

ET74C – Eletrônica 1

32

Análise do JFET

Considerando VGS < 0V e VDS > 0

ET74C – Eletrônica 1

33

Análise do JFET

Considerando VGS < 0V e VDS > 0

– A medida que VGS se torna mais negativa o JFET irá

saturar para valores menores de VDS;

– O valor de IDSS irá diminuir conforme VGS se torne mais

negativa;

– O valor de pinch-off diminui e passa a descrever uma

parábola conforme VGS se torne mais negativa;

– Quando VGS= –VP a saturação será, basicamente, ID= IDSS

= 0mA JFET desligado.

ET74C – Eletrônica 1

34

Análise do JFET

Considerando VGS < 0V e VDS > 0

– Em resumo:

“O valor de VGS que resulta em ID = 0mA é definido por

VGS=VP , sendo VP uma tensão negativa para

dispositivos de canal n e uma tensão positiva para

JFETS de canal p.”

ET74C – Eletrônica 1

35

Análise do JFET

Considerando VGS < 0V e VDS > 0

– Região ôhmica:

• Nessa região o JFET se comporta como um resistor

variável controlado pela tensão VGS;

• A inclinação de cada curva e portanto a resistência do

dispositivo entre dreno e fonte para VDS < VP é função de

VGS;

• Conforme VGS se torna mais negativa, a inclinação da

curva se torna mais horizontal, correspondendo a um

aumento de resistência.

ET74C – Eletrônica 1

36

Análise do JFET

ET74C – Eletrônica 1

37

Análise do JFET

JFET de canal p

• O JFET de canal p se comporta da

mesma forma que o JFET de canal n.

A diferenças são que as polaridadades

de tensão e as direções das correntes

são reversas.

ET74C – Eletrônica 1

38

Análise do JFET

JFET de canal p

• À medida que a VGS se torna mais positiva:

• A região de depleção aumenta, e

a ID diminui (ID < IDSS).

• A ID cai, por fim, a 0 A (quando

VGS = VGSoff)

• Observe também que a altos níveis de VDS o JFET atinge uma situação de

ruptura: a ID aumenta incontrolavelmente se VDS > VDSmáx.

ET74C – Eletrônica 1

39

Análise do JFET

Resumo para o JFET de canal n:

– A corrente máxima é definida por IDSS e ocorre

quando VGS=0V e VDS≥|VP|;

– Para tensões VGS menores do que o valor de pinchoff, a corrente de dreno ID = 0A;

– Para todos os valores de VGS entre 0V e o valor de

pinch-off, a corrente ID irá variar entre IDSS e 0A.

ET74C – Eletrônica 1

40

Análise do JFET

• As características de transferência de entrada a saída do JFET não

são tão simples quanto as do TBJ (IC=IB).

• TBJ: indica a relação entre IB (entrada) e IC (saída).

• JFET: a relação entre VGS (entrada) e ID (saída) é um pouco mais

complicada:

ID I

V

1 GS

DSS V

P

2

Equação de Shockley

ET74C – Eletrônica 1

41

Análise do JFET

• Este gráfico mostra o valor de ID para um dado valor de VGS.

ET74C – Eletrônica 1

A partir de IDxVDS é possível obter IDxVGS

42

Folha de Dados para o JFET

Os valores máximos de interesse são:

– A tensão entre dreno e fonte – VDS;

– A tensão entre dreno e porta – VDG;

– A tensão entre porta e fonte – VGS;

– A máxima corrente de porta – IG;

– A máxima potência dissipada – PD;

– O valor da corrente de saturação – IDSS;

– O valor da tensão de pinch-off – VP;

ET74C – Eletrônica 1

43

Folha de Dados para o JFET

Exemplo de folha de dados:

Tipo de encapsulamento

ET74C – Eletrônica 1

44

Folha de Dados para o JFET

Exemplo de folha de dados:

ET74C – Eletrônica 1

45

Folha de Dados para o JFET

Região de Operação:

Região para

Amplificação Linear

ET74C – Eletrônica 1

46

Relações importantes

As principais relações para análise do JFET e sua

comparação com o TBJ são apresentadas:

JFET

ET74C – Eletrônica 1

TBJ

47

Relações importantes

As principais relações para análise do JFET e sua

comparação com o TBJ são apresentadas:

ET74C – Eletrônica 1

48

Referências Utilizadas

BOYLESTAD, Robert L.; NASHELSKY, Louis.

Dispositivos eletrônicos e teoria de circuitos. 11.

ed. São Paulo: Pearson education do Brasil, 2013.

SEDRA,

Adel

S.;

SMITH,

Kenneth

C..

Microeletrônica. 5ed. São Paulo: Pearson Prentice

Hall, 2007.

MALVINO, Albert Paul. Eletrônica. 4. ed. São Paulo:

Makron, c1997. 2v.

ET74C – Eletrônica 1

49

Obrigado pela Atenção!

Prof. Dr. Ulisses Chemin Netto – [email protected]

Departamento Acadêmico de Eletrotécnica – DAELT – (41)3310-4626

Av. Sete de Setembro, 3165 - Bloco D – Rebouças - CEP 80230-901

Curitiba - PR - Brasil

ET74C – Eletrônica 1