www.mackenzie.com.br

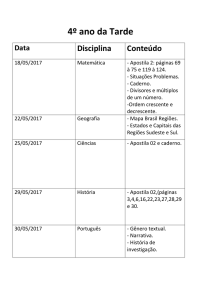

APOSTILA

MICROPROCESSADORES

PRIMEIRO SEMESTRE 2004

PROF. IVAIR REIS N. ABREU

www.ivair.com.br

Apostila de Microprocessadores

Ivair Reis N. Abreu

ÍNDICE

PLANEJAMENTO DIDÁTICO

4

1) - INTRODUÇÃO:

6

1.1) - Sistema Programável:

6

1.2) - Sistemas de Numeração:

6

1.3) - Estrutura de um microcomputador:

1.3.1) - Unidade Central de Processamento:

1.3.2) - Memória:

1.3.3) - Periféricos:

1.3.4) - Barramentos:

7

7

8

8

9

1.4) - Sinais envolvidos na escrita/leitura de dados na memória e periféricos:

9

1.5) - Arquitetura de um microprocessador:

10

1.6) - Conceito básicos:

1.6.1) - Temporização das Instruções - Ciclo de Instrução:

1.6.2) - Circuito de Inicialização:

1.6.3) - Interrupções:

1.6.4) - Acesso direto à memória (D.M.A):

1.6.5) - Multiplexação de sinais em microprocessadores:

1.6.6) – Sincronização de Dispositivos Lentos:

14

14

15

17

19

19

20

1.7) - Sistema Mínimo com o microprocessador 8085

1.7.1) - Principais características do 8085:

1.7.2) - Análise da arquitetura interna e pinagens:

1.7.3) - Sistema Mínimo com o 8085:

1.7.4) – Análise de 1 ciclo de temporização:

22

22

22

24

26

2.1) - Periféricos Paralelos:

2.1.1) - Utilização dos "latchs" como interface de saída:

2.1.2) - Utilização dos "latchs" como interface de entrada:

27

27

27

2.2) - Quadro comparativo entre Microprocessadores / Microcontroladores

30

2.3) - Arquitetura do Microcontrolador 8051:

2.3.1) - Descrição da pinagem:

2.3.2) - Descrição das funções internas:

30

31

32

2.4) - Sistema Mínimo com o 8051:

36

2.5) - Sistema Mínimo com o 8031 (ROMLESS):

36

3) - LINGUAGEM ASSEMBLER

2

39

3.1) - Introdução:

39

3.2) - Estrutura e diretivas da Linguagem Assembler:

40

Apostila de Microprocessadores

Ivair Reis N. Abreu

3.3) - Códigos de operação do microcontrolador 8051:

3.3.1) - Instruções de transferência de informação:

3.3.2) - Instruções Aritméticas:

3.3.3) - Instruções Lógicas:

41

41

44

45

3.4) - Exercícios de Linguagem Assembler do 8051:

49

3.5) - Projetos com o 8051:

50

3.5) - Projetos com o 8051:

51

4) - DISPLAY LCD PROGRAMÁVEL

52

4.1) - Introdução:

52

4.2) - Sistema mínimo com o display L.C.D. :

53

4.3) - Principais comandos utilizados:

53

4.4) - Escrita de dados no display:

56

4.5) - Exercícios:

56

5) - SISTEMA DE TEMPORIZAÇÃO E INTERRUPÇÃO DO 8051

57

5.1) - Sistema de Interrupção:

57

5.2) - Exercícios

57

5.3) - Aplicação de interrupção externa -> Sistema de Leitura direta de teclas.

58

5.4) - Exercício

59

5.5) - Sistema de temporização:

60

5.6) - Exercícios

61

7) - SISTEMA DE VARREDURA DE TECLADO/DISPLAY.

7.1) - Exercícios

8) – CONVERSORES ANALÓGICO / DIGITAIS E DIGITAIS / ANALÓGICOS

63

65

66

8.1) - Introdução:

66

8.2) – Conversor A/D ADC 0808

67

8.3) - Exercícios

67

Revisão:05/02/2004

3

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 1

Planejamento Didático

PLANEJAMENTO DIDÁTICO PEDAGÓGICO DA DISCIPLINA MICROPROCESSADORES

PRIMEIRO SEMESTRE 2004

TECNOLOGIA ELETRÔNICA

UNIDADE: FCEBI

DISCIPLINA: Microprocessadores

PROFESSOR: Ivair Reis Neves Abreu

DEPARTAMENTO: Eletrônica

ETAPA: 4

CÓDIGO

CARGA HORÁRIA: 8 aulas

CRÉDITOS

SEMESTRE LETIVO: segundo

OBJETIVOS: o aluno deverá adquirir os conceitos básicos de sistemas com microcontroladores ao

nível de projeto físico e programação em linguagem de montagem (e máquina) para teste do sistema

elaborado. Projetos básicos de sistemas práticos com microcontroladores deverão ser projetados.

EMENTA:

- Revisão de Conceitos de Microprocessadores

- Arquitetura do Microcontrolador 8051:

- Linguagem Assembler com as instruções do 8051:

- Projetos de Sistemas Práticos com Microcontroladores:

METODOLOGIA

Aula expositiva com auxílio de recursos audiovisuais (principalmente retroprojetor). O aluno deverá

constantemente participar através de aplicação de exercícios e projetos. Uma apostila envolvendo todos os

pontos abordados servirá de apoio didático durante as exposições. Trabalhos levarão o aluno a refletir sobre

pontos avançados não abordados diretamente na sala de aula.

CRITÉRIO DE AVALIAÇÃO:

Média = (0,2 x Lab + 0,8x P1) x 0,6 + P2 x 0,4

onde P1 = primeira prova semestral

P2 = segunda prova semestral.

Lab = laboratório

Média > 7 -> aluno aprovado

5,5 <= média <= 6.9 -> aluno aprovado se presença no curso > 80%

Calendário de Provas

P1

P2

4

-> 12/04/2004

-> secretaria

Apostila de Microprocessadores

Ivair Reis N. Abreu

CONTEÚDO PROGRAMÁTICO:

- Revisão de Conceitos de Microprocessadores (Arquitetura e Linguagem Assembler)

- Arquitetura do Microcontrolador 8051:

- Definir Arquitetura típica de microcontrolador

- Estudo da Arquitetura da família de microcontrolador 8051 da Intel.

- Sistema Mínimo com o 8051.

- Linguagem Assembler com as instruções do 8051:

- Definir código de operação de instruções e mneumônicos do 8051. Instruções de

transferência de informação, aritmética, lógica, transferência de controle e booleana.

- Estudo de rotinas típicas de controle: rotina de tempo, escrita e leitura de periféricos.

- Projetos de Sistemas Práticos com Microcontroladores:

- Alarme Residencial.

- Controle de Iluminação.

- Automação Industrial e Residencial.

- Estudo do Sistema de Interrupção do microcontrolador 8051. Aplicações.

- Estudo do Sistema de Temporização do microcontrolador 8051. Aplicações.

- Interface para teclados e displays com varredura. Aplicações.

- Interface para display de cristal líquido. Aplicações.

- Conversores A/D e D/A com microcontroladores

- Projetos completos de sistemas de controle com microcontroladores 8051.

BIBLIOGRAFIA

-

APLICAÇÕES PRÁTICAS DO MICRONTROLADOR 8051. Vidal Pereira da Silva Jr. - Érica

MICROCONTROLADORES 8051. Salvador P. Gimenez. Prentice Hall

DATABOOK EMBEDED APLICATIONS 8051. Intel.

THE 8051 FAMILY OF MICROCONTROLLERS. Richard H. Barnett. Prentice Hall.

THE 8051 MICROCONTROLLER. I. Schott Mackenzie. Prentice Hall.

APOSTILA MICROPROCESSADORES . Ivair Reis Neves Abreu

Internet:

www.microcontroller.com

www.8052.com

www.vidal.com.br

www.questlink.com

www.microchip.com

www.ti.com

www.zilog.com

5

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 2

1) - Introdução:

1.1) - Sistema Programável:

A grande utilização dos microprocessadores nos sistemas eletrônicos

atuais vem do fato de serem programáveis, ou seja, estes sistemas são

compostos por um conjunto físico (Hardware) que realizará determinada

tarefa, orientado por uma seqüência de instruções conhecidas por programa

(Software), proporcionando grande versatilidade e poder de processamento.

SISTEMA PROGRAMÁVEL

HARDWARE

/

\

SOFTWARE

\___ TAREFA FINAL

/

O objetivo final do curso será dotar o aluno da capacidade de

projetar o hardware e software básico (BIOS) do sistema acima.

Pelo fato da parte física do sistema ser padronizada, consegue-se

uma otimização na produção de tal forma a conseguirmos um custo bastante

reduzido, viabilizando seu consumo mesmo a nível residencial. Pode-se

citar os exemplos dos computadores pessoais padrão IBM-PC. Com uma

produção do computador em grande escala, consegue-se um sistema mínimo de

trabalho com valores próximos a U$ 1.0000,00, valor pequeno se

considerarmos o seu poder de processamento através da diversidade de

programa compatível ao mesmo. Um mesmo computador é capaz, sem alteração

nenhuma ao nível de máquina, de torna-se um poderoso processador de

texto, ou apenas trocando-se o programa a ser chamado, ser um grande

parceiro em um jogo de xadrez.

1.2) - Sistemas de Numeração:

Devido a facilidade de implementação do sinal binário (através de

chaves transistorizadas - saturada ou cortada), toda a informação dentro

do computador (com exceção de interfaces analógica/digitais) possui a

forma binária. Por isso, é fundamental o perfeito conhecimento dos

diversos sistemas de numeração, bem como a conversão entre cada base.

- Decimal -> base 10.

- Binário -> base 2 -> mais fácil de chavear (através de

transistores, chaves, etc.)

- Hexadecimal binário -> converte cada 4 números binários em

números de 0 (0000B) a F (1111B)

- Decimal binário (B.C.D.) -> converte cada 4 números binários em

números de 0 (0000B) a 9 (1001B)

6

Apostila de Microprocessadores

Ivair Reis N. Abreu

- Octal -> converte cada 3 números binários em números de 0 (000B)

a 7 (111B).

Conversões importantes:

Binário -> Decimal

<Binário -> Hexadecimal

<-

Ex:1) - 1010 0110 -> binário

-> hexadecimal

2) - 255 -> decimal

-> binário

3) - 2A0FH -> hexadecimal

-> decimal

1.3) - Estrutura de um microcomputador:

Os sistemas programáveis podem ter as suas estruturas resumidas a 3

blocos: Unidade Central de Processamento (C.P.U), Memória e Periféricos.

Figura 1

1.3.1) - Unidade Central de Processamento:

Bloco com capacidade de realizar tarefas orientadas por instruções.

É o principal elemento de decisão do computador, podendo ser comparado ao

cérebro se o ser humano fosse um computador.

Quando a C.P.U. está encapsulada em um único chip, temos um

microprocessador. Devido ao poder de processamento dos

microprocessadores atuais, temos sua utilização bem além dos tradicionais

computadores, como por exemplo câmaras fotográficas (que já possuem

disquetes ao invés dos tradicionais filmes químicos), aparelhos de som,

televisores, etc.

7

Apostila de Microprocessadores

Ivair Reis N. Abreu

1.3.2) - Memória:

Bloco semicondutor com capacidade de armazenar informações.

Armazena basicamente as instruções a serem processadas (através de seus

códigos de operação), variáveis (como resultados de operações da C.P.U.)

ou dados dos periféricos.

O programa a ser processado deve

necessariamente estar presente na memória (por isso o tamanho cada vez

maior das memórias voláteis - RAMs - dos computadores atuais, pois os

programas têm tamanhos cada vez maiores).

A memória dos computadores pode ser dividida em volátil (RAM

estática / dinâmica) e não voláteis (ROM / PROM / EPROM / E2PROM), onde

está armazenado a BIOS do sistema ou o FIRMWARE - software dedicado a uma

única função.

A estrutura de memória em computadores pode ser do tipo VonNeumann (estrutura de memória única onde podemos colocar programa e dados

na mesma área) e Harvard (estrutura com memória para área de programa

separada da área de dados – sinal de leitura diferenciado).

1.3.3) - Periféricos:

Bloco de comunicação do conjunto micro/memória com o meio exterior.

Pode ser caracterizado como entrada (teclado, mouse, etc.) ou saída

(monitor, impressora, plotter, etc.)

Quando temos a C.P.U., memória RAM e ROM e periféricos encapsulados

em um único chip, temos o MICROCONTROLADOR. Este, apesar de não ter o

mesmo poder de processamento dos microprocessadores atuais, é bastante

adequado a funções de controle de sistemas dedicados (eletrodomésticos,

controladores numéricos industriais, coletores de dados, etc.).

Exercícios / Pesquisa Complementares

1)– Verificar os seguintes dados do seu computador pessoal:

-

Tipo de Processador

Velocidade de Processamento

Capacidade da memória RAM

Periféricos disponíveis

2) – Pesquisar quais os principais processadores da Intel lançados (do

4004 ao Pentium 3 destacando a evolução entre cada processador).

8

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 3

1.3.4) - Barramentos:

- Bus endereço: carrega a informação binária da localização de um

dado de memória ou E/S. A capacidade de acesso é determinada pela

expressão 2n.

Ex: 8085 -> 16 bits na via de endereço -> 216 = 65512 kbytes

8088 -> 20 bits na via de endereço -> 1 Mbyte

- Bus dados: carrega a informação de instrução (através do código

de operação), variável do processamento ou dispositivo E/S. O tamanho

da via de dados determina respectivamente o máximo número de instruções

(e portanto o potencial de processamento) e a precisão do processamento

aritmético (através do cálculo de ponto flutuante).

Ex: 8085 -> 8 bits na via de dados -> 28 = 256 instruções e dados

com precisão de 8 bits.

8086 -> 16 bits na via de dados -> capacidade de até 65512

instruções (portanto mais versatilidade) e dados com precisão de 16 bits.

Instrução MOV

A,B

-> código de operação 78H (8085)

armazenado na memória que utiliza o barramento de dados para entrar no

microprocessador.

-

Tipos de Barramentos:

PCI, etc.)

serial (Ex.: I2C e SPI) e paralelo (ISA,

1.4) - Sinais envolvidos na escrita/leitura de dados na memória e periféricos:

__

- Sinal de Leitura (RD): sinal de saída do microprocessador

indicando a entrada de dados no mesmo. Coloca o barramento de dados como

entrada.

__

- Sinal de Escrita (WR): sinal de saída do microprocessador

indicando a saída de dados no mesmo. Coloca o barramento de dados como

saída.

_

- Sinal de Seleção entre memória/periféricos (IO/M): em nível alto

determina o endereçamento de periféricos. Em nível baixo o endereçamento

de memória.

Ex:

Instrução

MOV M,A

RD

->

WR

->

IO/M ->

Instrução IN 30H

RD

WR

->

->

9

Apostila de Microprocessadores

IO/M

Ivair Reis N. Abreu

->

1.5) - Arquitetura de um microprocessador:

Figura 2

- Unidade Lógica Aritmética (ULA): unidade responsável pela

realização de operações lógico/aritméticas no microprocessador. As

operações aritméticas são todas baseadas na soma (implementada através de

lógica 'OU EXCLUSIVO'). Toda lógica de decisão dos programas é baseada em

operações lógica/aritméticas. Por exemplo: a comparação entre duas

variáveis é implementada através da operação de subtração que por sua vez

é viabilizada pela operação de complemento de 2 ('A - B = A + /B + 1').

A complexidade da ULA do microprocessador determina a capacidade do mesmo

em realizar processamentos complexos (como tratamento de imagem ou som em

sistemas multimídia). Exemplos clássicos são os microprocessadores tipo

D.S.P. (Processador Digital de Sinais) ou os coprocessadores aritméticos

presentes na família de computadores PC até os microprocessadores 486-SX.

- Acumulador: principal registrador de auxílio da U.L.A. Bastante

acessado pelas instruções, é o registrador armazenador dos resultados da

U.L.A. O número de bits do acumulador pode ser do tamanho da via de

dados ou o dobro (para aumentar a precisão do resultado presente no

acumulador).

- Flag: registrador sinalizador de algumas condições do acumulador

(portanto do resultado) depois de realizadas operações lógico /

aritméticas. As condições encontradas normalmente são: zero, sinal,

"vai-um", "overflow", paridade, etc.

Ex: Flag do 8085:

______________________

| S | Z | - | AC | - | P | - | C |

10

Apostila de Microprocessadores

Ivair Reis N. Abreu

- S -> flag de sinal.

acumulador.

Indica a condição do oitavo bit do

S = 0 -> positivo

S=1 -> negativo

- Z -> flag indicar de zero.

Z = 1 -> zero no acumulador , Z = 0 -> número diferente

de zero.

- P -> flag de paridade.

P = 1 -> número par

Indica o número de '1' no acumulador.

, P = 0 -> número impar

- AC -> flag auxiliar carry.

segundo nibble do resultado.

Em 1 indica "vai um" entre primeiro e

- C -> flag carry principal.

acumulador.

Em 1 indica "estouro" ("overflow") do

Ex:

BBH + FAH

1 0 1 1 1 0 1 1

FLAG: S Z - AC - P - C

+

1 1 1 1 1 0 1 0

--------------Exemplo:

1) – Qual o conteúdo do Acumular e Flag da seguinte rotina?

no programa?

MOV

ADD

JZ

A,CAH

A,9DH

SALTO

Haverá salto

;CARREGA ACUMULADOR COM O NÚMERO CA

;SOMA A + 9D

;SALTA SE Z = 1

- Decodificador de Instruções: bloco lógico responsável por receber

o código de operação das diversas instruções e a partir deste gerar

sinais de controle externos e/ou internos, bem como sinais de

temporização, com o objetivo de executar a instrução. É implementado

através de lógica combinacional, onde as variáveis de entrada são o

código de operação do microprocessador e as variáveis de saída os

diversos sinais de controle e temporização internos/externos.

Exercícios / Pesquisa Complementares

1) – Pesquisar as principais características dos barramentos ISA e PCI do

computador PC.

2) – Pesquisar as principais características do barramento serial I2C

(site da Philips ou Microchip).

11

Apostila de Microprocessadores

Ivair Reis N. Abreu

3) – Pesquisar as principais características do co-processador aritmético

do processador Pentium II.

4) - Qual o conteúdo do Acumular e Flag da seguinte rotina?

no programa?

MOV

MOV

ADD

JNC

12

A,7AH

B,53H

A,B

SALTO

Haverá salto

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 4

- Registradores de uso geral: registradores para armazenamento de

dados ou endereços dentro do microprocessador. São implementados através

de "latchs" internos (podendo ser comparados a posições de memória dentro

do microprocessador). Quanto maior o número de registradores internos

maior é a velocidade de processamento, pois não é necessário o acesso à

memória externa para armazenamento de variáveis. É comum os

microcontroladores e os D.S.P.s possuírem algumas centenas de 'posições

de memória internas', diminuindo em muito o tempo de acesso à memória.

Outro exemplo bastante apropriado é a memória "caches" internas aos

microprocessadores 486 e PENTIUM.

- Contador de Programa (PC): registrador armazenador do endereço

da próxima instrução. Determina o fluxo do programa. Quando o

programador altera o valor do PC, necessariamente desvia o programa

(através de saltos sem retorno ou chamada de subrotinas).

Ex: Instrução: JMP 2000H -> carrega o PC com o endereço 2000H.

conteúdo anterior do PC é destruído (por isso o programa não consegue

voltar).

O

Instrução: CALL 2000H -> carrega o PC com o endereço 2000H.

Neste caso, o conteúdo anterior do PC

(PCH->SP-1 e PCL->SP-2) é salva

em uma região de memória (interna ou externa ao microprocessador)

conhecida por PILHA. Ao ser executada a instrução RET, o programa

retorna ao ponto em que foi chamado. A rotina acessada pela instrução

CALL é conhecida por subrotina. O conteúdo do registrador SP é

decrementado de dois para possibilitar o salvamento de outros parâmetros

na pilha (ou a chamada de outras subrotinas dentro de subrotinas)

Instrução: PUSH <registrador> -> guarda o conteúdo do

registrador na pilha. É utilizado para preservar o valor do registrador

ao retornar da sub-rotina.

POP

<registrador>

-> retorna com o valor do

registrador salvo na pilha.

0H LXI

1000H CALL

1003H :

2000H PUSH

2001H PUSH

2002H PUSH

SP,8000H

:

:

2000H

:

:

B

D

H

:

:

:

POP

POP

POP

RET

ÁREA DE PILHA

(SUBROTINA)

7FF8H =

7FF9H =

7FFAH =

7FFBH =

7FFCH =

7FFDH =

7FFEH =

7FFFH =

8000H

H

D

B

13

Apostila de Microprocessadores

Ivair Reis N. Abreu

- Apontador de Pilha (SP): registrador armazenador do endereço na

área de pilha do sistema. Será nesta área que serão armazenados

endereços de retorno das sub-rotinas, bem como parâmetros dos diversos

registradores.

1.6) - Conceito básicos:

1.6.1) - Temporização das Instruções - Ciclo de Instrução:

As atividades de um processador central são cíclicas. O

processador busca a instrução na memória, executa a tarefa ligada ao

código lido, busca a próxima instrução e assim por diante. A

temporização de um computador depende basicamente do sinal de clock que

sincroniza todas as operações do sistema. O clock é gerado a partir de

um oscilador com freqüência determinada normalmente por um cristal. Este

cristal pode estar interno ao microprocessador ou ser implementado

através de um C.I. dedicado a isto. A figura abaixo mostra um exemplo de

clock gerado internamente dentro do microprocessador 8085:

Figura 5

Chama-se ciclo de instrução o número de períodos de clock

necessários para executar uma instrução. O ciclo de instrução é composto

basicamente do ciclo de busca da instrução (onde o código de operação é

lido na memória) e ciclo de execução. O período de tempo necessário para

o microprocessador fazer um acesso externo (a memória ou periférico) é

conhecido por ciclo de máquina (representados pela letra 'M' no diagrama

de temporização da instrução). O ciclo de busca da instrução vai

depender do número de bytes necessários para a leitura da instrução (por

exemplo: o 8085 possui instruções de até 3 bytes que obviamente

necessitam de 3 ciclos de busca de códigos na memória). O tempo total

necessário para o ciclo de instrução é determinado pelo número de estados

14

Apostila de Microprocessadores

Ivair Reis N. Abreu

T (ou número de pulsos do clock) fornecidos pelo conjunto de instruções

do microprocessador.

Exercícios:

1) - Calcular os ciclos M1, M2 e o ciclo de instrução para a instrução

MOV A,B utilizando fc = 6 Mhz, n = 3, M1 = 4 clocks e M2 = 3 clocks.

2) - Idem para a instrução OUT 10h, fc = 1 Mhz, n=4, M1 = 4 clocks, M2 =

3 clocks e M3 = 3 clocks.

1.6.2) - Circuito de Inicialização:

Também conhecido por "reset", a entrada de inicialização nos

microprocessadores carrega o registrador de endereço PC com o endereço

inicial da área de programa (normalmente 0). Pode ser acionado com sinal

positivo (0 -> 1) ou negativo (1 -> 0). O manual do microprocessador

normalmente informa o tempo mínimo necessário para que o sinal de reset

fique ativo de tal forma a se determinar a constante RC do circuito. É

fundamental que o sinal de reset seje gerado cada vez que o

microprocessador seje ligado (reset automático) e em pequenas quedas de

rede (pois o microprocessador quando tem a tensão de alimentação abaixo

do nível mínimo recomendado, passa a executar tarefas fora do controle).

O circuito abaixo mostra o reset utilizado pelo 8085 (lógica positiva,

reset manual e automático). Nota-se a função do diodo em descarregar

rapidamente o capacitor em caso de queda de energia.

Figura 6

- Watch Dog: circuito supervisório que inicializa o

microprocessador a cada período de tempo configurável (1 ou 2 segundos

normalmente) se não receber um sinal do microprocessador. Desta forma o

programa do sistema deve, em um tempo menor que o tempo do W.D., gerar

este sinal. Se o programa se perder e não gerar o referido sinal, o W.D.

inicializará o microprocessador.

Exemplo:

1) - Determinar o mínimo valor de um capacitor para um circuito de reset

automático considerando:

15

Apostila de Microprocessadores

Ivair Reis N. Abreu

Vcc = 5V, Vreset = 2/3 Vcc

R = 100k

Freqüência: 100 Mhz

Número de clocks mínimo para reset: 100

2) – Calcular o período dos ciclos M1 (4 clocks), M2 (3 clocks) e o ciclo

de instrução para a instrução MOV A,B, freqüência do cristal de 6 Mhz.

3) – Idem para a instrução OUT 10h, fc = 1 Mhz e M1=4clocks, M1'= 3

clocks e M2 = 3 clocks.

16

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 5

1.6.3) - Interrupções:

Sinal de entrada no microprocessador gerado normalmente por

periféricos, fazendo o microprocessador parar seu processamento, salvar o

endereço atual, saltar para uma sub-rotina específica do periférico

(endereçado pelo vetor de interrupção, que pode ser fixo ou variável) e

posteriormente retornar ao ponto de parada (poderíamos comparar o

processo a uma chamada de sub-rotina através de um sinal de hardware).

Ex:

-Atendimento ao teclado: quando uma tecla é acionada, o

teclado gera um sinal positivo que ao entrar na interrupção do

microprocessador faz o mesmo parar o processamento, salvar o endereço

atual do PC na pilha e saltar para o endereço indicado no "vetor de

interrupção" (variável ou fixo).

-Interrupções disponíveis no 8085: 5 entradas de interrupções

ativadas em nível alto por um dispositivo externo. Neste caso, o 8085

interrompe a seqüência de execução do programa e salta para um endereço

pré-determinado (vetor de interrupção). As interrupções possuem os

seguintes vetores e prioridades:

Interrupções

+ priorit.

^

TRAP

|

|

RST6,5

|

|

RST6,5

|

|

RST5,5

|

|

INTR

Endereço

0024H

003CH

0034H

002CH

endereço fornecido por

um controlador de interrupção

Observa-se que a interrupção INTR necessita de um controlador de

interrupção (como o 8259 do IBM-PC) para gerar este endereço. Neste

caso, o microprocessador mostra o reconhecimento do endereço através do

sinal de saída INTRA.

17

Apostila de Microprocessadores

Ivair Reis N. Abreu

Figura 3

Dentro dos microprocessadores estão disponíveis registradores de

configuração que determinam interrupções pendentes e níveis de

prioridade.

No caso do IBM-PC, os vetores das 16 interrupções disponíveis para

periféricos (e programadas no 8259) são determinadas pelo sistema

operacional.

Exercícios / Pesquisa Complementares

1) - Levantar com o auxílio do Painel de Controle / Sistemas / Gerenciador de Sistemas / Propriedades os

vetores e periféricos do seu computador PC.

2) – Qual será o efeito para o computador se um modem for instalado na mesma interrupção / vetor do mouse?

3) – Explicar a diferença entre as instruções JMP 2000H e CALL 2000H.

4) – Quais as vantagens de utilizar sub-rotinas em programação.

18

Apostila de Microprocessadores

Ivair Reis N. Abreu

1.6.4) - Acesso direto à memória (D.M.A):

Sistema onde o barramento do computador é retirado do

microprocessador (colocando o mesmo em tri-state) e controlado através de

um outro microprocessador (multiprocessamento) ou através de um

controlador de D.M.A. (como o 8257) para transferência de dados entre

periféricos e memória.

Ex: 1) - Carga de programas de um "winchester" ou "floppy" para memória

RAM de um computador.

2) - Coprocessador aritmético nos computadores IBM-PC.

Figura 4

1.6.5) - Multiplexação de sinais em microprocessadores:

Consiste em um recurso de misturar 2 ou mais sinais em um terminal

do microprocessador com o objetivo básico de economizar pinagem do chip.

Um exemplo típico é a multiplexação da via de dados/endereço do 8085: os

8 bits de dados (D0-D7) são multiplexados no tempo com o byte menos

significativo de endereço (A0-A7). O sinal de controle "ALE" (sigla de

"Address Latch Enable") indica a natureza da informação presente naquele

instante.

ALE = 0 -> AD0-AD7 -> dados (D0-D7)

ALE = 1 -> AD0-AD7 -> endereços (A0-A7)

Ex:

19

Apostila de Microprocessadores

Ivair Reis N. Abreu

Figura 7

A separação da via de dados (D0-D7) da via de endereços (A0-A7) é

necessária pelo fato de termos diversos dispositivos de memória e

periférico com estes barramentos separados. A implementação desta

separação pode ser realizada com os latchs octais 74373 (unidirecional) e

74245 (bidirecional).

A figura abaixo mostra um circuito típico

utilizado na demultiplexação dos sinais de dados/endereço do 8085.

Figura 8

1.6.6) – Sincronização de Dispositivos Lentos:

O pino de entrada READY (em nível alto permite o funcionamento do

microprocessador e em nível alto o mesmo permanece em estado de espera –

“wait”). O dispositivo de sincronização de memória / periférico lento

20

Apostila de Microprocessadores

Ivair Reis N. Abreu

controla o sinal READY do processador de tal forma a fazer o mesmo

aguardar uma diferença de velocidade de acesso.

Ex: Qual o período de um pulso de espera (Wait State) para o acesso a uma

escrita no disco rígido considerando:

Ciclo de instrução de escrita: 10 clocks

Clock: 133 Mhz

Tempo de Acesso ao disco rígido: 100 microsegundos.

Exercícios / Pesquisa Complementares

1) - Determinar o mínimo valor de um capacitor para um circuito de reset

automático considerando:

Vcc = 3,3V

R = 10k

Freqüência: 500 Mhz

Número de clocks mínimo para reset: 500

2) – Qual o período de um pulso de espera (Wait State) para o acesso a

uma memória RAM rápida considerando:

Ciclo de instrução de escrita: 5 clocks

Clock: 500 Mhz

Tempo de Acesso a RAM: 15 nseg.

3) – Fazer um circuito de separação de dados / endereço de um processador

com um barramento AD0-AD15, com sinal de ALE. Colocar um Buffer para a

via de dados.

21

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 6

1.7) - Sistema Mínimo com o microprocessador 8085

1.7.1) - Principais características do 8085:

- 8 bits na via de dados (possui 246 instruções).

- 16 bits na via de endereço (acessa 64 k de memória e 256

periféricos).

- 5 entradas para interrupções.

- Interface serial.

- Controle de D.M.A.

- Controle de sincronização para periféricos lentos.

- Clock típico de 3 Mhz.

1.7.2) - Análise da arquitetura interna e pinagens:

Figura 9

1.7.2.1) - Descrição das principais funções internas:

- U.L.A: realiza operações aritméticas (soma, subtração, incrementação e

decrementação) e operações lógicas (AND, OR, OR EXCLUSIVO, Inversão,

deslocamentos bit a bit e comparação).

- FLAG:

registrador que sinaliza o resultado de operações da U.L.A.

- Acumulador: registrador de 8 bits com multiplas funções (armazena

resultados e operandos da U.L.A., dados de dispositivos de E/S, máscara

de interrupções, etc).

22

Apostila de Microprocessadores

Ivair Reis N. Abreu

- Registradores de uso geral: 6 registradores de 8 bits (armazenando

dados) podendo ser utilizados como pares de 16 bits (armazenando

endereços).

B C

/

Pares

Fixos

D E

\

H L -> par de registrador mais utilizado como

ponteiro de memória.

- Registrador contador de programa (PC): registrador de 16 bits com a

função específica de armazenar o endereço de busca da próxima instrução.

Quando carregado através de instrução altera o fluxo seqüencial do

programa ( realizando uma salto simples - instrução 'jump' - ou chamando

uma subrotina - instrução 'call').

- Registrador apontador de pilha (SP): registrador de 16 bits com a

função específica de armazenar o endereço final da área de memória

denominada "pilha" (onde são armazenados parâmetros de retorno das

subrotinas)

- Decodificador de instruções: bloco lógico interno com a função de

receber as instruções (códigos de operação que entram pela via de dados),

decodificando-as e gerando sinais de controle e temporização.

- Buffer de endereços alto (A8-A15): via de endereços mais

significativa formando junto com A0-A7 os 16 bits totais da via de

endereço.

- Controle Serial: o 8085 possui uma saída serial de dados (SOD)

controlada pela instrução SIM (coloca o oitavo bit do acumulador no pino

SOD) e uma entrada serial de dados (SID), controlada pela instrução RIM

(coloca o bit da entrada serial no oitavo bit do acumulador).

1.7.2.2) - Análise da pinagem do microprocessador 8085:

- Alimentações +5V e GND: alimentação única. Recomenda-se a colocação

de um capacitor cerâmico de desacoplamento com valor variando entre 10100 nF para eliminar ruídos.

- X1 e X2: pinos de entrada do cristal. Possui um oscilador interno

com a função de gerar um sinal de clock de 2 fases. Dispensa o circuito

dedicado gerador de clock.

- CLOCKOUT: saída de clock para periféricos.

freqüência do cristal ligado ao X1 e X2.

Tem a metade da

- RESETIN: entrada de reset do 8085. Inicializa o 8085 (colocando o PC

= 0000h e portanto buscando a primeira instrução) quando temos um nível

baixo por mais de 10 mseg.

23

Apostila de Microprocessadores

Ivair Reis N. Abreu

- RESETOUT: saída ativa em nível alto com a função de inicializar os

periféricos ligados ao 8085. Sincronizado com o sinal RESETIN.

- RD: saída ativa em nível baixo indicando processo de leitura de

memória ou periférico. Coloca o barramento de dados como entrada.

- WR: saída ativa em nível baixo indicando processo de leitura na

memória ou periférico. Coloca o barramento de dados como saída.

_

- IO/M: sinal de saída. Em nível alto indica acesso a periféricos. Em

nível baixo indica acesso a memórias.

- S0 e S1:

0

0

1

1

0

1

0

1

->

->

->

->

sinais de saída indicando status.

8085 parado

processo de

processo de

processo de

(HALT)

leitura

escrita

busca de instrução ("fetch")

- READY -> sinal de entrada com a função de sincronizar periférico ou

memória mais lenta que o 8085. Em nível alto habilita a operação do

8085. Em nível baixo para o 8085, fazendo-o permanecer em estado de

'WAIT'.

- HOLD: sinal de entrada. Em nível alto coloca barramentos de dado,

endereço e controle em "tri-state". Desta forma, um sistema externo

(controlador de D.M.A. ou um outro microprocessador mais prioritário)

assume um controle do barramento:

- HOLDA: saída ativa em nível alto indicando barramento em tri-state

para o controlador de D.M.A. ou para o microprocessador paralelo.

1.7.3) - Sistema Mínimo com o 8085:

FIGURA 10

24

Apostila de Microprocessadores

Ivair Reis N. Abreu

Exemplo:

1) – Projetar um sistema mínimo com o 8085 com as seguintes

características:

Clock – 4 Mhz

Reset automático / manual

5 periféricos ligados a 5 interrupções

Sistema DMA (representar em blocos)

Desabilitar sinal READY.

32 Kbytes de memória EPROM (2764)

32 Kbytes de memória RAM (6264)

8 Periféricos (endereço 00 – ff). Representar cada periférico por

um bloco.

Exercícios / Pesquisa Complementares

1) – Comparar o microprocessador Z80 com o 8085.

2) – Projetar um sistema mínimo com o 8085 com as seguintes

características:

Clock – 1 Mhz

Reset automático / manual

Desabilitar as interrupcões através de resistores de pull-down

Sistema DMA (representar em blocos)

Desabilitar sinal READY.

32 Kbytes de memória EPROM (27256)

32 Kbytes de memória RAM (62256)

8 Periféricos (endereço 00 – ff). Representar cada periférico por

um bloco.

3) – Projetar um sistema mínimo com o 8085 com as seguintes

características:

Clock – 2 Mhz

Reset automático / manual

Desabilitar as interrupcões através de resistores de pull-down

Sistema DMA (representar em blocos)

Desabilitar sinal READY.

16 Kbytes de memória EPROM (2764) – endereço 0-3fffh

32 Kbytes de memória RAM (62256) – endereço 8000h-bfffh

8 Periféricos (endereço 00 – ff). Representar cada periférico por

um bloco.

4) – Pesquisar no Painel de Controle do PC os endereços de memória e

periféricos do computador. Qual é a faixa de memória de vídeo?

5) – Projetar um banco de memória de um computador com 1 Mbytes tendo 512

K de eprom (271000) e 512 K de ram (621000).

25

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 7

1.7.4) – Análise de 1 ciclo de temporização:

Temporização da Instrução 'OUT <end>' (2 bytes) – Ex: OUT 20H (D3 20)

Figura 11

Exercício: Fazer um diagrama de tempo para a instrução IN 40H

26

Apostila de Microprocessadores

Ivair Reis N. Abreu

2) – Microcontroladores

2.1) - Periféricos Paralelos:

O periférico paralelo se caracteriza por controlar 2 ou mais sinais

simultaneamente. Uma forma simples de implementação é através de

"latchs" octais (8 flip-flops tipo D), como o 74LS373 apresentado na

figura abaixo:

Figura 12

2.1.1) - Utilização dos "latchs" como interface de saída:

Ex.: Projeto de acionamento de 8 lâmpadas de 100 W (de um sistema de

iluminação) com o "latch" 74LS373. Utilizar o sinal de endereço A8 para

selecionar o "latch". Fazer um programa para acender apenas a lâmpada 3.

Figura 13

2.1.2) - Utilização dos "latchs" como interface de entrada:

27

Apostila de Microprocessadores

Ivair Reis N. Abreu

Ex.: Projeto da leitura de 8 sensores de presença (tipo ultra-som

utilizado em alarmes) com o "latch" 74LS373. Utilizar o sinal de

endereço A8 em nível baixo para selecionar o "latch". Fazer um programa

para ler os 8 sensores e colocar sua condição na posição de memória

2000H.

Figura 14

Exemplo: Primeiro sensor controlando primeira lâmpada na o microprocessador 8085

IN

ANI

JZ

MOV

OUT

JMP

SALTA: MOV

OUT

FIM:

.....

20H

01

SALTA

A,#01

00

FIM

A,#00

00

Exercício:

1) - Fazer um programa para o primeiro sensor de um sistema (endereço 20H-3fH) ligue e desligue o quinto

motor (endereço 0-1fH).

28

Apostila de Microprocessadores

Ivair Reis N. Abreu

Exercícios / Pesquisa Complementares

1) – Representar o diagrama de tempo da instrução IN 20H do 8085 (lê o periférico de entrada de endereço

20h e coloca dado no acumulador).

2) – Utilizando os latchs 74373, fazer um sistema mínimo para o 8085 com as seguintes características:

Clock – 4 Mhz

Reset automático / manual

Desabilitar as interrupcões através de resistores de pull-down

Sistema DMA (representar em blocos)

Desabilitar sinal READY.

16 Kbytes de memória EPROM (2764) – endereço 0-3fffh

32 Kbytes de memória RAM (62256) – endereço 8000h-bfffh

Controle de 8 lâmpadas (endereço 0-1fh)

Entrada de 8 interruptores (endereço 20h-3fh)

3) – Fazer um controle de 8 motores (40h – 5fh) chaves 8 chaves (60h – 7fh). Fazer a quinta chave ligar ou

desligar os 8 motores.

29

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 8

2.2) - Quadro comparativo entre Microprocessadores / Microcontroladores

Características

Velocidade

Consumo

Memória de Programa

Memória de Dados

Arquitetura de Memória

Barramento

Aplicação

Microcontrolador

Lenta ( típico < 1Mhz)

Baixo (uA)

Pequena capacidade (kbytes)

Mínima (bytes)

Harvard (típica)

8 bits (dados)

fechada, firmware

Microprocessador

Rápida (típico > 1 Ghz)

Alto ( ventilador, fonte chav.)

Grande capacidade (mbytes)

Grande capacidade (mbytes)

Von- Newmann

> 64 bits (dados)

aberta, multimidia

2.2) - Família de Microcontroladores INTEL MCS-51:

A linha de microcontroladores MCS-51 de 8 bits sucedeu a antiga

família MCS-48. Os principais recursos destes microcontroladores são:

- Memória de Programa de 4 kbytes: ROM (8051), EPROM (8751).

Versão "romless" (8031).

- 256 bytes de RAM (registradores)

- 4 ports (latchs bidirecionais programáveis) com 8 bits.

- 2 temporizadores ("timers") de 16 bits

- 1 unidade serial assíncrona (UART) "full-duplex".

- 5 interrupções (2 externas, 2 "timers" e 1 "UART").

- Oscilador interno para geração de temporização.

- Acesso a até 64 Kbytes de RAM externa (dados) e 64 Kbytes de

EPROM (programa) externa através do controle de 2 sinais de leitura (PSEN

-> área de programa - RD -> área de dados). Esta estrutura é conhecida

como 'arquitetura HARVARD'.

- 256 instruções otimizadas para controle.

2.3) - Arquitetura do Microcontrolador 8051:

30

Apostila de Microprocessadores

Ivair Reis N. Abreu

Figura 15

2.3.1) - Descrição da pinagem:

- Vcc,Gnd:

alimentação única de 5 Vcc.

- X1-X2: conectada ao cristal externo (12 Mhz típico). O sistema

de temporização interno divide a freqüência do cristal por 12,

proporcionando um ciclo típico de máquina de 1 mseg.

- RST: entrada de inicialização ativa em nível alto

__

- EA ("external acess"): em nível baixo, desabita os 4 kbytes de

memória de programa interna. Toda a busca de instrução é realizada

externamente (através de uma EPROM). Em nível alto habilita a memória

interna.

31

Apostila de Microprocessadores

Ivair Reis N. Abreu

Figura 16

- ALE ("Address Latch Enable"): na utilização de memória de

programa externa, este pino tem a função de indicar a presença de

endereço (em nível alto) ou dado (em nível baixo) no barramento de

endereço/dado multiplexado (AD0-AD7).

____

- PSEN ("Program Strobe Enable"): em nível baixo indica leitura de

uma instrução da área de programa. Normalmente ligado ao pino RD da

memória de programa.

- Port P0 (P0.0-P0.7): seus 8 pinos podem ter dupla função. Se

não houver memória externa, são utilizados como sinais de entrada/saída

do "latch" bidirecional P0. Se houver memória externa, atua como 8

sinais multiplexados de dados/endereço (AD0-AD7). O sinal de ALE indica

a condição deste barramento.

- Port P1 (P1.0-P1.7):

bidirecional P1.

8 pinos de entrada/saída do "latch"

- Port P2 (P2.0-P2.7): seus 8 pinos também podem ter dupla função.

Se não houver memória externa com mais de 256 endereços, são utilizados

como sinais de entrada/saída do "latch" bidirecional P2. Se houver

necessidade de endereçamento maior que 8 bits, atua como 8 sinais de

endereço A8-A15.

- Port P3 (P3.0-P3.7):

P3.6

-

P3.0:

P3.1:

P3.2:

P3.3:

P3.4:

P3.5:

P3.6:

novamente, seus 8 sinais tem dupla função:

RxD (recepção serial) / port P3.0

TxD (transmissão serial) / port P3.1

INT0 (interrupção 0) / port P3.2

INT1 (interrupção 1) / port P3.3

T0 (entrada Timer 0) / port P3.4

T1 (entrada Timer 1) / port P3.5

WR (sinal de escrita da RAM externa)/port

P3.7: RD (sinal de leitura da RAM externa)/port

P3.7

2.3.2) - Descrição das funções internas:

- U.L.A.: unidade lógia aritmética de 8 bits, responsável pela

execução das 4 operações aritméticas básicas e das operações lógicas

tradicionais (AND, OR, OR EXCLUSIVE, INVERSÃO e SHIFT).

- Acumulador: registrador de 8 bits mais utilizado pelo

microcontrolador. Normalmente utilizado para colocar resultados da

U.L.A. ou fatores utilizados nas operações lógico / aritméticas. No caso

das operações de multiplicação, o registrador B também é utilizado para

colocação dos resultados, pois o resultado é apresentado em 16 bits.

- Flag PSW: registrador sinalizador das operações aritméticas da

U.L.A., configurador dos registradores R0-R7 e para uso geral. Abaixo é

mostrado a posição e nome de seus 8 bits:

32

Apostila de Microprocessadores

CY

Ivair Reis N. Abreu

AC

F0

RS1

RS0

OV

-

P

CY (PSW.7): indica presença de bit CARRY (vai um) nas operações

aritméticas da U.L.A.

AC (PSW.6): indica presença do bit Auxiliar Carry quando ocorre vai

um entre os 3 e 4 bits nas operações aritméticas da U.L.A..

F0 (PSW.5):

bit para uso livre do programador.

RS1 e RS0 (PSW.4 E PSW.3):

R0-R7 será acessado.

0

0

1

1

-

0

1

0

1

->

->

->

->

configura qual banco de registradores

primeiro banco

segundo banco

terceiro banco

quarto banco

Ex.: MOV PSW,#00001000B ;RS0=1 E RS1=1 -> SEGUNDO BANCO

OV (PSW.2): indica presença de bit CARRY (bit 8 ativado) nas

operações de multiplicação da U.L.A. Auxilia também as operações de

subtração.

P (PSW.0): indica paridade do acumulador. Se setado, indica

número par de '1' no acumulador. Caso contrário indica número ímpar.

- Contador de Programa (PC): registrador de 16 bits que guarda o

endereço da próxima instrução. Quando o 8051 é resetado, este

registrador é zerado, fazendo o 8051 buscar a primeira instrução da

memória.

- Apontador de Pilha (SP): registrador de 8 bits indicador do

endereço inicial da pilha do 8051. A pilha necessariamente tem que estar

localizada entre os endereços 30H e 7FH da área RAM interna do

microcontrolador. O tamanho da pilha deve ser suficiente para permitir

os diversos acessos de subrotinas do programa (considerando os

armazenamento dos endereços do PC e dos parâmetros da instrução PUSH).

- Ponteiro de Memória Externo (DPTR): registrador de 16 bits

utilizado para armazenar endereços de memória externa.

- Registrador B: registrador auxiliar nas operações de

multiplicação e divisão.

- Decodificador e Registrador de Instruções / Controle e

Temporização: sistema responsável pelo armazenamento, decodificação e

execução dos códigos de operação (bytes) das 256 instruções do 8051.

Controla os sinais externos de controle (reset, ALE, configuração da

memória interna de programa e sinal de leitura da memória externa).

- Timers: o 8051 possui 2 sistemas de temporização de 16 bits.

Maiores detalhes serão fornecidos nos capítulos subsequentes.

33

Apostila de Microprocessadores

Ivair Reis N. Abreu

- Unidade Serial: sistema para comunicação serial assíncrona fullduplex. Maiores detalhes serão fornecidos nos capítulos seguintes.

- Memória de Dados (SFR) e de Programa: o 8051 possui um estrutura

de acesso ao sistema de memória conhecida como HARVARD, onde o acesso a

memória de programa é diferenciado do acesso a memória de dados (através

de sinais de leitura distintos). Desta forma, o microcontrolador não

permite que um determinado programa fique localizado na área de dados ou

vice-versa. A grande vantagem deste sistema é a otimizacão do sistema no

acesso as instruções do programa e aos dados. O programa dos sistemas

com microcontroladores normalmente são dedicados (FIRMWARE). Observe que

este modo de acesso a memória é diferente dos microcomputadores padrão

IBM-PC, onde normalmente os programas localizam-se na área de dados (daí

o fato de cada vez mais ser importante uma grande área de memória RAM

dentro dos computadores).

- Memória de Dados (SRF): o 8051 possuir 256 bytes de memória de

dados interna e permite o acesso de mais 64 Kbytes de memória de dados

externa (unicamente através das instruções MOVX). Na maioria das vezes a

memória interna de dados é suficiente, pois as aplicações de controle

normalmente não exigem muita quantidade de memória volátil (já que os

programas não são armazenados na área de RAM).

A memória RAM interna é divida em 4 áreas:

- Área de Registradores R0-R7 (00-1FH): o 8051 possui 4 bancos de

registradores selecionados através dos bits RS1 e RS0 do registrador PSW.

Normalmente estes registradores armazenam endereços da área de rascunho

(modo de endereçamento indireto).

- Área Booleana (binária) (20H-2FH): 16 bytes endereçados bit a

bit (totalizando 128 bits). Pode-se acessar cada bit individualmente

indicando uma determinada condição binária (por exemplo: a tecla A de um

teclado foi acionada). Estes bits são acessados pelas instruções

booleanas do 8051.

- Área de Rascunho (30H-7FH):

localiza a pilha do sistema.

memória de uso geral onde se

- Área de Registradores Especiais (SFR) (80H-FFH): área onde se

localiza todos os registradores com função especial. O número destes

registradores varia de acordo com as funções disponíveis dentro do

processador. Os registradores especiais mais comuns são:

34

PO (80H): port P0.

P1 (90H).

P2 (A0H).

P3 (B0H).

ACC (E0H): acumulador.

B (F0H)

PSW (D0H): registrador de status

SP (81H): apontador de pilha

DPL (82H): byte menos significativo do registrador DPTR.

DPH (83H): byte mais significativo do registrador DPTR.

PCON (87H): registrador de controle de consumo do 8051.

Apostila de Microprocessadores

Ivair Reis N. Abreu

- IE (A8H): registrador de habilitação do sistema de

interrupções.

- IP (B8H): registrador indicador de prioridade do sistema

de interrupção.

- TMOD (89H): registrador de modo dos timers.

- TCON (88H): registrador de controle do timer 1

- T2CON (C8H): registrador de controle do timer 2.

- TL0 (8AH): byte inferior do timer 1.

- TH0 (8CH): byte superior do timer 1.

- TL1 (8DH): byte inferior do timer 2.

- TH1 (8BH): byte superior do timer 2.

Exercícios / Pesquisa Complementares

1) – Fazer um download de um arquivo .PDF com a arquitetura do 8051 (preferencialmente da Philips ou

Intel).

2) – Fazer um levantamento dos fabricantes que possuem microcontroladores com a arquitetura do 8051

(www.8052.com).

3) – Fazer um levantamento dos microcontroladores fabricados pela Philips e pela ATMEL.

4) – Obter um compilador para Assembler diferente do ASM51 utilizado no laboratório.

5) – Levantar o endereço de todos os registradores especiais do 8051.

35

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 9

2.4) - Sistema Mínimo com o 8051:

- 32 sinais de entrada/saída

FIGURA 17

- Interface serial (RxD e TxD), interrupções externas (INT0 e

INT1), "timer" duplo externo (T0 e T1).

FIGURA 18

2.5) - Sistema Mínimo com o 8031 (ROMLESS):

36

Apostila de Microprocessadores

Ivair Reis N. Abreu

- EPROM 4 kbytes (2732)

Exemplo:

1) – Sistema com o 8031 com as seguintes características:

37

Apostila de Microprocessadores

Ivair Reis N. Abreu

- Eprom Externa 27128.

- RAM 6264 (end. 0 – 1fffh).

- Clock de 11.059Mhz

- Reset automático e manual

- Alarme com uma chave liga/desliga, 4 sensores ultrasônicos, 1

lâmpada e 1 buzina.

- Comunicação serial.

2) – Sistema com o 8051 com as seguintes características:

-

Clock de 12 Mhz

Reset automático e manual.

Controle de 12 motores .

12 entradas de chaves.

Exercícios / Pesquisa Complementares

1) – Obter na internet um projeto com o 8051.

2) – Projetar um coletor de dados com o 8031 com as seguintes

características:

-

38

Eprom Externa 27128.

RAM 62512

Clock de 11.059Mhz

Reset automático e manual

8 ports para um teclado.

Comunicacao serial

Previsão de utilizar 2 ports para controle de um display.

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 10

3) - Linguagem Assembler

3.1) - Introdução:

A linguagem Assembler é uma linguagem de nível intermediária,

composta basicamente de mnemônicos (palavra representando o código de

operação da instrução), diretivas (pseudo-instruções), labels e

comentários. Pelo fato de estar bem próxima a linguagem de

microprocessador (linguagem de máquina composta de bits compreensível

pelo processador), exige um compilador (programa que converte o programa

fonte em linguagem de máquina) bastante simples e portanto rápido. É

ideal para utilização na área de projeto e testes de microprocessadores,

pois exige conhecimento da estrutura do microprocessador utilizado (ao

contrário das linguagens superiores transparentes a estrutura do

processador). Tem a desvantagem de não possuir a estrutura de linguagens

como PASCAL e C.

HARDWARE<-L.MÁQUINA<-L.ASSEMBLER<-L.SUPERIOR<-APLICATIVO

^

|

BITS

^

|

|

^

|

ESTRUTURAS

|

MENMEUMÔNICOS

PSEUDO-INSTRUÇÕES

LABELS

^

|

|

|

INTERATIVA

AO USUÁRIO

A medida que a linguagem fica mais interativa ao programador, o

compilador necessita de ser mais complexo e portanto mais lento.

- Instrução: código binário composto de 1 ou mais bytes com a função de

orientar o processador a realizar uma tarefa específica. Estes códigos

serão lidos seqüencialmente da memória e, através da via de dados,

entrarão no decodificador de instruções do microprocessador, gerando uma

série de sinais internos e externos de controle.

- Tamanho das instruções no 8085:

memória.

podem ocupar 1, 2 ou 3 bytes de

- 1 byte: o código de operação já especifica completamente a

função da instrução, não necessitando de complemento algum.

D7 D6 D5 D4 D3 D2 D1 D0 -> código de operação

Ex: MOV B,A (desloca o dado do acumulador para o registrador B) ->

não necessita de complemento

Código de operação -> 01000111 - 47H

- 2 bytes:

necessita de 1 byte de complemento

D7 D6 D5 D4 D3 D2 D1 D0 -> código de operação

39

Apostila de Microprocessadores

Ivair Reis N. Abreu

D7 D6 D5 D4 D3 D2 D1 D0 -> segundo byte

de compl.

Ex: MVI A,07 (carrega o acumulador com o dado 07)

Primeiro Byte (cód. operação) -> 00111110 - 3EH

Segundo Byte (complemento)

- 3 bytes:

-> 00000111 - 07H

necessita de 2 bytes de complemento

D7 D6 D5 D4 D3 D2 D1 D0 -> código de operação

D7 D6 D5 D4 D3 D2 D1 D0 -> primeiro complemento

D7 D6 D5 D4 D3 D2 D1 D0 -> segundo complemento

Ex: LXI H,2000H (carrega H com 20H e L com 00H)

Primeiro Byte (cód. operação) -> 00100001 - 21H

Segundo Byte (primeiro compl.)-> 00000000 - 00H

Terceiro Byte (segundo compl.)-> 00000010 - 20H

- Modos de endereçamento do 8051:

- Direto:

transferência do dado.

o dado do operando indica o endereço de

Ex:

MOV

A,50H ; o dado do endereço 50H da RAM interna do

8051 é transferido para o acumulador

- Registrador: o dado do operando Rn é transferido para o

destino.

Ex:

MOV

A,R6

transferido para o acumulador

- Imediato (#dado):

; o dado do registrador R6 é

o dado seguido de # é transferido para o

destino

Ex.: MOV

R1,#70H

- Indireto (@Rn): o dado armazenado no endereço da memória

com endereço guardado no registrado Rn é transferido para o destino

Ex.: MOV

MOV

R0,#50H

; o dado 50H é carregado em R0

A,@R0 ; o dado do endereço 50H é carregado no

acumulador.

3.2) - Estrutura e diretivas da Linguagem Assembler:

40

Apostila de Microprocessadores

Ivair Reis N. Abreu

Um programa em assembler é composto basicamente de comentários,

códigos de operação, operandos, pseudo-instruções (diretivas) e labels.

Os comentários são sempre precedidos de ponto e vírgula e tem a

função de documentar o programa, esclarecendo funções e procedimentos.

O "label" (rótulo) pode ser de 2 tipos: quando seguido de ':',

determinada com um nome um determinado endereço. Quando seguido da

expressão EQUATE (EQU), associa um nome a uma constante.

Uma linha em Assembler completa costuma ter a seguinte estrutura:

LABEL:

CÓDIGO DE OPERAÇÃO

Ex:

INICIO:

MOV

-------label cód.oper.

OPERANDO

;COMENTÁRIO

SP,70H

;CARREGA SP COM END. DA PILHA

---------------------------------operando

comentário

As pseudo-instruções (diretivas) são instruções especiais, não

codificáveis (para linguagem de máquina), com o objetivo de melhorar a

estrutura do programa e facilitar o processo de programação. As

diretivas mais utilizadas såo:

- ORG (origem): indica endereço inicial da memória onde devem ser

armazenadas as instruções posteriores. Um programa pode possuir mais de

uma diretiva ORG.

- EQU (equate): define equivalência entre nomes (labels) de dados

ou endereços que serão substituidos no processso de compilação para se

obter os códigos executáveis finais. Tem a função de otimizar possíveis

alterações nos dados e endereços nomeados pelo EQU.

- DB (define byte):

define valor a ser colocado na memória

- DS (define espaço): define número de espaços reservados na

memória para posterior utilização.

- END:

finaliza a edição do programa.

3.3) - Códigos de operação do microcontrolador 8051:

Com o objetivo de introduzir as instruções do 8051 da forma mais

didática possível, dividiremos os 256 mnemônicos em 5 grupos: instruções

de transferência de informação, aritméticas, lógicas, transferência de

controle e booleana.

3.3.1) - Instruções de transferência de informação:

Conjunto de instruções com o objetivo de transferir ou carregar

dados da área de memória/registradores. Normalmente são instruções

voltadas para a área de RAM interna, havendo apenas 4 instruções que

envolvem acesso a RAM externa.

41

Apostila de Microprocessadores

Ivair Reis N. Abreu

Utilizaremos a seguinte notação:

- Rn: registradores R0-R7 (banco selecionado em PSW)

- Ri: registradores R0-R1 utilizados para endereço indireto

- Direto: endereço direto da área de memória interna

- MOV destino,fonte

o destino

Ex.: MOV

Acumulador

MOV

MOV

MOV

MOV

A,R7

;transfere (copiando) o dado da fonte para

A,Rn

A,direto

A,@Ri

A,#dado

; copia o dado contido no registrador R7 para o

MOV

A,40h ; copia o dado do endereço 40h da RAM interna

; para o acumulador

MOV

A,P1

; copia o dado do PORT 1 (registrador

;localizado na área SFR da RAM interna) para

;o acumulador

MOV

A,@R0 ; copia o dado contido na área de RAM cuja o

; endereço esta em R0 para o acumulador

MOV

A,#40h ; carrega o dado 40h no acumulador

- MOV Rn,A

- MOV Rn,direto

- MOV Rn,#dado

Ex.:

MOV

MOV

A,07

R5,A

;carrega o dado 07 no registrador R5

MOV

R2,30H

;carrega o dado do endereço 30H no reg.R2

MOV

R3,#00

;carrega o dado 00 em R3

3333

Ex.:

42

MOV

MOV

MOV

MOV

MOV

direto,A

direto,Rn

direto,direto

direto,@Ri

direto,#dado

MOV

P1,A

;carrega o port P1 (SFR) com dado de A

MOV

45h,R0

MOV

45h,40h

;copia dado do end. 40h para o end. 45h

MOV

MOV

MOV

40h,#05h

R0,40h

50h,@R0

;carrega end. 50h com dado 05

Apostila de Microprocessadores

Ivair Reis N. Abreu

- MOV @Ri,A

- MOV @Ri,direto

- MOV @Ri,#dado

Ex.:

MOV

MOV

MOV

A,#0FFh

R1,#50h

@R1,A ;carrega dado FFH no end. 50h

MOV

MOV

R1,#60h

@R1,#00h

;zera posição 60h da memória

- MOV DPTR,#dado (16);carrega DPTR com dado de

;16 bits (pois a memória

;externa tem capac. de

;64k)

- Instruções de leitura de tabela: tabela é um conjunto de

constantes colocadas na área de programa com a finalidade de relacionar

uma variável com uma dado de saída. Por exemplo: os valores de seno de

0 a 90 graus podem ser tabelados ao invés de executar-se cálculos através

de processos numéricos. A tabela sempre é composta de um endereço

inicial e de uma variável conhecida por offset. Retomando o exemplo do

seno, o endereço inicial seria da tabela de seno e a variável seria o

grau de seno que desejamos conhecer.

- MOVC

A,@A+DPTR

;leitura de tabela da ROM com

endereço armazenado em A (offeset) + DPTR (início da tabela)

- MOVC

Ex.:

MOV

MOV

MOVC

ASCII:

MOV

.

.

.

DB

DB

DB

.

.

.

A,@A+PC

;idem com end. inicial em PC

DPTR,#ASCII ;carrega DPTR com inicio da

;tab.

A,#0

;indica 0 para conversão

A,@A+DPTR

;carrega A com valor de 0

;em ASCII

P1,a

30H

31H

32H

- Instruções de acesso a memória externa: a memória de dados

externa tem capacidade máxima de 16 bits com endereçamento através do

DPTR ou Ri (R0 ou R1).

- MOVX

A,@Ri ;le dado de mem. ext.

;endereçado por Ri

- MOVX

A,@DPTR

43

Apostila de Microprocessadores

Ivair Reis N. Abreu

- MOVX

@Ri,A

- MOVX

@DPTR,A

;escreve dado no acum. na

;memória ext.

- XCH A,Rn

;troca dados do acum. com reg.

- XCH A,direto

- XCH A,@Ri

- XCHD

Ex.:

A,@Ri ;troca apenas nibble inferior

MOV

MOV

XCH

A,#00H

30H,#5AH

A,30H

;ACUM=5AH e end. 30h=00H

MOV

MOV

MOV

XCHD

A,#0F5h

R0,#30h

@R0,#6Ah

A,@R0

;ACUM=FAH e end. 30H=65H

3.3.2) - Instruções Aritméticas:

A U.L.A. do 8051 tem condições de realizar as 4 operações

aritméticas básicas.

As operações normalmente envolvem o acumulador como um dos parâmetros e o

resultado normalmente são armazenados no acumulador. As operações

aritméticas normalmente afetam os bits do flag (PSW).

- Instruções de Soma:

-

ADD A,Rn

;Acum + Rn = Acum.

ADD A,direto

ADD A,@Ri

ADD A,#dado

ADDC

A,Rn

;Acum + Rn + Carry = Acum.

ADDC

A,direto

ADDC

A,@Ri

ADDC

A,#dado

ADDC

A,Rn

INC A

;Acum+1 = Acum

INC Rn

INC direto

INC @Ri

INC DPTR

- Instruções de Subtração:

- SUBB

- SUBB

- SUBB

44

A,Rn

A,direto

A,@Ri

;Acum - Rn = Acum.

Apostila de Microprocessadores

- SUBB

- DEC A

- DEC Rn

- DEC direto

- DEC @Ri

Ivair Reis N. Abreu

A,#dado

;Acum-1=Acum

- Multiplicação: o resultado de 16 bits é armazenado no Acumulador

(LSB) e no registrador B (MSB).

- MUL A,B

;multiplica dado de A por B

- Divisão: a parte inteira do resultado é armazenado no acumulador

e o resto no registrador B

- DIV A,B

;divide A por B

- Ajuste decimal: soma o número 6 ao nibble superior a 9.

Instrução para ajuste decimal.

- DA

A

3.3.3) - Instruções Lógicas:

A C.P.U. do 8051 realiza as seguintes operações lógicas: AND, OU,

OU EXCLUSIVO, COMPLEMENTAÇÃO, ROTAÇÃO (SHIFT REGISTER) PARA ESQUERDA E

ROTAÇÃO PARA DIREITA.

- Instruções AND:

-

ANL

ANL

ANL

ANL

A,Rn

A,direto

A,@Ri

A,#dado

;A ^ Rn = A

- Instruções OU:

-

ORL

ORL

ORL

ORL

A,Rn

A,direto

A,@Ri

A,#dado

;A OU Rn = A

- Instruções OU-EXCLUSIVO:

-

XRL

XRL

XRL

XRL

- Rotação:

A,Rn

A,direto

A,@Ri

A,#dado

;A OU-EXC Rn = A

divisão/multiplicação binária

- RR

A

;rotaciona todo os bits do

;acumulador 1 posição para a

;direita. O bit 1 é deslocado para

;o oitavo bit

45

Apostila de Microprocessadores

Ivair Reis N. Abreu

- RRC A

;o primeiro bit o acumulador é

;rotacionado para o carry e o bit

;deste para o oitavo bit do

;acumulador

- RL

- RLC A

A

;idem a RR mas invertendo a direção

;idem a RLC mas invertendo a dir.

- Complementação:

- CPL A

- CLR A

- SWAP

;complementa todos os bits do acum.

;zera acumulador

A

;troca os nibbles do acumulador

Exercícios / Pesquisa Complementares

1) – Obter um download do conjunto de instruções do 8051.

2) – Explicar a diferença entre as instruções abaixo:

mov

a,@r0

movx

a,@r0

3) – Fazer um programa para somar os dados da memória interna 30H com o

dado da memória externa 30h. Incrementar o resultado e fazer uma

operação OU exclusivo com o dado do registrador R3. Guardar o resultado

final no registrador R7.

46

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 11

3.3.4) - Instruções de Transferência de Controle:

Instruções que alteram o valor do PC (fluxo do programa) e utilizam

a pilha para salvamento de parâmetros. Podemos ter 2 tipos de salto no

programa: sem retorno (não há salvamento do PC na pilha) e com retorno

(tipo subrotina onde há o salvamento do PC na pilha).

- Instruções de Salto sem retorno: temos 3 tipos de instruções

"jump" que não salvam o conteúdo do PC. Normalmente pode-se apenas

utilizar a instrução JMP que o compilador transformará no tipo

conveniente (dependendo do tamanho do endereço):

- JZ

SJMP

end(8) ;carrega PC com endereço de 8 bits

AJMP

end(11);carrega PC com endereço de 11 bit

LJMP

end(16);carrega PC com endereço de 16 bit

JMP @A+DPTR ;carrega PC com endereço (A+DPTR)

JNZ end(8) ;se Z=0, salta para endereço

end(8) ;se Z=1, salta para endereço

- Instruções de chamada e retorno de subrotina: instruções que

carregam o PC com um determinado endereço mas salvam o endereço anterior

do PC na área de pilha (PCH -> (SP+1) e PCL -> (SP+2)). Por isso, podem

retornar através da instrução RET que resgatam o endereço do PC na pilha.

- ACALL

end(11) ;salta para a subrotina de endereço

PCH->(SP+1), PCL->(SP+2) e SP->SP+2

- LCALL

end(16)

;idem com end. de 16 bits

- RET

;resgata endereço da pilha, retornando ao

ponto da chamada de subrotina. SP->PCL,

SP-1->PCH e SP=SP-2

- RETI

;retorno de subrotinas de

interrupção.

- PUSH

direto

;salva na pilha (SP+1) dado direto

- POP direto

;resgata da pilha (SP-1) dado direto

indicado.

- Instruções de comparação: compara-se dois dados. Se diferentes,

saltam, caso contrário não. São instruções condicionais presentes nas

estruturas de decisão.

-

CJNE

CJNE

CJNE

CJNE

A,direto,end(8) ;se A

A,#dado,end(8) ;se A

Rn,#dado,end(8)

;se

@Ri,#dado,end(8) ;se

direto, saltam

#dado, saltam

Rn #dado, saltam

(Ri)#dado, saltam

- Instruções para "loop" de contagem: instruções que permitem o

retorno a um determinado endereço se um determinado contador não chegar a

zero. Ao retornar, o conteúdo do contador é decrementado.

- DJNZ Rn,end(8)

- DJNZ

;decrementa Rn. Se Rn0,

;retorna ao endereço

direto,end(8) ;idem utilizando dado

;direto como contador.

47

Apostila de Microprocessadores

Ivair Reis N. Abreu

3.3.5) - Instruções Booleanas:

Instruções que envolvem processamento binário. Muito comuns em

operações de controle onde ligamos/desligamos equipamentos (motores,

solenóides, lâmpadas, leds, etc) ou lemos entradas (chaves, sensores,

etc) que estão ligados/desligados. Os bits do sistema se localizam em

duas áreas: área boolena da RAM interna (20H-2Fh, ou bits 0 a 127) e

bits dos registradores especiais (SFR). Os bits da área boolena podem

ser designados de 2 formas:

- 20.0 ou 0-> primeiro bit do primeiro byte da área boolena

- 2F.7 ou 7F-> último bit do último byte da área boolena

Os bits dos registradores especiais (SFR) podem ser designados

pelos nomes do registrador endereçado pela posiçao no bit ou pelo próprio

nome do bit:

- PSW.7 ou Cy-> bit carry do flag

O bit Cy (ou simplesmente C) é bastante utilizado nas instruções

boolenas.

-

CLR C

;zera bit Cy

CLR bit

;zera bit especificado

SETB

C

;seta bit Cy

SETB

bit

;seta bit especificado

CPL C

;complementa Cy

CPL bit

;complementa bit

ANL C,bit ;operação "and" entre o Cy e o bit

ANL C,/bit;operação "and" entre o Cy e o inverso

;do bit especificado

- ORL C,bit ;operação "OU" entre o Cy e o bit

- ORL C,/bit;operação "OU" entre o Cy e o inverso

;do bit especificado

- MOV C,bit ;copia bit especificado para o Cy

- MOV bit,C ;copia Cy para o bit

- JNC end(8);salta para o endereço especificado se

;Cy é zero

- JC

end(8);salta para o endereço especificado se

;Cy é um

- JB

bit,end(8) ;salta para o endereço espec.

;se bit=1

- JNB bit,end(8) ;salta para o endereço espec.

;se bit=0

- JBC bit,end(8) ;salta e zera o bit se o mesmo

;estiver setado

48

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 12

3.4) - Exercícios de Linguagem Assembler do 8051:

1) - Carregar o dado do PORT P1 nos registradores internos R0-R7 do

terceiro banco.

2) - Somar o dado do endereço 30H da memória interna com o dado 30H da

memória externa. Complementar o resultado e fazer uma operação AND com o

dado do PORT P1. Guardar o resultado no endereço 50H da memória interna.

3) - Carregar a memória RAM interna do 8051 com o dado AAH.

4) - Idem para uma área de memória RAM externa entre 8000H e FFFFH.

5) - Fazer uma rotina de 0,5 segundos, utilizando um 8051 com cristal de

12 Mhz. Piscar um led localizada em P1.0 com freqüência de 2 Hz.

6) - Fazer uma rotina de tempo genérica, utilizando um 8051 com cristal

de 12 Mhz. Esta rotina receberá pelo par de registradores R6 e R7 o

periodo de tempo em mseg.

7) - Zerar todos os bits dos ports P1 e P3 se o bit P0.0 estiver em nível

alto.

8) - Ler o bit P1.0 com uma rotina de "debouced" de 10 mseg. Se este bit

estiver em nível alto, acender de forma consecutiva 7 lâmpadas

controladas pelos outros bits do port P1 com intervalo de 1 segundo.

49

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 13

3.5) - Projetos com o 8051:

1) – Projetar um sistema mínimo com o 8051 para um sensor fotoelétrico

ligar 15 lâmpadas 1 minuto apos o sensor indicar condição de escuro e

desligar 1 minuto após o sensor indicar claridade.

2) – Projetar um sistema com o 8031 com as seguintes características:

- Alarme com 1 chave liga/desliga, 1 sensor ultra-sônico e 1 buzina

- Cristal de 12 Mhz

- Reset automático e manual

- Memória externa de programa 2764

- Fazer um programa para ativar o alarme se a chave liga/desliga

estiver ativa. Monitorar o sensor de tal forma que se o mesmo indicar

violação e 10 segundos depois de verificado a chave liga/desliga (no caso

de alarme ter sido desligado pelo dono), se o mesmo ainda estiver

ativado, disparar a buzina e desligá-la apenas se o alarme estiver

desativado.

3) – Idem para ligar a buzina por um período máximo de 5 minutos.

4) – Idem para 8 sensores.

50

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 14

3.5) - Projetos com o 8051:

3) - Projetar um forno de micro-ondas com o 8051 com as seguintes

caracteristicas:

- Cristal de 12 Mhz

- Reset automático

- Comunicação Serial

- Memória ROM de programa interna

- Entrada para chave da porta, 4 bits para o display de LCD

- Controle de teclado de 16 teclas através de 8 bits e de 1 chave

de início de operaçao.

- Controle de 1 motor para o prato, lâmpada de iluminação interna e

1 válvula de microondas.

- Firmware ativando o motor, a lâmpada e a válvula por 5 minutos se

forem acionada a tecla de início e se a porta estiver fechada.

4) - Fazer um projeto de uma máquina de lavar roupas utilizando o

microcontrolador 8031 com as seguintes características:

- 4 Kbytes de EPROM externa.

- Controle do relê de acionamento do motor principal, solenóide

para abrir a válvula de entrada de água fria e água quente, solenóide

para saída de água, solenóide para saída de detergente e amaciante, 4

leds para indicações gerais e 1 sonorizador.

- Entrada do sensor de nível máximo de água de 2 teclas de

programação para o usuário.

- Possibilidade de comunicação serial.

5) - Fazer um projeto de um FIRMWARE para o projeto acima com as

seguintes características:

- Inicializar o sistema desligando todas as saídas e acendendo o

primeiro led indicando espera de programação.

- Esperar a primeira tecla de programação estar ativada. Quando

estiver, ligar o solenóide para água fria ou quente, dependendo da

condição da segunda tecla de programação. Aguardar indicação do sensor

de nível máximo de água e desligar o solenóide em questão.

- Acionar solenóide para saída do detergente e amanciante por 1

minuto.

- Ligar o motor principal por 15 minutos.

- Abrir a válvula de saída de água por 5 minutos.

- Acionar led de fim de operação e acionar o sonorizador por 5

segundos.

51

Apostila de Microprocessadores

Ivair Reis N. Abreu

AULA 15

4) - Display LCD programável

4.1) - Introdução:

Atualmente estão disponíveis no mercado uma grande variedade de

displays de Cristal Líquido com circuitos de controle e processamento

interno que visam facilitar o projeto de hardware e a rotina de

programação destes tipos de dispositivos de saída.

A figura a seguir mostra os principais controles destes tipos de

displays:

Arquitetura básica dos displays L.C.D.

Descrição dos sinais:

- D0-D7: barramento de dados com dupla função: envio dos comandos

de programação do display (posicionamento do cursor, endereço do caracter

a ser utilizado, etc.) e dos dados a serem escritos no display.

_

- C/D: em nível baixo, indica que o barramento de dados D0-D7

carrega a informação de controle (configuração geral do display). Em

nível alto, informação de dados (informação a ser mostrado no display).

Sinal normalmente ligado ao endereço A0 (endereço ímpar -> dado; endereço

par -> controle)

- E: sinal que em nível alto habilita o display. Nos modelos com

4 linhas, utilizamos um sinal E1 para a habilitação das 2 primeiras

linhas e um sinal E2 para a habilitação das 2 últimas linhas.

_

- R/W: sinal de entrada indicando em nível baixo processo de

escrita (barramento de dados como entrada) e em nível alto processo de

leitura (barramento de dados como saída).

- Vo:

entrada de tensão para controle de luminosidade do display

- Vss/GND: entrada de alimentação única de +5 Vcc.

Comercialmente, citamos abaixo alguns dos modelos disponíveis:

- Display 8 caracteres x

5 pontos horizontais

- Display 16x1, caracter