Controlo

1.2.7 Sistemas de controlo

Os VRs de microprocessadores dos PCs inevitavelmente incorporaram uma série de programas

avançados de monitorização e controlo que são essenciais para cumprir as tarefas

problemáticas que maximizam o desempenho, evitando instabilidades e garantir o

funcionamento adequado, apesar de distúrbios, incertezas e tolerâncias de variação na fonte,

carga e componentes do circuito [178].

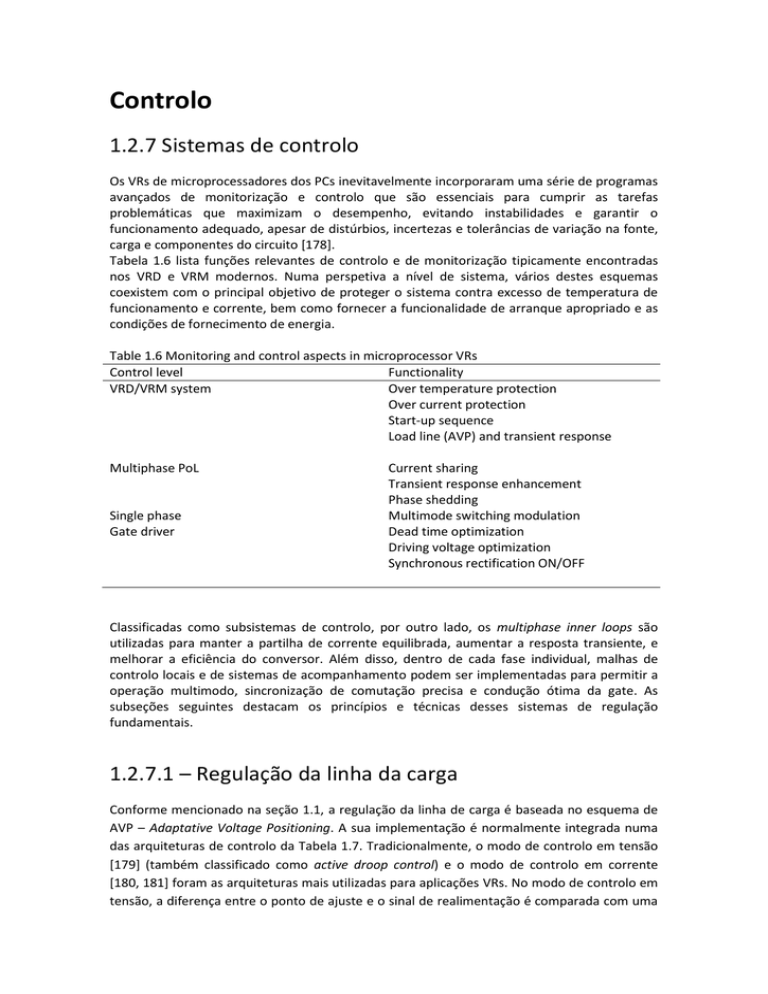

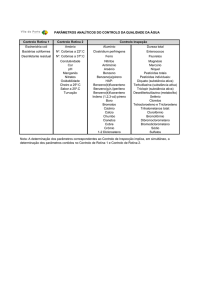

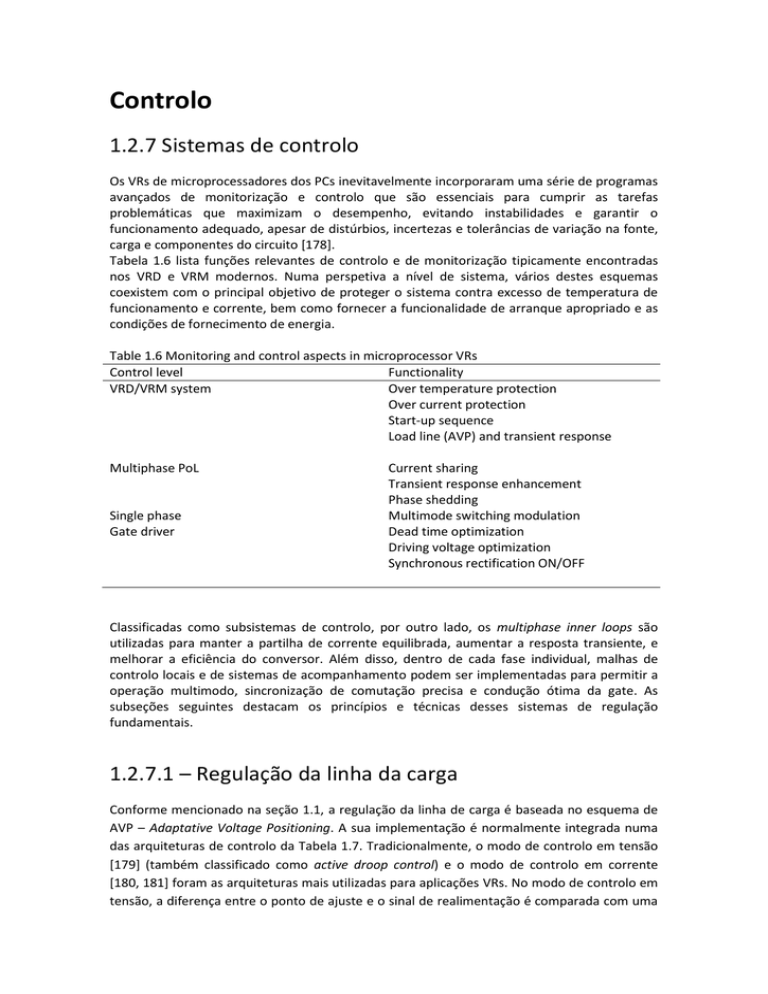

Tabela 1.6 lista funções relevantes de controlo e de monitorização tipicamente encontradas

nos VRD e VRM modernos. Numa perspetiva a nível de sistema, vários destes esquemas

coexistem com o principal objetivo de proteger o sistema contra excesso de temperatura de

funcionamento e corrente, bem como fornecer a funcionalidade de arranque apropriado e as

condições de fornecimento de energia.

Table 1.6 Monitoring and control aspects in microprocessor VRs

Control level

Functionality

VRD/VRM system

Over temperature protection

Over current protection

Start-up sequence

Load line (AVP) and transient response

Multiphase PoL

Single phase

Gate driver

Current sharing

Transient response enhancement

Phase shedding

Multimode switching modulation

Dead time optimization

Driving voltage optimization

Synchronous rectification ON/OFF

Classificadas como subsistemas de controlo, por outro lado, os multiphase inner loops são

utilizadas para manter a partilha de corrente equilibrada, aumentar a resposta transiente, e

melhorar a eficiência do conversor. Além disso, dentro de cada fase individual, malhas de

controlo locais e de sistemas de acompanhamento podem ser implementadas para permitir a

operação multimodo, sincronização de comutação precisa e condução ótima da gate. As

subseções seguintes destacam os princípios e técnicas desses sistemas de regulação

fundamentais.

1.2.7.1 – Regulação da linha da carga

Conforme mencionado na seção 1.1, a regulação da linha de carga é baseada no esquema de

AVP – Adaptative Voltage Positioning. A sua implementação é normalmente integrada numa

das arquiteturas de controlo da Tabela 1.7. Tradicionalmente, o modo de controlo em tensão

[179] (também classificado como active droop control) e o modo de controlo em corrente

[180, 181] foram as arquiteturas mais utilizadas para aplicações VRs. No modo de controlo em

tensão, a diferença entre o ponto de ajuste e o sinal de realimentação é comparada com uma

rampa de dente de serra artificialmente gerada para controlar o ciclo de trabalho. Numa

disposição possível, o ponto de ajuste é composto pela tensão de saída e uma tensão de

inclinação da linha de carga, que é emulada por um sinal de saída de corrente detetado e uma

resistência. A implementação AVP é conhecida como AVP- pois a tensão de inclinação (Droop

voltage) é alimentada para a entrada negativa do amplificador de erro. Alternativamente, a

tensão de inclinação pode ser combinado com um potencial de referência de modo a formar

uma corrente de sinal dependente do ponto de ajuste, o qual é então comparado no

amplificador de erro com a tensão de saída do conversor. Esta configuração é denominada

AVP+ porque a tensão de inclinação é alimentada à entrada positiva do amplificador de erro. O

modo de controlo em corrente é uma abordagem de multiloop em que a corrente na bobina é

a variável de controlo principal, em oposição ao ciclo de funcionamento no modo de controlo

em tensão. Assim, o ciclo de trabalho torna-se conceptualmente uma variável auxiliar. O modo

de controlo em corrente resulta num circuito interno que regula tanto o pico de corrente, o

“valley” atual, ou a média atual. Em ambos os casos, um circuito de controlo externo da tensão

de saída especifica um valor-alvo de controlo de corrente. Tal informação é combinada com a

queda de tensão e a entrada na “nested loop” para gerar o ponto de ajuste certo para a

corrente de carga.

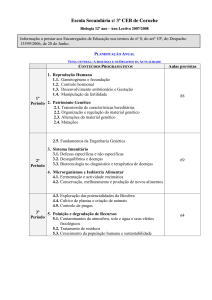

Table 1.7 Classification of relevant control architectures for the VR load line

Voltage mode (active droop control)

AVP+

AVPCurrent mode

Current peak

Current valley

Current average

Current mode with feedforward loop

Input current feedforward

Output current feedforward

V2 scheme

Hysteretic

Voltage mode

Current mode

O facto de que o modo de controlo em corrente de transforma aproximadamente a saída da

bobina para uma fonte de corrente proporciona vantagens significativas sobre o controlo de

modo em tensão, algumas das quais incluem a compensação fácil, a regulação correta na

partilha de corrente, a rejeição da linha, e o controlo ótimo em ambos CCM - Continuous

Conduction Mode e DCM - Discontinuous conduction mode. Pelo contrário, existem certas

desvantagens, tais como instabilidades sub-harmónicas e suscetibilidade áudio baixo que

tornam o modo de controlo em tensão a melhor escolha em alguns casos [182, 183].

Outros métodos mais avançados de controlo têm sido desenvolvidos com o objetivo de

proporcionar uma capacidade de resposta ao transitório mais rápida do que os controlos do

modo de tensão e corrente. Circuitos de controlo Feedforward oferecem vantagens dinâmicas

em virtude da medição das variações de carga de corrente e alimentá-los para o processo de

ações corretivas antes que perturbam os parâmetros de controlo. Controle antecipado é usado

em conjunto com o controlo de feedback para fornecer um controlo multiple-input-singleoutput.

Várias implementações combinando o método de controlo em corrente com feedforward de

corrente na carga têm sido analisadas em [184]. Somando o sinal de erro da tensão de saída de

controlo (loop externo) e o sinal de corrente da carga, e alimentando a soma para o

controlador de modo de corrente, a corrente da bobina pode automaticamente, e

praticamente sem nenhum atraso, seguir as variações de corrente na carga, mesmo sem

reação da malha de regulação de tensão. O conceito pode ser melhor explorado quando o

sinal de comando de corrente e a corrente na bobina estão intimamente relacionadas. O

controlo V2 surge como uma tentativa de conseguir isso em uma abordagem de

implementação simples e efetiva [185-189]. Na arquitetura V2, o sinal de feedforward

corresponde à tensão de saída do conversor, que inerentemente contém a informação da

corrente na bobina gerada pela ESR (Equivalent Series Resistance) dos condensadores de saída.

O sinal de feedforward é então usado como sinal de referência para o modulador em oposição

a um dente de serra gerados artificialmente como nos anteriores esquemas de controlo. Uma

alteração na corrente na carga terá um efeito sobre a tensão de saída, alterando assim o sinal

de rampa. Isso causa uma mudança rápida na saída do modulador para corrigir o ciclo de

trabalho (Duty Cycle) dos semicondutores, sem alterar o sinal de erro da malha de

realimentação. Assim a malha de frequência baixa fornece precisão DC e melhora a imunidade

a ruídos. A simplicidade e eficiência do controlo V2 tem sido implementada com sucesso por

vários fabricantes de semicondutores oferecendo para a indústria uma variedade de

controladores CI para aplicações de alto desempenho VR[190].

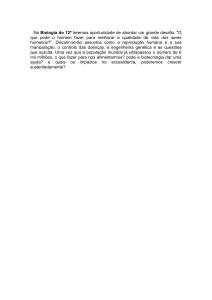

Fig. 1. 1 – Representação básica de um controlador de histerese num SRBC – Synchronous Buck Converter

Técnicas de controlo limite, com a superfície de comutação linear, como métodos de controlo

por histerese e modo de deslizamento surgem como alternativas aos controladores PWM. Um

controlo não-linear histerese é o mais popular em VRs para microprocessadores pela sua

simples implementação e rápida resposta transitória [191]. Como está mostrado na fig.1.1, um

controlador de histerese de base utiliza apenas um comparador e um Schmitt trigger para

modular o estado dos semicondutores como função da diferença entre a referência e os sinais

de realimentação. Assim, como no controlo de V2, gerar a referência de dente de serra ou

função de temporização não são fundamentalmente necessárias.

No modo de controlo em tensão, o sinal de realimentação corresponde à tensão de saída,

enquanto que no modo de controlo em corrente, é a corrente na bobina. Em ambos os casos,

a deteção precisa da componente do sinal AC é crucial para que o controlo por histerese

funcione corretamente. Com a deteção de sinais adequados, a não compensação de

realimentação é necessária para garantir a estabilidade. A ausência de um compensador de

baixa frequência banda faz com que o controlo por histerese seja uma das arquiteturas

existentes mais rápidas em malha fechada, com potencial para uma resposta quase

instantânea no que diz respeito a transitórios de carga. No entanto, o atraso de propagação

existe, o que afeta o ripple da tensão de saída e a de frequência de comutação. Além disso,

estes parâmetros estão inerentemente dependentes dos parasitas ESR e ESL do filtro de saída.

A frequência de comutação, apesar de ser muito previsível a partir de equações simples, pode

ainda variar substancialmente com as tensões de entrada e saída, condições de carga, e da

distribuição dos componentes. Isso pode levar a fenómenos indesejáveis de vibrações,

questões de EMI, e dificuldades na otimização dos semicondutores e componentes de filtro.

Estas desvantagens foram abordadas nos últimos anos, com várias abordagens tendo como

soluções, essencialmente, alcançar o modo de operação a frequência quase constante [192].

Entre as soluções propostas, as abordagens do comparador por histerese de largura variável

[193], constante no tempo ON ou tempo OFF [194] e adaptativa na modulação do tempo ON

[195] revelam-se métodos muito eficazes. Estas técnicas de modulação, resumidas na Tabela

1.8, correspondem a PFM (Pulse frequency modulation) e podem ser aplicadas a outras

estratégias de controlo, particularmente para a operação em DCM (Discontinuous conduction

mode), como será descrito na secção 1.2.7.3.

Table 1.8 Classification of relevant modulation techniques

Constant frequency

Pulse width modulation (PWM)

Variable frequency

Pulse frequency modulation (PFM)

Constant ON time

Constant OFF time

Adaptive constant ON time

Para a implementação AVP (Adaptive voltage positioning) tanto a corrente como a tensão

precisam de ser medidas simultaneamente. No modo de controlo em tensão por histerese, por

exemplo, a compensação da queda de tensão é feita pela subtração do sinal detetado de

corrente pelo sinal de referência na entrada do comparador [196].

1.2.7.2 Regulação multifásica / Controlo Multifásico

Um dos aspetos mais críticos das arquiteturas multifásicas é o mecanismo de controlo

pelo qual todas as fases individuais partilham igualmente a potência de saída. Uma distribuição

de carga estável melhora o desempenho e fiabilidade, sem a necessidade de

sobredimensionamento dos componentes devido à redução do pico do stress térmico.

Técnicas de partilha de corrente são criadas para atingir esse objetivo. A partilha de

informação sobre a carga é cada vez mais gerada e distribuída ao longo de uma única

interligação entre as células. Tipicamente, o circuito de interligação é concebido de modo a

que um sinal de erro de partilha de corrente seja produzido a partir da corrente de saída de

uma célula e da corrente média de todas as células. O sinal de erro é então utilizado para

reajustar localmente o sinal de compensação da realimentação da malha, como é mostrado na

fig. 1.21 [197].

Outras abordagens existem onde partilha de informação da corrente é comunicada

implicitamente através da saída do conversor, e não é são necessárias interconexões adicionais

entre as células [198].

A partilha de corrente em arquiteturas com controlo por histerese também pode ser

realizada com uma abordagem alternativa de seleção de fase. O algoritmo, através das quais

são dirigidas controla a entrega de energia da fase ativa, em qualquer dado momento que

corresponde ao carregamento com menor corrente instantânea [199].

Um meio para precisão na deteção/medição da corrente em fases individuais é

primordial na maioria dos métodos de partilha de correntes. Tabela 1.9 resume os métodos de

deteção atualmente mais usados. Por uma questão de maximizar a eficiência, as abordagens

sem perdas predominam, em que a maioria dessas aboradagens explora a RDSon dos

semicondutores de potência ou a ESR dos componentes de filtro passivos. Em qualquer caso, e

uma vez que a tensão através do ESR não pode ser medido diretamente, o uso de filtros de

compensação é necessário para subtrair a informação útil a partir das quantidades medidas.

Foram fornecidas funcionalidades adicionais de controlo para arquiteturas multifásicas

para a resposta “of conventional trailing and leading edge modulations”. Nestas topologias

básicas, as fases são sincronizadas com um relógio fixo e desfasamento de fase tal que o

sistema pode reagir a patamares de carga com um desfasamento de Ts / n, sendo n o número

de fases, e com uma ação corretiva apenas consistindo num reajuste do duty cycle.

Fig. 1. 2 – Modulação da tensão com função de equilíbrio de corrente.

Table 1.9 Current sensing approaches

External resistor

Output capacitor ESR

MOSFET RDSon

Output inductor ESR

With passive filter

With active filter

MOSFET RDSon & output inductor ESR

Sources: From [185, 198, 202, 203]

A proposta dual-edge PWM control [200] combina tanto o “leading and trailing edge

methods” sem um relógio fixo. Isto permite que o controlador reaja girando mais do que uma

fase de uma só vez, sempre que um patamar de carga ocorra. A resposta transitória é, assim,

melhorada em comparação com moduladores convencionais, porque a frequência da ativação

da fase a não é restrita a múltiplos de Fs. Além disso, caso em de um transitório step-up, em

paralelo com várias fases ativas permite a acumulação rápida de corrente no conversor.

A fim de maximizar a eficiência em toda a gama de valores para a carga, as arquiteturas

multifásicas podem incorporar “phase shedding control”. Com baixa carga, as perdas de

condução são baixas em comparação com as perdas de comutação. Assim, neste caso, as

perdas globais podem ser eficazmente reduzidas desativando fases. “Phase shedding” pode,

no entanto prejudicar os benefícios de entrelaçamento em relação ao tamanho do

condensador de saída, uma vez que a redução de fases pode provocar um aumento do ripple

da tensão de saída.

A selecção óptima do número de fases como uma função da corrente de carga tem

sido recentemente analisados em [201]. Os resultados sugerem que a gama de corrente entre

os limiares “phase shedding” podem ser de aproximadamente constante, o que simplifica a

implementação do controlo.

1.2.7.3 Modulação Multimode Switching

Modulação de comutação multimodo representa uma abordagem adicional ao “phase

shedding” para maximizar a eficiência sobre uma larga faixa de carga, em particular, em cargas

leves. O conceito surge com base no facto de que a técnica de modulação de comutação que

leva a perdas de energia mínimas depende da corrente de carga.

Técnicas de modulação de comutação foram classificadas anteriormente na Tabela 1.8

de frequência constante e variável. O PWM de frequência constante é eficaz em cargas

elevadas, onde o conversor funciona em CCM (Continous Conduction Mode). Em carga leve, o

PWM tem grandes perda de comutação. Assim, a PFM (Pulse frequency modulation) torna-se

mais eficaz uma vez que a frequência de comutação pode ser drasticamente reduzida sem

aumentar o ripple de saída, isto é, para correntes baixas dos condensadores de saída pode

manter a tensão mais tempo durante o ciclo desligado (OFF).

Modulação de comutação multimodo foi introduzido em produtos comerciais para

oferecer ganhos de eficiência significativos em cargas leves. Os controladores caraterizados

com a funcionalidade hyper light loadTM ou deep sleep são baseados neste conceito e podem

aumentar a eficiência do sistema em mais de 50% em correntes muito baixas [60]. Outras

soluções comerciais usam burst-mode control, que produz um trem de pulsos de frequência

fixa seguido por períodos OFF [204]. Numa carga menor o controlador pode atingir a

capacidade de duty cycle mínimo. O que acontece é que a energia a ser empurrada para

dentro do conversor está em excesso em relação à potência de saída. Portanto, o controlador

pode tipicamente responder tentando omitir ciclos. Este é vulgarmente conhecido como o

“variable frequency pulse skipping mode”, que está disponível em vários controladores

comerciaias - CIs [205]. Todas estas técnicas de controlo, podem ser aplicadas tanto em

circuitos analógicos e digitais [206, 207].

A capacidade de comutar entre os modos de modulação, como uma função da

corrente de carga comumente tem sido uma característica da VRs para dispositivos portáteis.

Para aplicações de elevada potência esta técnica é usada com menos frequência, mas está a

tornar-se cada vez mais relevante devido à importância que a eficiência de cargas leves estão a

adquirir.

1.2.7.4 Controlo de condução da Gate

Os controladores mais simples da gate de um SRBC Synchronous buck converter

fixaram tempos de atraso com duração suficiente para garantir que o estado ON dos

semicondutores não se sobrepõe sob quaisquer condições, evitando assim perdas relacionadas

com shoot-through (ou cross-conduction). Esses tempos mortos (dead times) devem ter em

conta a propagação dos componentes (components spreads), dependências de temperatura e

condições de operação, que normalmente resultam em tempos excessivos incorrendo na

condução do díodo de corpo do Sync-FET. A Condução do díodo corpo é indesejável pois

produz elevadas perdas de condução ON, bem como ruído adicional e perdas de comutação

associados ao inverter da “recuperação” (reverse recovery). Consequentemente, as técnicas de

controlo são necessárias para gerir o tempo de comutação com um atraso suficiente de modo

a evitar simultaneamente tanto o shoot-through como a condução do díodo corpo.

Uma técnica proposta é o controlo do tempo morto (dead time) adaptativo, o qual

permite reajustes de atraso “fly” por meio de monitorizar as tensões da gate [208].Quando a

tensão da gate do SyncFET passa a ser inferior a um certo limiar, presume-se que o dispositivo

é desligado e, assim, o CtrlFET pode ser ligado. Da mesma forma, o nó de comutação no falling

egde do tempo morto (the switched node falling edge dead time) sofre uma sequência de

eventos inversa. Além disso, o ligar do sync-FET pode também depender da tensão de nó de

comutação e de um detetor de cruzamento zero (zero crossing detector) para determinar a

condição de ativar/ligar o dispositivo. Embora esta estratégia de controlo possa reduzir

substancialmente o excesso de tempos mortos, condução do díodo corpo não pode ser

totalmente evitada devido aos atrasos de propagação dos controladores e dos drivers.

Várias soluções têm sido introduzidas para superar esses atrasos de propagação por

condução preditiva da gate. A técnica funciona na premissa de que o tempo de atraso

necessário para o ciclo de comutação seguinte pode ser ajustado automaticamente por ação

corretiva de tempos mortos escolhidos a partir de ciclos anteriores. O conceito usa um

controlo de realimentação que deteta de forma adaptativa e minimiza a condução do corpo de

díodo em cada ciclo. Independentemente dos atrasos de propagação inerentes, o controlo

consegue produzir os sinais de temporização precisos necessários para operar eficazmente

perto do limiar de condução cruzada (cross conduction), impedindo, assim, praticamente

condução corpo de díodo e perdas de recuperação reversa (reverse recovery). A condução

preditiva da gate foi inicialmente proposta e implementada pela Texas Instruments [210-212].

Uma abordagem alternativa para otimizar o tempo morto (dead time) é baseada na

ideia de minimizar algumas medidas de perda de energia. Uma série de trabalhos que estudam

este conceito têm sido apresentados. Em [213], os tempos mortos são intensificadas para

medir as alterações resultantes na corrente de entrada do conversor, que está relacionada

com a eficiência. O tempo morto é então ajustado com o objetivo de aumentar a eficiência.

Um método semelhante proposto em [214] ajusta os tempos mortos, para que o ciclo de

trabalho (duty cycle) seja minimizado, correspondendo a maximizar a eficiência.

Nas cargas “leves”, o SyncFET pode ter de ser desativado de modo a emular o

comportamento do díodo e permitir assim o DCM (Discontinuos Conduction Mode). Muitos

dos controladores dos ICs implementam esta função detetando uma corrente negativa na

bobina [215]. Outras soluções simplesmente desligam o SyncFET sempre que um comando de

carga “leve” é recebido pelo VR (Voltage Regulator) a partir do microprocessador principal

(host microprocessor) [216]. Para reduzir a necessidade de deteção de elevada largura de

banda devido a atrasos de propagação, técnicas adaptativas e preditivas (adaptive and

predictive tecnhiques) podem também ser adequadas para desligar o SyncFET nos tempos à

direita do cruzamento da corrente zero (at the right zero current crossing times)

A tensão de condução da gate dos semicondutores de potência são outras variáveis de

ajustamento, para além dos tempos mortos. Nomeadamente, as tensões ótimas das gates

dependem da corrente de carga. Para correntes elevadas, a tensão da gate poderá ter que ser

bastante elevada, de modo a minimizar a RDSon dos semicondutores. Ao contrário, tensões da

gate baixas para cargas “leves” podem ser mais benéficas, já que as perdas de carga da gate

dominam as perdas de condução. Por conseguinte, um ajuste adaptativo das tensões da gate

pode levar a melhorias em termos de eficiência em toda gama de carga.