FEI – NE 6710 – 2.a Prova de Sistemas Digitais I - 29/05/13 – Turma B – Tempo 80min Sem consulta Não é permitido o uso de calculadora – Interpretação faz parte da prova.

Nome ...................................................................................Nota ...............

N.o

N.o da Lista

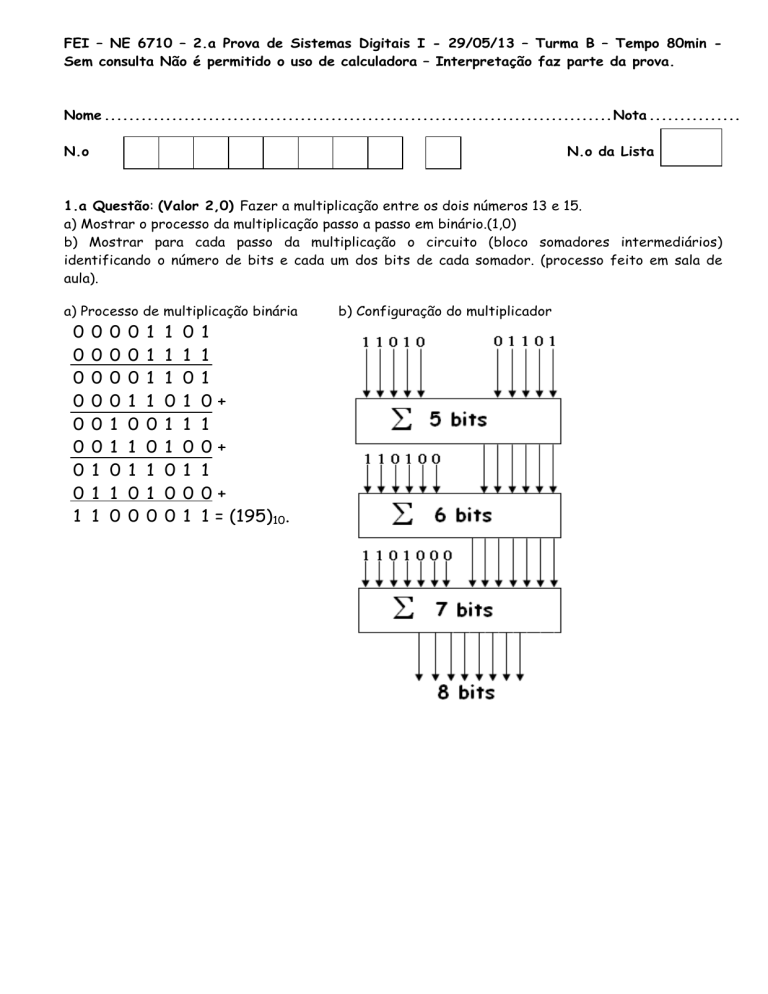

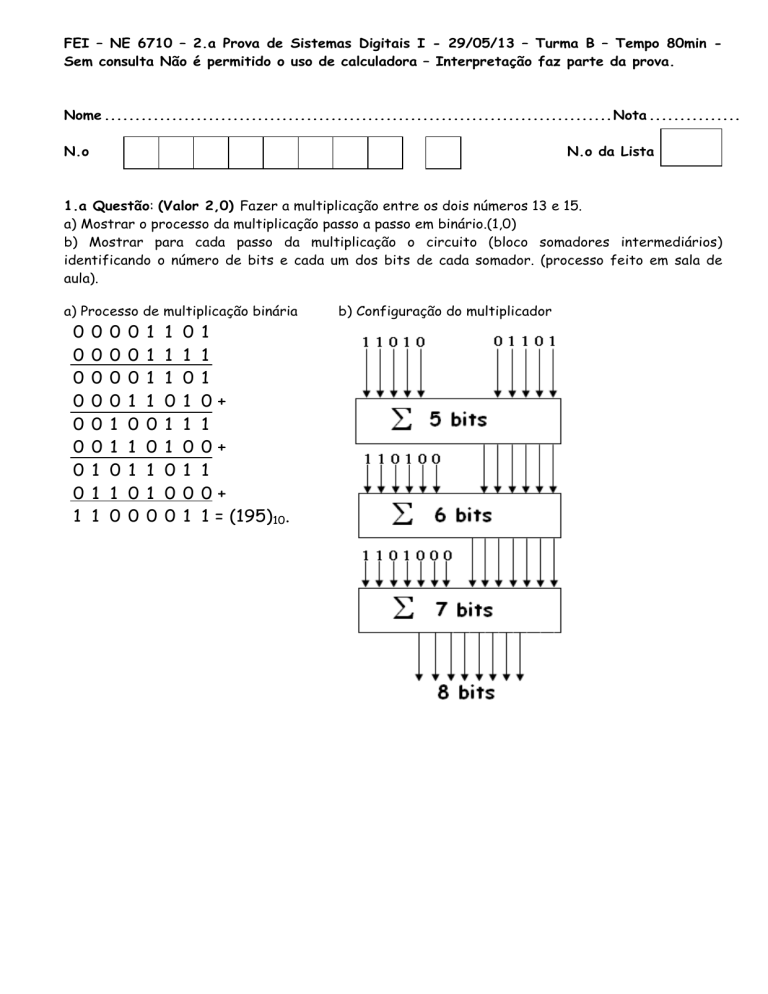

1.a Questão: (Valor 2,0) Fazer a multiplicação entre os dois números 13 e 15.

a) Mostrar o processo da multiplicação passo a passo em binário.(1,0)

b) Mostrar para cada passo da multiplicação o circuito (bloco somadores intermediários)

identificando o número de bits e cada um dos bits de cada somador. (processo feito em sala de

aula).

a) Processo de multiplicação binária

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

1

1

1

0

0

0

0

1

1

0

1

0

0

0

0

1

0

1

1

0

0

1

1

1

1

0

0

1

1

0

1

1

1

0

1

1

0

0

0

0

1

0

1

1

0

1

0

1

1

1

1

0+

1

0+

1

0+

1 = (195)10.

b) Configuração do multiplicador

2.a Questão: (Valor 3,0) Implementar um extensor para 1 bit capaz de operar com um meio

somador para a realização da comparação entre 2 número a e b de 1 bit. A resposta de a > b deve

ser apresentada no bit s de saída do somador e a resposta a = b deve ser apresentada no bit c0, bit

vai um do meio somador. Para a resposta de a < b deve ser feita externamente associando uma

lógica booleana. A tabela a seguir mostra a seleção das operações selecionadas maior, menor e igual.

Pede-se:

a) A tabela funcional mostrando os valores adotados pelos bits de saída do extensor para cada

operação selecionada.(1,0)

b) A expressão booleana de saída dos bits do extensor.(1,0)

c) A lógica associada às saídas s e c0 para a apresentação da resposta da operação a < b.(1,0)

a) Tabela funcional

S1

0

0

1

1

S0 Operação

0

a>b

1

a=b

a<b

1

-

S1

0

0

1

1

S0 Operação IA IB

0

a>b

1/0 0/1

1

a=b

1

1

a<b

0

0

1

-

a

S1

S0

b) A expressão booleana da saida do extensor

S 1S 0

00 01 11 10

a0b0 00 0

1 X 0

01 0

0 X 0

11 0

1 X 0

10 1/0 0 X 0

IA = S1’S0a0’b0’ + S1’S0a0b0 + S1’S0’a0b0’(caso 1)

S 1S 0

00 01 11 10

a0b0 00 0

1 X 0

01 0

0 X 0

11 0

1 X 0

10 0/1 0 X 0

IB = S1’S0a0’b0’ + S1’S0a0b0 + S1’S0’a0b0’(caso 1)

IB = S1’S0(a0 ⊕ b0)’ + S1’S0’a0b0’

c) A função booleana para a < b será: NOU de 2 entradas com s e c0.

b

Extensor

IA

IB

MEIO

SOMADOR

C0

S

a=b

a>b

3.a Questão: (Valor 2,0) Responda os itens a seguir

a) Escrever a expressão booleana de saída F, sabendo-se que os circuitos integrados são do

tipo coletor em aberto. (1,0)

R1

47kΩ

J1

Key = A

U3A

D1

74LS00N

1BH62

U3B

D2

74LS00N

1BH62

U3C

D3

74LS00N

1BH62

U3D

D4

74LS00N

1BH62

J2

F = A’B’C’D’

F

Key = B

J3

Key = C

J4

Key = D

V1

5V

b) Desenhar o circuito CMOS para a função F a seguir dada pela tabela da verdade. Fazer

uma solução otimizada com trade-off para o menor número de transistores. (1,0)

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

VDD

F

0

0

1

1

1

1

1

1

VDD

a) F = [A’B’]

‘

A'

A

B'

A'

Saída

VDD

B'

B

B'

A'

b) F = A + B

VDD

A

Solução b: Circuito que consome 6 transistores.

Total = 6 Transistores

B

A+B

B

A

4.a questão: (Valor 3,0) Pelos parâmetros fornecidos no circuito A,B e C, pede-se :

a) Quantas entradas do circuito B podem ser acionadas pelo circuito A ?(0,5)

b) Qual o maior ruído positivo que pode ser tolerado numa interface entre o circuito A como

saída e o circuito C como entrada ? (0,5)

c) Qual o maior ruído negativo que pode ser tolerado numa interface entre o circuito C como

saída e o circuito B como entrada ? (0,5)

d) Calcule a resistência máxima de entrada permitida colocar no circuito A. (0,5)

e) Responda e explique como ficam os transistores de saída Tottem-pole para realizar a

função “OU com fio” ( Wired-OR). (0,5).

f) Considerando-se os 3 circuitos A, B e C com 2 entradas para cada porta lógica NE.

Calcular a corrente total em nível lógico 1 e nível lógico 0 de entrada quando as 2 entradas de

cada um deles estão curto-circuitadas? (0,5) A, B TTL e C CMOS.

Parãmetros

Condições

VCC Fonte de Alimentação

VIH Tensão Entrada NL1

VIL Tensão Entrada NL0

VOH Tensão Saída NL1

VOL Tensão Saída NL0

IIH Corrente Entrada NL1

IIL Corrente Entrada NL0

IOH Corrente Saída NL1

IOL Corrente Saída NL0

IOS Corr. Curto-Circuito

ICCH Consumo em NL1

ICCL Consumo em NL0

tPH-L Tempo propagação

tPL-H Tempo propagação

Circ. A TTL

MIN

MAX

5,0

5,5

2,5

1,5

4,9

0,5

100,0

-1.000,0

-1.000

10

130

2

12

12

10

Circ B TTL

MIN

MAX

4,5

5,25

2,0

1,0

2,4

0,4

40,0

-2.000,0

-400

15

130

2

12

16

24

Circ C CMOS

MIN

MAX

6,0

7,5

3,5

2,0

7,4

1,0

1,0

1,0

100

0,4

130

1

9

10

10

Udd

V

V

V

V

V

µA

µA

µA

mA

mA

mA

mA

ns

ns

a) NL0 = 10mA/2mA = 5 e NL1 = 1mA/0,04mA = 25 => N = 5 entradas.

b) NL0 = 2,0 – 0,5 = 1,5V.

c) NL1 = 7,4 – 2,0 = 5,4V.

d) R ≤ 1,5V/1mA = 1,5kΩ.

e) Os transistores de saída estão cortados.

f) A, B e C respectivamente IILA = - 1mA, IILB = - 2mA, e IILC = 2µA e P/ NL1

IIHA = 200µA, IIHB = 80µA e IIHC = 2µA.