Capítulo 3:

ELE0317 − Eletrônica Digital II

3. MULTIVIBRADORES E PROJETOS DE TEMPORIZADORES

Intuitivamente, pode-se caracterizar os multivibradores como circuitos digitais

cuja saída se alterna entre dois estados lógicos: 1 (um) e 0 (zero) ou, verdadeiro e

falso ou ainda, ativado ("setado") e desativado ("resetado") . Uma mudança de

estado em um multivibrador pode ocorrer espontaneamente (caso o estado atual

seja considerado instável) ou forçado (caso o estado atual seja considerado

estável).

3.1. Os Multivibradores Monoestáveis, Astáveis e Biestáveis.

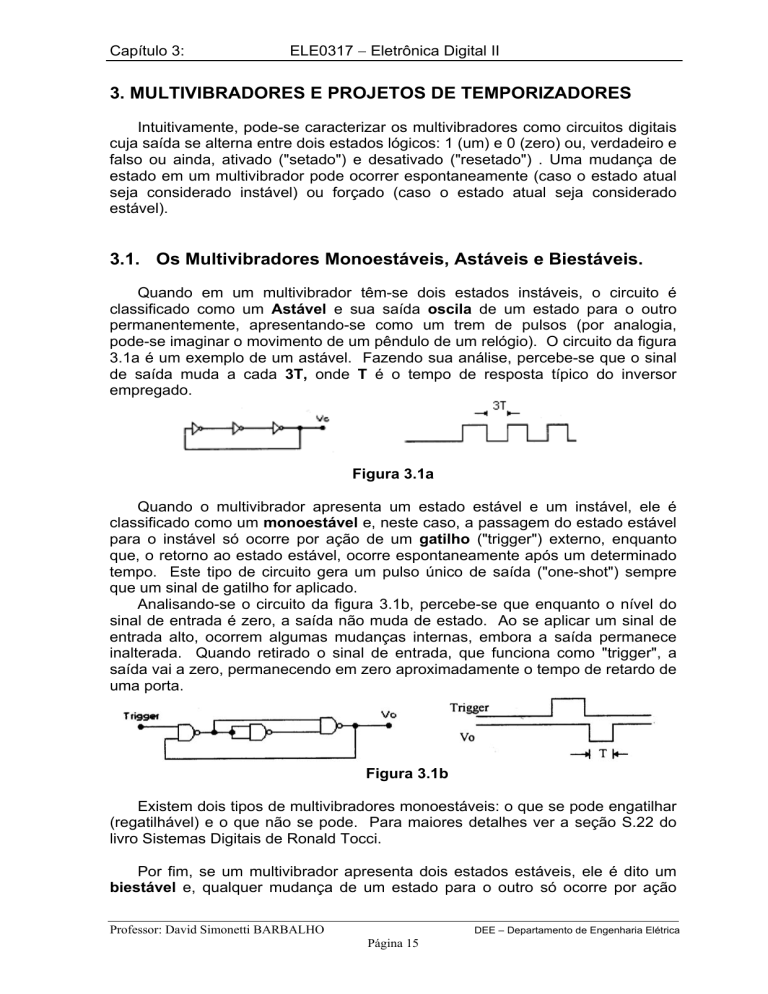

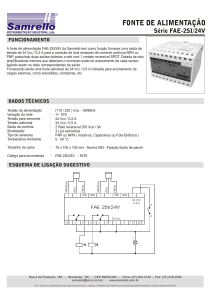

Quando em um multivibrador têm-se dois estados instáveis, o circuito é

classificado como um Astável e sua saída oscila de um estado para o outro

permanentemente, apresentando-se como um trem de pulsos (por analogia,

pode-se imaginar o movimento de um pêndulo de um relógio). O circuito da figura

3.1a é um exemplo de um astável. Fazendo sua análise, percebe-se que o sinal

de saída muda a cada 3T, onde T é o tempo de resposta típico do inversor

empregado.

Figura 3.1a

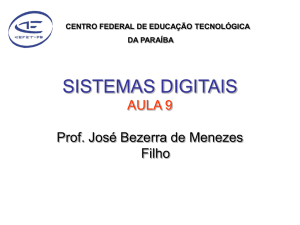

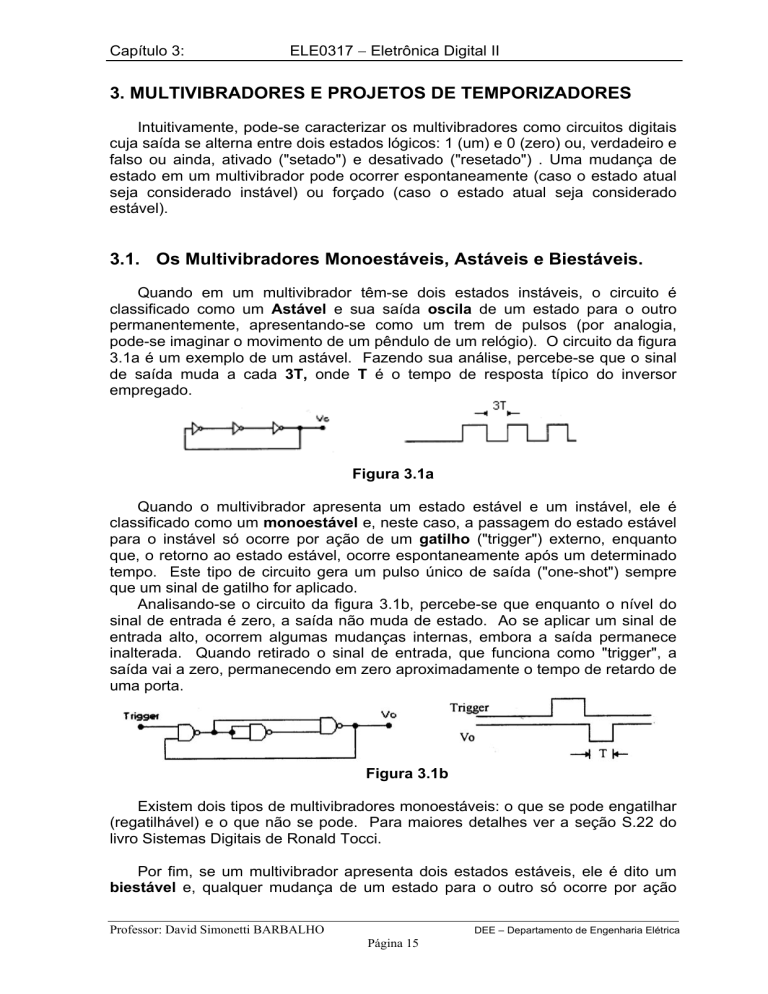

Quando o multivibrador apresenta um estado estável e um instável, ele é

classificado como um monoestável e, neste caso, a passagem do estado estável

para o instável só ocorre por ação de um gatilho ("trigger") externo, enquanto

que, o retorno ao estado estável, ocorre espontaneamente após um determinado

tempo. Este tipo de circuito gera um pulso único de saída ("one-shot") sempre

que um sinal de gatilho for aplicado.

Analisando-se o circuito da figura 3.1b, percebe-se que enquanto o nível do

sinal de entrada é zero, a saída não muda de estado. Ao se aplicar um sinal de

entrada alto, ocorrem algumas mudanças internas, embora a saída permanece

inalterada. Quando retirado o sinal de entrada, que funciona como "trigger", a

saída vai a zero, permanecendo em zero aproximadamente o tempo de retardo de

uma porta.

Figura 3.1b

Existem dois tipos de multivibradores monoestáveis: o que se pode engatilhar

(regatilhável) e o que não se pode. Para maiores detalhes ver a seção S.22 do

livro Sistemas Digitais de Ronald Tocci.

Por fim, se um multivibrador apresenta dois estados estáveis, ele é dito um

biestável e, qualquer mudança de um estado para o outro só ocorre por ação

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 15

Capítulo 3:

ELE0317 − Eletrônica Digital II

externa, podendo permanecer em qualquer dos dois estados indefinidamente,

caso não venha a ocorrer uma outra ação.

No circuito da figura 3.2a, percebe-se que as saídas apresentam estados

estáveis permanentes, já que não existe nenhum sinal externo capaz de alterar o

seu estado. O uso de duas portas NAND, em substituição aos inversores, permite

uma ação externa, como mostra o circuito da figura 3.2b.

Figura 3.2a

Figura 3.2b

O biestável, por sua característica de manter uma informação até que nova

situação de entrada seja aplicada, caracteriza-se como unidade básica de

memória semicondutora estática, o que é estudado com detalhes em outras

partes do curso.

3.2. Análise e Implementação de multivibradores com CMOS.

Embora tenham servido como exemplo na conceituação dos multivibradores

monoestáveis e astáveis, os circuitos apresentados nas figuras 3.1a e 3.1b não

são aplicáveis, já que não existe nenhum controle sobre o tempo de permanência

do circuito no estado dito instável. Uma maneira de solucionar este problema é

associar malhas RC ou um cristal ao circuito, de tal forma que este tempo possa

ser estabelecido.

Pelas características de alta impedância de entrada e de baixa impedância de

saída, bem como pela proteção a díodo na entrada, as portas CMOS são

extremamente adequadas ao projeto de circuitos astáveis e monoestáveis.

3.2.1. Monoestável

Na figura 3.3a é apresentado um circuito monoestável implementado com

portas NOR da família CMOS. O seu funcionamento pode ser acompanhado

através das formas de onda mostradas na figura 3.3b.

Figura 3.3a

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 16

Capítulo 3:

ELE0317 − Eletrônica Digital II

Pelas condições iniciais, capacitar descarregado, as tensões V1 e V2 são

iguais a Vss (nível lógico 1) e portanto Vo = 0.

Enquanto o sinal de gatilho se mantiver baixo (Trigger = 0) , esta condição é

estável e imutável.

Ao se aplicar um sinal de gatilho de largura st (maior que o tempo de resposta

das duas portas presentes no circuito e menor que o tempo T ou tw), resulta:

V1 = 0, V2 = 0 e Vo = 1.

Esta condição será mantida mesmo quando o pulso de gatilho for retirado.

Submetido a esta nova situação, o capacitar começa a se carregar com uma

constante de tempo t até que seja alcançada a tensão:

V1 = V2 = Vin (tensão de nível 1 para a segunda porta NOR)

Com estas tensões, Vo vai a zero, voltando portanto ao seu estado estável.

Pela análise da tensão de carga do capacitar (mostrada abaixo), pode-se definir o

tempo em que a saída se manteve em nível alto.

−t

Vss

Vss

v 2 ( t ) = v C ( t ) = Vss 1 − e RC ⇒ e t w RC =

t w = RCLn(

)

∴

Vss − Vih

Vss − Vih

Se for considerado Vih ≅ Vss/2 o tempo T (ou tw) será dado por:

tw ≅ RCLn(2) ou

tw ≅ 0,693RC.

Caso o valor da resistência de saída da primeira porta não seja desprezível

em relação ao valor da resistência usada na malha RC, deve-se adicionar seu

valor a R no cálculo de tw.

As figuras 4.a e 4.b mostram o circuito e as formas de onda geradas em um

outro modelo de monoestável, desta vez implementado a partir de portas, NAND.

A equação que define a temporização tw será dada por:

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 17

Capítulo 3:

ELE0317 − Eletrônica Digital II

Figura 4.a

Figura 4.b

Vss

,

Vc

calculada a partir da equação de descarga do capacitar dada por:

−t

Vc = Vss e RC .

t = RC ln

E, exatamente a mesma que foi definida para o circuito da figura 3.a se

for

considerado que

Vc = Vss 2 .

3.2.2. Astável

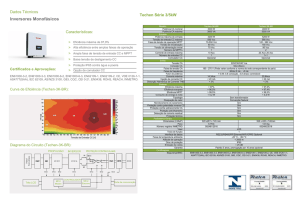

Para análise de um multivibrador astável implementado com portas CMOS,

será tomado como referência o circuito mostrado na figura 5.a. Novamente serão

consideradas as características ideais das portas CMOS. Pela figura 5.b pode-se

acompanhar o desenvolvimento relatado a seguir.

Figura 5.a

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 18

Capítulo 3:

ELE0317 − Eletrônica Digital II

Figura 5.b

Considera-se que, ao se ligar o circuito o capacitar está descarregado, logo

as tensões nos pontos Vo2 e Vi1 são nulas e a tensão em Vo1 é

aproximadamente igual a Vss (nível lógico 1). Nestas condições, o capacitar

tende a se carregar através de R pela diferença de tensão existente entre as

tensões de saída da porta 1 e da porta 2, com constante de tempo dada por RC.

Assim, nesta situação a tensão Vi1 tende a crescer. No momento em que a

tensão Vi1 (que é, nestas condições, a própria tensão no capacitor C) é

reconhecida como nível lógico 1 pela porta 1, a tensão Vo1 cai a 0 (zero), levando

automaticamente Vo2 a 1 (um, ou seja, Vo2≅Vss). Uma vez que a tensão no

capacitar não muda instantaneamente, verifica-se que neste momento a tensão

Vi1 ultrapassará a tensão de alimentação Vss! (Vi1≅Vss+Vc). Como a tensão

Vo1 é agora nula e o capacitar está carregado com uma tensão Vc (tensão limiar

de 1-lógico), sua tendência será de descarregar-se através de R pela diferença de

tensão existente neste instante entre as saídas da porta 2 (≅Vss) e da porta 1

(tensão nula). Durante este tempo, a tensão Vi1 tende a decrescer

assintoticamente para zero até ser reconhecida como de nível lógico 0 (Vi1≅Vd,

onde Vd é o valor da tensão que a porta 1 reconhece como nível lógico 0),

fazendo com que Vo1 retorne a 1 e que Vo2 retorne a 0. Neste instante preciso, o

capacitar está descarregado, mas agora com uma tensão negativa (−Vss+Vd),

logo Vi1 é também negativa e igual a −Vd. Esta é praticamente a situação original

a menos da tensão no capacitor C. Este ciclo irá se repetir indefinidamente e, se

forem consideradas as características idênticas das portas, tem-se um sinal de

"clock" com um período dado por:

2 * Vss − Vd Vss + Vc

T = Tc + Td = RC ln

+

,

Vd

Vss − Vc

onde Tc e Td são calculados a partir das equações de Vi1, levando em conta a

carga e descarga do capacitar dadas por:

vi1(t ) = Vss + (Vd − 2 ∗ Vss)e

−t

RC

−t

e

vi1(t ) = (Vc + Vss )e

e

Vss + vc

t d = RCLn

.

Vd

RC

,

onde:

2 ∗ Vss − Vd

t c = RCLn

Vss − Vc

Caso se considere as tensão Vc (limiar para o nível lógico 1) e Vd limiar para

o nível lógico 0) iguais a um certo valor Vt e, assumindo que para as portas

lógicas da família CMOS tem-se Vt=Vss/2, logo o sinal de "clock" possuirá um

período T com ciclo de trabalho (C.T.) de aproximadamente 50% dado por:

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 19

Capítulo 3:

ELE0317 − Eletrônica Digital II

2 ∗ Vss − Vt Vss + Vt

T = t c + t d = RCLn

+

= RCLn(3 + 3) ≅ 1,79 RC ,

Vt

Vss − Vt

t

com C.T . = c ≅ 0,5 ou C.T. de 50%.

T

A figura 5.c mostra como é possível um multivibrador astável gerar uma forma

de onda, onde se pode controlar o ciclo de trabalho sem alterar a freqüência,

através da inclusão de 2 díodos de sinal e de um potenciômetro na malha RC.

Figura 5.c

A figura 6 mostra outro modelo de astável, montado a partir de portas NOT

(implementadas com portas NANDs). Os cálculos dos tempos de carga e de

descarga, seguem semelhantes aos princípios da configuração mostrada na

figura 5.a.

Figura 6

3.3. Cuidados na Implementação com portas CMOS e/ou TTL.

Não existe uma regra para se definir que um dado circuito venha a funcionar

com portas da família CMOS ou com portas da família TTL. O que é realmente

necessário são os cuidados que se devem tomar com relação aos valores de

resistências e de capacitâncias envolvidos na definição dos tempos de

permanência em um dado estado instável do multivibrador. Por esta razão

colocaremos a seguir algumas restrições que devem ser obedecidas quando da

implementação dos circuitos mostradas nas figuras 4.a e 6.a quando forem

usadas portas da família TTL.

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 20

Capítulo 3:

ELE0317 − Eletrônica Digital II

·

No circuito da figura 4a, o valor ideal para R está compreendido entre

0,2Ω e

·

No circuito da figura 6a, o valor da freqüência do sinal de saída deve

estar compreendido entre lOOHz e lMHz.

*

Ainda no circuito da fig. 6a, para que a freqüência de oscilação seja

menos dependente da temperatura, a relação fo << I/2.tp.n deve ser

observada (tp representa o atraso por porta e n o número de portas).

Nas figuras 7a e 7b são fornecidos ábacos que podem ser utilizados na

implementação do astável da figura 6a usando-se portas da família TTL e CMOS

respectivamente. Os valores limites devem ser obedecidos principalmente para

implementações que envolvam portas TTL.

3.3.1. Monoestável

3.3.2. Astável

3.4. Projeto de Circuitos Monoestáveis e Astáveis com Circuitos

Temporizadores Integrados

Trata-se de um circuito integrado projetado para aplicações gerais de

temporização, atualmente já bastante consagrado, sendo muito estável e

confiável como circuito controlador, na produção de circuitos de atraso ou de

osciladores.

Foi introduzido no mercado pela Signetics embora, atualmente, a maioria dos

fabricantes o produzam. Pode ser utilizado em circuitos monoestáveis ou

astáveis, com períodos que variam entre microsegundos e horas.

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 21

Capítulo 3:

ELE0317 − Eletrônica Digital II

Sua tensão de alimentação situa-se entre 4,5V e 18V o que o torna

compatível com as lógicas CMOS e TTL, bem como, para aplicações em circuitos

alimentados por bateria.

A saída é capaz de fornecer correntes de até 200mA, permitindo o comando

de relés e outras cargas que necessitem de correntes relativamente grandes.

3.4.1. Multivibradores com o Temporizador 555

A figura 8 mostra a configuração interna e a pinagem do temporizador 555.

Verifica-se a presença de dois comparadores (compA e compB) associados a

uma malha resistiva interna, de um biestável com entrada independente de

"reset", de um inversor "buffer" de saída e de um transistor coletor aberto que

funciona como chave.

•

•

•

•

Figura 8

A função de cada um destes blocos é bastante simples:

a malha resistiva opera como um divisor de tensão, aplicando 2/3 de Vcc no

terminal - (menos) do comparador compA e um nível 1/3 de Vcc no terminal +

do comparador compB. É possível alterar estes valores através do pino 5

(controle de tensão);

comparador compA avalia os níveis de tensão dos terminais - (fornecido pela

malha resistiva) e + (nível "threshold" aplicado externamente através do pino

6) e gera uma saída nível l ou O caso o nível no terminal + seja maior ou

menor que o do terminal - respectivamente;

comparador compb avalia os níveis de tensão dos terminais + (fornecido pela

malha resistiva) e - (nível do sinal de "trigger" aplicado externamente através

do pino 2) e gera uma saída nível l ou O caso o nível no te @ nal + seja maior

ou menor que o do terminal respectivamente;

caso a entrada direta "resetll (pino 4) esteja em nível lógico I (desativada) , o

biestável reflete um estado "set" (saídas Ql=O e Q2=1) quando se aplica R=0

e S=1 ou um estado "reset" (saídas Ql=O e Q2=1) quando se aplica R=1 e

S=O. Caso seja aplicado um nível O (zero) na entrada direta de "reset", o

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 22

ELE0317 − Eletrônica Digital II

Capítulo 3:

•

•

biestável também assume o estado "reset". A condição R=0 e S=0 não altera

o seu estado atual e, a condição R=1 e S=1 não deve ocorrer;

inversor reflete o estado atual da saída Ql (complemento de Q2) através do

pino 3 e;

transistor satura ou corta dependendo do valor atual de Q2 e reflete esta

situação através do pino 7 (descarga).

3.4.2. Uso do Temporizador 555 como Monoestável

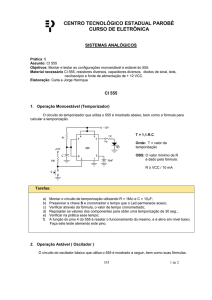

A configuração básica de um circuito monoestável implementado com o

"timer" 555 é mostrada na figura 9a. o pino 4 é desabilitado por uma ligação a

Vcc, o pino 5 é conduzido a terra por um capacitar de lOnF e serve de "bypass" a

ruídos de alta freqüência, o pino 2 é usado como entrada de gatilho e os pinos 6 e

7 são associados a uma malha RC externa-a qual, será responsável pela

definição da largura do pulso de saída.

V+

R

C

Saída

Disparo

Ct

Figura 9.a

No início da operação será admitido que o sinal de gatilho se apresenta em

nível alto (tensão superior a Vcc/3) e que o biestável está "resetado" (Q2=1 e

Ql=O). Nestas condições, observa-se que:

• saída é igual a zero;

• transistor está saturado (tensão no pino 6 aproximadamente igual zero);

• tensão sobre o capacitar é nula;

• a tensão no pino 6 é nula (inferior portanto a 2Vcc/3) e que;

• S=0 e R=0 o que não altera o estado do biestável.

Enquanto não houver um pulso de gatilho esta situação permanecerá

inalterada. Caso ocorra um pulso de gatilho (inferior a Vcc/3) o comparador

compa fornecerá S=I. Como R=O, o biestável será levado a condição "set" (Ql=l

e Q2=0). Nesta nova situação observa-se que:

• a saída é igual a l (um);

• o transistor é levado ao corte abrindo a conexão que mantinha o capacitar em

zero;

• o capacitor tende a se carregar através de R elevando a tensão de limiar

("threshold") do pino 6.

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 23

ELE0317 − Eletrônica Digital II

Capítulo 3:

Se o pulso negativo de gatilho for retirado antes que a tensão de limiar possa

atingir o limite de 2Vcc/3, tem-se S=0 e R=0 o que também não altera as

condições atuais de saída. A tensão no capacitor continua crescer.

Quando a tensão no capacitar ultrapassa 2Vcc/3, o compA fornece R=1 (temse ainda S=0) levando o biestável ao estado "reset" e aí tem-se novamente:

• saída nula;

• transistor saturado (o que força a descarga rápida do capacitar);

• capacitar descarregado.

A figura 9.b mostra o diagrama de tempo para o multivibrador monoestável

Básico, onde a largura do pulso de saída é dada por: T = 1,1 RC.

Figura 9.b

3.4.3. Uso do Temporizador 555 como Astável

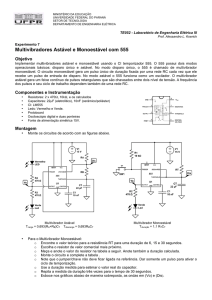

A configuração básica de um circuito astável implementado com o CI 555,

conhecido como "timer", é mostrada na figura 10.a. O pino 4 do CI é desabilitado

por uma ligação a Vcc. O pino 5 é conduzido a terra por um capacitar de

aproximadamente 10nF e serve de "bypass" a ruídos de alta freqüência

originários da fonte de alimentação DC. Uma malha externa com dois resistores

(R1 e R2) e um capacitar (C) é usada para, através dos pinos: 2 (trigger), 7 (tensão

de limiar) e 6 (descarga), estabelecer a freqüência do sinal de saída.

V+

R1

Saída

R2

C

Ct

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 24

Capítulo 3:

ELE0317 − Eletrônica Digital II

Figura 10.a

Ao ligar o circuito, o biestável ( ou "latch") estará no estado de "setado" (Q=1),

pois a tensão no capacitor C é nula e, por conseguinte, o compB está fazendo

S=1 e o compA fazendo R=0 nas entradas do "latch". Esta condição de "set" é

obtida pela primeira vez ao ligar o circuito.

•

•

•

•

•

•

•

•

•

•

•

•

Nesta condição, observa-se que:

a saída do monoestável é igual a 1 (um);

o transistor está na região de corte, abrindo o ponto de baixa impedância

localizado entre as duas resistências R1 e R2, através do pino 7 do CI 555;

a tensão inicial sobre o capacitor C, que é igual a zero e é a mesma tensão

dos pinos 2 e 6 do CI 555, tende a se carregar através de R1 e R2 em direção

a Vcc e, quando sua tensão atinge Vcc/3, o compB (faz S=0), retirando assim

o sinal de "set" do "latch";

quando pela primeira vez a tansão do capacitor atingir 2Vcc/3, o compA fará

R=1, logo o "latch" vai ao estado de "reset", pois já se tem S=0;

Na condição "reset" tem-se que:

a saída do monoestável é igual a 0 (zero);

o transistor está agora saturado, com tensão no pino 7 de aproximadamente

zero, aterrando o ponto central das duas resistências;

a tensão sobre o capacitor, vai decrescer em direção a zero a partir do valor

inicial de 2Vcc/3, logo que ela ficar menor que esta valor, o compA retira o

"reset" (R=0);

o capacitor C se descarrega através de R2, quando a tensão de C atingir o

valor de Vcc/3, o compB faz S=1, o "latch" vai ao estado "set", pois R=0.

Na condição "set" tem-se que:

a saída do monoestável é igual 1 (um);

o transistor está agora na região de corte, abrindo o ponto de baixa

impedância localizado entre as duas resistências R1 e R2;

o capacitar C, com tensão inicial igual a Vcc/3, tende a se carregar, através de

R1 e R2, em direção a Vcc, logo que a sua tensão ficar ligeiramente maior que

Vcc/3, o compB retira o "set" do "latch" (S=0);

quando a tensão de C atingir o valor de 2Vcc/3, o compA fará novamente R=1,

logo o "latch" vai ao estado de "reset", pois já se tem S=0;

O ciclo passa a se repetir continuamente como mosta a figura 10.b.

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 25

ELE0317 − Eletrônica Digital II

Capítulo 3:

Figura 10.b

Toda vez que a tensão sobre o capacitor for uma tensão entre os valores

Vcc/3 e 2Vcc/3, tem-se sempre S=0 e R=0. Esta a situação não altera o regime

de carga ou descarga do capacitor. Ele continua a se carregar caso a saída do

"latch" valha 1, ou a se descarregar caso a saída do "latch" valha 0.

Toda vez que a tensão sobre o capacitar ultrapassa 2Vcc/3 tem-se R=1 e

S=0, biestável será "resetado" o que leva a saída a zero (0).

Toda vez que a tensão sobre o capacitar é inferior a Vcc/3 tem-se R=0 e S=1,

biestável será "setado" o que leva a saída a um (1).

A figura 10.b mostra o diagrama de tempo para o multivibrador astável básico,

onde as larguras dos pulsos de saída são dadas por:

Vcc − Vd

Vc

T = Tc + Td = C (R1 + R2 )Ln

+ C (R2 )Ln ,

Vcc − Vc

Vd

onde Tc e Td são calculados a partir das equações de carga e descarga do

capacitar dadas por:

vc (t ) = Vcc − (Vcc − Vd )e

−t

C ( R1 + R2 )

e

v d (t ) = (Vc)e

−t

C ( R2 )

Substituindo as tensão de carga Vc=2Vcc/3 e de descarga Vd=Vcc/3, tem-se:

Vcc − Vcc / 3

2 ∗ Vcc / 3

T = Tc + Td = C (R1 + R2 )Ln

+ C (R2 )Ln

,

Vcc / 3

Vcc − 2 ∗ Vcc / 3

onde finalmente encontra-se:

T = Tc + Td = C (R1 + R2 )Ln(2) + C (R2 )Ln(2 ) = C ( R1 + 2 R2 ) Ln(2) ≅ 0,69( R1 + 2 R2 )C .

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 26

Capítulo 3:

ELE0317 − Eletrônica Digital II

3.5. O Multivibrador "SCHMITT TRIGGER"

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 27

Capítulo 3:

ELE0317 − Eletrônica Digital II

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 28

Capítulo 3:

ELE0317 − Eletrônica Digital II

3.6. Multividradores TTL e suas Aplicações

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 29

Capítulo 3:

ELE0317 − Eletrônica Digital II

Professor: David Simonetti BARBALHO

DEE – Departamento de Engenharia Elétrica

Página 30