TÉCNICA PARA O PROJETO DE UM AMPLIFICADOR OPERACIONAL

FOLDED CASCODE EM TECNOLOGIA CMOS.

Murillo Fraguas Franco Neto e João Navarro

Escola Politécnica da Universidade de São Paulo

[email protected], [email protected]

maior durante o projeto e, consequentemente, para um

tempo de projeto maior, o que acaba por elevar custos. Por

fim, para os projetistas de mixed-signal, somam-se às

dificuldades dos projetistas analógicos outras, tais como

problemas de ruído, de testabilidade, etc.

O objetivo deste trabalho é contribuir para a

simplificação de projetos de circuitos analógicos,

procurando disponibilizar programas que determinem as

dimensões de transistores de blocos analógicos. Essa idéia

tem como atrativo a redução dos erros de projeto, uma vez

que os programas utilizados já foram testados, além da

redução do tempo de projeto, pois parte das tarefas de

projeto será realizada pelo programa.

A proposta foi desenvolvida em um bloco construtivo

particular, um amplificador operacional do tipo folded

cascode [3]. Amplificadores operacionais são blocos

essenciais em muitos circuitos analógicos tais como

bandgaps, conversores AD/DA, etc. Além disso, ele é

considerado um bloco complexo para projeto, pois muitas

de suas características estão correlacionadas e, portanto, ao

se alterar uma dessas características, como por exemplo o

ganho, se degradam outras, como o consumo de potência.

Na literatura, essa dependência é conhecida como tradeoff. A facilidade de gerar amplificadores que atendam às

especificações de um projeto, facilita o seu

desenvolvimento e dá ao projetista maior tempo para

otimizações ou análises de eventuais alternativas.

As seções a seguir irão apresentar a descrição do bloco

amplificador operacional proposto e como foi realizado seu

projeto, e estão divididas da seguinte forma: a seção 2

apresentará a técnica de projeto a ser desenvolvida e sua

aplicação ao projeto de um amplificador simples; a seção 3

abordará o amplificador folded cascode, apresentando as

equações que rejem seu funcionamento e a sequência

utilizada para projeto; a seção 4 apresentará os resultados

de simulação e fará a comparação com os resultados do

amplificador projetado realizado na seção 3; a seção 5

apresentará os rumos que este trabalho pretende seguir, e a

seção 6 apresentará as conclusões. Nas próximas seções

será usada a seguinte notação: VGS é a tensão gate-source;

RESUMO

Este trabalho pretende contribuir para a simplificação do

projeto de circuitos integrados analógicos, apresentando

uma técnica para o projeto de um amplificador operacional

folded cascode em tecnologia CMOS. Esta técnica consiste

em, a partir de uma topologia pré determinada completa

(operacional e polarização), relacionar as dimensões dos

transistores através das expressões que rejem seu

funcionamento e implementar rotinas computacionais para

realização dos cálculos necessários para o projeto. Essas

rotinas devem receber, como parâmetros, um arquivo

contendo o modelo dos transistores e as especificações

desejadas e irão fornecer, como resultados, as dimensões

dos transistores e um arquivo para simulações.

1. INTRODUÇÃO

Atualmente o mundo dos projetistas de circuitos integrados

se divide em três porções: o digital, o analógico e o mixedsignal. Para os projetistas de circuitos digitais, existem

diversas ferramentas de auxílio ao projeto que são

poderosas e que facilitam em muito o desenvolvimento de

sistemas digitais, disponibilizando células semi-prontas,

como memórias, contadores, somadores, etc., para as quais

basta configurar e instanciar e teremos blocos prontos para

serem utilizados. Além disso, sistemas digitais podem ser

continuamente

testados

em

plataformas

de

desenvolvimento bastante completas, que disponibilizam

diversos módulos como interfaces de comunicação,

dispositivos de saída de vídeo, portas de entrada e saída de

dados, bancos de memória, botões, etc., tudo à um custo

relativamente baixo [9].

Já para o projetista analógico aparecem várias

dificuldades: custo elevado das ferramentas de projeto;

inexistência de plataformas de desenvolvimento onde se

possa realizar testes, em tempo real, e rapidamente corrigir

eventuais erros; menor número de blocos de propriedade

intelectual - IP Cores - disponíveis para serem prontamente

utilizados. Isto contribui para uma probabilidade de erros

1

VSB é a tensão source-bulk; gMi é a transcondutância

transistor Mi; gdsMi é a condutância dreno-source

transistor Mi; CgsMi é a capacitância gate-source

transistor Mi; CdbMi é a capacitância dreno-bulk

transistor Mi; VTH é a tensão de limiar do transistor.

Tabela 1: Especificações do amplificador simples.

do

do

do

do

2. TÉCNICA DE PROJETO

A técnica proposta consiste em definir uma sequência de

projeto para o amplificador operacional utilizando

fórmulas que relacionam as dimensões dos transistores,

além de automatizar esse seqüência através de rotinas

computacionais que recebem especificações iniciais como

parâmetros e retornam as dimensões dos transistores.

Obviamente a topologia do amplificador deve ser

previamente definida, e o software de auxílio ao projeto

será capaz de trabalhar apenas para essa topologia de

amplificador. Os resultados obtidos através do projeto com

o software devem ser verificados através de algum

simulador de circuitos, por exemplo o simulador Eldo da

Mentor Graphics utilizado neste trabalho.

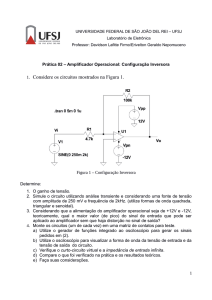

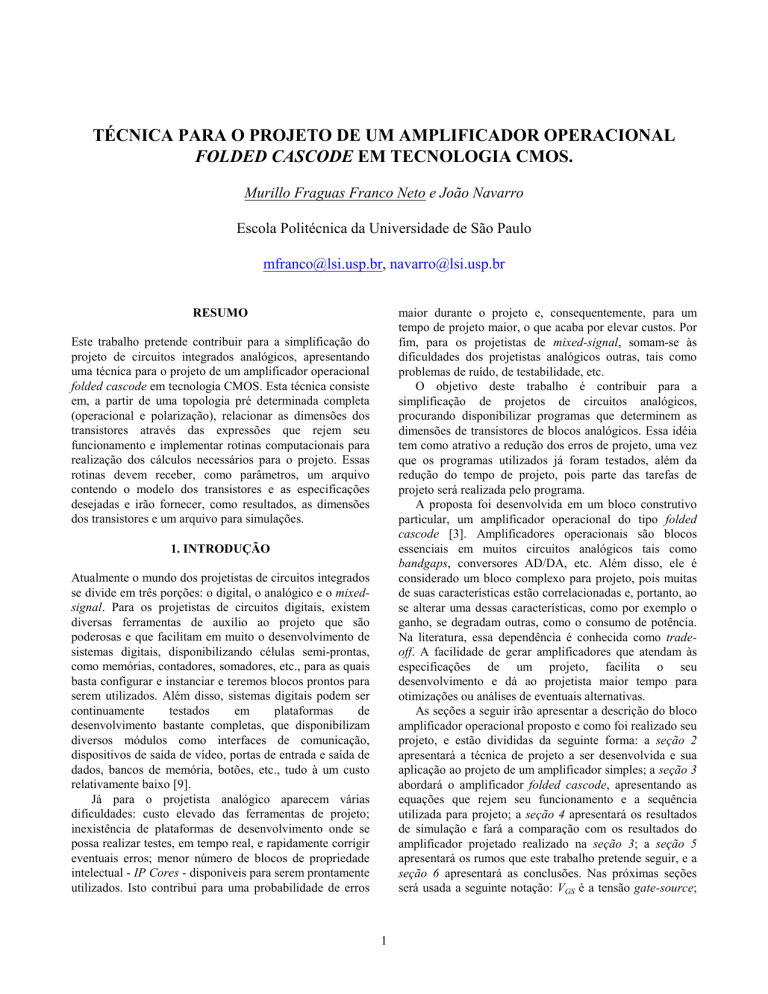

Essa técnica será aplicada, inicialmente, ao projeto de

um amplificador simples, figura 1, composto de um par

diferencial de entrada e de um espelho de corrente

funcionando como carga ativa, além de um capacitor

representado uma carga conectada ao nó de saída do

circuito.

M3

M4

UNIDADE

Ganho DC

45

dB

GBW

> 30

MHz

Margem de Fase

80

°

CL

10

pF

IBIAS

500

μA

Para o projeto dos transistores foram usadas as

seguintes equações simplificadas:

Corrente de dreno:

ID =

W

1

⋅ K ⋅ ⋅ (VGS − VTH )2

2

L

(1)

onde K= μCox

Tensão de saturação:

VDSAT =

Tensão de limiar:

VTH = VTH 0 + γ ⋅

2 ⋅ ID

W

K⋅

L

( 2⋅ φ

F

+ VSB − 2 ⋅ φ F

(2)

) (3)

onde VTH0, γ e φF são parâmetros da tecnologia.

Condutância dreno source do transistor:

gds ≈ λ ⋅ I D

Nó 1

onde λ é o inverso da tensão de Early:

1

λ=

VA

As seguintes equações, conhecidas na literatura, são

importantes no amplificador:

Impedância de saída (Nó 1):

CL

M2

M5

VALOR

2.1. Equações do Amplificador Simples

Nó 2

M1

Especificação

Ro1 = (gds M 4 + gds M 2 )−1

Impedância do nó interno (Nó 2, Figura 1):

Ro 2 = ( gmM 3 + gdsM 1 )−1 ≈ 1

gmM 3

Capacitância de saída (Nó 1, Figura 1):

C1 ≈ C L

onde CL é a carga na saída.

Capacitância do nó interno (Nó 2):

M6

Figura 1: Amplificador Operacional simples.

C 2 = C dbM 1 + C gsM 3 + C dbM 3 + C gsM 4

Pólo dominante (Nó 1):

1

1

fp1 =

≈

2 ⋅ π ⋅ Ro1 ⋅ C1 2 ⋅ π ⋅ Ro1 ⋅ C L

Pólo não-dominante (Nó 2):

1

fp 2 =

2 ⋅ π ⋅ Ro 2 ⋅ C 2

Esse amplificador simples foi escolhido inicialmente

pois suas características e as equações que rejem seu

funcionamento são amplamente conhecidas na literatura e

estão devidamente validadas [3] [8], o que reduz o trabalho

de avaliação da idéia.

A tabela 1 mostra as especificações adotadas para o

projeto do amplificador operacional simples.

2

(4)

Ganho do amplificador (entrada não-inversora):

AV = gm M 1 ⋅ Ro1

Transcondutância do transistor:

2⋅ ID

W

gm ≈ 2 ⋅ I D ⋅ K ⋅

=

L

VGS − VTH

Banda de ganho unitário do amplificador:

GBW = AV ⋅ fp1

Margem de fase do amplificador:

⎛ | fp | ⎞

2 ⎟

⎟

⎝ GBW ⎠

Φ M = arctan⎜⎜

o valor da tensão entre os terminais porta-fonte de M6.

Para nosso caso temos:

>> vgs_n_mirror(500e-6, 0.4979, 40, 1)

resultando

>> VGS = 0,97 V

(5)

3- Determinação da tensão dreno-fonte, VDS, no

transistor M5 do espelho de corrente: Para uma primeira

tentativa, será adotada para a tensão VDS de M5, o valor de

VGS do espelho de corrente, calculado no passo 2. Essa

tensão VDS é importante, pois influenciará na tensão de

limiar, VTH, dos transistores do par diferencial de entrada

(transistores M1 e M2). Logo,

VDS = 0,97 V (transistor M5)

(6)

Uma vez conhecidas essas equações, que dependem da

topologia do amplificador, torna-se possível definir uma

sequência de projeto e utilizar rotinas computacionais para

efetuar os cálculos dessa sequência. Dessa forma, se as

especificações do projeto forem modificadas, pode-se

reprojetar rapidamente o amplificador, apenas mudando os

parâmetros fornecidos para as rotinas.

4- Determinação da tensão de limiar para os

transistores do par diferencial da entrada: Foi escrita a

rotina vt() no MATLAB para tal. Esta rotina recebe o valor

da tensão fonte-substrato, VBS, do transistor M1 ou M2, e

retorna o valor da nova tensão de limiar VTH. Para nosso

caso temos:

>> vt(0,97)

resultando

>> VTH = 0,7738 V

2.2. Projeto do Amplificador Simples

O projeto do amplificador simples foi realizado

utilizando rotinas construídas com a ferramenta MATLAB,

que implementam as equações apresentadas anteriormente,

e os parâmetros dos transistores foram retirados do modelo

BSIM3v3 CMOS 0,35μm. A seguir são mostradas a

seqüência de projeto e uma breve descrição dessas rotinas.

O símbolo “ >> “ usado abaixo representa a linha de

comando da ferramenta MATLAB, podendo indicar a

chamada de uma rotina, com os parâmetros passados, ou a

saída de uma rotina, com os resultados do projeto.

5- Determinação das dimensões dos transistores M1,

M2, M3 e M4: Para isso, a rotina dsgn() foi escrita no

MATLAB. Esta rotina recebe como parâmetros a corrente

de dreno ID que passa pelo transistor M1, a tensão de limiar

VTH de M1, calculada no passo 4, o ganho desejado para o

amplificador (em dB) e a margem de fase desejada para o

circuito. Ela retorna a relação W/L dos transistores M1,

M2, M3 e M4, a banda do circuito (em MHz), a tensão VGS

dos transistores M1 e M2, a posição do primeiro e do

segundo pólos (fp1 e fp2, em Hz). Para o cálculo da

dimensão dos transistores M1 e M2, são utilizados o valor

do ganho fornecido e a impedância de saída, nó 1, da

figura 1. Essa impedância, para o caso deste circuito, é

dada pela expressão (4), onde a condutância do transistor i

pode ser aproximada por gds ≈ λ ⋅ I D .

Para se estimar os termos gdsM2 e gdsM4 de (4), traçouse uma reta tangente à curva ID x Vds de cada transistor; o

ponto onde esta reta cruza o eixo horizontal representa a

tensão de Early usada para determinar gds. Essa

caracterização foi realizada, tanto para os transistores

PMOS quanto para os transistores NMOS, e os resultados

estão na tabela 2. Os valores do parâmetro λ foram obtidos

para um valor de comprimento de canal L=1 μm.

1- Determinação do Espelho de Polarização: O primeiro

passo é adotar um valor para a tensão VDSAT do transistor

M5. Essa escolha deve levar em consideração a mínima

tensão de modo comum a ser aplicada nos transistores de

entrada. Para o nosso caso, será escolhida uma tensão

VDSAT =0,38V. Dessa forma, a relação W/L dos transistores

do espelho de polarização (transistores M5 e M6) pode ser

calculada. De (2) teremos:

0,38 =

2 ⋅ 500 μ

W

170 μ ⋅

L

40 ⎡ μm ⎤

⎛W ⎞

.

Obtendo-se uma relação ⎜ ⎟

=

μm⎥⎦

1 ⎢⎣

⎝ L ⎠ M 5, M 6

2- Determinação da tensão porta-fonte, VGS, no espelho

de corrente: Foi escrita a rotina vgs_n_mirror() no

MATLAB para determinar essa tensão. Esta rotina recebe

como parâmetros a corrente de dreno ID de M6, a tensão de

limiar VTH de M6, e as dimensões W e L, que foram

escolhidas para o espelho de corrente no passo 1, e retorna

3

Tabela 2: Estimativa do parâmetro λ que representa o

inverso da tensão de Early

Parâmetro

VALOR

UNIDADE

λPMOS

0,047

V

-1

λNMOS

0,016

V

-1

Foi realizada uma simulação AC do circuito projetado e

os resultados dessa simulação são apresentados na tabela 3.

O modelo dos transistores utilizado para as simulações é o

MOS BSIM3v3.

Tabela 3: Resultados da simulação AC do amplificador

operacional simples

Os valores de λ estimados foram inseridos no corpo da

rotina dsgn(). Agora já é possível efetuar os cálculos:

>> dsgn(250e-6,0.7738,45,81)

resultando:

95 ⎡ μm ⎤

⎛W ⎞

>> ⎜ ⎟

=

⎝ L ⎠ M 1, M 2 1 ⎢⎣ μm ⎥⎦

96 ⎡ μm ⎤

⎛W ⎞

>> ⎜ ⎟

=

μm ⎥⎦

L

⎝ ⎠ M 3, M 4 1 ⎢⎣

>> fp1 = 250 kHz

>> fp2 = 281,4 MHz

>> GBW = 44,5 MHz

>> VGS = 0,95 V

Parâmetro

PROJETO

SIMULAÇÃO

UNIDADE

IBIAS

500

500

μA

VDD

3

3

V

CL

10

10

pF

(W/L)1,2

95/1

95/1

-

(W/L)3,4

96/1

96/1

-

Ganho DC

45

42,3

dB

fp1

250

275

kHz

GBW

44,5

35,7

MHz

MF

81

86,5

°

6- Determinação da tensão mínima de modo comum

da entrada: A tensão mínima de modo comum da entrada

deve ser calculada levando-se em consideração a tensão

VDSAT de M5, utilizada no passo 1, e a tensão VGS de M1,

calculada no passo 5. Assim,

VCMmin = VDSAT_M5 + VGS_M1 = 0,38 V + 0,95 V = 1,33 V

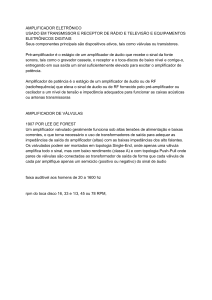

Nó 2

Nó 1

Figura 2: Topologia completa do amplificador operacional folded cascode.

4

Banda de ganho unitário do amplificador (expressão

simplificada):

gm M 1

GBW ≈

(14)

2 ⋅ π ⋅ (2 ⋅ C C )

Banda de ganho unitário do amplificador (expressão

completa):

AV ⋅ gmM 1 ⋅ ( gmM 8 + gdsM 8 ) +

GBW = OUT

2 ⋅ π ⋅ (2 ⋅ CC ) ⋅ ( AVOUT + 1) ⋅

3. O AMPLIFICADOR OPERACIONAL FOLDED

CASCODE

Em relação ao amplificador simples apresentado na seção

anterior, o amplificador operacional folded cascode

apresenta uma série de fatores que o tornam mais

complexo, dentre eles [5] [6]:

•

•

•

•

•

•

[

Estágio de polarização completo;

Estágio de saída classe AB, rail-to-rail;

Circuito de controle de corrente mínima na saída;

Espelhos cascode;

Compensação Miller com nulling resistor;

Carga capacitiva na saída elevada.

+ gdsM 7 ⋅ gdsM 8

(15)

R

⎤

⋅ (gmM 8 + gdsM 7 + gdsM 8 ) + C ⋅ gdsM 7 ⋅ gdsM 8 ⎥

2

⎦

Parâmetro que determina a região de operação do

transistor [7]:

I

(16)

LIM = D

I D lim

onde os seguinites limites devem ser observados:

• LIM > 8: Inversão Forte;

• LIM < 0,125: Inversão Fraca;

• 0,125 < LIM < 8: Inversão Moderada

Limiar de corrente de dreno [7]:

W

I D lim = K ⋅ ⋅ 2n ⋅ U T2

(17)

L

onde n é um parâmetro da tecnologia e UT é a tensão

térmica (∼ 27 mV à 40°C).

Slew Rate (SR):

I

I

(18)

SR = ≈ FOLDED

C

2 ⋅ CC

IFOLDED é a corrente que passa pelo transistor M12

Neste caso foram também utilizadas equações

simplificadas para o transistor. Para este amplificador as

equações importantes são:

Transcondutância do estágio de saída:

gmO = gm MP + gm MN

(7)

Pólo dominante após a compensação em frequência

(Nó 1):

1

fp1 =

2 ⋅ π ⋅ Ro1 ⋅ AVOUT ⋅ C + C P

(

)

onde R01 é a resistência no nó 1 da figura 2, AVout é o

ganho do estágio de saída, CP representa a somatória

das capacitâncias parasitas no nó 1 da figura 2 e C,

capacitância de compensação.

Pólo não-dominante após a compensação em

frequência (Nó 2):

gmO

(8)

fp 2 =

2 ⋅ π ⋅ CL

onde CL é a capacitância de carga do amplificador.

Ganho do estágio de saída:

AVOUT ≈ gmO ⋅ R L

(9)

A expressão (15) é mais completa do que (14), e

corrige uma falha grave que (14) apresenta: o fato de

considerar gdsM7 muito menor do que gmM8 pode acarretar

um erro considerável caso essa hipótese não seja

verdadeira. No caso deste amplificador, gdsM7 é da mesma

ordem de grandeza de gmM8, e por isso a expressão (14)

fornece um resultado bastante diferente da banda real,

enquanto que a expressão (15) fornece um resultado

próximo.

Infelizmente (15) contém os termos gds que são difíceis

de estimar; dependendo do ponto de operação dos

transistores na curva Id x Vds, a componente gds pode

variar muito. Por este motivo, o projeto do amplificador

será, num primeiro momento, realizado utilizando (14),

sendo que (15) será utilizada após a simulação AC do

circuito, para verificar a banda de ganho unitário, e para

realizar eventuais modificações no circuito. Para poder

utilizar (15) aproveitaremos os parâmetros gds calculados

pelo simulador Eldo aplicado ao projeto feito utilizando

(14).

onde RL é a resistência de carga do amplificador.

Relação entre a capacitância de compensação em

frequência C, e capacitâncias parasitas CP:

AVOUT ⋅ C >> C P

(10)

Capacitância CC é dada por:

C = 2 ⋅ CC

(11)

Frequência do zero introduzido pela compensação em

frequência:

1

(12)

ZC =

⎛ 1

RC ⎞

⎟

2 ⋅ π ⋅ C ⋅ ⎜⎜

−

2 ⎟⎠

⎝ gm O

Resistor de compensação em frequência:

2

RC =

(13)

gmO

5

VGMN ≈ 0,68 V

3.1. Projeto do Amplificador Folded Cascode

O projeto do amplificador folded cascode foi realizado

utilizando-se uma sequência de projeto que será

posteriomente transformada em rotinas computacionais. A

tabela 4 mostra as especificações iniciais adotadas para o

projeto do amplificador e a seqüência de projeto é

apresentada abaixo.

3- Projeto dos capacitores, CC, e resistores, RC, de

compensação: Utilizando as expressões (9), (10) e (11),

levando em conta uma capacitância parasita CP ≅ 0,35 pF

no nó 2, e considerando a resistência de carga indicada na

tabela 4, teremos,

[ V]

AVOUT ≈ 6,5 V

Tabela 4: Especificações para o projeto do amplificador

operacional folded cascode.

ESPECIFICAÇÃO

Valor

Unidade

GBW

5

MHz

MF

60

°

VOUT (PP)*

2,4

V

RL

4

kΩ

CL

30

pF

SR

2

V/μs

IBIAS

1,5 ± 20%

μA

VDD

2,8

*(PP) indica a excursão pico à pico do sinal

RC = 1,227 kΩ

4- Projeto dos transistores de entrada M1 e M2:

Conforme explicado no início da seção 3, o projeto de M1

e M2 será feito utilizando-se a expressão simplificada de

GBW, (14). Assim, substituindo em (14) os valores da

tabela 4 e de CC , chegamos à,

gm M 1 = 47 μS

Transistores PMOS operando em inversão forte geram

menor ruído flicker do que operando em inversão

moderada ou fraca [1]. As expressões (16) e (17) indicam

em qual região de operação o transistor está operando.

Logo, para que os transistores M1 e M2 operem em

inversão forte, de acordo com (17),

⎛W ⎞

I D lim = 0,114 ⋅ ⎜ ⎟

μA

⎝ L ⎠ M1

Substituindo o resultado em (16), a corrente de

polarização de M1 deve ser tal que,

V

gm = 1,63 mS

o

⎛W ⎞

I D > 0,91 ⋅ ⎜ ⎟

⎝ L ⎠M1

logo,

⎤

⎡ μm

μm⎥⎦

⎢⎣

4,6 9,2

⎛W ⎞

=

=

⎜ ⎟

1

2

⎝ L ⎠ M 1, M 2

⎞ ⎛W ⎞

⎛W ⎞

⎟⋅⎜ ⎟

= 2,93 ⋅ ⎜ ⎟

⎟ ⎝L⎠

⎝ L ⎠ MN

⎠

MN

⎡ μm ⎤

⎢⎣ μm⎥⎦

onde L=2μm foi utilizado para se ter um melhor

casamento entre os transistores [4].

O par diferencial de entrada é polarizado através de uma

fonte de corrente ITAIL que é dada por ITAIL = m ⋅ I BIAS ,

onde m representa o fator de espelhamento e IBIAS é uma

corrente externa de polarização. Assim, M1 e M2 terão

m ⋅ I BIAS

.

uma corente de dreno dada por I D =

2

Considerando o pior caso de IBIAS da tabela 4 (-20%), e

garantindo que os transistores estejam trabalhando na

região de inversão forte, devemos ter um fator de

temos,

29 ,1

⎛W ⎞

=

⎜ ⎟

1

⎝ L ⎠ MN

μA

Substituindo esse resultado em (5), e utilizando o valor da

transcondutância de M1 calculado anteriormente, a

relação W/L de M1 e de M2 pode ser calculada,

considerando a relação entre os transistores PMOS e

NMOS,

⎛K

⎛W ⎞

= ⎜⎜ P

⎜ ⎟

⎝ L ⎠ MP ⎝ K N

e CC >> 0 ,025 pF

Um valor razoável para CC é CC = 0 ,75 pF . Finalmente,

pela expressão (13) temos,

1- Projeto dos transistores MN e MP do estágio de

saída: Admitindo apenas dois pólos importantes para o

amplificador, de (5) (6) (7) e (8) e escolhendo uma

corrente quiescente de saída IQ = 80μA, temos,

85,3

⎛W ⎞

=

⎜ ⎟

1

L

⎝ ⎠ MP

VGMP ≈ 1,92 V

⎤

⎡ μm

μm ⎥⎦

⎢⎣

2- Cálculo das tensões VgsMN e VgsMP (quiescentes)

nos terminais de porta dos transistores de saída:

Considerando a corrente quiescente IQ = 80μA, e

utilizando as relações W/L calculadas no passo 1, de (1)

temos,

6

( L)

espelhamento

m > 6,93 .

Escolhendo

m=8,

e

considerando agora o caso nominal de IBIAS, teremos

I TAIL = 12 μA .

Resolvendo as duas equações para W

1,7

⎛W ⎞

=

⎜ ⎟

2

L

⎝ ⎠ M 15

5- Projeto de M5 e M7 / M6 e M8: A corrente para

polarizar cada ramo do estágio folded cascode pode ser

escolhida levando-se em consideração a especificação de

Slew Rate do amplificador. Para o circuito, o nó

responsável pelo Slew Rate é o nó 1, figura 2, e (18)

relaciona SR e a corrente no estágio folded cascode. A

expressão é aproximada pois não foram consideradas as

capacitâncias parasitas mas apenas a capacitância de

compensação. Assim, substituindo o resultado do passo 3

e resolvendo para IFOLDED teremos,

I FOLDED = 3μA

Logo, para o cálculo de M5 e M7, vamos utilizar a

corrente de polarização IFOLDED=3μA, e substituir o

resultado do passo 2 em (1), o que fornece,

6,6

⎛W ⎞

=

⎜ ⎟

2

⎝ L ⎠ M 5, M 7

5

⎛W ⎞

=

⎜ ⎟

⎝ L ⎠ M 16 2

⎡ μm ⎤

⎢⎣ μm⎥⎦

7- Projeto das fontes de corrente formadas por M3,

M4, M9, M10, M11 e M12: Para o espelho de corrente

formado por MP1, MP2 e MP3, será escolhido o valor

10 ⎡ μm ⎤

⎛W ⎞

⎛W ⎞

=⎜ ⎟

=

⎜ ⎟

μm ⎥⎦ e

L

L

⎝ ⎠ MP1 ⎝ ⎠ MP 2 2 ⎢⎣

20 ⎡ μm ⎤

⎛W ⎞

=

⎜ ⎟

2 ⎢⎣ μm⎥⎦

⎝ L ⎠ MP3

De forma imediata, de acordo com o cálculo de ITAIL

realizado no passo 4, teremos, ao considerar o caso

I

nominal de IBIAS na tabela 4, TAIL = 8 e portanto,

I BIAS

⎡ μm ⎤

μm⎥⎦

⎢⎣

⎛W ⎞

⎛W ⎞

⎛W ⎞

=⎜ ⎟

= 8⋅⎜ ⎟

⎜ ⎟

L

L

⎝ L ⎠ MP3

⎝ ⎠M 4 ⎝ ⎠M3

6- Projeto do circuito de controle AB, composto por

M15 e M16: Para seu projeto, devem ser consideradas

duas situações: a situação quiescente de operação do

circuito, e a situação em que o sinal de saída se encontra

em um valor de pico, onde um dos transistores de saída

conduz uma corrente máxima, e o outro transistor conduz

IQ

uma corrente mínima, dada por I MIN =

= 40 μA [6].

2

Além disso, deve-se levar em consideração o efeito de

corpo que modifica a tensão de limiar dos transistores do

controle AB. Assim, para a condição quiescente de

operação, utilizando (3) para calcular a nova tensão de

limiar

de

M15,

e

utilizando

o

resultado

V S M 15 = VGMN ≈ 0,68 V do passo 2, temos a primeira

⇒

160 ⎡ μm ⎤

⎛W ⎞

⎛W ⎞

=⎜ ⎟

=

⎜ ⎟

2 ⎢⎣ μm ⎥⎦

⎝ L ⎠M 4 ⎝ L ⎠M3

No passo 5 foi determinado IFOLDED = 3μA, que fornece

I FOLDED

= 2 , logo,

I BIAS

⎛W ⎞

⎛W ⎞

⎛W ⎞

=⎜ ⎟

= 2⋅⎜ ⎟

⎜ ⎟

L

L

⎝ L ⎠ MP3

⎝ ⎠ M 9 ⎝ ⎠ M 10

⇒

40 ⎡ μm ⎤

⎛W ⎞

⎛W ⎞

=

⎜ ⎟ =⎜ ⎟

L

L

⎝ ⎠ M 9 ⎝ ⎠ M 10 2 ⎢⎣ μm⎥⎦

equação dada por,

1

⎛W ⎞

1,5μ = ⋅170 μ ⋅ ⎜ ⎟

⋅ VGM 15 − 0,68 − 0,7 2

2

⎝ L ⎠ M 15

Para a condição de corrente mínima em um dos

transistores de saída, teremos V S M 15 = VGMN ≈ 0,63 V , e

)

Escolhemos ainda M11 = M9 e M12 = M10.

8- Projeto do estágio de polarização: Os transistores

MP8, MP12, MP13, MP18 e MP19 são espelhos de

corrente que espelham IBIAS, e têm, portanto, a mesma

relação W/L de MP3. Já a tensão de polarização de M6 e

M8 segue a seguinte equação,

calculando a nova tensão de limiar de M15 para este caso,

teremos a segunda equação,

1

⎛W ⎞

3μ = ⋅170 μ ⋅ ⎜ ⎟

⋅ VGM 15 − 0,63 − 0,69 2

2

⎝ L ⎠ M 15

(

⎡ μm ⎤

μm⎥⎦

⎢⎣

Escolhemos ainda M13 = M15 e M14 = M16.

Escolhendo uma tensão de overdrive para M6 e M8 igual

à de M5 e M7 e utilizando (1), vem,

(

vem,

Fazendo a mesma consideração do passo 1, temos

⎡ μm ⎤

⎢⎣ μm⎥⎦

2,2

⎛W ⎞

=

⎜ ⎟

2

⎝ L ⎠ M 6, M 8

M 15

)

VGS M 5 − VTH M 5 + VGS M 6 = VGS MP11 + VGS MP10 − VGS MP 9

7

MP14, MP15, e pode ser expressa da seguinte maneira [5]

[6],

Como a corrente de polarização que passa por MP10 e

MP11 é metade da corrente que passa por M6 e é um

sexto da corrente que passa por M5, para que as tensões

VGS de MP10 e MP11 sejam iguais às tensões VGS de M5

e M6, devemos ter,

1 ⎛W ⎞

1 ⎛W ⎞

⎛W ⎞

⎛W ⎞

=⎜ ⎟

= ⎜ ⎟ = ⎜ ⎟

⎜ ⎟

⎝ L ⎠ MP10 ⎝ L ⎠ MP11 2 ⎝ L ⎠ M 6 6 ⎝ L ⎠ M 5

Facilmente se obtém ,

1,1 ⎡ μm ⎤

⎛W ⎞

⎛W ⎞

=⎜ ⎟

=

⎜ ⎟

⎝ L ⎠ MP10 ⎝ L ⎠ MP11 2 ⎢⎣ μm⎥⎦

VSG MP + VSGM 16 = VSGMP14 + VSG MP15

Foram escolhidas

VSG MP = VSG MP15

e VSG M 16 = VSGMP14

Temos então,

5,2 ⎡ μm ⎤ ⎛ W ⎞

1,6 ⎡ μm ⎤

⎛W ⎞

=

e ⎜ ⎟

=

⎜ ⎟

μ

m

⎢

⎥

⎣

⎦

L

L

2

⎝ ⎠ MP14

⎝ ⎠ MP15 1 ⎢⎣ μm ⎥⎦

A tensão VGS de MP9 deve ser aproximadamente igual à

tensão de limiar, VTH , de M5. Para isso MP9 deve ser

projetado para trabalhar na região de inversão fraca.

Assim, como a corrente que passa por MP9 é 1,5 μA, de

(17) devemos ter I D = 1,5μA < I D lim e LIM < 0,125 , de

forma a garantir operação na região de inversão fraca.

Assim, I D ≤ 0,125 ⋅ I D lim ⇒ I D lim ≥ 12 μA . Logo,

utilizando (17) e escolhendo n=1,2, teremos,

⎛W ⎞

≥ 40,3 [7]. Vamos trabalhar com o valor de

⎜ ⎟

⎝ L ⎠ MP9

Analogamente, para a tensão VGB, os transistores MP20 e

MP21 são projetados, obtendo-se,

0,55 ⎡μm ⎤

1,7 ⎡ μm ⎤

⎛W ⎞

⎛W ⎞

=

e ⎜ ⎟

=

⎜ ⎟

μ

m

μm ⎥⎦

⎢

⎥

⎣

⎦

1

⎝ L ⎠MP20

⎝ L ⎠ MP 21 2 ⎢⎣

A tabela 5 apresenta os valores das relações W/L dos

transistores projetados para o amplificador operacional

folded cascode.

L=0,35μm, para diminuir a área ocupada pelo transistor.

70 ⎡ μm ⎤

⎛W ⎞

=

,o

Finalmente, será escolhido ⎜ ⎟

0

,35 ⎢⎣ μm ⎥⎦

L

⎝ ⎠ MP9

que fornece um valor para o parâmetro LIM=0,025,

indicando operação na região de inversão fraca.

Da mesma forma, os transistores MP4, MP5, MP6 e MP7

podem ser calculados. MP7 espelha IBIAS e tem a mesma

relação W/L de MP1 e MP2. Será escolhida a seguite

relação,

Tabela 5: Transistores projetados para o amplificador folded

cascode.

10 ⎡ μm ⎤

⎛W ⎞

⎛W ⎞

⎛W ⎞

=⎜ ⎟

=⎜ ⎟

=

⎜ ⎟

L

L

L

⎝ ⎠ MP1 ⎝ ⎠ MP 2 ⎝ ⎠ MP 7 2 ⎢⎣ μm ⎥⎦

De forma análoga ao cálculo de MP9, MP10 e MP11, os

transistores MP4, MP5, MP6 são projetados, resultando

em,

20 ⎡ μm ⎤

⎛W ⎞

⎛W ⎞

=⎜ ⎟

=

⎜ ⎟

2 ⎢⎣ μm⎥⎦

⎝ L ⎠ MP 4 ⎝ L ⎠ MP5

120 ⎡ μm ⎤

⎛W ⎞

e ⎜ ⎟

=

, para operação na região de

⎝ L ⎠ MP6 0,35 ⎢⎣ μm⎥⎦

inversão fraca. Os transistores MP16 e MP17 são

projetados para espelhar a corrente IBIAS nos seus

respectivos ramos de polarização, e têm a mesma relação

W/L de MP1 e MP2.

As tensões de polarização VGA e VGB, nos terminais de

porta de M16 e M15, respectivamente, são geradas pelos

transistores de polarização MP14 e MP15 (VGA), e MP20

e MP21 (VGB). A equação para VGA é obtida através da

malha translinear formada pelos transistores MP, M16,

TRANSISTOR

Projeto

(W/L)

Transistor

Projeto

(W/L)

MN

29,1

1

MP1, MP2,

MP7, MP16,

MP17

10

2

MP

85,3

1

MP3, MP4,

MP5, MP8,

MP18, MP19

20

2

M1, M2

9,2

2

MP10, MP11

1,1

2

M5, M7

6,6

2

MP9

70

0,35

M6, M8

2,2

2

MP6

120

0,35

M13, M15,

MP21

1,7

2

MP14

5,2

2

M14, M16

5

2

MP15

1,6

1

M3, M4

160

MP20

0,55

1

MP12, MP13

20

2

2

M9, M10,

M11, M12

8

40

2

simulado para

amplificador.

4. RESULTADOS DE SIMULAÇÃO E ANÁLISE

A tabela 6 apresenta os resultados de uma simulação AC

do amplificador operacional folded cascode e as

especificações iniciais.

Especificação

Resultado

simulado

Unidade

Av

-

78,2

dB

fp1

-

407,9

Hz

GBW

5

3,03

MHz

MF

60

63,5

°

VOUT (PP) *

2,4

2,4

V

das

características

do

6. CONCLUSÕES

Neste trabalho é proposto o desenvolvimento de programas

para auxilio no projeto de blocos analógicos. A função dos

programas é, a partir de uma especificação de entrada,

determinar as dimensões dos transistores do bloco

analógico. Para levar adiante a idéia é necessário primeiro

obter as relações importantes de funcionamento do bloco e

depois estabelecer uma seqüência apropriada de projeto.

Apresentamos aqui como tal programa pode ser

implementado considerando dois blocos amplificadores,

um simples, com apenas um par diferencial, e outro

complexo, com configuração folded cascode e seu circuito

de polarização. No caso do circuito simples foram

determinadas as relações importantes, desenvolvidas a

seqüência de projeto e algumas rotinas. Os resultados de

simulação apontam que os parâmetros calculados e o

simulados ficam próximos. Para o circuito complexo as

relações importantes e a seqüência de projeto foram

desenvolvidas, assim como o programa de auxílio ao

projeto, que foi utilizado para projetar o amplificador

folded cascode. Também neste caso, em boa parte, as

especificações calculadas ficaram próximas das

encontradas na simulação. A exceção foi do parâmetro

GBW, o que era esperado.

Tabela 6: Resultados da simulação AC do amplificador folded

cascode.

PARÂMETRO

avaliação

*(PP) indica a excursão pico à pico do sinal

Podemos verificar uma grande discrepância entre os

valores de GBW projetado e simulado. Conforme explicado

na seção 3, essa diferença ocorre por causa da utilização da

expressão (14) no projeto dos transistores do estágio de

entrada, onde gdsM7 é considerado desprezível em relação à

gmM8, o que não é verdade para esta topologia. Do arquivo

de saída da simulação AC, podemos retirar os valores dos

gds de interesse e utilizar a expressão (15) para confirmar

que a banda do circuito fica mesmo em torno de 3 MHz.

Efetuando os cálculos, obtemos para a expressão

simplificada o valor GBW ≈ 4 ,6 MHz , e para a expressão

7. BIBLIOGRAFIA

[1] J. Chang, A.A. Abidi, and C.R. Viswanathan, “Flicker Noise

in CMOS Transistors from Subthreshold to Strong Inversion at

Various Temperatures,” IEEE Transactions on Electron Devices,

pp. 1965-1971, November, 1994.

completa o valor GBW ≈ 3 ,4 MHz . Os resultados

mostram que a expressão completa fornece o melhor

resultado, mesmo sem levar em consideração as

capacitâncias parasitas. Infelizmente, como dito, sua

utilização implica no conhecimento do valor de gds.

[2] E. Crain and M.H. Perrott, "A numerical Design Approach for

High-Speed, Differential, Resistor-Loaded, CMOS Amplifiers,"

IEEE International Symposium on Circuits and Systems,

Vancouver, Canada, 2004.

5. CONTINUIDADE DO TRABALHO

Os próximos passos deste trabalho visam a implementação

do software que irá automatizar o projeto do amplificador

operacional folded cascode, seguindo a sequência de

projeto estabelecida na seção 3 [2]. Como dito

anteriormente, esse software pretende facilitar o projeto de

um amplificador nesta topologia, dando rapidamente uma

visão ao projetista das suas características. Dessa forma, a

tomada de decisão para aprimorar o projeto ou partir para

uma outra topologia, pode ser feita com menor esforço e

tempo.

O software será escrito em linguagem de programação

C, e funcionará por linha de comando na plataforma Linux.

A saída do software deverá fornecer um arquivo tipo

SPICE, ou seja um netlist, que poderá ser prontamente

[3] P.R. Gray and R.G. Meyer, "MOS Operational Amplifier

Design - A Tutorial Overview," IEEE Journal Solid-State

Circuits, pp. 969-983, December, 1982.

[4] A. Hastings, The Art of Analog Layout, Prentice Hall, 2000.

[5] R. Hogervorst, J.P. Tero, R.G.H. Eschauzier, and J.H.

Huijsing, “A Compact Power-Efficient 3V CMOS Rail-to-Rail

Input/Output Operational Amplifier for VLSI Cell Libraries,”

IEEE Journal of Solid-State Circuits, pp. 1505-1512, December,

1994.

[6] K. Langen and J.H. Huijsing, “Compact Low-Voltage PowerEfficient Operational Amplifier Cells for VLSI,” IEEE Journal of

Solid-State Circuits, pp. 1482-1496, October, 1998.

9

[7] M. Pardoen, “A Simple and Pretty Accurate MOS Model for

Hand Calculations,” Internet, 2001.

[8] M. Steyaert, W. Sansen, J.H. Huijsing, and R. Plassche,

“Opamp Design towards Maximum Gain-Bandwidth”. Analog

circuit design. Operational amplifiers, analog to digital

converters, analog computer aided design, Kluwer Academic

Publishers, Delft, pp. 63-85, March 1993.

[9] http://www.xilinx.com/products/devboards/index.htm

10