UNIVERSIDADE SÃO MARCOS

DATA:

HORÁRIO DE ENTRADA:

RGM:

Curso: TECNOLOGIA EM REDES DE TELECOM.

Roteiro – Parte Prática: DISC. CIRCUITOS SEQUÊNCIAIS

Profs Resps.: SÉRGIO PEREIRA / HERMEVALDO P. REIS

Lab.: ECE - 1 Apoio Geral: EQUIPE LAB TELE 2007

Turma: 5º/6ºA – 2º SEMESTRE DE 2007

HORÁRIO DE SAÍDA:

BANCADA:

NOMES DOS COMPONENTES DO GRUPO DE TRABALHO:

PROJETO - CONTADORES ASSÍNCRONOS

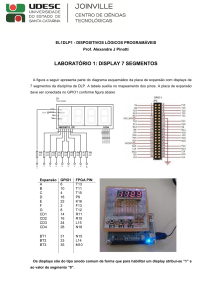

O objetivo desse projeto extra é aplicar os conceitos vistos em aula teórica

e os experimentos realizados em ambiente de laboratório e desenvolver um pequeno projeto:

Contador síncrono ou assíncrono e implementá-los em hardware (montagem em proto-board) e

também em software de simulação - MULTISIM.

Para montagem e testes desse projeto está prevista a realização em três fases

seqüênciais, como está citado no diagrama abaixo:

FASE I

OSCILADOR 555

FASE II

CIRCUITO COM

FLIP-FLOP

FASE III

DECODIFICADOR E

DISPLAY

1 - FASE I – OSCILADOR 555

O objetivo dessa primeira fase é calcular a freqüência de oscilação quando trabalha

como circuito estável.

O 555 é um circuito integrado (chip) utilizado em uma variedade de aplicações de

temporização ou como multivibrador. O 555 tem três modos de operação:

Modo monoestável: nesta configuração, o CI 555 funciona como um disparador. Suas

aplicações incluem temporizadores, detector de pulso, chaves imunes a ruído,

interruptores de toque, etc;

Modo estável: O CI 555 opera como um oscilador. Os usos incluem pisca-pisca de LED,

geradores de pulso, relógios, geradores de tom, alarmes de segurança, etc;

Modo biestável: o CI 555 pode operar como um flip-flop, se o pino DIS não for

conectado e se não for utilizado capacitor. A aplicações incluem chaves imunes a ruído,

etc.

Iremos utilizar o 555 como oscilador eletrônico (modo estável) é um circuito eletrônico que

produz um sinal eletrônico repetitivo, em nossa aplicação uma onda quadrada. Sem a

necessidade de aplicação de um sinal externo.

1

UNIVERSIDADE SÃO MARCOS

Curso: TECNOLOGIA EM REDES DE TELECOM.

Roteiro – Parte Prática: DISC. CIRCUITOS SEQUÊNCIAIS

Profs Resps.: SÉRGIO PEREIRA / HERMEVALDO P. REIS

Lab.: ECE - 1 Apoio Geral: EQUIPE LAB TELE 2007

Turma: 5º/6ºA – 2º SEMESTRE DE 2007

O impulso aparece quando a entrada de disparo (TRIGGER IN) cai abaixo de 1/3 da tensão

de alimentação, que neste caso é de 5V. A entrada do pulso de disparo tem que ser mais curta

que a largura do impulso de saída T. Às vezes convém proporcionar o impulso do disparador

médio de um circuito diferenciador formado por um capacitor e uma resistência. O impulso de

saída procedente deste circuito é aproximadamente igual a constante de tempo RC, no que a

largura se refere.

Na figura 1 mostra um circuito estável que utiliza um CI 555.

Figura 1 – Circuito de modo estável 555.

A temporização se controla por meio dos valores de Ra, Rb e C. A saída é alta durante

um tempo Th, dado pela expressão:

Th = 0,695 (Ra + Rb) C

A saída é baixa durante um tempo T1, dado pela expressão:

T1 = 0,695 Rb C

Algebricamente pode demonstrar que o período total e a freqüência de repetição dos

impulsos são demonstrados por:

T = Th + T1 = 0,695 (Ra = 2Rb) C

F = 1/T = 1,44/ ( (Ra + 2Rb) C)

O 555 tem duas entradas de controle adicionais. Uma entrada de reposição (RESET) que

para imediatamente a saída e a põe a nível baixo, e uma entrada de tensão de controle (Cv)

que se pode utilizá-la para varia a largura do impulso de saída, variando a tensão contínua a ela

aplicada e que varia a freqüência estável de oscilação.

2

UNIVERSIDADE SÃO MARCOS

Curso: TECNOLOGIA EM REDES DE TELECOM.

Roteiro – Parte Prática: DISC. CIRCUITOS SEQUÊNCIAIS

Profs Resps.: SÉRGIO PEREIRA / HERMEVALDO P. REIS

Lab.: ECE - 1 Apoio Geral: EQUIPE LAB TELE 2007

Turma: 5º/6ºA – 2º SEMESTRE DE 2007

Figura 2 – Configuração do circuito de modo estável 555

Figura 3 – Circuito simulado no MULTISIM - Modo estável 555

3

UNIVERSIDADE SÃO MARCOS

Curso: TECNOLOGIA EM REDES DE TELECOM.

Roteiro – Parte Prática: DISC. CIRCUITOS SEQUÊNCIAIS

Profs Resps.: SÉRGIO PEREIRA / HERMEVALDO P. REIS

Lab.: ECE - 1 Apoio Geral: EQUIPE LAB TELE 2007

Turma: 5º/6ºA – 2º SEMESTRE DE 2007

1.2 - RELAÇÃO DE MATERIAL

Quantidade

1

1

1

1

1

5

1

2

2

-

Descrição

Fonte de tensão de +5VCC (VDC)

Matriz de contatos

Multímetro

Osciloscópio

CI LM555, NE555

Resistores de 100, 1K e 10K Ω

Potenciômetro de 100K Ω

Capacitores 100nF

Cabos banana-banana

Fios rígidos 0,51mm φ

2 - FASE II – CIRCUITOS COM FLIP-FLOP E CIRCUITOS COMBINATÓRIOS

PARA CONTADOR ASSÍNCRONO

Nessa fase será verificado o funcionamento de contadores assíncronos Crescente e

Decrescente.

2.1 - PREPARAÇÃO – CONCEITOS

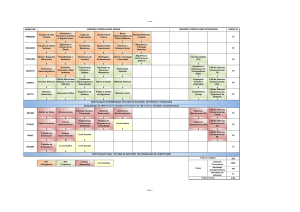

2.1.1- Contador Assíncronos Crescente

Nestes contadores, a saída de um Flip-Flop é ligada a entrada de clock do Flip-Flop

seguinte, ou seja, somente um Flip-Flop é controlado por pulsos de clock externos.

O numero “n” de estados internos irá caracterizar o modulo do contador. Assim, por

exemplo, um contador que possui oito estados internos é dito de modulo 8. Se este contador for

do tipo crescente, a sua base binária de contagem é de 000 a 111.

Figura 4 - Contador Assíncronos Crescente

O ciclo de contagem se repete após o 8º pulso de clock, pois todas as saídas mudam de

nível lógico “1” para nível “0”, forçando o retorno ao estado inicial: Q2 = 0, Q1 = 0 e Q0 = 0.

4

UNIVERSIDADE SÃO MARCOS

Curso: TECNOLOGIA EM REDES DE TELECOM.

Roteiro – Parte Prática: DISC. CIRCUITOS SEQUÊNCIAIS

Profs Resps.: SÉRGIO PEREIRA / HERMEVALDO P. REIS

Lab.: ECE - 1 Apoio Geral: EQUIPE LAB TELE 2007

Turma: 5º/6ºA – 2º SEMESTRE DE 2007

Pode-se, então, construir a seguinte tabela:

Figura 5 – Seqüência de Saída do Contador e Diagrama de Estado do Contador Crescente

2.1.2 - Contador Assíncrono Decrescente

O contador módulo 8 também pode fornecer em suas saídas, uma contagem decrescente como

mostra o diagrama de estados abaixo:

Figura 6 –Diagrama de Estado do Contador Descrescente

Uma das formas de se construir um contador assíncrono decrescente módulo 8 é dada abaixo:

5

UNIVERSIDADE SÃO MARCOS

Curso: TECNOLOGIA EM REDES DE TELECOM.

Roteiro – Parte Prática: DISC. CIRCUITOS SEQUÊNCIAIS

Profs Resps.: SÉRGIO PEREIRA / HERMEVALDO P. REIS

Lab.: ECE - 1 Apoio Geral: EQUIPE LAB TELE 2007

Turma: 5º/6ºA – 2º SEMESTRE DE 2007

Figura 7 - Contador Assíncronos Descrescente

2.3- Metodologia

M1- Será montado, inicialmente, um contador assíncrono crescente de módulo 16 (de 0 a 15),

utilizando Flip-Flop tipo JK master-slave e depois um contador decrescente de módulo 16.

M2- em seguida, será montado um contador assíncrono UP-DOWN de módulo 8. Uma linha de

controle irá determinar o tipo de contagem. Esta contagem será monitorada por display de sete

segmentos, utilizando-se o CI 7447 para decodificar/ acionar o display.

2.4 - Relação de Material

Quantidade

1

1

1

1

1

2

2

1

1

4

8

6

1

-

Descrição

Matriz de contatos

Fonte de alimentação de +5V

CI 7400

CI 7408

CI 7432

CI 7476

CI 4027

CI 7447

Display de 7-segmentos tipo ando comum

LEDs

Resistores de 330Ω

Resistores de 1Ω

Chave H-H

Fios rígidos 0,51mm φ

6

UNIVERSIDADE SÃO MARCOS

Curso: TECNOLOGIA EM REDES DE TELECOM.

Roteiro – Parte Prática: DISC. CIRCUITOS SEQUÊNCIAIS

Profs Resps.: SÉRGIO PEREIRA / HERMEVALDO P. REIS

Lab.: ECE - 1 Apoio Geral: EQUIPE LAB TELE 2007

Turma: 5º/6ºA – 2º SEMESTRE DE 2007

2.5 - Praticando

P1- Utilizando-se Flip-Flops tipo JK master-slave, sensíveis a borda de descida (CI

7476), montar e estudar a seqüência de contagem do circuito mostrado a seguir. Impor estado

inicial igual a zero, através do controle Clear.

Figura 9 – Circuito com Flip-Flop

P2 - Montar e estuda a seqüência de contagem do circuito a seguir. Impor estado inicial

iguala 15, através do contador Preset.

P3 - Colocar a linha de controle X em “0” e aplicar pulsos de clock, monitorando a

seqüência de contagem através do display.

P4- Colocar a linha de controle X em “1” e aplicar pulsos de clock, monitorando a

seqüência de contagem através do display.

P5- Utilizando Flip-Flops JK sensíveis à borda de subida (CI 4027), montar o contador

assíncrono a seguir. A seqüência de contagem será monitoramento pelo display de 7

segmentos. Para isso utiliza-se o CI 7447.

7

UNIVERSIDADE SÃO MARCOS

Curso: TECNOLOGIA EM REDES DE TELECOM.

Roteiro – Parte Prática: DISC. CIRCUITOS SEQUÊNCIAIS

Profs Resps.: SÉRGIO PEREIRA / HERMEVALDO P. REIS

Lab.: ECE - 1 Apoio Geral: EQUIPE LAB TELE 2007

Turma: 5º/6ºA – 2º SEMESTRE DE 2007

Figura 12 – Circuito com Flip-Flop utilizando o circuito eliminador de ruíd

3 - FASE III – DECODIFICADOR BCD DE 7 SEGMENTOS E DISPLAY

Nessa fase, o objetivo é verificar o funcionamento de um CI decodificador em conjunto com

um display de 7 segmentos.

3.1 PREPARAÇÃO – CONCEITOS Display

Para verificação dos algarismos decimais é comum utilizar em mostrador onde a

combinação de 7 segmentos de retas, luminosos ou não, são capazes de formar os 10

algarismos do sistema decimal. Este dispositivo é conhecido como display de 7 segmentos.

Existem displays de 7 segmentos eletromecânicos, outros construídos com lâmpadas

incandescentes, displays que utilizam LEDs, cristal liquido, etc. um tipo muito conhecido é o

construído com LEDs.

Os LEDs que constituem o display são alocados no componente numa disposição padrão

recebendo cada um deles uma letra minúscula para identificação. As letras são a, b, c, d, e, f e

g. os displays trazem, ainda, m ponto identificado pela letra “p”.

Quanto ao tipo de ligação interna, os displays podem ser classificados como anodo comum

e catodo comum. No display anodo comum, todos os anodos dos LEDs que formam o display

8

UNIVERSIDADE SÃO MARCOS

Curso: TECNOLOGIA EM REDES DE TELECOM.

Roteiro – Parte Prática: DISC. CIRCUITOS SEQUÊNCIAIS

Profs Resps.: SÉRGIO PEREIRA / HERMEVALDO P. REIS

Lab.: ECE - 1 Apoio Geral: EQUIPE LAB TELE 2007

Turma: 5º/6ºA – 2º SEMESTRE DE 2007

estão ligados entre si formando um único terminal – o anodo comum. No display catodo comum,

todos os catodos dos LEDs que formam o display estão ligados entre si formando um único

terminal – o catodo comum.

Figura 13 – Display de 7 segmentos anodo e catodo comum

Os LEDs que compõem o display suportam no máximo 2V/ 20mA, portanto não podem

ser ligados diretamente nas saídas das portas lógicas. É necessário utilizar um resistor em serie

para proteger os LEDs da corrente excessiva.

3.2 - Decodificador 7447

A Figura seguinte mostra os pinos do CI 7447 - decodificador/ driver BCD para 7

segmentos, ativo em nível baixo, saída – coletor aberto.

Figura 14 – Decodificador 7447

9

UNIVERSIDADE SÃO MARCOS

Curso: TECNOLOGIA EM REDES DE TELECOM.

Roteiro – Parte Prática: DISC. CIRCUITOS SEQUÊNCIAIS

Profs Resps.: SÉRGIO PEREIRA / HERMEVALDO P. REIS

Lab.: ECE - 1 Apoio Geral: EQUIPE LAB TELE 2007

Turma: 5º/6ºA – 2º SEMESTRE DE 2007

3.3 - Tabela de Funcionamento do CI 7447

Figura 15 – Tabela de Funcionamento do CI Decodificador 7447

3.4 - METODOLOGIA

M1 – Será implementado um circuito acionador decodificador para display de 7 segmentos

usando o CI 744 e um display anodo comum do tipo SD 567.

3.5 - RELAÇÃO DE MATERIAL

Quantidade

1

1

1

1

1

7

2

-

Descrição

Fonte de tensão de +5VCC (VDC)

Matriz de contatos

Multímetro

CI 7447

Display SD 567 (anodo comum)

Resistores de 330 Ω

Cabos banana-banana

Fios rígidos 0,51mm φ

10

UNIVERSIDADE SÃO MARCOS

Curso: TECNOLOGIA EM REDES DE TELECOM.

Roteiro – Parte Prática: DISC. CIRCUITOS SEQUÊNCIAIS

Profs Resps.: SÉRGIO PEREIRA / HERMEVALDO P. REIS

Lab.: ECE - 1 Apoio Geral: EQUIPE LAB TELE 2007

Turma: 5º/6ºA – 2º SEMESTRE DE 2007

3.6 - PRATICANDO

P1 – Implementar o circuito abaixo.

Figura 16 – Decodificador 7447 e Display de 7 segmentos.

P2 – Ligar a fonte de alimentação e aplicar níveis lógicos as entradas A, B, C e D do circuito,

conforme as indicações das linhas da tabela da verdade. Para cada situação de entrada

verificar o algarismo formando no display.

P3 – Colocar por um instante a entrada Lamp Test em nível baixo, ligando-se o pino 3 ao

terra do circuito. (RI-II)

P4 – Verificar o que acontece ao passar a entrada BI / RBO DO Vcc para o terra.

4 - REFERÊNCIAS BIBLIOGRÁFICAS

[1] ARAÚJO, Celso de e CHUI, William Soler. Praticando Eletrônica Digital, 3ed. São PauloSP: Érica, 2000.

[2] DEGEM SYSTEMS. EB-134 – Circuitos de Lógica Seqüênciais (Parte Prática).

DEGEM SYSTEMS, 2000.

[3] CAPUANO F. G. Elementos de Eletrônica Digital. 32ª edição, ed. Érica. São

Paulo, 2005.

[4] TOCCI, R. J., Sistemas Digitais – Princípios e Aplicações. 5ª edição, ed. LTC, Rio

de Janeiro – RJ, 1999.

11