EL1DLP1 - DISPOSITIVOS LÓGICOS PROGRAMÁVEIS

Prof. Alexandre J Pinotti

LABORATÓRIO 1: DISPLAY 7 SEGMENTOS

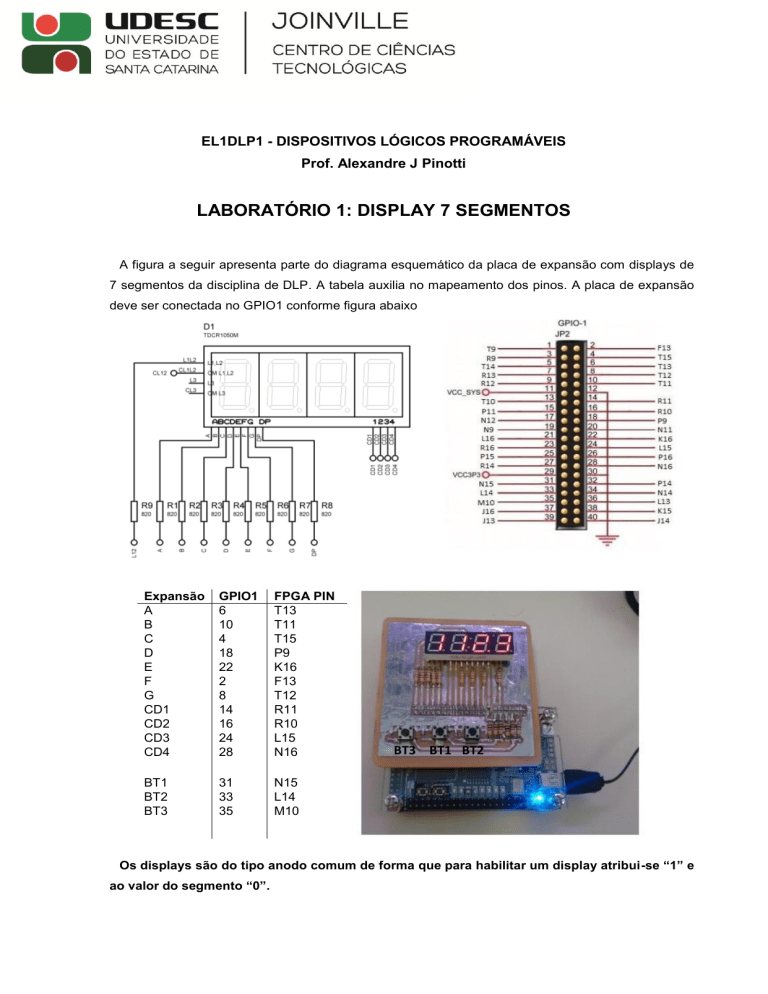

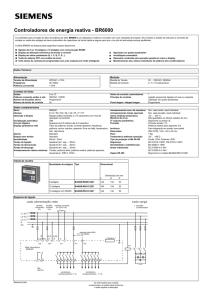

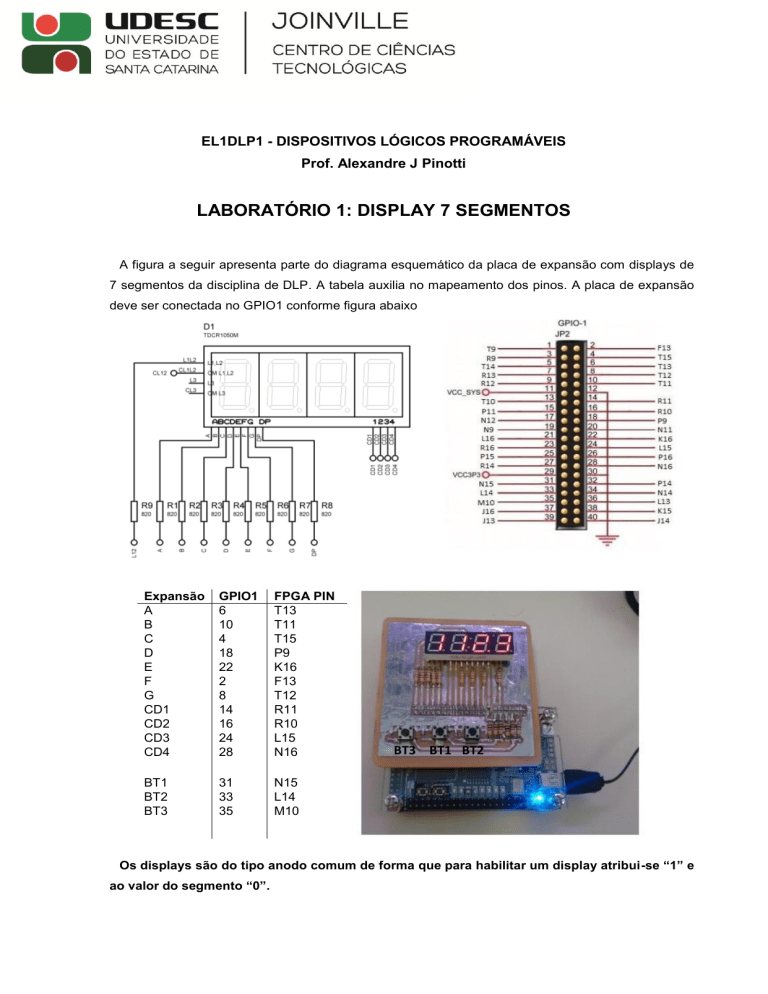

A figura a seguir apresenta parte do diagrama esquemático da placa de expansão com displays de

7 segmentos da disciplina de DLP. A tabela auxilia no mapeamento dos pinos. A placa de expansão

deve ser conectada no GPIO1 conforme figura abaixo

Expansão

A

B

C

D

E

F

G

CD1

CD2

CD3

CD4

GPIO1

6

10

4

18

22

2

8

14

16

24

28

FPGA PIN

T13

T11

T15

P9

K16

F13

T12

R11

R10

L15

N16

BT1

BT2

BT3

31

33

35

N15

L14

M10

BT3 BT1 BT2

Os displays são do tipo anodo comum de forma que para habilitar um display atribui-se “1” e

ao valor do segmento “0”.

ATIVIDADE 1

Mapear os segmentos (a – g) de forma a garantir um valor “0” ou “1” em cada um dos LEDs de um

display de 7-segmentos.

Utilizar os 3 push buttons para determinar para qual display de 7 segmentos a informação estabelecida

nos segmentos será apresentada.

Lembrar que o circuito dos push buttons apresentam Pull-Ups e que o display é selecionado com nível

“1”.

Realize uma lógica combinacional nos botões segundo a tabela verdade a seguir:

BT3

Solto

Pressionado

Solto

Solto

BT1

Solto

Solto

Pressionado

Solto

BT3

Solto

Solto

Solto

Pressionado

Display Selecionado

CD1

CD2

CD3

CD4

OBS: Acione apenas um push Button por vez para evitar que as saídas do FPGA acionem mais do que

apenas um dos displays.

ATIVIDADE 2

Utilizar um decodificador 7447 para transformar os valores dos 3 botões (informação binária) em um

valor hexadecimal e apresentar o valor em um dos display de 7 segmentos.

ATIVIDADE 3

Jogo da Conversão Decimal – Binário

Em UM display de 7 segmentos, deve ser apresentado um valor entre 0 e 7.

O número mostrado no display é fixo e faz parte do projeto do circuito, na forma binária.

Utilize o 7447 para converter o valor binário e apresentar no display.

O objetivo do jogo será determinar a combinação binária através dos 3 push buttons.

Caso a combinação que o jogador mantiver pressionado nos botões for equivalente à conversão

correta do número mostrado no display, um LED do kit FPGA deverá ser mantido aceso.