2.a Aula Prática – Projeto de Circuitos Sequenciais com

FPGA

Prof. Cesar da Costa

Projeto e simulação de contadores e divisores de

freqüência síncronos

Os contadores e divisores de freqüência síncronos possuem uma entrada comum

de clock, ou seja, todos os flip-flops são sincronizados, mudam de estado exatamente

com o mesmo sincronismo com que os pulsos de clock são aplicados.

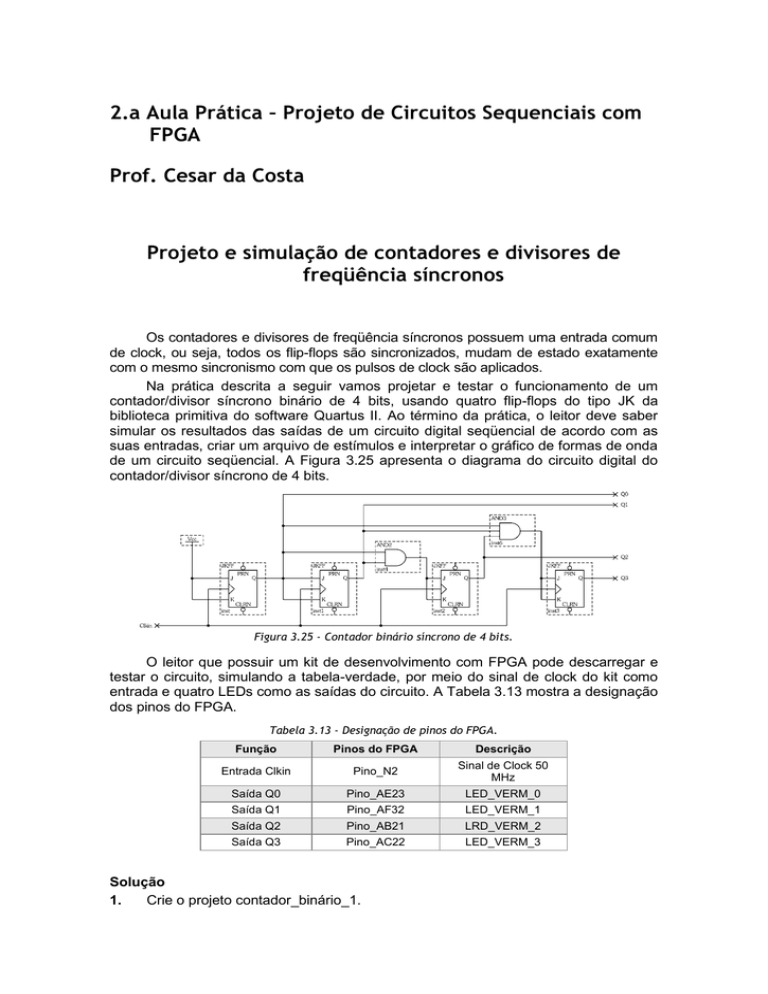

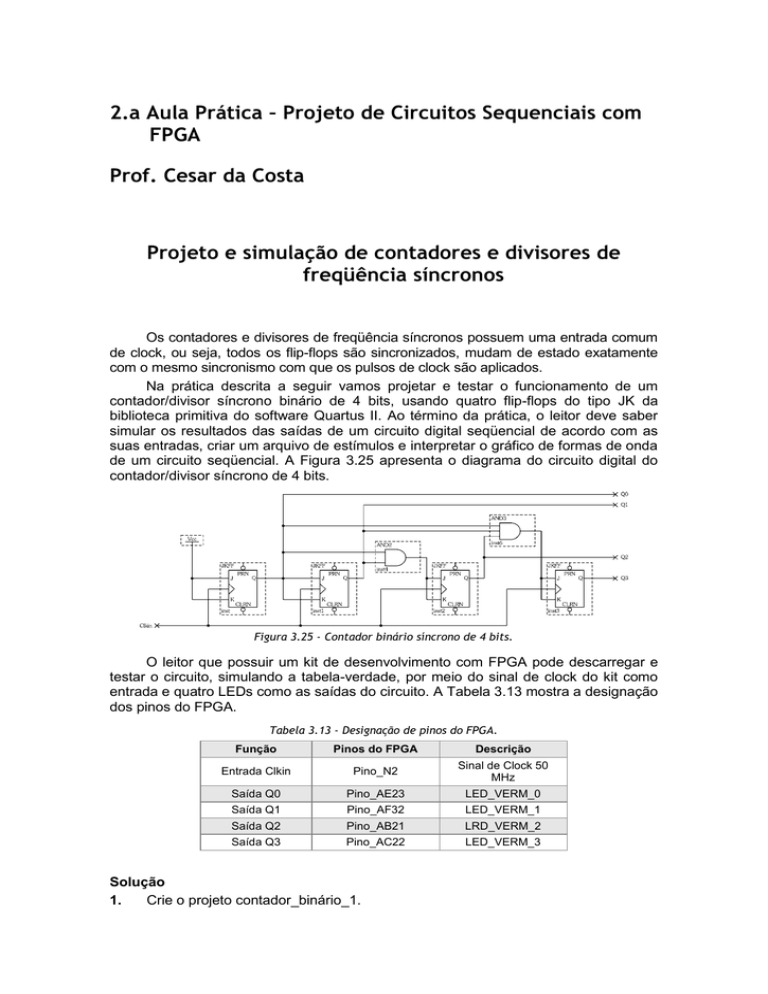

Na prática descrita a seguir vamos projetar e testar o funcionamento de um

contador/divisor síncrono binário de 4 bits, usando quatro flip-flops do tipo JK da

biblioteca primitiva do software Quartus II. Ao término da prática, o leitor deve saber

simular os resultados das saídas de um circuito digital seqüencial de acordo com as

suas entradas, criar um arquivo de estímulos e interpretar o gráfico de formas de onda

de um circuito seqüencial. A Figura 3.25 apresenta o diagrama do circuito digital do

contador/divisor síncrono de 4 bits.

Figura 3.25 - Contador binário síncrono de 4 bits.

O leitor que possuir um kit de desenvolvimento com FPGA pode descarregar e

testar o circuito, simulando a tabela-verdade, por meio do sinal de clock do kit como

entrada e quatro LEDs como as saídas do circuito. A Tabela 3.13 mostra a designação

dos pinos do FPGA.

Tabela 3.13 - Designação de pinos do FPGA.

Função

Pinos do FPGA

Descrição

Entrada Clkin

Pino_N2

Sinal de Clock 50

MHz

Saída Q0

Pino_AE23

LED_VERM_0

Saída Q1

Pino_AF32

LED_VERM_1

Saída Q2

Pino_AB21

LRD_VERM_2

Saída Q3

Pino_AC22

LED_VERM_3

Solução

1.

Crie o projeto contador_binário_1.

2.

3.

4.

5.

Crie o arquivo contador_binario_1.bdf.

Insira os componentes lógicos JKFF, AND2 e AND3, o terminal de entra-da de

clock e os terminais de saídas do circuito.

Interligue os componentes lógicos do circuito, o terminal de entrada (input) e os

terminais de saídas (output).

Identifique o nome do terminal Clkin para a entrada e Q0, Q1, Q2 e Q3 para as

saídas.

A Figura 3.26 exibe os componentes lógicos, o terminal de entrada e as saídas

interligadas e identificadas.

Figura 3.26 - Circuito contador_binario_1 interligado com os terminais de E/S identificados.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

16.

17.

Compile e salve o projeto para verificar a existência de erros.

Se o compilador acusar algum erro, verifique as mensagens de erros, na parte

inferior da janela, corrija os erros e compile novamente.

Faça a simulação do funcionamento do circuito.

Escolha a simulação funcional.

Escolha o arquivo Vector waveform.

Insira a entrada Clkin e as saídas Q0, Q1, Q2 e Q3 no Editor de Formas de

Ondas.

Altere a propriedade da entrada para binário.

Selecione o tipo de estímulo para a entrada Clkin.

Selecione Count value (gerador de onda quadrada) para a entrada Clkin.

Teste o arquivo de sinais de estímulos criado.

Salve o arquivo contador_binario_1.vwf.

Inicie a simulação.

O projeto é compilado e simulado. Se a compilação ocorrer sem nenhum erro, o

resultado da simulação, saídas Q0, Q1, Q2 e Q3, em função da entrada Clkin, é

igual ao apresentado na Figura 3.27.

Figura 3.27 - Resultado da simulação do arquivo contador_binario_1.

O circuito contador síncrono de 4 bits opera da mesma forma que o contador

assíncrono de 4 bits:

1.

Contador binário síncrono de 4 bits

A Tabela 3.14 mostra a tabela de estados do contador binário síncrono de 4

bits conforme apresentado no diagrama de forma de ondas da Figura 3.27.

Tabela 3.14 - Estados dos flip-flops do contador binário síncrono de 4 bits.

2.

23

22

21

20

Q3

Q2

Q1

Q0

Seqüência de contagem binária

0

0

0

0

Antes do pulso de Clkin

0

0

0

1

Após o pulso nº 1

0

0

1

0

Após o pulso nº 2

0

0

1

1

Após o pulso nº 3

0

1

0

0

Após o pulso nº 4

0

1

0

1

Após o pulso nº 5

0

1

1

0

Após o pulso nº 6

0

1

1

1

Após o pulso nº 7

1

0

0

0

Após o pulso nº 8

1

0

0

1

Após o pulso nº 9

1

0

1

0

Após o pulso nº 10

1

0

1

1

Após o pulso nº 11

1

1

0

0

Após o pulso nº 12

1

1

0

1

Após o pulso nº 13

1

1

1

0

Após o pulso nº 14

1

1

1

1

Após o pulso nº 15

0

0

0

0

Após o pulso nº 16 retorna para 0000

Divisor de freqüência módulo 16

O flip-flop Q0 muda de estado na transição positiva de cada pulso da entrada

Clkin. A saída Q0 tem a freqüência igual à metade da freqüência da entrada

Clkin.

O flip-flop Q1 muda de estado na transição positiva de cada pulso da entrada

Clkin. A saída Q1 tem a freqüência igual à metade da freqüência da entrada

Q0.

O flip-flop Q2 muda de estado na transição positiva de cada pulso da entrada

Clkin. A saída Q2 tem a freqüência igual à metade da freqüência da entrada

Q1.

O flip-flop Q3 muda de estado na transição positiva de cada pulso da entrada

Clkin. A saída Q3 tem a freqüência igual à metade da freqüência da entrada

Q2.

Cada flip-flop divide a freqüência do sinal de sua entrada por 2. Assim, o

último flip-flop tem uma freqüência igual a 1/16 da frequência da entrada

Clkin.

Para simular o circuito no kit de FPGA, os nomes dos terminais de entradas e

saídas do circuito projetado devem ser associados com os pinos do FPGA utilizado,

conforme a Tabela 3.13.