EAPS - Curso de Engenharia Electrónica e de Computadores

44––Conversão

ConversãoAnalógica/Digital

Analógica/Digital

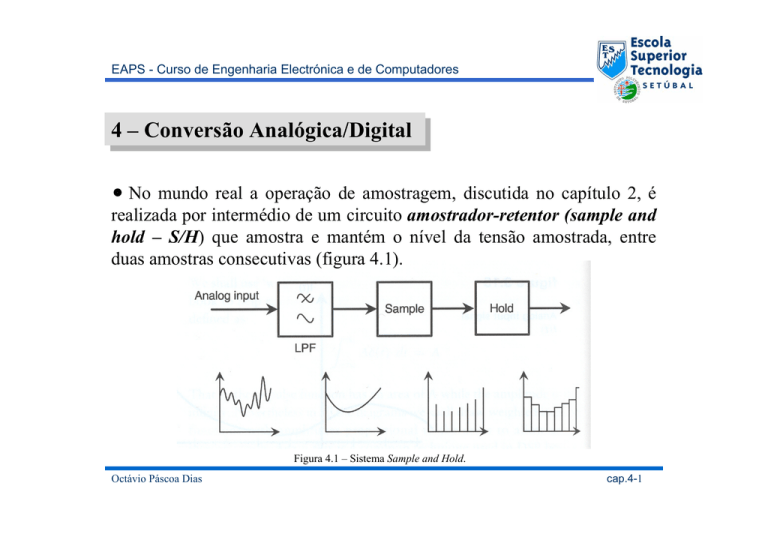

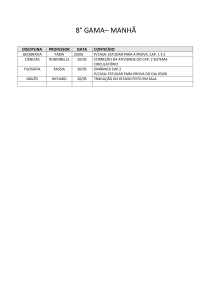

No mundo real a operação de amostragem, discutida no capítulo 2, é

realizada por intermédio de um circuito amostrador-retentor (sample and

hold – S/H) que amostra e mantém o nível da tensão amostrada, entre

duas amostras consecutivas (figura 4.1).

n

Figura 4.1 – Sistema Sample and Hold.

Octávio Páscoa Dias

cap.4-1

EAPS - Curso de Engenharia Electrónica e de Computadores

44––Conversão

ConversãoAnalógica/Digital

Analógica/Digital(cont.)

(cont.)

Da operação de amostragem resulta um sinal em degrau, com a forma

típica ilustrada na figura 4.2.

n

A etapa que se segue à amostragem, consiste em quantificar os valores

das amostras do sinal analógico. A operação de quantificação é realizada

por um conversor analógico para digital (analog to digital converter –

ADC).

V

n

Figura 4.2 – Sinal em degrau na saída do Sample and Hold.

Octávio Páscoa Dias

cap.4-2

EAPS - Curso de Engenharia Electrónica e de Computadores

44––Conversão

ConversãoAnalógica/Digital

Analógica/Digital(cont.)

(cont.)

A quantificação pode ser interpretada como uma classificação das

amostras do sinal, relativamente a níveis de tensão pré-determinados. Por

exemplo, para classificar as amostras da figura 4.2 em dois grupos, pode

escolher-se um nível “a” como se mostra na figura 4.3.

n

V

Figura 4.3 – Quantificação das amostras relativamente a 1 nível.

Octávio Páscoa Dias

cap.4-3

EAPS - Curso de Engenharia Electrónica e de Computadores

44––Conversão

ConversãoAnalógica/Digital

Analógica/Digital(cont.)

(cont.)

Assim, todas amostras acima ou iguais ao nível “a” pertencem, por

hipótese, ao “grupo 1”, e aquelas cujos valores se encontram abaixo do

nível “a” pertencem ao “grupo 0”. Com base neste critério, as amostras

geram a sequência de zeros (0s) e uns (1s), ilustrada na figura 4.4, que

constitui um exemplo da quantificação das amostras utilizando um único

bit.

V

Figura 4.4 – Quantificação com 1 bit.

Octávio Páscoa Dias

cap.4-4

EAPS - Curso de Engenharia Electrónica e de Computadores

44––Conversão

ConversãoAnalógica/Digital

Analógica/Digital(cont.)

(cont.)

Se forem usados dois bits para quantificar as amostras do sinal

analógico, são definidos quatro níveis de tensão, que podem ser

igualmente espaçados, para quantificar os valores das amostras (figura

4.5). O sinal pode assim, ser quantificado em quatro grupos (00, 01, 10,

11), como se mostra na figura 4.6.

n

V

Figura 4.5 – Quantificação com quatro níveis.

Octávio Páscoa Dias

V

Figura 4.6 – Quantificação com 2 bits.

cap.4-5

EAPS - Curso de Engenharia Electrónica e de Computadores

44––Conversão

ConversãoAnalógica/Digital

Analógica/Digital(cont.)

(cont.)

Dos exemplos apresentados pode concluir-se que quanto maior for o

número de níveis usados na quantificação, maior é a precisão com que é

descrito o sinal analógico, isto é, mais precisa é a conversão A/D. Deste

modo, se forem usados ADCs de 10 bits ou de 12 bits, as amostras podem

ser quantificadas em 210 (1024) ou 212 (4096) níveis.

n

nAssim,

para um sinal analógico que varie entre 0 e 5 volts o bit menos

significativo (least significant bit - LSB), ou seja, um único bit,

corresponde a 4,88 mV para um ADC de 10 bits, e a 1,22 mV para um

ADC de 12 bits, uma vez que,

5

5

= 4,88 mV , e

= 1,22 mV

1024

4096

Octávio Páscoa Dias

cap.4-6

EAPS - Curso de Engenharia Electrónica e de Computadores

44––Conversão

ConversãoAnalógica/Digital

Analógica/Digital(cont.)

(cont.)

Comparando os níveis quantificados com o sinal analógico original,

pode avaliar-se o erro introduzido pela conversão A/D (figura 4.7). Estes

erros produzem um efeito designado por ruído de quantificação.

n

V

Figura 4.7 – Erro de quantificação.

Octávio Páscoa Dias

cap.4-7

EAPS - Curso de Engenharia Electrónica e de Computadores

44––Conversão

ConversãoAnalógica/Digital

Analógica/Digital(cont.)

(cont.)

Os exemplos referidos até agora, relacionam-se com a quantificação

uniforme, assim designada pelo facto dos níveis estarem igualmente

espaçados (figura 4.8).

n

Figura 5.8 – Quantificação uniforme.

Octávio Páscoa Dias

cap.4-8

EAPS - Curso de Engenharia Electrónica e de Computadores

44––Conversão

ConversãoAnalógica/Digital

Analógica/Digital(cont.)

(cont.)

Porém, nem sempre, a utilização da quantificação uniforme conduz aos

melhores resultados para a conversão A/D. De facto, por exemplo na

língua inglesa, numa conversação, existem sons tipicamente de maior

amplitude, por exemplo as vogais, e outros de muito menor amplitude,

como as consoantes. Na figura 4.9 apresenta-se a forma de onda típica de

uma conversação.

n

Figura 4.9 – Forma de onda típica de uma conversação.

Octávio Páscoa Dias

cap.4-9

EAPS - Curso de Engenharia Electrónica e de Computadores

55––Conversão

ConversãoAnalógica/Digital

Analógica/Digital(cont.)

(cont.)

Para o exemplo da figura 5.10, a quantificação uniforme (figura 4.11)

pode assegurar uma representação adequada para as amplitudes elevadas,

mas revela-se inadequada para as amplitudes mais reduzidas que

acabariam por ser quantificadas num mesmo nível, isto é, representadas

pelo mesmo valor binário.

n

Figura 5.10 – Forma de onda típica de um discurso.

Octávio Páscoa Dias

Figura 5.11 – Quantificação uniforme de um discurso.

cap.4-10

EAPS - Curso de Engenharia Electrónica e de Computadores

44––Conversão

ConversãoAnalógica/Digital

Analógica/Digital(cont.)

(cont.)

Isto significa que uma quantificação que codifique diferentemente as

componentes de maior amplitude e as de menor amplitude de um mesmo

sinal conduz a uma melhor qualidade do sinal obtido à saída da cadeia de

processamento. Para sinais com as características do que se representa na

figura 4.12, a quantificação não-uniforme (figura 4.13) pode constituir

uma solução possível.

n

Figura 4.12 – Amplitude das componentes de um discurso típico

Octávio Páscoa Dias

Figura 4.13 – Quantificação não-uniforme do discurso.

cap.4-11

EAPS - Curso de Engenharia Electrónica e de Computadores

44––Conversão

ConversãoAnalógica/Digital

Analógica/Digital(cont.)

(cont.)

Na prática é usual a utilização da quantificação uniforme acompanhada

pela compressão das componentes do sinal com maior amplitude,

deixando quase inalteradas as componentes de amplitudes mais reduzidas.

n

O resultado final é semelhante ao da quantificação não-uniforme. Após

o processamento, o sinal é restaurado à saída usando a descompressão das

componentes do sinal previamente comprimidas.

n

Este processo de compressão e de descompressão é designado por

companding (COMpressing and exPANDING).

n

Octávio Páscoa Dias

cap.4-12

EAPS - Curso de Engenharia Electrónica e de Computadores

4.1

4.1––Tipos

Tiposde

deADCs

ADCs

Existem diversos tipos de ADCs disponíveis no mercado, contendo

alguns deles o S/H já incluído no circuito intrgrado. Em seguida é feita a

descrição do princípio de funcionamento de alguns dos tipos ADC mais

populares.

n

ADC

ADCFlash

Flash

n O método flash utilitiza circuitos comparadores que realizam a

comparação das tensões de referência com o sinal analógico de entrada.

Quando a tensão analógica excede a tensão de referência num dado

comparador a saída desse comparador assume o valor “alto”.

A figura 4.14 mostra um conversor AD flash de 3 bits, que utiliza sete

circuitos comparadores para realizar a conversão.

n

Octávio Páscoa Dias

cap.4-13

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCFlash

Flash(cont.)

(cont.)

Figura 4.14 – Conversor AD flash de 3 bits.

Octávio Páscoa Dias

cap.4-14

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCFlash

Flash(cont.)

(cont.)

Este tipo de conversor não necessita de comparador para detectar a

tensão analógica que corresponde ao zero, uma vez que nessa situação

todos os sete comparadores têm a saída a zero, sendo portanto suficientes

para interpretar o nível zero da tensão analógica na entrada. Do mesmo

modo, um ADC flash de 4 bits necessita de 15 circuitos comparadores.

Seguindo este raciocínio, pode concluir-se que os conversores de

analógico para digital do tipo flash (ADC flash) necessitam de 2n-1

comparadores para realizarem a conversão A/D com um código binário de

n- bits.

n

A tensão de referência para cada comparador é fixada por um divisor de

tensão. A saída de cada comparador é ligada à entrada de um codificador

com prioridade (priority encoder).

n

Octávio Páscoa Dias

cap.4-15

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCFlash

Flash(cont.)

(cont.)

As tensões analógicas na entrada do codificador são amostradas por

intermédio de um impulso de relógio aplicado na entrada enable do

codificador, e um código de n-bits representa o valor do sinal analógico

presente na saída dos comparadores. A palavra binária correspondente à

tensão codificada é determinada pelo nível “alto” de maior ordem na

entrada da coluna de comparadores.

n

O ritmo do sinal de relógio que amostra o sinal analógico determina a

precisão com que a sequência de palavras digitais representam a entrada

analógica do ADC. De facto, quanto maior for o número de amostras

tomadas do sinal analógico, maior é a precisão com que o sinal analógico

é representado na forma digital.

n

Octávio Páscoa Dias

cap.4-16

EAPS - Curso de Engenharia Electrónica e de Computadores

Exemplo 4.1

Determine as palavras binárias de 3 bits de saída do ADC flash, que representam cada uma das amostras

do sinal analógico, tomadas no flanco ascendente do impulso de relógio, como mostra a figura 4.15.

Figura 4.15 – Amostragem de um AD flash de 3 bits para o exemplo 4.1.

Octávio Páscoa Dias

cap.4-17

EAPS - Curso de Engenharia Electrónica e de Computadores

Solução:

Figura 4.16 – Codificação do conversor AD flash do exemplo 4.1.

Octávio Páscoa Dias

cap.4-18

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deAproximações

AproximaçõesSucessivas

Sucessivas

O ADC de aproximações sucessivas produz um código binário de n-bits

por intermédio da comparação do sinal de entrada, xs(t), com a saída de

um conversor digital-analógico (digital to analog converter – DAC). A

figura 4.17 mostra o diagrama básico de blocos de um ADC de

aproximações sucessivas, de 4 bits. O diagrama é constituído por um

DAC, um registo de aproximações sucessivas (sucessive aproximationregister – SAR) e por um comparador.

n

n

A operação básica deste tipo de ADC é a seguinte:

Os bits de entrada do DAC são sequencialmente colocados a “1”,

começando pelo bit de maior peso (most significant bit - MSB). De cada

vez que um bit é colocado a “1” a saída do comparador indica se a entrada

analógica é maior ou menor do que a saída do DAC.

Octávio Páscoa Dias

cap.4-19

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deAproximações

AproximaçõesSucessivas

Sucessivas(cont.)

(cont.)

Se a tensão produzida pelo DAC é maior do que o valor do sinal

analógico, a saída do comparador coloca a “0” o último bit da entrada do

DAC que assumiu o valor “1”. Se a saída do DAC é inferior ao sinal

analógico, então o último bit do DAC colocado a “1” é mantido naquele

valor. Estes procedimentos repetem-se para cada bit de entrada do DAC,

começando pelo MSB, em seguida o próximo bit mais significativo e

assim por diante, até ao bit de menor peso (least significante bit – LSB).

Para ilustrar o modo de operação do ADC de aproximações sucessivas,

considere-se o exemplo de uma conversão de 4 bits, que a figura 4.18,

mostra passo-a-passo.

n

Octávio Páscoa Dias

cap.4-20

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deAproximações

AproximaçõesSucessivas

Sucessivas(cont.)

(cont.)

Neste exemplo, considera-se a conversão de uma tensão analógica de 5,1 V.

A conversão é realizada por intermédio de um ADC de aproximações

sucessivas, de quatro bits, com as seguintes características: VO=8 V para o

bit 23 (MSB), VO= 4 V para o bit 22, VO=2 V para o bit 21 e VO=1 V para o

bit 20 (LSB).

A figura 4.18 (a) mostra o primeiro passo do ciclo de conversão com o MSB

igual a 1. Nesta situação a saída do DAC é de 8 V. Como a saída do DAC é

maior do que o sinal analógico (5,1 V), então a saída do comparador coloca

o MSB do SAR a “0”;

Octávio Páscoa Dias

cap.4-21

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deAproximações

AproximaçõesSucessivas

Sucessivas(cont.)

(cont.)

A figura 4.18 (b) ilustra o segundo passo do ciclo de conversão com o bit 22

colocado a “1”. Assim, o valor da saída do DAC é de 4 V, que sendo inferior

a 5,1 V (tensão analógica), faz com que a saída do comparador retenha este

bit no valor “1”;

A figura 4.18 (c) representa o terceiro passo da conversão com o bit 21 igual

a “1”. A saída do DAC tem agora o valor de 6 V, uma vez que os bits 22 e 21

estão colocados a “1” o que conduz a 4+2=6 V. Como a saída do DAC é

superior ao valor do sinal analógico, a saída do comparador fixa em “0” o

bit 21;

A figura 4.18 (d) mostra o quarto passo, último para a conversão de quatro

bits, com o bit 20 colocado a “1”. A saída do DAC é de 5 V uma vez que os

bits 22 e 20 têm o valor “1”; logo: 4+1=5 V.

Octávio Páscoa Dias

cap.4-22

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deAproximações

AproximaçõesSucessivas

Sucessivas(cont.)

(cont.)

Após os quatro bits terem sido testados o ciclo de conversão fica

completo, e assim, o sinal analógico foi codificado com a palavra binária

0101, que corresponde, aproximadamente, ao valor da entrada analógica,

que é de 5,1 V.

n

O fim de um ciclo de conversão, determina o inicio de outro, com a

repetição do processo básico acabado de descrever.

n

n

No início de cada ciclo de conversão o SAR é colocado a zero.

Quanto maior for o número de bits do DAC maior será a precisão da

conversão.

n

Octávio Páscoa Dias

cap.4-23

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deAproximações

AproximaçõesSucessivas

Sucessivas(cont.)

(cont.)

Figura 4.17 – Diagrama de blocos do ADC de Aproximações Sucessivas.

Octávio Páscoa Dias

cap.4-24

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deAproximações

AproximaçõesSucessivas

Sucessivas(cont.)

(cont.)

Figura 4.18 – Conversão AD segundo o método de aproximações sucessivas.

Octávio Páscoa Dias

cap.4-25

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaSimples

Simples

O ADC de rampa simples utiliza um gerador de rampa linear para

produzir uma tensão de referência em rampa com declive constante. A

figura 4.19 representa o diagrama de blocos deste tipo de ADC.

n

No início do ciclo de conversão o contador está colocado a “0” e a

saída do gerador de rampa tem o valor de 0 V. Nesta situação, a entrada

analógica é superior à tensão de referência (saída do gerador de rampa), o

que faz com que a saída do comparador se encontre na saturação positiva

(L+), o que permite a operação do contador e do gerador de rampa. A

tensão em rampa crescerá até que o seu valor iguale a tensão analógica de

entrada. Neste ponto, a saída do comparador comuta para a saturação

negativa (L-), fazendo com que a rampa seja colocada a zero ( reset da

rampa), e o código correspondente ao valor da tensão analógica seja

armazenado nos registos.

n

Octávio Páscoa Dias

cap.4-26

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaSimples

Simples(cont.)

(cont.)

Assuma-se que o declive da rampa é de 1V/ms e que a tensão analógica

de entrada tem o valor de 2 V no instante da comutação da saída do

comparador. Nestas condições, a tensão da rampa tem o valor de 2 V e o

gerador funcionou durante 2 ms, dado que o declive da rampa é de 1 V/ms.

n

Assumindo que a frequência do relógio é de 100 kHz, foram contados

200 impulsos no intervalo de tempo de 2 ms. Deste modo, no instante em

que a tensão da rampa igualou a entrada analógica, o número binário do

contador corresponde ao número decimal 200, que pode ser apresentado

num display na forma 2.00.

n

Alguns tipos de voltímetros digitais usam este princípio de conversão

A/D.

n

Octávio Páscoa Dias

cap.4-27

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaSimples

Simples(cont.)

(cont.)

Figura 4.19 – Diagrama de blocos do ADC de Rampa Simples.

Octávio Páscoa Dias

cap.4-28

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla

A figura 4.20 mostra o diagrama de princípio de operação de um

conversor A/D de rampa dupla. Este tipo de conversor, embora lento,

apresenta uma resolução elevada (12 a 14 bits).

Figura 4.20 – Diagrama de principio de funcionamento do conversor A/D de Rampa Dupla.

Octávio Páscoa Dias

cap.4-29

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

O principio de operação do conversor A/D de rampa dupla usa a

quantidade de carga armazenada por um condensador durante um

intervalo de tempo fixo, mas com o declive do regime de carga variável, e

a respectiva descarga, feita durante um tempo variável mas com o declive

do regime de descarga constante.

O condensador inicia a carga a partir de zero e carrega durante o tempo

fixo T1 (figura 4.21) ligado à tensão analógica, vA a converter para a forma

digital. Terminado o intervalo de tempo T1 o condensador é ligado a uma

tensão fixa, Vref, e descarrega até atingir de novo os 0 Volts. O tempo de

descarga é contado por um contador digital, cujo valor final da contagem é

proporcional à tensão vA.

Octávio Páscoa Dias

cap.4-30

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

Para analisar, com pormenor, o seu modo de operação assuma-se que a

tensão analógica de entrada, vA, é negativa. Antes de iniciar o ciclo de

conversão o interruptor S2 deve fechar para descarregar o condensador C e

fazer v1=0. O ciclo de conversão inicia-se com a abertura de S2 e o fecho

do interruptor S1. O fecho de S1 coloca a tensão analógica, vA, na entrada

do integrador.

Dado que se assumiu que vA é negativa, então esta tensão dá origem a uma

corrente I=vA/R, com o sentido integrador → S1.

Tendo em conta que, Q=CV=It, então, V=(I/C)t. Deste modo, a tensão v1

cresce linearmente com o declive,

I

m1 =

C

Octávio Páscoa Dias

cap.4-31

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

e como,

obtém-se,

vA

I=

R

m1 =

vA

RC

como se ilustra na figura 4.21.

Em simultâneo a lógica fica configurada para permitir que o contador

inicie a contagem dos impulsos fornecidos pelo relógio (clock). Esta fase

de conversão (Fase I) continua durante o tempo fixo, T1, e termina quando

o contador atinge o valor de uma contagem pré-fixada, nref.

Usualmente, para um ADC de N bits, tem-se nref=2N.

Octávio Páscoa Dias

cap.4-32

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

(m1 )

(V p )

(m2 )

Figura 4.21 – Método de conversão A/D com rampa dupla.

Octávio Páscoa Dias

cap.4-33

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

Designando por Vp o valor de pico da tensão, v1, presente na saída do

integrador, pode escrever-se,

vA Vp

m1 =

=

RC T1

uma vez que o valor de Vp é alcançado no final de T1 (figura 5.21).

No final da Fase I (final de T1), o contador é colocado a zero (reset).

A Fase II da conversão inicia-se no instante t=T1. Nesse instante o

interruptor S1 liga a tensão positiva de referência, Vref, à entrada do

integrador. Assim, a corrente no integrador inverte de sentido, passando a

fluir no sentido S1→ integrador. Esta corrente é agora calculada pela

expressão, I=Vref /R.

Octávio Páscoa Dias

cap.4-34

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

Recordando de novo que a carga no condensador é dada por, Q=CV=It, o

que implica a igualdade, V=(I/C)t. Deste modo, a tensão v1 decresce

linearmente com o declive,

I

m2 =

C

e dado que,

I=

Vref

então,

m2 =

R

Vref

RC

como se mostra na figura 4.21.

Octávio Páscoa Dias

cap.4-35

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

Simultaneamente a lógica de controlo permite que o contador inicíe a

contagem dos impulsos fornecidos pelo clock. Quando a tensão na saída

do integrador atinge o valor v1=0 V, a saída do comparador faz parar a

contagem do contador.

Designando por T2, o tempo de duração da Fase II pode escrever-se

(figura 4.21),

m2 =

Vp

T2

=

Vref

RC

Da equação,

vA Vp

m1 =

=

RC T1

Octávio Páscoa Dias

cap.4-36

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

Conclui-se que,

vA

V p = T1

RC

E da equação,

m2 =

Vp

T2

Retira-se a conclusão de que,

V p = T2

logo,

=

Vref

RC

Vref

RC

Vref

v

vA

= T2

⇔ T1v A = T2Vref ⇒ T2 = T1 A

T1

RC

RC

Vref

Octávio Páscoa Dias

cap.4-37

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

Uma vez que a leitura, nref, do contador no final de T1 é proporcional a T1,

nref = f clk T1

onde fclk é a frequência do relógio (clock).

E a leitura n, no final de T2, é proporcional a T2,

então,

logo,

Octávio Páscoa Dias

n = f clk T2

nref v A

vA

n = f clk T1

⇔ n = f clk

Vref

f clk Vref

n = nref

vA

Vref

cap.4-38

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

Assim, a contagem no final do processo de conversão (final de T2) é o

equivalente digital de vA.

O ADC de dupla rampa apresenta uma precisão elevada, dado que o ceu

comportamento é independente de R e de C.

Embora, de algum modo, constitua uma repetição do que atrás foi

descrito, por se considerar um bom exercício para a assimilação do

funcionamento deste tipo de ADCs, mostram-se, nas figura 4.22 a 4.25, as

principais etapas da operação de um conversor AD, no qual se assume que

a tensão de entrada, Vin, é positiva, e, por consequência, com a tensão de

referência, Vref, negativa.

Octávio Páscoa Dias

cap.4-39

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

No início da conversão o contador e o integrador (gerador da rampa), A1,

estão colocados a “0”. A tensão analógica é aplicada à entrada do

comutador, SW, que é actuado pela lógica de controlo.

Dado que na entrada inversora de A1 está presente uma massa virtual, e

assumindo que a tensão de analógica de entrada, Vin, é constante durante

um dado intervalo de tempo, então a corrente através da resistência R, é

constante, e assim, a corrente que no condensador é também constante.

O condensador, C, carrega linearmente, uma vez que a corrente de carga

é constante, e assim, a saída de A1 produz uma rampa linear de tensão com

declive negativo (figura 4.22), que é proporcional à corrente de carga, a

qual, por sua vez, é proporcional à tensão Vin.

Octávio Páscoa Dias

cap.4-40

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

O contador é colocado a zero quando atinge um valor pré-fixado de

contagem, e a lógica de controlo comuta SW, fazendo com que a tensão de

referência –Vref. seja aplicada à entrada de A1 (figura 4.24). Nesta situação o

condensador descarrega linearmente devido à corrente constante fornecida

por –Vref. Esta descarga linear, produz uma rampa de tensão com declive

positivo (figura 4.25) na saída de A1, com o valor inicial de –V. O declive da

descarga depende de –Vref, sendo independente do valor de –V.

No final da carga de C, o contador é colocado a “0”. Durante a descarga do

condensador o contador incrementa a contagem até a descarga se completar.

O tempo que o condensador leva a completar a sua descarga, depende do

valor inicial da tensão –V, o qual é proporcional a Vin, dado que o declive da

característica de descarga é constante.

Octávio Páscoa Dias

cap.4-41

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

Quando a tensão de saída do integrador A1 atinge o valor 0 V, o

comparador A2 comuta para L-, o que faz com que o contador cesse a

contagem.

A palavra binária produzida pelo contador é proporcional a Vin, uma vez

que o tempo que o condensador leva a descarregar depende apenas do

valor inicial, -V, o qual depende de Vin, e o contador incrementa a

contagem (a partir de “0”) durante o tempo da descarga de C.

O ciclo de conversão termina com o armazenamento da palavra binária

nos registos.

Octávio Páscoa Dias

cap.4-42

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

Figura 4.22 –Diagrama de blocos do ADC de Rampa Dupla.

Octávio Páscoa Dias

cap.4-43

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

Figura 4.23 – ADC de Rampa Dupla. Etapa1: carga do condensador (intervalo de tempo fixo e rampa variável).

Octávio Páscoa Dias

cap.4-44

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

Figura 4.24 – ADC de Rampa Dupla. Etapa2: fim do intervalo de tempo fixo e comutação para –Vref.

Octávio Páscoa Dias

cap.4-45

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

RampaDupla

Dupla(cont.)

(cont.)

Figura 4.25 – ADC de Rampa Dupla. Etapa3: descarga do condensador (intervalo de tempo variável e rampa fixa).

Octávio Páscoa Dias

cap.4-46

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

Rampaem

emDegrau

Degrau

A figura 4.26 mostra o diagrama de blocos do método de conversão

A/D por rampa em degrau ou rampa digital.

n

No início do ciclo de conversão o contador e o DAC estão colocados a

zero. Quando a tensão analógica de entrada excede a tensão de referência

(saída do DAC) o comparador comuta para L+, permitindo que os

impulsos de relógio passem pela gate AND e activem o contador. A acção

de contagem gera a tensão de rampa em degrau (tensão de referência).

n

O contador incrementa a contagem até a tensão de referência alcançar a

tensão analógica. Nesta situação, o comparador comuta para L-, o que

bloqueia os impulsos de relógio na gate AND, e pára a contagem do

contador.

n

Octávio Páscoa Dias

cap.4-47

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

Rampaem

emDegrau

Degrau(cont.)

(cont.)

No ponto em que o contador cessa a contagem, a palavra binária é igual

ao número de degraus da tensão de referência, que foram necessários para

alcançar a tensão analógica de entrada. Assim, o valor binário do contador

corresponde ao valor analógico da entrada. A lógica de controlo carrega a

palavra binária nos registos e faz o reset do contador, preparando-o para o

início de novo ciclo de conversão.

A figura 4.27 ilustra uma conversão de 4 bits, sendo de realçar que, para

cada amostra, o contador tem de incrementar a sua contagem a partir de

“0” até ao ponto em que em que a tensão de referência alcança o valor da

tensão analógica.

O tempo de conversão varia com o valor da amostra a converter para a

representação binária.

Octávio Páscoa Dias

cap.4-48

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

Rampaem

emDegrau

Degrau(cont.)

(cont.)

Figura 4.26 – ADC de Rampa em Degrau.

Octávio Páscoa Dias

cap.4-49

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCde

deRampa

Rampaem

emDegrau

Degrau(cont.)

(cont.)

Figura 4.27 – Conversão de 4 bits pelo método da rampa em degrau.

Octávio Páscoa Dias

cap.4-50

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCTracking

Tracking

O método tracking usa um contador up/down. Este tipo de conversor A/D

é mais rápido que o método de rampa em degrau, uma vez que não é feito

o reset ao contador no final de cada conversão. De facto, este método

consiste em fazer com que a tensão de referência atinja rapidamente o

valor da tensão analógica.

A figura 4.28 mostra o diagrama de princípio de funcionamento de um

ADC tracking (tracking counter ADC), que se processa com a seguir se

descreve.

Enquanto a tensão de referência, vr, for menor do que a tensão analógica

de entrada, va, a saída, vC, do comparador está no estado L+, fazendo com

que o contador incremente o valor da palavra binária (up mode).

Octávio Páscoa Dias

cap.4-51

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCTracking

Tracking(cont.)

(cont.)

va

vc

vr

⎧

⎪

⎪⎪

⎨

⎪

⎪

⎪⎩

Figura 4.28 – Diagrama de blocos de um ADC tracking (tracking counter ADC).

Octávio Páscoa Dias

cap.4-52

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCTracking

Tracking(cont.)

(cont.)

Deste modo, a tensão em degrau na saída, vr, do DAC aumenta até atingir

o valor de va. Quando vr alcança a tensão analógica, o comparador comuta

para o estado L-, fazendo com que o contador decremente uma contagem

(down mode).

Se a tensão analógica está a diminuir, então o contador continua a

decrementar até alcançar de novo a tensão de entrada.

Se a tensão de entrada está a aumentar, o contador após decrementar uma

contagem (por ter alcançado a tensão analógica), volta a incrementar o

valor da palavra digital até atingir o novo valor da tensão de entrada.

Se a tensão analógica é constante o contador decrementa uma contagem

quando alcança o valor da tensão de entrada.

Octávio Páscoa Dias

cap.4-53

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCTracking

Tracking(cont.)

(cont.)

A tensão de referência é agora inferior à entrada analógica, o comparador

comuta para L+, e o contador incrementa a contagem. Logo que a palavra

digital é incrementada, a tensão de referência fica superior à entrada

analógica e de novo o comparador comuta para L-, o que faz com que o

contador decremente uma contagem. Esta acção incrementa/decrementa

mantém-se enquanto a tensão analógica permanecer constante,

provocando a oscilação da saída entre dois estados binários. Este

comportamento constitui uma desvantagem deste tipo de conversão A/D.

A figura 4.29 mostra a acção de tracking deste modo de conversão, para

um ADC de 4 bits.

n

Octávio Páscoa Dias

cap.4-54

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCTracking

Tracking(cont.)

(cont.)

Figura 4.29 – Conversão por um ADC tracking de 4 bits.

Octávio Páscoa Dias

cap.4-55

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCpor

porRedistribuição

Redistribuiçãode

deCarga

Carga

A técnica de conversão AD por redistribuição de carga é particularmente

indicada para ser implementada por intermédio da tecnologia CMOS. A

figura 4.30, mostra o esquema eléctrico de princípio de operação deste

tipo de conversor, na qual, se pode identificar o conjunto de

condensadores ligados em paralelo, cujas capacidades têm ponderação

binária, um comparador de tensão, e os interruptores analógicos, os quais

são activados por um bloco de controlo lógico, que a figura não

representa.

O circuito da figura 4.30 ilustra um conversor de 5 bits, cujos pesos

binários são assegurados pela relação entre as capacidades dos

condensadores. De facto, cada uma das capacidades pode ser determinada

pela expressão,

− ( N −1)

Cbi = 2

Octávio Páscoa Dias

× C ; com i = 1, 2,......., N

cap.4-56

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCpor

porRedistribuição

Redistribuiçãode

deCarga

Carga(cont.)

(cont.)

onde Cbi é a capacidade do condensador que implementa o bit i e C é a

capacidade do condensador que implementa o peso do MSB. Deste modo,

para um conversor de 5 bits (figura 4.30), tem-se,

C

C

bit 1( LSB) ≡ C1 = 2 −(5−1) × C ⇒ C1 = 4 ⇒ C1 =

2

16

C

C

−( 5− 2 )

bit 2 ≡ C2 = 2

× C ⇒ C2 = 3 ⇒ C2 =

2

8

C

C

bit 3 ≡ C3 = 2 −(5−3) × C ⇒ C3 = 2 ⇒ C3 =

2

4

C

C

bit 4 ≡ C4 = 2 −(5− 4) × C ⇒ C4 = 1 ⇒ C3 =

2

2

C

bit 5( MSB) ≡ C5 = 2 −(5−5) × C ⇒ C4 = 0 ⇒ C3 = C

2

Octávio Páscoa Dias

cap.4-57

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCpor

porRedistribuição

Redistribuiçãode

deCarga

Carga(cont.)

(cont.)

bit4 C

2

bit5

(MSB) C

bit3 C

4

S5

bit2 C

8

2 − ( 5 −3 ) × C

2 − ( 5− 4 ) × C

2 − ( 5− 5 ) × C

S4

vO

bit1 C

(LSB ) 16

2 − (5−1) × C

2 − ( 5− 2 ) × C

S3

comparador

S2

S1

va

SA

Vref

Figura 5.30 – Valor dos condensadores de um conversor AD de 5 bits, por redistribuição de carga.

A contribuição de cada um dos bits para a tensão vO, que é aplicada à

entrada do comparador, pode ser determinada ligando o bit em teste à

tensão de referência Vref, e os restantes à massa.

Octávio Páscoa Dias

cap.4-58

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCpor

porRedistribuição

Redistribuiçãode

deCarga

Carga(cont.)

(cont.)

Assim, a contribuição de tensão do bit i para a tensão vO, pode ser

determinada por intermédio do circuito representado na figura 4.31, de

onde se conclui que,

∆VO b = Vref

i

Vref

N

Ci

Ci

⇒ ∆VO b = Vref

, com Ctotal = ∑ Ci

i

Ci + (Ctotal − Ci )

Ctotal

i =1

vO = ∆VO b

Ci

i

Ctotal − Ci

∆VO b

comparador

i

Figura 4.31 – Contribuição de bi para vO.

Octávio Páscoa Dias

cap.4-59

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCpor

porRedistribuição

Redistribuiçãode

deCarga

Carga(cont.)

(cont.)

A operação do conversor pode ser dividida em três fases distintas, que se

ilustram nas figuras 4.32, 4.33 e 4.34, sendo de realçar que o condensador

CT tem a função de terminar o paralelo dos condensadores ponderados,

fazendo com que a capacidade total, Ctotal, seja igual a 2C.

Na fase de amostragem (figura 4.32), o interruptor SB fecha para ligar à

massa o terminal superior dos condensadores o que faz com que a tensão

vO seja colocada a zero (vO=0 V). Em simultâneo o interruptor SA liga a

tensão analógica va ao terminal inferior do paralelo de condensadores,

fazendo com que a capacidade total de 2C fique com o valor que a tensão

va apresenta nesse instante, dando origem a uma carga armazenada

Q=2C×va. Deste modo, durante a fase de amostragem, é tomada uma

amostra de va sendo armazenada na bateria de condensadores uma carga

proporcional ao valor que a tensão analógica apresenta nesse instante.

Octávio Páscoa Dias

cap.4-60

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCpor

porRedistribuição

Redistribuiçãode

deCarga

Carga(cont.)

(cont.)

(MSB)

(LSB )

S5

S4

S3

S2

S1

Figura 4.32 – Operação do ADC por redistribuição de carga (Fase de Amostragem).

Octávio Páscoa Dias

cap.4-61

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCpor

porRedistribuição

Redistribuiçãode

deCarga

Carga(cont.)

(cont.)

Na fase de retenção (figura 4.33), o interruptor SB abre enquanto os

interruptores S1 (LSB) a S5 (MSB) e o interruptor ST comutam para o

terminal de massa. Assim, a carga adquirida pelos condensadores na fase

de amostragem, permanece constante e igual a 2CvA, uma vez que os

condensadores ficam em circuito aberto. Deste modo, o terminal superior

dos condensadores ficam com a tensão –vA.

É de realçar que durante esta fase, o interruptor SA é ligado à tensão de

referência, Vref, o que faz com que o circuito fique preparado para a fase

de distribuição de carga.

Octávio Páscoa Dias

cap.4-62

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCpor

porRedistribuição

Redistribuiçãode

deCarga

Carga(cont.)

(cont.)

(MSB)

S5

(LSB )

S4

S3

S2

S1

Figura 4.33 – Operação do ADC por redistribuição de carga (Fase de Retenção).

Octávio Páscoa Dias

cap.4-63

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCpor

porRedistribuição

Redistribuiçãode

deCarga

Carga(cont.)

(cont.)

A fase de distribuição de carga (figura 4.34), é iniciada pela comutação

do bit mais significativo, S5 (MSB), para o terminal de Vref, o que faz com

o circuito fique configurado como um divisor de tensão capacitivo,

constituído pela tensão de referência, Vref, e pelo condensador C em série

com o paralelo dos restantes. Agora, se o módulo de va for maior do que

Vref/2 (contribuição do bit 5) a tensão vO negativa. Assim, comparador

permanece no mesmo estado e o interruptor S5 é deixado na sua nova

posição (ligado a Vref). Porém, se o módulo de va for inferior a Vref/2, a

tensão vO torna-se positiva o que faz com que o comparador mude de

estado, e faça com que a lógica de controlo comute S5 para aposição

anterior (ligado à massa).

Octávio Páscoa Dias

cap.4-64

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCpor

porRedistribuição

Redistribuiçãode

deCarga

Carga(cont.)

(cont.)

Em seguida é testado o bit 4, isto é, o interruptor S4 é ligado a Vref, o que

faz com que a tensão va sofra uma variação positiva igual a Vref/4

(contribuição do bit 4).

Se vO continuar negativa, S4 é deixado na sua nova posição. Se tal não

acontecer, ou seja, se vO se tornar positiva, S4 volta à posição anterior e a

lógica de controlo passa ao teste de S3, repetindo o mesmo procedimento

para todos os bits.

É de realçar que durante a fase de redistribuição de carga, o valor do

módulo da tensão, vO, vai diminuindo incrementalmente até zero. A

posição dos interruptores no final desta fase, fornece a palavra digital que

codifica a tensão analógica na entrada do conversor.

Octávio Páscoa Dias

cap.4-65

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCpor

porRedistribuição

Redistribuiçãode

deCarga

Carga(cont.)

(cont.)

De facto, um interruptor comutado para a massa, indica que o bit

correspondente é “0”, enquanto que, se o interruptor se encontrar ligado a

Vref , significa que o bit respectivo tem o valor “1”. No caso particular do

exemplo indicado na figura 4.34, a palavra digital é, D=0110.

Repare-se que no final da fase de redistribuição de carga, toda a carga se

encontra armazenada nos condensadores correspondentes aos bits

colocados a “1”, uma vez que os condensadores ligados aos bits

colocados a “0” foram descarregados, dado que o terminal inferior destes

condensadores tem a tensão zero (massa) e a tensão nos terminais

superiores de todos os condensadores é também nula (vO=0).

Octávio Páscoa Dias

cap.4-66

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCpor

porRedistribuição

Redistribuiçãode

deCarga

Carga(cont.)

(cont.)

A precisão deste método de conversão A/D é independente do valor das

capacidades parasitas ligadas às placas inferiores dos condensadores. De

facto, isto ocorre porque as placas inferiores são ligadas tanto a Vref como

à massa, o que faz com que as correstes de carga/descarga destas

capacidades parasitas não circulem pelo paralelo dos condensadores.

Porém, as capacidades parasitas associadas às placas superiores dos

condensadores podem provocar um desvio no valor final de vO, o que faz

com que este tipo de conversão seja utilizada em conversores A/D até 10

bits.

Octávio Páscoa Dias

cap.4-67

EAPS - Curso de Engenharia Electrónica e de Computadores

ADC

ADCpor

porRedistribuição

Redistribuiçãode

deCarga

Carga(cont.)

(cont.)

(MSB)

S5

S4

S3

S2

(LSB )

S1

Figura 4.34 – Operação do ADC por redistribuição de carga (Fase de Redistribuição).

Octávio Páscoa Dias

cap.4-68

EAPS - Curso de Engenharia Electrónica e de Computadores

4.2

4.2––Características

Característicasde

deDesempenho

Desempenhodos

dosConversores

ConversoresA/D

A/D

resolução

resolução

A resolução (resolution) de um conversor analógico/digital pode ser

caracterizada pelo seu número de bits ou pelo valor da cada degrau de

tensão em que a tensão analógica de entrada pode ser discritizada, sendo

determinada pela relação,

VFS

resolução = N

2 −1

onde N é o número de bits do ADC e VFS é o valor máximo da tensão que

pode ser aplicada ao conversor.

Como exemplo, um ADC de 10 bits com VFS=5 V, tem uma resolução de

5/(210-1)=4,88 mV, o que significa que a tensão de entrada deve variar

pelo menos 4,88 mV para que o ADC distinga o novo nível de tensão.

Octávio Páscoa Dias

cap.4-69

EAPS - Curso de Engenharia Electrónica e de Computadores

precisão

precisão

A precisão (accuracy) de um conversor analógico/digital avalia o desvio

entre o comportamento teórico e o comportamento real do ADC.

De facto, a precisão depende de diversos parâmetros que caracterizam o

desempenho do ADC nomeadamente (1) o erro de quantificação, (2) o erro

de desvio do zero (offset), (3) o erro do ganho e (4) as não-linearidades.

Usualmente a precisão de um ADC é especificada por uma fracção do LSB,

sendo, normalmente indicada como “melhor do que ± 1/2 LSB”.

Octávio Páscoa Dias

cap.4-70

EAPS - Curso de Engenharia Electrónica e de Computadores

erro

errode

dequantificação

quantificação

O erro de quantificação (quantization error) mede a diferença máxima

entre o nível usado para representar a tensão de entrada e o valor real dessa

tensão.

Por exemplo, se um conversor A/D tem os níveis de quantificação

separados por 1 V (figura 4.35), então o valor de tensão correspondente ao

LSB é também de 1 V. Assim, no caso da tensão analógica de entrada ter o

valor de 2,5 V, o código binário de saída será 1 0, que corresponde ao valor

2 na base 10. O erro cometido nesta quantificação será de 0,5 V= ½ LSB.

Se o valor da tensão de entrada pertencer ao intervalo 2,001 V e 3 V

(figura 4.36) a palavra binária de saída será também 1 0 ( 2 decimal).

Octávio Páscoa Dias

cap.4-71

EAPS - Curso de Engenharia Electrónica e de Computadores

erro

errode

dequantificação

quantificação

Deste modo, mesmo que o conversor tenha uma precisão perfeita, a

palavra de saída pode apresentar um erro de 1 V ou seja 1 LSB. De facto, o

erro de quantificação pode descrever melhor a precisão a esperar do ADC.

Figura 4.35 – Conversor paralelo de 4 bits.

Octávio Páscoa Dias

Figura 4.36 – Códigos binários do conversor paralelo de 4 bits.

cap.4-72

EAPS - Curso de Engenharia Electrónica e de Computadores

erro

errode

dedesvio

desviodo

dozero

zero

O erro de desvio do zero (offset error) mede o desvio entre a curva de

transferência ideal e a curva de transferência real, para o menor nível de

transição, de um ADC, (figura 4.37).

Figura 4.37 – Característica de saída com erro de desvio do zero.

Octávio Páscoa Dias

cap.4-73

EAPS - Curso de Engenharia Electrónica e de Computadores

erro

errode

deganho

ganho

O erro de ganho (gain error) mede a diferença entre os declives das

curvas de transferência ideal e real do ADC, para o valor máximo do

código binário (figura 4.38).

Figura 4.38 – Característica de saída com erro de desvio do zero.

Octávio Páscoa Dias

cap.4-74

EAPS - Curso de Engenharia Electrónica e de Computadores

não-linearidade

não-linearidadediferencial

diferencial

O erro de linearidade diferencial ou não-linearidade diferencial

(differential nonlinearity) descreve as variações na tensão analógica entre

pares de códigos adjacentes, em toda a gama das palavras digitais de

saída. Se a largura de cada degrau de transição é exactamente 1 LSB, o

erro de não-linearidade diferencial é nulo.

Uma não-linearidade diferencial menor do que ± 1LSB, garante que não

se perdem de códigos.

Por exemplo, se a transição entre códigos consecutivos é de 1LSB±1LSB,

o que corresponde um erro de linearidade diferencial de ±1LSB, existe a

possibilidade de se perderem códigos. No exemplo da figura 4.39 a saída

digital passa de 0011 para 0101 perdendo-se o código 0100.

Octávio Páscoa Dias

cap.4-75

EAPS - Curso de Engenharia Electrónica e de Computadores

não-linearidade

não-linearidadediferencial

diferencial(cont.)

(cont.)

DNL

1 LSB 1 LSB

Figura 4.39 – Característica de saída com não-linearidade diferencial.

Octávio Páscoa Dias

cap.4-76

EAPS - Curso de Engenharia Electrónica e de Computadores

não-linearidade

não-linearidadeintegral

integral

O erro de linearidade integral ou não-linearidade integral (integral

nonlinearity), é definido como a diferença máxima entre as curvas de

transferência ideal e real, do conversor A/D (figura 4.40)

INL

1 LSB

Figura 4.40 – Característica de saída com não-linearidade integral.

Octávio Páscoa Dias

cap.4-77

EAPS - Curso de Engenharia Electrónica e de Computadores

não-linearidade

não-linearidadeintegral

integral

A gama dinâmica (dynamic range – DR) de um conversor A/D é a razão

entre o nível mais elevado e o menor nível da quantificação digital. A DR

é usualmente expressa em decibeis (dB). Para um conversor de N bits temse,

n

DR = 20 log

2

N

⇒

DR

=

20

log

2

⇔ DR = 20 N log 2 ⇒ DR = 6,02 N

0

2

tempo

tempode

deconversão

conversão

O tempo de conversão (conversion time) de um ADC corresponde ao

tempo necessário para o conversor produzir o código na saída, que

corresponde à tensão analógica de entrada.

Em aplicações exigentes quanto à velocidade de conversão são usados

conversores paralelo (flash).

Octávio Páscoa Dias

cap.4-78

EAPS - Curso de Engenharia Electrónica e de Computadores

4.3

4.3––Erros

Errosassociados

associadosààvariação

variaçãodo

dosinal

sinal

Em aplicações que exigem uma conversão A/D muito rápida, pelo facto

do sinal analógico variar rapidamente, podem ocorrer erros graves na

conversão. De facto, como se ilustra na figura 4.41, se o valor do sinal

analógico variar significativamente durante o tempo de conversão, a

palavra digital de saída pode corresponder ao valor do sinal no início do

ciclo de conversão, no fim do ciclo de conversão ou qualquer outro valor

intermédio, dependendo do método de conversão utilizado.

Uma vez que o erro de tensão, ∆V, é função da rapidez da variação do

sinal, o erro das palavras digitais de saída é variável, sendo, por isso,

muito difíceis de corrigir.

Octávio Páscoa Dias

cap.4-79

EAPS - Curso de Engenharia Electrónica e de Computadores

4.3

4.3––Erros

Errosassociados

associadosààvariação

variaçãodo

dosinal

sinal(cont.)

(cont.)

Este tipo de erros pode ser eliminado ou significativamente reduzido, por

intermédio de um circuito de amostragem e retenção (sample and hold –

S/H). A figura 4.42, representa um exemplo simples, deste tipo de

circuitos, onde se pode identificar o interruptor analógico, implementado

por intermédio de um transístor MOS, e o respectivo condensador de

amostragem, que se destina à retenção do valor das amostras tomadas do

sinal analógico. O circuito S/H é estudado na próxima secção, e a análise

do interruptor analógico é desenvolvida no capítulo 5 deste texto.

Figura 4.41 – Variação de vi durante o tempo de conversão.

Octávio Páscoa Dias

Figura 4.42 – Circuito sample and hold.

cap.4-80