Cod. Disc:_________ TURMA: _______ GRUPO:_______

NOME:__________________________________________

Sistemas Digitais

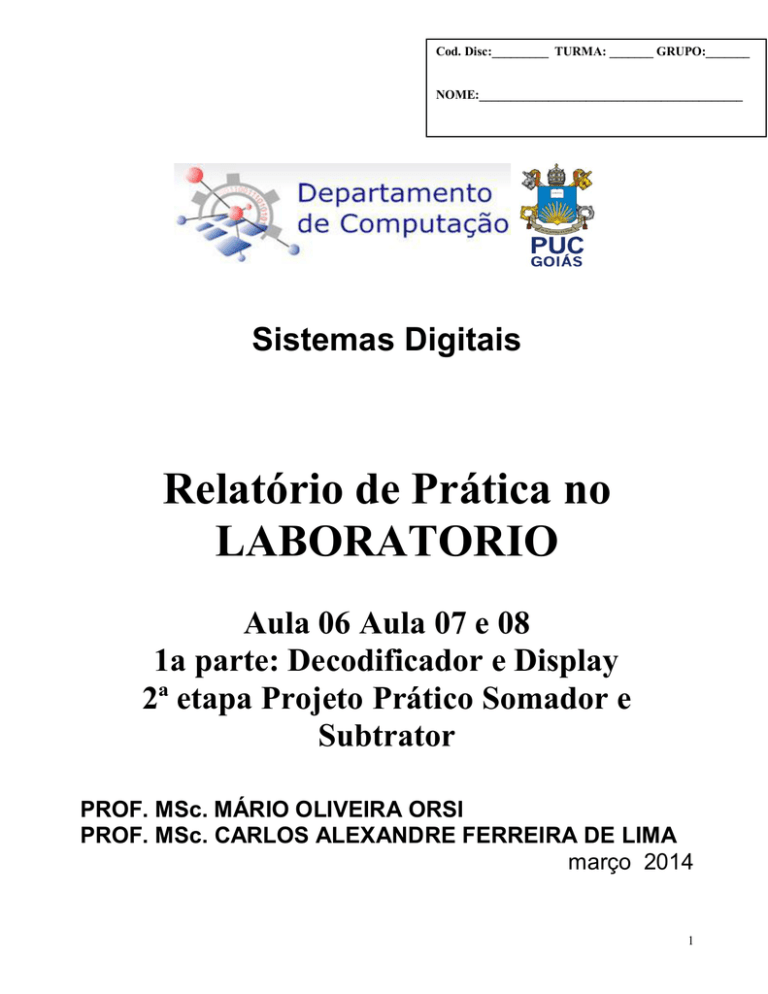

Relatório de Prática no

LABORATORIO

Aula 06 Aula 07 e 08

1a parte: Decodificador e Display

2ª etapa Projeto Prático Somador e

Subtrator

PROF. MSc. MÁRIO OLIVEIRA ORSI

PROF. MSc. CARLOS ALEXANDRE FERREIRA DE LIMA

março 2014

1

1. Projeto Final do Laboratório

Trata-se do projeto de uma calculadora BCD (Bynare Coded Decimal – Quatro bits

representam um algarismo decimal) sendo dividido para a implementação em oito partes

descritas abaixo e mostradas no diagrama de blocos funcionais Fig 1.

Projeto Final: Calculadora BCD

a

1 parte: Decodificador e Display

2a parte: Somador e Subtrator

3a parte: Correção BCD e Sinal

4a parte: Seletor

5a parte: Chaves sem Rebatimento – Pulso 1 e Pulso 2

6a parte: Contador BCD

7a parte: Gerador de Sinais de Controle

8a parte: Registrador A e B

O projeto deverá ser implementado por grupos de no máximo 5 alunos, observando

que o relatório é sempre individual.

SINAL

DISPLAY

I

DECODIFICADOR

SELETOR 3:1

MONITOR

SOMADOR /

SUBTRATOR BCD

REG B

REG A

GERADOR

DE SINAIS

DE

CONTRÔLE

MODO

+/PULSO 1

PULSO 2

CONTADOR BCD

Fig 1 – CALCULADORA BCD

2

AULA 6

Projeto final etapa 1 (Circuito Decodificador e Display)

Implementar o Decodificador e Display conforme figura 1.

1. Fundamentos Teóricos: conforme Referência Livro Texto: Capítulo 9.2

2. Projetos de decodificador BHEXA e BCD propostos nas aulas 10 e 11 da PRELEÇÃO

como AED.

EXPERIÊNCIA 1: Montar e Testar um decodificador BHEXA (CI 9863)

Objetivo: Considerando o funcionamento previsto no projeto do decodificador BHEXA, usar

o Ci 9368 do Modulo de teste, para testar o funcionamento do decodificador.

Procedimento experimental: Interligue 4 chaves em 4 leds do modulo de teste e Teste do

display e decodificador HEXA (CI 9368 catodo comum) do Modulo 8110, e preenchendo na

tabela verdade abaixo a coluna resultado e compare com os resultados previstos no

projeto (coluna previsto)

PREVISTO

CI

mod

BCD Hexa

CHAVES

RESULTADO

A

B

C

D

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

CI

MOD

.. .. .. ..

L3 L2 L1 L0

AA BB CC DD

0

1

0

1

1

A

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

0

1

B

0

SINAL

1

C

1

D

0

DISPLAY

0

fig 1

etapa 1

DECODIFICADOR

Decodificador

SELETOR 3:1

MONITORES

GERADORES

DOS SINAIS

DE

CONTROLE

SOMADOR /

SUBTRATOR

BCD

REG A

REG B

PULSOS 2

MODO

`+/-

1

1

1

0

1

1

1

1

PULSOS 1

CONTADOR BCD

3

EXPERIENCIA 2: Montar e testar o Decodificador BCD e Display de 7 seguimentos

Objetivo: Considerando o funcionamento previsto no projeto do decodificador BCD usar o

CI 7448 ou 7447 interligando-o ao display de 7 segmentos no Modulo do projeto final,

testar o funcionamento do decodificador e display (etapa 1 do projeto final)

Procedimentos experimentais

1. Montar no módulo do projeto final um dos Displays de 7 segmentos (layout abaixo):

CI 7448 display Catodo comum

Display acende com nível 1 (+5Vcc)

g

f

a

f a

b

b

f

CI 7447 display Anodo comum

Display acende com nível 0 (terra)

R

+5v

g f

a b

a

g

b

f a

g

e

e d

g

e

d

c

n/c

b

c

c

e

d

e d

d

c

n/c

c

Nunca ligar direto na fonte + 5V - Para testar os displays sem o usar um dos CIs monte o

fios de +5V (Vcc) e 0V (terra) no módulo com um resistor de 360 OHM.

2. Identifique no kit de montagem

do projeto final qual o

decodificador BCD (CI 7448 –

catodo comumalimentação

display TERRA, ou 7447 –

anodo

comumalimentação

display

1,5V)

que

esta

disponível, e monte o circuito

do esquema correspondente

fazendo a interligação do CI

ao display e um barramento

com as chaves

+

5

v

0 conectado 1 em aberto

4

3. Testar o circuito preenchendo com as figuras na tabela verdade abaixo a coluna

resultado CI e compare com os resultados previstos no projeto do CI (coluna

previsto)

PREVISTO

CI

mod

BCD Hexa

CHAVES

RESULTADO

B3 B2 B1 B0

A

B

C

D

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

CI

MOD

.. .. .. ..

L3 L2 L1 L0

AA BB CC DD

0

1

0

1

1

A

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

0

1

B

0

1

C

1

D

0

0

fig 1

SINAL

DISPLAY

etapa 1

DECODIFICADOR

Decodificador

SELETOR 3:1

MONITORES

GERADORES

DOS SINAIS

DE

CONTROLE

SOMADOR /

SUBTRATOR

BCD

REG A

REG B

PULSOS 2

MODO

`+/-

1

1

1

0

1

1

1

1

PULSOS 1

CONTADOR BCD

Questões

1. Comparando agora os resultados previstos no projeto desenvolvido na teoria (AED da

preleção) com os do teste do CI da experiência 1 dec BHEXA. São diferentes? _____

Por quê?

2. Comparando agora os resultados previstos no projeto desenvolvido na teoria (AED da

preleção) com os do teste do CI da experiência 2 dec BCD. São diferentes? _____

Por quê?

5

AULA 7

Circuitos XOR e XNOR; Aplicações.

Objetivo: Circuitos XOR e XNOR; Aplicações: Gerador e Teste de paridade; Circuitos T/C.

Fundamentos Teóricos: conforme Referência Livro Texto: Capítulo 4.6 a 4.8

Experiência 1: CIRCUITO GERADOR DE PARIDADE PAR.

Procedimentos experimentais

Testar o funcionamento do módulo ou kit de montagem

Colocar o(s) CI(s) no módulo ou kit de montagem e testar as portas do CI 7486

Layout abaixo (roteiro Aula 1)

chaves

gerador de paridade PAR

A B C D

paridade

P

A

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

Numerar os pinos das portas no esquema do circuito gerador de paridade ACIMA

de acordo com o Layout do CI7486 abaixo

Simular o teste do circuito gerador de paridade para 4 Bits ABCD preenchendo a

coluna res. da tabela verdade.

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

prev

S

0

1

1

0

1

0

0

1

1

0

0

1

0

1

1

0

res.

S

Vcc

14

13

12

11

10

9

8

5

6

7

7486

1

2

3

4

6

Experiência 2: CIRCUITO True / Complement – T / C

Usando um CI 7486 (4 portas XOR) Layout abaixo e um CI 7447 ou 7448

(DECOFICADOR BCD) com DISPLAY de 7 segmentos; Montar um Circuito T/C

(True/Complement) para 4 bits de entradas: B3 B2 B1 B0 ,

Vcc

14

13

12

11

10

9

8

5

6

7

7486

1

2

3

4

Procedimentos Experimentais

Numerar no ESQUEMA acima do circuito T/C, os pinos das portas de acordo

como layout (acima) do CI 7486

Montar e testar o circuito T/C com 4 Bits – entradas: B3 B2 B1 B0 no modulo de

teste

7

Considerando que K é chave do modo T/C verifique o funcionamento do circuito

preenchendo as colunas K = 0 e K = 1 da tabela a seguir:

PREVISTO

entr. fios coloridos

B3

B2

B1

B0

15

0

0

0

0

14

0

0

0

1

13

0

0

1

0

12

0

0

1

1

11

0

1

0

0

10

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

10

1

0

1

0

11

1

0

1

1

12

1

1

0

0

13

1

1

0

1

14

1

1

1

0

15

1

1

1

1

K=T K=C

RESULTADO

K=0

K=1

Obs. Números 10 a 15 figuras correspondentes (decodificador BCD)

8

AULA 8

Projeto final etapa 2 (Circuito somador e subtrator)

Objetivo: Montar e testar CI 74283 Somador Binário Paralelo de 4 bits (Layout Fig 2) e

implementar um circuito somador / subtrator (fig 1) com um CI 74283 e um CI 7486 (usado

na etapa 1 como T/C)

Fundamentos Teóricos: conforme Referência Livro Texto: Capítulo 4.6 a 4.8 e cap 6

SINAL

DISPLAY

I

DECODIFICADOR

SELETOR 3:1

MONITOR

SOMADOR /

SUBTRATOR BCD

GERADOR

DE SINAIS

DE

CONTRÔLE

etapa 2

REG B

REG A

MODO

+/-

PULSO 1

PULSO 2

CONTADOR BCD

Fig 1- diagrama da calculadora BCD 2a ETAPA

16

15 14 13 12

11 10

9

Vcc B2 A2 S2 A3 B3 S3 Cout

S1

1

B1 A1 S0 A0 B0 Cin Gnd

2

3 4 5

6 7

Fig 2 - LAY OUT CI 74283

8

9

Procedimentos experimentais:

EXPERIENCIA 1: teste do circuito somador binário pleno de 4 bits

Coloque um CI 74283 (layout ACIMA) no modulo de teste ligando a alimentação

pinos 08- terra (0) e 16- +5v (1).

CI 74283

Complete o esquema (acima) Numerando no circuito somador de acordo com os

pinos do layout do CI 74283 (PAGINA ANTERIOR).

Fazer a interligação (traço ponto) do pino C4 no “ponto” do display. Observe

qual CI Decodificador foi utilizado já que o PONTO do Display acende com nível

ALTO se for Display CC com CI 7448 e permanece apagado se for Display AC com

CI 7447

Escreva abaixo 2 somas de dois números (A e B) de 4

bits,S = A + B no modelo:

Teste o circuito descrevendo e executando as contas

abaixo, destacando os resultados intermediários e no

final desenhando o display bem como o estouro C4

acesso

apagado

A=

B=

A=

B=

S= A + B S < 9

S= A + B S > 9

10

EXPERIENCIA 2: CIRCUITO SOMADOR / SUBTRATOR DE 4 Bits

CI 74283

B3

B2

B1

B0

Complete o esquema (acima) (repetindo a numeração dos pinos) usado na

AULA 6 como T/C, ao CI 7483 E (repetindo a numeração dos pinos DO

ESQUEMA FOLHA ANTERIOR) para implementar o circuito somador / subtrator.

Fazer a interligação (traço ponto) do pino C4 no “ponto” do display. Observe

qual CI Decodificador foi utilizado já que o PONTO do Display acende com nível

ALTO se for Display CC com CI 7448 e permanece apagado se for Display AC com

CI 7447

Escreva abaixo 3 somas de dois números (A e B) de 4

bits,S=A+B no modelo:

Teste o circuito descrevendo e executando as contas

abaixo, destacando os resultados intermediários e no final

desenhando o display bem como o estouro C4

acesso

apagado

A=

B=

S= A + B S = 9

A=

B=

S= A + B9< S <15

A=

B=

S= A + B S > 15

11

CI 74283

B3

B2

B1

B0

Manter a interligação do pino C4 no “ponto” do display. Observe qual CI

Decodificador foi utilizado já que o PONTO do Display acende com nível ALTO se

for Display CC com CI 7448 e permanece apagado se for Display AC com CI 7447

Escreva abaixo 3 subtrações de dois números (A e B) de 4 bits,S = A - BA + (- B)

no modelo:

Testar o circuito, descrevendo e executando as

contas

abaixo,

destacando

os

resultados

intermediários e no final desenhando o display bem

como o estouro C4

acesso

apagado.

A=

B=

S= A - B A = B

A=

B=

S= A - B A > B

A=

B=

S= A - B A < B

12