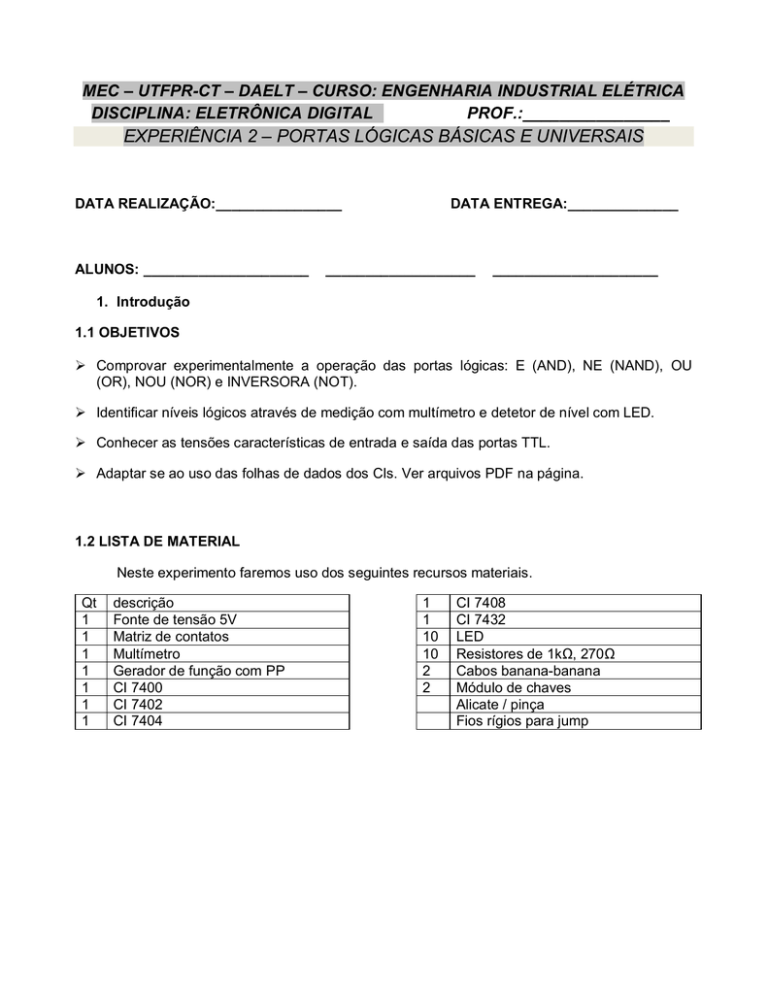

MEC – UTFPR-CT – DAELT – CURSO: ENGENHARIA INDUSTRIAL ELÉTRICA

DISCIPLINA: ELETRÔNICA DIGITAL

PROF.:________________

EXPERIÊNCIA 2 – PORTAS LÓGICAS BÁSICAS E UNIVERSAIS

DATA REALIZAÇÃO:________________

ALUNOS: _____________________

DATA ENTREGA:______________

___________________

_____________________

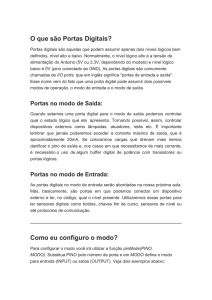

1. Introdução

1.1 OBJETIVOS

Comprovar experimentalmente a operação das portas lógicas: E (AND), NE (NAND), OU

(OR), NOU (NOR) e INVERSORA (NOT).

Identificar níveis lógicos através de medição com multímetro e detetor de nível com LED.

Conhecer as tensões características de entrada e saída das portas TTL.

Adaptar se ao uso das folhas de dados dos CIs. Ver arquivos PDF na página.

1.2 LISTA DE MATERIAL

Neste experimento faremos uso dos seguintes recursos materiais.

Qt

1

1

1

1

1

1

1

descrição

Fonte de tensão 5V

Matriz de contatos

Multímetro

Gerador de função com PP

CI 7400

CI 7402

CI 7404

1

1

10

10

2

2

CI 7408

CI 7432

LED

Resistores de 1kΩ, 270Ω

Cabos banana-banana

Módulo de chaves

Alicate / pinça

Fios rígios para jump

2

1.3 METODOLOGIAS

Ml - Para simular a entrada das variáveis em níveis lógicos “0” e “1” será utilizado o arranjo

de chaves “NA” / “NF” associadas a resistores, utilizando-se de estratégias de resistores pull-up

ou pull-down.

M2- Alimente o CI antes de verificar a tabela verdade (TV) da porta lógica indicada.

M3- Para identificar os pontos na base de montagem, da matriz de contatos (MC) utilize a

função teste de continuidade do Multímetro Digital. Adapte o jump na ponta de prova do

Multímetro Digital, para facilitar o contato com os pontos de contatos da matriz.

M4- Para facilitar a inserção dos componentes na matriz de contatos deve-se fazer uso de

pinça ou alicate de bico chato apropriado.

M5- Para evitar constantes manobras no interruptor da fonte de tensão, adotar-se-á uma

chave H-H, liga/desliga, entre a fonte e a matriz de contatos.

M6 – Esboce o circuito e escreva a respectiva TV antes da implementação.

M7 – Certifique-se de que entendeu a proposição e redija uma conclusão para cada

exercío implementado.

MATRIZ DE TABELA DA VERDADE (TV) PARA DUAS E TRÊS VARIÁVEIS.

TABELA PARA DUAS VARIÁVEIS

TABELA PARA TRÊS VARIÁVEIS

RELEMBRANDO O CIRCUITOS GERADOR DE VARIÁVEIS E O VERIFICADOR DE VARIÁVEIS

GERADOR DE VARIÁVEIS

PROVADOR LÓGICO

3

2 Desenvolvimento

2.1 Fundamentação teórica

A cargo do aluno

2.2 Procedimentos

P1 – Implemente o módulo gerador de variáveis. Observar experiência 1 figura 4.

P2 – Implemente o módulo detector de variáveis, provador lógico. Observar experiência 1 figura 3.

P3 – Teste a tv da porta “NÃO” (INVERSORA) usando o CI 74LS04.

a) Apenas alimente o CI pinos 7(massa) e 14 (VCC) e meça a tensão nos pinos 1, 2, 3, 4 e 5

do CI. Justifique.

b) Faça uso da folha MAPA DE CIs.

c) Construa a tabela da verdade (TV) da porta inversora.

d) Faça as verificações utilizando o multímetro e o provador lógico.

e) Antes de conectar o gerador de variáveis, com o multímetro, meça os valores de tensão

encontrados nos pinos 1, 2, 3, 4.... Justifique...

f) Pode-se aplicar nível lógico aos pinos 2, 4, 6, 10 ou 12? Justifique!

g) Faça o pino 1 assumir o nível lógico “0” e meça o nível lógico presente no pino 2.

Justifique.

h) Faça o pino 1 assumir o nível lógico “1” e meça o nível lógico presente no pino 2.

Justifique.

i) Faça o pino 3 assumir o nível lógico “0” e meça o nível lógico presente no pino 4.

Justifique.

j) Faça o pino 5 assumir o nível lógico “1” e meça o nível lógico presente no pino 6.

Justifique.

CP3:

P4 – Coloque 2 portas “NÃO” em série e verifique a saída conforme a variação da entrada.

Construa a TV do circuito.

4

CP4:

P5 – Coloque 3 portas “NÃO” em série e verifique a saída conforme a variação da entrada.

Desenhe o diagrama esquemático para este circuito. Desenhe o diagrama de interligação das

portas. Construa a TV do circuito. Verifique a TV.

CP5:

P6 – TESTANDO A TV DA PORTA E

Construa a TV da porta E. Esboce o diagrama de interligações. Implemente o circuito. Teste a

TV.

CP6:

P7 – TESTANDO A TV DA PORTA OU

Esboce a TV, esboce o diagrama esquemático, esboce o diagrama de interconexões, teste

a TV.

CP7:

P8 – TESTANDO A TV DE PORTAS “NÃO E”

a) Implemente a função NE utilizando o CI de porta “E” e Inversor. Teste a TV.

b) Implemente a função NE utilizando o CI 7400. Teste a TV.

c) Compare os resultados.

5

CP8:

P9 – TESTANDO A TV DE PORTAS NÃO OU

a) Implemente a função NOU utilizando o CI de porta OU e Inversor. Teste a TV.

b) Implemente a função NOU utilizando o CI 7402. Teste a TV.

c) Compare os resultados.

CP9:

P10 – Aplicando portas universais operar como portas inversoras

a) Faça uma porta “NÃO E” funcionar como um porta inversora (Use as duas possibilidades)

b) Faça uma porta “NÃO OU” funcionar como uma porta inversora.

c) Obtenha porta E a partir de porta “NÃO E”

d) Obtenha porta OU a partir de porta “NÃO OU”

6

QUESTÕES PARA REFLEXÃO

1. O que devemos entender por coletor aberto em termos de bloco lógico TTL?

2. O que podemos encontrar na saída de um bloco lógico cujo pino de entrada encontra-se

suspenso (flutuando) se a lógica for coletor aberto? (suspenso?) (flutuando?) (Estou boiando?)

3. Qual fundamento da álgebra de Boole é utilizado no procedimento 3?

4. Qual fundamento da álgebra de Boole é utilizado no procedimento 4?

5. Dos CIs em uso quais contêm portas básicas e quais contêm portas consideradas universais?

6. O que acontece se aplicarmos o sinal de entrada a uma porta cujo CI não foi alimentado?

7. O que acontece a qualquer CI se aplicarmos sinal a um pino cuja função seja de saída?

8. Explicite seus conhecimentos sobre os níveis lógicos nos pinos de entrada e de saída das

portas lógicas da família TTL tradicional.

9. Em uma única tabela da verdade de 3 entradas apresente a solução de saída para portas E,

OU, NE, NOU.

10. O que você pensa sobre o tempo de propagação se sinais em portas lógicas, considere portas

lógicas de tecnologia TTL e tecnologia CMOS.

11. O que você está entendendo sobre deixar um pino de entrada de uma porta lógica TTL com o

sinal suspenso?

12. Desenhe o equivalente de uma porta E, OU, NE e NOU utilizando chaves, LEDs, diodos e

resistores.

CONCLUSÃO: