Victor Siqueira Cunha

Projeto e Simulação de um AMP-OP para

Validação de um Sistema de Filtro de Tempo

Discreto

Curitiba

2016

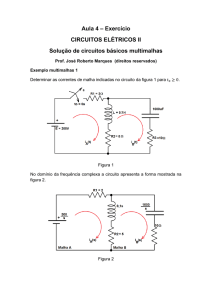

Victor Siqueira Cunha

Projeto e Simulação de um AMP-OP para Validação de

um Sistema de Filtro de Tempo Discreto

Projeto de Graduação como requisito de matrícula na disciplina TEX003 – Projeto de

Engenharia Elétrica para Dupla Diplomação,

do Departamento de Engenharia Elétrica, Setor de Tecnologia, Universidade Federal do

Paraná

Universidade Federal do Paraná – UFPR

Departamento de Engenharia Elétrica

Graduação em Engenharia Elétrica

Orientador: Prof. Dr. Luis Henrique A. Lolis

Curitiba

2016

Agradecimentos

Agradeço aos meus pais por todo o suporte e incentivo. Estes me fizeram quem

sou.

Resumo

Os dispositivos sem fio, amplamente utilizados nos dias de hoje, exigem um baixo consumo

de energia e precisam ser flexíveis a múltiplas frequências de portadoras. A técnica de

subamostragem é usada de modo a reduzir os requisito do amostrador, resultando em

circuitos com consumo de potência reduzido. O presente trabalho consiste no estudo de

sinais e sistemas e no projeto de um amplificador operacional de transcondutância (OTA)

com especificações para funcionamento em um filtro de tempo discreto, que faz o uso de

capacitores chaveados e possui frequência de amostragem de 25 Mhz.

Palavras-chave: Amplificador Operacional de Transcondutância, Filtro de Tempo Discreto, Capacitores Chaveados.

Abstract

Wireless devices, widely used today, require low power consumption and need to be

flexible at multiple carrier frequencies. The subsampling technique is used in order to

reduce sampler requirement, resulting in circuits with reduced power consumption. The

present work consists of the study of signals and systems and the design of a operational

transconductance amplifier (OTA) with specifications for operation in a discrete time filter,

which operates with switched capacitors and has a sampling frequency of 25 Mhz.

Keywords: Operational Transconductance Amplifier, Discrete Time Filter, Switched

Capacitors.

Lista de ilustrações

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

1

2

3

4

5

6

7

8

–

–

–

–

–

–

–

–

Sinal em Tempo Discreto . . . . . . . . . . . . . . . . . . . . . . . . . .

Representação de um Sistema em Tempo Discreto . . . . . . . . . . . .

Representação de um passa baixa em Tempo Discreto . . . . . . . . . .

Representação de um delay unitário no domínio z . . . . . . . . . . . .

Representação da EDCC no domínio z . . . . . . . . . . . . . . . . . .

Representação de um FIR e sua resposta em frequência |H(f )|2 . . . .

Resposta em frequência |H(f )|2 de um filtro IIR . . . . . . . . . . . . .

Representação de um capacitor em um circuito integrado (a) construção

física (b) modelo elétrico . . . . . . . . . . . . . . . . . . . . . . . . . .

9 – Representação de um switch com transistores MOSFET (a) NMOS (b)

PMOS (c) CMOS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10 – Símbolo e circuito equivalente de um AMP-OP ideal . . . . . . . . . .

11 – Representação de 2 clocks não sobrepostos (a) 2 sinais de clock (B)

realização prática dos clocks . . . . . . . . . . . . . . . . . . . . . . . .

12 – Representação de um resistor com capacitores chaveados (a) circuito

(b) resistor equivalente . . . . . . . . . . . . . . . . . . . . . . . . . . .

13 – Circuito de um FIR de 4a ordem com capacitores chaveados . . . . . .

14 – Circuito de um IIR a partir de um circuito integrador com capacitores

chaveados . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15 – Circuito para simular o ganho diferencial de um OTA . . . . . . . . . .

16 – Representação do ruído em um OTA (a) circuito (b) resposta em frequência

17 – Curva de transferência DC ideal de um OTA . . . . . . . . . . . . . . .

18 – Curva de transferência DC "real"de um OTA . . . . . . . . . . . . . . .

19 – Curva de transferência "real"AC de um OTA . . . . . . . . . . . . . . .

20 – Representação do tempo de resolução de um OTA . . . . . . . . . . . .

21 – Representação de dois sinais produzindo intermodulação de terceira

ordem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22 – Representação gráfica do cálculo de IIPn . . . . . . . . . . . . . . . . .

23 – Topologia de OTA escolhida para o projeto . . . . . . . . . . . . . . .

24 – Circuito equivalente do OTA de dois estágios . . . . . . . . . . . . . .

25 – Circuito equivalente do OTA com capacitor de compensação . . . . . .

26 – Representação gráfica do efeito do capacitor de compensação na resposta

em frequência do OTA . . . . . . . . . . . . . . . . . . . . . . . . . . .

27 – Circuito de teste usado para testar o OTA . . . . . . . . . . . . . . . .

28 – Circuito de espelho de corrente usado para gerar Vbias . . . . . . . . . .

29 – Curva de comportamento DC do OTA . . . . . . . . . . . . . . . . . .

14

15

17

18

18

19

20

21

22

22

23

24

25

26

28

29

30

30

31

32

34

34

37

38

38

39

46

46

48

Figura

Figura

Figura

Figura

Figura

Figura

Figura

Figura

30

31

32

33

34

35

36

37

–

–

–

–

–

–

–

–

Resposta em frequência do OTA, curvas de ganho e fase

Resposta transiente do OTA . . . . . . . . . . . . . . . .

Resposta de ruído do ota a) Visto de Vout b) Visto de Vin

Figura de ruído do OTA . . . . . . . . . . . . . . . . . .

Calculo do IIP3 do OTA . . . . . . . . . . . . . . . . . .

Circuito equivalente do modelo OTA do Cadence . . . .

Resposta em frequência do modelo do OTA . . . . . . .

Resposta transiente do modelo do OTA . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

49

49

50

50

51

52

53

54

Lista de tabelas

Tabela

Tabela

Tabela

Tabela

Tabela

Tabela

1

2

3

4

5

6

–

–

–

–

–

–

Dimensionamento dos capacitores do filtro IIR . .

Especificações do OTA . . . . . . . . . . . . . . .

Dimensionamento do OTA . . . . . . . . . . . . .

Dimensionamento do OTA após correções . . . .

Parâmetros do OTA utilizado de modelo . . . . .

Comparação do OTA com outros apresentados na

. . . . . .

. . . . . .

. . . . . .

. . . . . .

. . . . . .

literatura

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

27

36

45

47

53

56

Lista de abreviaturas e siglas

FIR

Resposta ao Impulso de Duração Finita

IIR

Resposta ao Impulso de Duração Infinita

CAD

Conversor Analógico-Digital

EDCC

Equação de Diferença a Coeficientes Constantes

AMP-OP

Amplificadores Operacionais

OTA

Amplificadores Operacionais de Transcondutância

PSRR

Taxa de Rejeição da Fonte de Alimentação

CMRR

Taxa de Rejeição de Ganho de Modo Comum

AC

Corrente Alternada

DC

Corrente Direta

CMR

Faixa de tensão de modo comum na entrada (Common Mode Range)

GB

Frequência de ganho unitário (Gain-Bandwidth)

SR

Slew-rate

MOSIS

Metal Oxide Semiconductor Implementation Service

GICS

Group of Integrated Circuits and Systems

PSS

Análise periódica de estado estacionário (Periodic Steady-State Analysis)

PAC

Análise AC periódica (Periodic AC Analysis)

PNOISE

Análise periódica de ruído (Periodic Noise Analysis)

IIP3

Ponto de intercepção de terceira ordem

IMD

Distorções de intermodulação

Sumário

1

1.1

1.2

1.2.1

1.2.2

INTRODUÇÃO . . .

Contexto e motivação

Objetivos . . . . . . .

Objetivo geral . . . . . .

Objetivos específicos . .

.

.

.

.

.

.

.

.

.

.

. . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

12

12

12

12

12

2

2.1

2.1.1

2.1.2

2.1.3

2.1.4

2.1.5

REVISÃO BIBLIOGRÁFICA . . . .

Sinais e sistemas de tempo discreto

Sinais de tempo discreto . . . . . . . .

Sistemas de tempo discreto . . . . . . .

Resposta em frequência . . . . . . . . .

Transformada z . . . . . . . . . . . . .

Filtros . . . . . . . . . . . . . . . . . .

Filtro FIR . . . . . . . . . . . . . . . . .

Filtro IIR . . . . . . . . . . . . . . . . .

Filtros a Capacitores Chaveados . .

Elementos Importantes . . . . . . . . .

Capacitores . . . . . . . . . . . . . . . .

Switches . . . . . . . . . . . . . . . . .

AMP-OPs . . . . . . . . . . . . . . . .

Clocks não sobrepostos . . . . . . . . . .

Resistência equivalente . . . . . . . . .

Implementação analógica de um FIR . .

Implementação analógica de um IIR . .

Características dos OTA . . . . . . .

Ganho Diferencial . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

14

14

14

15

16

17

18

2.4

2.4.1

2.4.2

. . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . .

Taxa de rejeição de ganho de modo comum (CMRR) . . . . . . . . . . . .

Taxa de rejeição da fonte de alimentação (PSRR) . . . . . . . . . . . . . .

Ruído . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Resposta DC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Resposta AC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Modelagem do sistema . . . . . . . . . . . . . . . . . . . . . .

Bloco ampop do cadence . . . . . . . . . . . . . . . . . . . . . . .

Ponto de intercepção de terceira ordem (IIP3) . . . . . . . . . . . .

3

PROJETO DO OTA . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

2.1.5.1

2.1.5.2

2.2

2.2.1

2.2.1.1

2.2.1.2

2.2.1.3

2.2.1.4

2.2.2

2.2.3

2.2.4

2.3

2.3.0.1

2.3.0.2

2.3.0.3

2.3.0.4

2.3.0.5

2.3.0.6

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

19

19

20

21

21

21

22

23

23

24

25

27

27

28

28

29

29

30

32

32

33

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

3.1

3.2

3.3

3.4

3.5

Especificações do OTA desejado

Topologia . . . . . . . . . . . . .

Dimensionamento . . . . . . . .

Circuitos de suporte . . . . . . .

Resultados Obtidos . . . . . . . .

4

4.1

4.2

MODELO COMPORTAMENTAL DO OTA . . . . . . . . . . . . . . 52

Dimensionamento . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Resultados Obtidos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

5

CONCLUSÃO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

REFERÊNCIAS

36

36

39

45

47

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

12

1 Introdução

1.1 Contexto e motivação

O mundo de hoje é conectado e os dispositivos eletrônicos fazem grande uso da

comunicação sem fio. Uma característica determinante para que estes dispositivos possam

estar conectados é a duração da bateria. Os circuitos de recepção wireless são alguns dos

elementos que mais consomem bateria nos dispositivos eletrônicos. Por isso, é importante

que estes componentes sejam altamente eficientes. Outra característica importante é a

flexibilidade, pois existem diversas frequências de portadoras e diferentes protocolos de

comunicação. Este conceito de flexibilidade na recepção RF é chamado de Radio Definido

por Software e faz parte de um sistema no qual os únicos componentes analógicos são

o conversor analógico/digital no receptor e o conversor digital/analógico no transmissor.

(BAGHERI et al., 2006).

A utilização de capacitores CMOS para o tratamento de sinais de radiofrequência

é interessante, pois permite uma resolução no tempo do sinal digital superior a resolução

da tensão do sinal analógico (STASZEWSKI et al., 2004).

A subamostragem, que consiste na amostragem do sinal em banda passante, é

uma técnica utilizada para simplificar a cadeia de recepção do sinal. Esta técnica faz a

conversão do sinal da banda passante para a banda base, de modo a reduzir os requisitos

do amostrador. Este trabalho faz parte de um estudo de sinais e sistemas para filtragem de

sinais em banda passante e do projeto de um amplificador operacional a transcondutância,

de baixo consumo, que será utilizado para compor um filtro de tempo discreto utilizando

capacitores chaveados, previamente apresentado por (LOLIS, 2011).

1.2 Objetivos

1.2.1 Objetivo geral

Projetar e simular um amplificador operacional (AMP-OP) que será utilizado em

um filtro de tempo discreto e modelar o amplificador projetado, com o intuito de reduzir o

tempo de processamento do mesmo.

1.2.2 Objetivos específicos

Para atingir este objetivo geral serão propostos os seguintes objetivos específicos:

Capítulo 1. Introdução

13

a) Estudar a teoria dos filtros de tempo discreto;

b) Estudar as especificações e a topologia de um amplificador operacional;

c) Projetar o esquemático do AMP-OP e simular separadamente cada estágio do

AMP-OP para então validar o amplificador completo;

d) Estudar os modelos prontos de AMP-OP do Cadence , que estão escritos em linguagem

Verilog-A;

14

2 Revisão Bibliográfica

2.1 Sinais e sistemas de tempo discreto

2.1.1 Sinais de tempo discreto

Este trabalho é sobre o projeto de um AMP-OP que irá operar no domínio de tempo

discreto. No processo de conversão de um sinal analógico para digital, o tempo discreto

é o processo intermediário, neste domínio o sinal analógico já foi amostrado no tempo

e precisa ser quantizado pelo conversor analógico-digital (CAD). Um sinal no domínio

discreto de tempo pode ser representado pelos valores de um sinal analógico no enésimo

valor do sinal no tempo nT . Onde n é um inteiro e T é o Período de amostragem.

x[n] = xn (nT ),

−∞ < n < ∞.

(2.1)

A figura 1 mostra um sinal qualquer no domínio discreto de tempo.

x[n]

2

1.5

1

0.5

−6

−4

−2

2

4

6 n

Figura 1 – Sinal em Tempo Discreto

Fonte: O autor, 2016

Uma forma de analisar um sinal no tempo discreto é tomar em conta a função

dirac no domínio de tempo contínuo:

δ[n] =

1, n6=0,

0, n=0.

(2.2)

Capítulo 2. Revisão Bibliográfica

15

E com isso podemos caracterizar o sinal em tempo discreto como a reconstrução

de um sinal pela sua resposta ao impulso conforme a equação 2.3.

∞

X

x[n] =

x[k]δ[n − k].

(2.3)

k=−∞

2.1.2 Sistemas de tempo discreto

Um sistema de tempo discreto é um sistema que converte a partir de um operador

matemático um sinal x[n] em uma saída y[n]. Como mostram a equação 2.4 e a figura 2.

y[n] = T {x[n]}.

T{.}

x[n]

(2.4)

y[n]

Figura 2 – Representação de um Sistema em Tempo Discreto

Fonte: O autor, 2016

A maior parte das aplicações de sistemas discretos no tempo são feitas em cima de

sistemas que são chamados de sistemas lineares invariáveis no tempo, pois estes possuem

algumas características que permitem um tratamento simplificado do sinal em questão.

A classe de sistemas lineares é definida pelo princípio da superposição. Para um

sistema ser considerado linear é preciso que para duas entradas x1[n] e x2[n] que possuem

respostas y1[n] e y2[n] as seguintes afirmações sejam validas:

T {x1 [n]} + T {x2 [n]} = y1 [n] + y2 [n].

(2.5)

aT {x1 [n]} = ay1 [n].

(2.6)

Estas equações podem ser generalizadas para muitas entradas. Desta maneira

podemos garantir que para uma entrada:

x[n] =

X

k

ak xk [n].

(2.7)

Capítulo 2. Revisão Bibliográfica

16

O sistema será linear se a saída for:

y[n] =

X

ak yk [n].

(2.8)

k

Um sistema é invariante no tempo se um delay ou deslocamento de tempo causar

uma mudança correspondente no sinal de saída. Como por exemplo o sinal a seguir:

y1 [n] =

n−n

X0

x[k1 ] = y[n − n0 ].

(2.9)

k1 =−∞

Um sistema linear invariante no tempo é um sistema que combina as duas propriedades acima. Quando um sistema satisfaz ambas as propriedades podemos dizer que sua

resposta é completamente caracterizada por sua resposta em frequência, o que faz com

que este sistema seja interessante para o processamento de sinais. Ao aplicarmos as duas

propriedades no sinal temos que a resposta ao impulso de um sistema linear é a seguinte:

y[n] =

∞

X

x[k]h[n − k].

(2.10)

k=−∞

A equação 2.10 é também conhecida como a convolução da soma e pode ser

representada pela equação 2.11. Partindo desta propriedade, é possível realizar sistemas,

sejam eles matemáticos ou práticos, que tratem um sinal x[n] para uma saída y[n] desejada,

a partir do sinal h[n]. O tratamento do sinal pode ser feito ainda em tempo discreto, em

hardware, antes da quantização do sinal, ou mesmo depois da quantização do sinal, através

de softwares que realizem as filtragens desejadas.

y[n] = x[n] ∗ h[n].

(2.11)

2.1.3 Resposta em frequência

O conceito de resposta em frequência de um sistema linear invariante no tempo

é essencialmente o mesmo para sistemas de tempo continuo e para sistemas de tempo

discreto. A representação de uma transformada de fourier em tempo discreto é a seguinte:

jω

H(e ) =

∞

X

h[k]e−jωk .

(2.12)

k=−∞

O sinal no domínio da frequência H(ejω ) é geralmente complexo e pode ser expresso

da seguinte maneira:

H(ejω ) = HR (ejω ) + jHI (ejω ).

(2.13)

Capítulo 2. Revisão Bibliográfica

17

ou em termos de magnitude e fase:

H(ejω ) = |H(ejω )|ej

6 H(ejω )

.

(2.14)

A partir da equação 2.15 podemos provar que H(ejω ) é periodica com periodo 2π.

e−j(ω+2π)n = e−jωn e−j2πn = e−jωn .

(2.15)

A figura 3 mostra a representação de um filtro passa baixa ideal no domínio da

frequência. Observa-se que próximo da frequência 0 e de seus múltiplos consecutivos de 2π,

o sinal possui resposta unitária, enquanto que para valores próximos de π (alta frequência),

o sinal possui resposta 0. A frequência ωc é a frequência de corte do filtro.

1

Figura 3 – Representação de um passa baixa em Tempo Discreto

Fonte: O autor, 2016

A partir do teorema de Nyquist, definido pela equação 2.16, que define que um sinal

amostrado no tempo, possuí banda passante B limitada em Fs /2, onde Fs é a frequência

de amostragem, podemos concluir portanto que para um sinal periódico no tempo, quando

analisado em frequência, seus múltiplos de π serão Fs /2.

B<

Fs

.

2

(2.16)

2.1.4 Transformada z

Uma forma mais eficiente de analisar sistemas de tempo discreto é a partir da

transformada z, a seguir a transformada z da equação 2.17.

X(z) =

∞

X

x[n]z −n .

(2.17)

k=−∞

Os multiplicadores z −n da transformada z podem ser interpretados como valores

atrasados em n amostras do sinal atual x[n]. A figura 4 representa um delay unitário de

um devido sinal x[n] no domínio z.

Capítulo 2. Revisão Bibliográfica

18

Figura 4 – Representação de um delay unitário no domínio z

Fonte: (OPPENHEIM; SCHAFER; BUCK, 1999)

2.1.5 Filtros

Os filtros de sistemas lineares invariantes no tempo podem ser generalizados na

Equação de Diferença a Coeficientes Constantes(EDCC) que está escrita no domínio do

tempo e em z nas equações 2.18 e 2.19.

y[n] −

N

X

ak y[n − k] =

k=1

M

X

bk x[n − k].

(2.18)

k=0

M

P

H[z] =

1

bk x[n − k]

k=0

.

N

P

−

ak y[n − k]

k=1

(2.19)

Esta equação define que o sinal de saída será uma combinação do sinal atual, com

os últimos valores do sinal na entrada e os últimos valores do sinal na saída do sistema.

Podemos observar melhor a partir da figura 5.

Figura 5 – Representação da EDCC no domínio z

Fonte: (OPPENHEIM; SCHAFER; BUCK, 1999)

Capítulo 2. Revisão Bibliográfica

19

2.1.5.1 Filtro FIR

Quando o sistema em questão possui apenas o numerando da equação 2.19, este

sistema é chamado de Filtro de Resposta ao Impulso de Duração Finita (FIR), sua função

de transferência é dada pela equação 2.20 . Como não possuímos divisor na equação de

transferência, então podemos garantir que qualquer sistema FIR será sempre estável. A

equação de transferência nunca irá tender ao infinito, logo sua resposta é de duração finita.

A resposta de um filtro FIR será sempre dependente do sinal de entrada e de seus ultimas

medições, porém independe das ultimas medidas na saída.

H[z] =

M

X

bk x[n − k].

(2.20)

k=0

A figura 6a mostra a representação em blocos de um FIR e a figura 6b mostra

a resposta típica de um filtro FIR no domínio da frequência com MN=4, ou seja, este

filtro utiliza das ultimas 4 medidas na entrada para produzir o sinal de saída. A partir da

figura 6b podemos claramente ver seu comportamento de passa baixa, tendo em vista que

perto da frequência 0 nosso ganho é 1 ( 0 dB) enquanto que perto de 0,5 da frequência de

amostragem, nosso sinal é próximo de 0 (-30 dB).

(a)

(b)

Figura 6 – Representação de um FIR e sua resposta em frequência |H(f )|2

Fonte: (LOLIS, 2011)

2.1.5.2 Filtro IIR

Se o filtro possui denominador na equação 2.19, este sistema terá Resposta ao

Impulso de Duração Infinita (IIR). E diferente do filtro FIR, este filtro pode ser instável

Capítulo 2. Revisão Bibliográfica

20

em situações na qual o denominador possa tender ao infinito. A equação 2.21 tem um

exemplo de IIR de primeira ordem. Em função do valor β o filtro pode ser instável(β > 1)

ou estável. A estabilidade é melhor explicada pelo Região de Convergência da função de

transferência(LOLIS, 2011). A figura 7 contém um exemplo de filtro IIR, onde o termo

N = 4, para diferentes valores de β. Pode-se observar que a resposta em frequência deste

filtro é mais seletiva que a dos filtros FIR.

M

P

H[z] =

bk x[n − k]

k=0

1 − βz −N +1

.

(2.21)

Figura 7 – Resposta em frequência |H(f )|2 de um filtro IIR

Fonte: (LOLIS, 2011)

2.2 Filtros a Capacitores Chaveados

A forma mais popular de fazer o tratamento de sinais em Tempo Discreto antes da

quantização pelo CAD é através de capacitores chaveados. Capacitores chaveados operam

como processadores de sinal em tempo discreto e podem ser facilmente analisados com

o uso da transformada z. Sua popularidade esta diretamente relacionada ao fato que

capacitores nos circuitos integrados são altamente precisos (na ordem de 0,1%), enquanto

que circuitos RC convencionais não atingem grandes precisões (podem variar até 20%)

(CARUSONE; JOHNS; MARTIN, 2011). O chaveamento é controlado a partir de sinais

de clock que também são altamente precisos.

Filtros a capacitores chaveados usam capacitores, AMP-OPs, switches e clocks não

sobrepostos. Estes serão brevemente explicados.

Capítulo 2. Revisão Bibliográfica

21

2.2.1 Elementos Importantes

2.2.1.1 Capacitores

Nos circuitos integrados convencionais, as capacitâncias são geralmente construídas

por duas trilhas condutivas levemente separadas, sua construção física esta representada

na figura 8a. Os capacitores possuem duas capacitâncias parasitas, conforme a figura 8b.

A capacitância Cp1 é chamada de capacitância da placa superior (top-plate capacitance) e

é da ordem de 20% de C. A capacitância Cp2 é chamada de capacitância da placa inferior

e é da ordem de 5% de C, muito menos relevante que Cp1 .

(a)

(b)

Figura 8 – Representação de um capacitor em um circuito integrado (a) construção física

(b) modelo elétrico

Fonte: (CARUSONE; JOHNS; MARTIN, 2011)

2.2.1.2 Switches

Os transistores MOSFET satisfazem as necessidades de switch para aplicações com

capacitores chaveados. Estes possuem alta resistência em off (GΩ) e baixa resistência em

on (< 5KΩ). Um switch pode ser feito com somente um transistor seja este NMOS ou

PMOS, conforme figuras 9a e 9b. Porem este tipo de ligação possui limitações devido a

tensão de threshold dos transistores, sendo que os sinais V1 e V2 na montagem da figura 9a

não podem ser inferiores a VDD − Vth e na figura 9b não podem ser inferiores a VSS + Vth .

Tendo como base a tecnologia usado neste trabalho, os valores de Vth são em torno de

0, 35V e VDD = 1, 2V, limitando o switch NMOS de 0 a 0, 95V o switch PMOS de 0, 35

a 1, 2V. Como forma de evitar esta limitações, pode-se utilizar de uma combinação dos

transistores NMOS e PMOS, conforme figura 9c, esta combinação é chamada de switch

CMOS.

Capítulo 2. Revisão Bibliográfica

(a)

22

(b)

(c)

Figura 9 – Representação de um switch com transistores MOSFET (a) NMOS (b) PMOS

(c) CMOS

Fonte: (CARUSONE; JOHNS; MARTIN, 2011)

2.2.1.3 AMP-OPs

Amplificadores operacionais (AMP-OPs) são o elemento chave no processamento

analógico de sinais. Quando o tratamento de sinais é feito em tempo discreto, estes também

são muito usados. O AMP-OP ideal da figura 10 nos mostra que este é um elemento que

amplifica um sinal diferencial nas entradas V+ e V− em função de um ganho A. Geralmente

os AMP-OPs são utilizados realimentados, então é importante que o ganho diferencial A

seja alto, para que quando a tensão em V+ esteja em Vss , o sinal em V− se comporte como

uma "massa virtual", ou seja, com um valor muito próximo de Vss .

Figura 10 – Símbolo e circuito equivalente de um AMP-OP ideal

Fonte: (MALOBERTI, 2001)

Os AMP-OPs em circuitos embarcados geralmente são blocos genéricos, com

ganho alto, alta impedância de entrada e baixa impedância de saída, porém em circuitos

integrados, não existe a necessidade de baixa impedância de saída, pois normalmente a

carga do circuito é uma capacitância e não uma carga resistiva. Deste modo, o ultimo

estágio(normalmente um buffer), que serve para garantir a baixa impedância de saída, é

suprimido, reduzindo assim o consumo geral do bloco. AMP-OPs com alta impedância de

saída também são chamados de amplificadores operacionais de transcondutância (OTA) e

neste trabalho quando estivermos tratando de AMP-OPs estes serão inevitavelmente de

Capítulo 2. Revisão Bibliográfica

23

baixa impedância de saída. As características de AMP-OPs reais serão melhor tratadas no

capítulo 2.3.

2.2.1.4 Clocks não sobrepostos

Pelo menos um par de clocks não sobrepostos é necessário para a realização de

circuitos com capacitores chaveado. O termo não sobrepostos remete ao fato de que, ambos

os sinais não podem ficar em alto ao mesmo tempo, para evitar a perca de carga. A figura

11a mostra em um gráfico dois sinais de clock φ1 e φ2 não sobrepostos e a figura 11b

mostra um circuito prático para a realização destes dois sinais usando portas lógicas.

(a)

(b)

Figura 11 – Representação de 2 clocks não sobrepostos (a) 2 sinais de clock (B) realização

prática dos clocks

Fonte: (CARUSONE; JOHNS; MARTIN, 2011)

2.2.2 Resistência equivalente

A grande vantagem de trabalharmos com circuitos chaveados é o fato de podemos

substituir os resistores do circuito. Isso é possível, pois podemos reproduzir o comportamento de um resistor a partir de um capacitor chaveado, como mostra a figura 12.

A equação 2.22 é o valor de carga em um capacitor. As frequências φ1 e φ2 na

figura 12a são clocks complementares não sobrepostos. Em um primeiro momento, quando

φ1 está em alto, carrega-se o capacitor C1 com a tensão V1 . Em um segundo momento,

quando φ2 esta alto, transfere-se a tensão de C1 para V 2.

Qx = Cx Vx .

(2.22)

A carga será transferida para o capacitor a cada ciclo de clock, o que nos possibilita

calcular a corrente média que passará pelo capacitor, conforme a equação 2.23.

Imed =

C1 (V1 − V2 )

.

T

(2.23)

Capítulo 2. Revisão Bibliográfica

24

∆Q = C1 (V1 − V2 ) cada ciclo de

clock

Req =

T

C1

(b)

(a)

Figura 12 – Representação de um resistor com capacitores chaveados (a) circuito (b)

resistor equivalente

Fonte: (CARUSONE; JOHNS; MARTIN, 2011)

A corrente equivalente em um resistores é a seguinte:

Ieq =

V1 − V2

.

Req

(2.24)

Ao igualar as duas equações chega-se na relação da equação 2.25, que é a resistência

equivalente mostrada na figura 12b.

Req =

T

1

=

.

C1

C1 fs

(2.25)

Uma forma de analisar esta relação é imaginar que caso aumentemos a frequência

de clock, uma maior corrente será transferida para a saída. Caso a capacitância seja

aumentada, também haverá uma maior transferência de corrente para a saída.

2.2.3 Implementação analógica de um FIR

É possível implementar um filtro FIR apenas com capacitores chaveados, seguindo

do princípio de utilizar cada capacitor para carregar um período anterior do sinal de

entrada. A figura 13 mostra um filtro FIR de ordem 4 utilizando 4 capacitores chaveados.

A saída do circuito é amostrada a cada 4 amostras do sinal de entrada, realizando

uma operação equivalente a formula 2.20 com M = 4, conforme equação 2.26.

1

H(z) = P (C1 + C2 z −1 + C3 z −2 + C4 z −3 ),

Ci

Cn

bn = P .

Cn

n

(2.26)

Capítulo 2. Revisão Bibliográfica

25

Figura 13 – Circuito de um FIR de 4a ordem com capacitores chaveados

Fonte: (LOLIS, 2011)

2.2.4 Implementação analógica de um IIR

Para melhorar a seletividade dos filtros FIR, pode ser adicionado em seguida de

um estágio FIR um filtro IIR (SUN, 2006). O filtro IIR é um filtro que realiza a soma o

sinal atual com a saída anterior. Para isso é preciso que exista um loop de feedback do

sinal de saída. O circuito integrador é um circuito que realiza essa tipo de operação. Na

figura 14 temos um circuito integrador realizado com capacitores chaveados. Este funciona

de maneira similar ao integrador com resistores, os capacitores CA e Cf b2 operam como

resistores.

Em um primeiro momento o capacitor CA é carregado, em um segundo momento,

CA é conectado ao amplificador operacional, como a tensão V− é aproximadamente igual a

V+ (uma massa virtual), a carga que estava em CA é diretamente transferida para a saída.

O capacitor Cf b2 é descarregado enquanto CA carrega, este tem a função de controlar o

ganho total do sistema, podendo ser retirado se não existe a necessidade de ganho no

sistema.

A partir da equação de conservação de carga 2.22 é possível calcular a a diferença

de carga no circuito quando o switch S2 é fechado, conforme equação 2.27.

Vdec (n) · CA + 0 · (Cf b1 + Cf b2 ) = −Vout (n) · (Cf b1 + Cf b2 )

Capítulo 2. Revisão Bibliográfica

26

Figura 14 – Circuito de um IIR a partir de um circuito integrador com capacitores chaveados

Fonte: (LOLIS, 2011)

Vout (n)

CA

.

=−

Vdec (n)

Cf b1 + Cf b2

(2.27)

Quando o switch S2 abre, podemos dizer que a carga em Vout (n) é igual a Cf b1 /(Cf b1 +

Cf b2 ).

Se aplicarmos a conservação de carga neste caso temos:

Vdec (n + 1) · CA + Vout (n) ·

Cf b1

· (Cf b1 + Cf b2 ) = −Vout (n + 1) · (Cf b1 + Cf b2 )

Cf b1 + Cf b2

Vout (n + 1) = Vout (n) ·

Cf b1

CA

−

Vdec (n + 1).

Cf b1 + Cf b2 Cf b1 + Cf b2

(2.28)

A transformada z da equação 2.28 é a seguinte:

H(z) =

Vout (z)

CA

1

=−

·

,

Vdec (z)

Cf b1 + Cf b2 1 − β · z −1

β=

Cf b1

.

Cf b1 + Cf b2

(2.29)

É possível também ligar em série o filtro FIR com o IIR para assim conseguir uma

melhor seletividade de frequência.

O ganho em dB de um filtro IIR de um polo pode ser dado pela equação 2.30, onde

r = β. Se igualarmos H(ejω )dB = 3dB, podemos portando achar a frequência de corte ωc

Capítulo 2. Revisão Bibliográfica

27

de um filtro para um determinado valore de β, e vice versa.

H(ejω )dB = −10log10 [1 + r2 − 2r(cos(ω))]

(2.30)

Um exemplo prático de dimensionamento dos capacitores do filtro IIR foi feito. A

frequência de corte é de 3 MHz e a frequência de amostragem de 25 MHz. O β calculado foi

de 0,9, então a partir da equação 2.29 o valor de Cf b2 foi calculado para um Cf b1 = 200fF.

O valor de CA foi então calculado assumindo o ganho da função igual a 1. Os valores do

dimensionamento encontram-se na tabela 1.

Tabela 1 – Dimensionamento dos capacitores do filtro IIR

Dimensionamento

Cf b1

Cf b2

CA

Rout

Fonte: O autor

Valor

20f F

200f F

220f F

50Ω

O objetivo era que fossem feitas simulações de sinal periódico (PSS, PAC e PNOISE),

com a frequência do clock amostragem de 25 Mhz. O curto período de tempo impossibilitou

que estas simulações fossem feitas.

2.3 Características dos OTA

Na sessão 2.2.1.3 foi citado que espera-se de um OTA que este tenha um alto ganho.

Algumas das características de performance que um OTA serão discutidas a seguir. O

design de um OTA nem sempre permite que todas as características sejam optimizadas.

Para que possamos atingir as especificações desejadas, muitas vezes precisamos abrir mão

de algumas características de performance que não prejudiquem muito o circuito para o

qual este será utilizado. Como este trabalho é baseado no projeto de um OTA, as topologias

e o dimensionamento do OTA serão tratados em um capítulo a parte (Capítulo 3).

2.3.0.1 Ganho Diferencial

O ganho diferencial (Av ) é o ganho mais alto atingido pelo amplificador, ao

colocarmos um sinal pequeno na entrada e medirmos a saída. Este só pode ser medido

se compensarmos o offset para que este funcione em seu melhor ponto de operação. A

figura 15 possui um circuito que possibilita o teste do ganho diferencial de um OTA. As

resistências possuem o mesmo valor, para que o circuito opere em ganho unitário. Observe

que para altas frequências os resistores se comportam como um circuito aberto. Porém,

Capítulo 2. Revisão Bibliográfica

28

para fins de simulação os resistores podem ser bem altos, para que a frequência de transição

para alta frequência aconteça com valores pequenos. Desta forma, espera-se um alto ganho

na saída. Os valores de típicos de Av variam entre 60 − 80 dB. Para situações de alta

precisão estes valores podem ser maiores e para operações em ganho unitário, para reduzir

o consumo, este ganho pode ser inferior.

Figura 15 – Circuito para simular o ganho diferencial de um OTA

Fonte: (MALOBERTI, 2001)

2.3.0.2 Taxa de rejeição de ganho de modo comum (CMRR)

Se colocarmos um sinal de pequenos sinais de mesmo valor nos terminais V+ e

V− do circuito, para um OTA ideal, não haverá sinal algum na saída. Devido a erros no

processo de fabricação dos circuitos integrados, existe um ganho de modo comum (Acm ),

que varia de acordo com a tecnologia escolhida e com o layout dos transistores. Este ganho

é projetado para ser o menor possível. Um fator de mérito para determinar a qualidade de

um OTA é a taxa entre o ganho diferencial e o ganho de modo comum. o Acm tem valores

típicos de 10 − 30dB.

CM RR =

Av

Acm

(2.31)

2.3.0.3 Taxa de rejeição da fonte de alimentação (PSRR)

Se aplicarmos um sinal de pequenos sinais na alimentação positiva ou negativa do

circuito, haverá um sinal na saída do amplificador com uma amplificação (Aps+ ou Aps− ).

A taxa de rejeição da fonte de alimentação (PSRR) é a taxa entre o ganho diferencial e o

ganho na alimentação do OTA. Isto ocorre pois a tensão aplicada aos pinos do circuito não

é exatamente a tensão que chega para alimentar o OTA. Existem indutâncias e resistências

nas trilhas que espalham a tensão de alimentação pelo circuito. Além disso, como estamos

tratando de sinais de circuitos mistos, exitem também surtos na alimentação vindos da

Capítulo 2. Revisão Bibliográfica

29

alta frequência de chaveamento nas partes digitais do sistema, este ruído é chamado de

Ldl/dt.

2.3.0.4 Ruído

O ruído em um OTA pode ser representado por uma fonte de corrente na entrada

do circuito, conforme figura 16a. O ruído produzido por um OTA é majoritariamente

ruído branco e ruído 1/f . A frequência na qual o ruído 1/f atinge o valores médios do

ruído branco é chamado de frequência de corner. O ruído branco possui valor típico de 50

√

nV/ Hz. A frequência de corner é dependente da tecnologia em si, mas pode variar de 1

kHz a 10 Khz.

(a)

(b)

Figura 16 – Representação do ruído em um OTA (a) circuito (b) resposta em frequência

Fonte: (MALOBERTI, 2001)

2.3.0.5 Resposta DC

A figura 17 mostra como se comporta idealmente um OTA, se variarmos a tensão

DC nas entradas Vp e Vn . A tensão VOL é a tensão de saturação quando Vn > Vp e a tensão

VOH é a tensão de saturação quando Vp > Vn . Na prática esta curva só seria possível, se

nosso amplificador tivesse ganho infinito, pois o ganho é a inclinação da curva entre os

dois valores de saturação, conforme equação 2.32.

VOH − VOL

∆V →0

∆V

Ganho = Av = lim

(2.32)

Na prática esta curva é inclinada em valores entre as saturações, mas além disso

temos um offset, que na prática causa um deslocamento na curva, conforme figura 18. A

tensão de offset portanto é VOS , que é de tensão aplicada na diferença das entradas para

que a tensão na saída seja 0 V.

As tensões VOL e VOH são chamadas de swing da tensão na saída (output swing)

e são inferiores a Vdd e Vss . Já as tensões VIL e VIH são chamadas de faixa de tensão de

modo comum na entrada (Common Mode Range - CMR).

Capítulo 2. Revisão Bibliográfica

30

Figura 17 – Curva de transferência DC ideal de um OTA

Fonte: (ALLEN; HOLBERG, 2002)

Figura 18 – Curva de transferência DC "real"de um OTA

Fonte: (ALLEN; HOLBERG, 2002)

2.3.0.6 Resposta AC

A função de transferência de um OTA, costuma ter uma combinação de polos

e zeros. A figura 19 mostra uma curva de transferência típica de um OTA. Existe a

necessidade de um polo dominante para garantir a estabilidade do sistema. A frequência

onde o ganho atinge 0 dB é chamada de frequência de ganho unitário (GB).

Cada polo adicionado na função de transferência causa uma alteração de fase de

90◦ , para garantir que o sistema fique estável, é necessário que na frequência de ganho

unitário o sistema tenha fase próxima de 90◦ (conhecida como margem de fase). Valores

de até 60◦ graus de margem de fase ainda garantem boa estabilidade ao sistema. Quando

a margem de fase é muito baixa o tempo de resolução do sistema para uma alteração

brusca na entrada pode interferir no funcionamento, o tempo de resolução é representado

pela figura 20. Portanto é interessante que os polos não dominantes ω2, ω3 estejam bem

distantes de ω1, para garantir que o deslocamento de fase causado por eles não interfira

Capítulo 2. Revisão Bibliográfica

31

Figura 19 – Curva de transferência "real"AC de um OTA

Fonte: (ALLEN; HOLBERG, 2002)

de maneira drástica na margem de fase. Caso o sistema venha a operar realimentado, o

sistema não precisa respeitar a margem de fase superior a 60◦ , se este operar em frequências

inferiores ao ganho unitário, estando este limitado a fase na frequência na qual o circuito

está operando.

O slew-rate também é uma característica importante para o projeto de OTAs, e é

definido pela capacidade máxima de fornecimento de corrente e é definido geralmente em

V/µs. Ainda analisando a figura 20, dela podemos extrair o slew-rate, que é a inclinação

da curva antes de atingir estabilidade, logo que exista uma mudança brusca no sinal na

entrada do amplificador.

Capítulo 2. Revisão Bibliográfica

32

Figura 20 – Representação do tempo de resolução de um OTA

Fonte: (ALLEN; HOLBERG, 2002)

2.4 Modelagem do sistema

O Group of Integrated Circuits and Systems (GICS), do curso de engenharia elétrica

da UFPR conta com um convênio com a projeto de fabricação de circuitos integrados

Metal Oxide Semiconductor Implementation Service (MOSIS). O MOSIS é um serviço

que busca agrupar múltiplos designs em um único wafer de modo a baratear os custos

de produção dos circuitos integrados. Seu foco é voltado para protótipos e este possui

convênios com finalidade educacional, do qual o GICS faz parte. Eles também fornecem o

design kit da tecnologia em questão. Uma das tecnologias que o GICS possui acesso é a

Global Foundries 130nm, que foi a tecnologia escolhida para este projeto. As simulações

são feitas com o software de CAD Virtuoso da Cadence.

2.4.1 Bloco ampop do cadence

A estratégia usada será a de projetar um OTA, usando os modelos de transistor

fornecidos pela tecnologia, em seguida extrair as características principais do amplificador e simular fazendo o uso do bloco analógico de amplificador (ampop) da biblioteca

"adhlLib"fornecido pela Cadence, onde os parâmetros obtidos pelo modelo original serão

aplicados no bloco. As mesmas simulações serão repetidas com o bloco fornecido pela

Cadence, e comparadas com o bloco completo, para validar o modelo.

O bloco de ampop do Cadence é escrito em Verilog-A e possui os seguintes parâmetros:

• Ganho;

Capítulo 2. Revisão Bibliográfica

33

• Frequência de ganho unitário;

• Resistência de entrada (rin);

• Tensão de offset;

• Corrente de entrada (ibias);

• Corrente máxima (iin_max);

• Resistência de saída (rout);

• limitação de tensão na saída (vsoft);

É visível que este bloco não possui informações dos polos não dominantes, nem de

margem de fase, o que pode vir a prejudicar nossa resposta, porem devido ao curto tempo

deste trabalho, este será o modelo usado. Caso seja necessário o desenvolvimento de um

bloco mais complexo, este pode vir a ser um incentivo para a continuação deste trabalho.

2.4.2 Ponto de intercepção de terceira ordem (IIP3)

O ponto de intercepção de terceira ordem (IIP3) faz parte das características de

intermodulação dos dispositivos analógicos e é uma figura de mérito que representa a

linearidade do dispositivo. Se temos dois sinais fortes em frequências muitos próximas,

estes produzem distorções de intermodulação (IMD). O ganho não linear de um bloco

pode ser modelado por um polinômio conforme equação 2.33.

y0 = a0 + a1 xi + a2 x2i + a3 x3i + ... =

∞

X

ak xki

(2.33)

k=0

Esta função possui geralmente característica de função impar, portanto os valores

de k impar possuem amplitude dominante com relação aos valores de k pares. O mais

importante termo desta equação é o valor de terceira ordem. Se pegarmos a figura 21

como exemplo, tempos dois sinais próximos um do outro, estes produzem uma distorção

de terceira ordem. A distorção de intermodulação de terceira ordem (IMD3) é representa

pelo ∆3 . O interesse é que o IMD3 seja pequeno, consequentemente o sistema em questão

será altamente linear. A intermodulação de terceira ordem pode cair em uma faixa do

espectro que prejudique outros canais do espectro.

Se aumentarmos o valor dos sinais principais, pode-se traçar as curvas dos sinais

de entrada e dos IMD3, antes do circuito saturar, ambos se comportam como retas

acendentes, conforme figura 22. Se extrapolarmos ambas as retas, pode-se encontrar o

ponto de interceptação das duas curvas, quando o sinal de entrada em teoria produziria

Capítulo 2. Revisão Bibliográfica

34

Figura 21 – Representação de dois sinais produzindo intermodulação de terceira ordem

Fonte: (GU, 2006)

Figura 22 – Representação gráfica do cálculo de IIPn

Fonte: (GU, 2006)

Capítulo 2. Revisão Bibliográfica

35

o equivalente a sua componente de terceira ordem, este é o que chamamos de ponto de

intercepção de terceira ordem (IIP3).

A formula para calcularmos o IIP3 a partir de um valor de IMD3 está na equação

2.34, onde S é a potencia do sinal de entrada:

1

IIP3 = (3S − IM D3 )

2

(2.34)

36

3 Projeto do OTA

Este trabalho consiste no projeto de um OTA que será utilizado para validar o

integrador de um filtro IIR. Tem-se a pretensão de utilizar este OTA para validar o filtro

completo da tese (LOLIS, 2011). Foi desta que algumas das especificações do OTA foram

extraídas.

3.1 Especificações do OTA desejado

O trabalho será um OTA para validar o circuito da figura 14. A frequência de

amostragem é de 25 MHz. Os capacitores serão calculados para a frequência de corte de 3

MHz. Não existe a necessidade de um ganho alto, pois o circuito irá operar realimentado, o

valor estabelecido de ganho minimo do OTA em malha aberta é de 30 dB, que é um valor

baixo se comparado com o estado da arte. Pensando nisso, o foco foi em baixo consumo,

com corrente inferior a 100 µA. A tensão de alimentação é de 1, 6 V que é a tensão padrão

da tecnologia. A margem de fase foi definida maior que 60◦ .

Tabela 2 – Especificações do OTA

Especificação

Frequência de amostragem (fs )

Frequência de corte do filtro (fc )

Ganho

Frequência de ganho unitário (GB)

Consumo de corrente

Tensão de alimentação

Margem de fase

Fonte: O autor

Valor

25 MHz

3 MHz

>30 dB

>25 MHz

>100 µA

1, 6 V

>50◦

3.2 Topologia

A topologia escolhida para o OTA é a da figura 23. A motivação da escolha foi

que este é um circuito de baixa complexidade, devido ao curto tempo para este trabalho,

era importante que uma topologia simplificada fosse escolhida. Esta é uma topologia de

dois estágios, onde o primeiro estágio é constituído por um par diferencial, este par é

desbalanceado por um espelho de corrente formado por M 3 e M 4, para transformar as 2

entradas em uma saída. Portanto, devido ao espelho de corrente, a corrente IDS em M 4 é

equivalente a corrente em M 1. A saída do primeiro estágio, que é o nó entre M 4 e M 2, é a

Capítulo 3. Projeto do OTA

37

diferença de corrente entre M 1 e M 2. O segundo estágio é chamado de fonte comum onde

a entrada do amplificador é a base do transistor M 6, e o transistor M 7 se comporta como

fonte de corrente. Opta-se por um segundo estágio simples para melhorar a amplitude do

sinal de saída do amplificador.

Figura 23 – Topologia de OTA escolhida para o projeto

Fonte: (ALLEN; HOLBERG, 2002)

O capacitor Cc é chamado de capacitor de compensação e ele é necessário, pois

cada estágio do circuito insere um polo na função de transferência e os polos encontram-se

muito próximos um do outro, quando os polos estão muito próximos um do outro, é difícil

garantir os 60◦ de margem de fase pois o segundo polo desloca a fase mais 90◦ , se isto

ocorre antes do ganho unitário, a margem de fase fica próxima de 0◦ . A figura 24 representa

o circuito equivalente de pequenos sinais sem o capacitor de compensação. Os polos da

função deste circuito são as equações 3.1 e 3.2 e possuem a mesma ordem de gradeza,como

estamos tratando de transistores com W/L parecidos, os valores tendem a ser próximos

um do outro.

p01 =

p02 =

−1

RI CI

(3.1)

−1

RII CII

(3.2)

A técnica de adicionar um capacitor entre o primeiro e o segundo estágio é chamado

de compensação de Miller, observamos como fica o circuito equivalente pequenos sinais

quando adiciona-se o capacitor, na figura 25.

Capítulo 3. Projeto do OTA

38

+

+

+

Vin

VI

g mIVin

g mIIVI

RI CI

-

Vo

RII CII

-

Figura 24 – Circuito equivalente do OTA de dois estágios

Fonte: O autor

Cc

+

+

+

Vin

VI

g mIVin

RI CI

-

g mIIVI

-

Vo

RII CII

-

Figura 25 – Circuito equivalente do OTA com capacitor de compensação

Fonte: O autor

Ambos os polos da função são alterados com o capacitor, os novos polos são as

equações 3.3 e 3.4. Quanto temos CII muito maior que Cc o segundo polo pode ser reduzido

para aproximadamente a equação 3.5. A figura 26 mostra o que acontece com a resposta

em frequência do circuito quando acrescenta-se o capacitor de compensação. Na prática

o primeiro polo é reduzido em frequência e o segundo polo é aumentado, portante é

preciso que o capacitor de compensação seja escolhido de modo que os polos estejam

suficientemente afastados um do outro para que a margem de fase desejada seja garantida.

A função também apresenta um zero, no semi-plano direito, que pode ser calculado pela

equação 3.6 e precisa ser projetado muito maior que GB para garantir a estabilidade do

sistema.

−1

gmII RI RII Cc

(3.3)

−gmII Cc

CI CII + CII Cc + CI Cc

(3.4)

p1 =

p2 =

Capítulo 3. Projeto do OTA

39

−gmII

p2 ∼

=

CII

z1 =

gmII

Cc

(3.5)

(3.6)

Figura 26 – Representação gráfica do efeito do capacitor de compensação na resposta em

frequência do OTA

Fonte: (ALLEN; HOLBERG, 2002)

3.3 Dimensionamento

Para o dimensionamento dos transistores de nosso OTA, primeiro é preciso levar

em consideração algumas formulas essenciais para o cálculo. O dimensionamento é baseado

nos valores de transcondutância gm e de admitância gds dos transistores. As formulas

usadas no cálculo são aproximadas, na prática o simulador leva em conta para a simulação

dos transistores, modelos complexos. Os cálculos iniciais serão feitos para se obter uma

aproximação dos valores de W/L dos transistores, para que depois em simulação, seja

possível ajustar um pouco os valores.

A equação 3.7 e a equação 3.8 são os valores de gm e gds usados nos cálculos. Porém

evitou-se usar o valor de gds aproximado, contatou-se com as primeiras simulações, que a

aproximação do gds destoa muito do valor atingido em simulação.

gm ∼

=

K 0W

2K 0 (W/L)|ID | ∼

(VGS − VT )

=

L

q

(3.7)

Capítulo 3. Projeto do OTA

40

gds ∼

= λID

(3.8)

As varáveis destas equação são as seguintes:

• K 0 = parâmetro de transcondutância [ A/V2 ]

• Vt = tensão de threshold (limiar) do transistor [ V ]

• ID = corrente de dreno do transistor [ A ]

• VGS = tensão entre gate e fonte (source) do transistor [ Vgs ]

• λ = parâmetro de modulação do comprimento do canal [ V−1 ]

• µ0 = mobilidade de portadores de canal [ cm2 /V.s ]

• Cox = capacitância por unidade de área do óxido no gate do transistor [ F/cm2 ]

• ox = permissividade do SiO2 [ F/cm ]

• tox = espessura do óxido [ cm ]

O K 0 é um valor que varia entre os transistores PMOS e NMOS e é dependente da

tecnologia, seu valor pode ser calculado pela formula 3.9 e enquanto Cox é dependente da

tecnologia, µ0 depende do tipo do canal do transistor ( P ou N), comprovando que este

depende do tipo de transistor. Cox é calculado pela formula 3.11, onde 0 é uma constante

e tox é dependente da tecnologia. Outro parâmetro de transcondutância usado nos cálculos

é o β que é calculado pela formula 3.10.

K0 ∼

= µ0 Cox

β = (K 0 )

W

L

Cox =

[ A/V 2 ]

ox

tox

(3.9)

(3.10)

(3.11)

Para simplificar a notação Si = Wi /Li = (W/L)i para se referir a proporção entre

o W que é a largura do canal e L que é o comprimento do canal do transistor e i refere-se

a notação numérica dos transistores do circuito da figura 23.

O dimensionamento segue o procedimento apresentado por (ALLEN; HOLBERG,

2002). Assume-se os seguintes valores de transcondutância e admitância:

Capítulo 3. Projeto do OTA

41

• gmI = gm1 = gm2

• gmII = gm6

• 1/RI = (gds2 + gds4 )

• 1/RII = (gds6 + gds7 )

A seguir as relações importantes do circuito da figura 23 :

Slew-rate:

I5

Cc

(3.12)

Av1 =

gm2

gds2 + gds4

(3.13)

Av2 =

gm6

gds6 + gds7

(3.14)

SR =

Ganho do primeiro estágio:

Ganho do segundo estágio:

Frequência de ganho unitário:

GB =

gm2

Cc

Polo do estágio de saída:

p2 =

Zero do semi-plano direito:

z1 =

[ rad/s ]

(3.15)

−gm6

CL

(3.16)

gm6

Cc

(3.17)

Tensão de modo comum máxima:

Vin(max)

I5

= VDD −

β3

!1/2

− |VT 03(max) | + VT 1(min)

(3.18)

+ VT 1(max) + VDS5 (sat)

(3.19)

Tensão de modo comum mínima:

Vin(min) = VSS

I5

−

β1

!1/2

Tensão de saturação:

VDS (sat) =

2IDS

β

!1/2

(3.20)

Capítulo 3. Projeto do OTA

42

Para este procedimento de dimensionamento as seguintes especificações precisam

ser conhecidas:

• Frequência de ganho unitário (GB)

• Faixa de tensão de modo comum na entrada (CMR)

• Capacitância de carga (CL )

• Slew-rate (SR)

• Swing da tensão de saída

O ganho diferencial Av e o consumo de corrente Itotal serão consequência dos valores

estabelecidos pelas outras especificações.

Para que se obtenha 60◦ de margem de fase, o polo 2 precisa ser colocado numa

frequência 2,2 vezes maior que GB e o zero precisa estar a pelo menos 10 vezes a frequência

GB. Assumindo esta relação podemos, a partir formula de GB(equação 3.15) e da formula

do zero(equação 3.17), chegar na seguinte condição:

gm6

gm2

> 10

Cc

Cc

(3.21)

também podemos derivar a equação 3.22, com as equações 3.15 e 3.16.

gm6

gm2

> 2.2

C2

Cc

(3.22)

Se combinarmos as duas equações, chegamos na relação da equação 3.23. Portanto,

com a especificação de CL pode-se calcular Cc . Com Cc e o slew-rate pode-se calcular I5 ,

conforme equação 3.24.

Cc > (2, 2/10)CL

(3.23)

I5 = SR(Cc )

(3.24)

A relação do transitor M 3 pode ser calculada a partir da formula da tensão de

modo comum mínima, conforme equação 3.25.

S3 = (W/L)3 =

(K30 )[VDD

I5

− Vin(max) − |VT 03(max) | + VT 1(min) ]2

(3.25)

Capítulo 3. Projeto do OTA

43

Como temos GB e Cc , podemos calcular gm2 , conforme equação 3.26. E usando a

equação 3.7 pode-se calcular a proporção de M 2, conforme equação 3.27.

gm2 = GB(Cc )

(3.26)

2

gm2

S2 = (W/L)2 =

(K20 )(I5 )

(3.27)

Pode-se calcular a tensão VDS5 com a equação de tensão de modo comum máxima.

E então calcular a proporção de M 5 conforme equações 3.28 e 3.29.

VDS5 = Vin(min) − VSS

I5

−

β1

S5 = (W/L)5 =

!1/2

− VT 1(max)

2(I5 )

0

K5 (VDS5 )2

(3.28)

(3.29)

Com a equação 3.22 pode-se calcular gm6 .

gm6 = 2.2(gm2 )(CL /Cc )

(3.30)

Se assumirmos que VDS6 = VDS6 (min) = VDS6 (sat) = VDD − Vout (max) pode-se

calcular S6 .

S6 = (W/L)6 =

gm6

0

K6 VDS6 (sat)

(3.31)

Podemos calcular a corrente I6 com as equações 3.32 e 3.33. Escolhe-se a maior

das duas correntes. Se a corrente maior for a da equação 3.32, é preciso recalcular S6 a

partir da equação 3.33.

I6 =

2

gm6

(2)(K60 )(W/L)6

(3.32)

(W/L)6

I1

(W/L)3

(3.33)

I6 =

A relação S7 pode ser calculada com a equação 3.34.

S7 = (W/L)7 = (W/L)5

I6

I5

(3.34)

Para dimensionar os transistores foi feita uma primeira simulação DC do circuito,

todos com L mínimo (120nm) e com W qualquer, para que fossem extraídos os valores de

Capítulo 3. Projeto do OTA

44

VT 1 (max), VT 1 (min), VT 03 (max). Os valores (max) foram extraídos quando a diferença

de V + e V− é máxima (1, 6 V) e o valor (min) quando a diferença é mínima (0 V). Os

valores de Kp0 e Kn0 foram calculados a partir da formula 3.9 onde o µ0p , µ0n e tox foram

extraídos do modelo do transistor para da tecnologia e a constante ox = 3, 45 ∗ 10−11 F/m.

Os valores usados foram os seguintes:

• Kn0 = 115 µA/V2

• Kp0 = 516 µA/V2

• vt1 (max) = 470 mV

• vt1 (min) = 402 mV

• vt03 (max) = 402 mV

• CL = 2 pF

• Slew − rate = 40 V/µs

• GB = 40 MHz

• Vin (max) = 1, 5 V

• Vin (min) = 0, 7 mV

• Vds6 = 100 mV

Algumas observações podem ser feitas:

• O slew-rate foi escolhido, imaginando que o circuito chaveie a tensão nominal 1, 6 V

na frequência de 25 MHz, bem acima do que irá acontecer na prática, pois sabe-se

que o circuito integrador ira carregar apenas a variação de carga de um período a

outro, esse valor foi mantido, pois este influencia a corrente do primeiro estágio, que

é muito inferior a corrente do segundo estágio, não afetando de maneira drástica o

consumo real do circuito.

• A tensão de modo comum mínima Vin (min) está bem acima do valor ideal (deveria

estar próxima a GND) para viabilizar o cálculo, pois este influencia inversamente S3 ,

caso este esteja pequeno demais, a corrente I6 sobe para valores muito altos devido

a equação 3.33.

• GB está acima dos 25 MHz para que o circuito possa operar com um pouco de ganho

se for preciso.

Os valores calculados estão na tabela 3, referentes ao circuito da figura 23.

Capítulo 3. Projeto do OTA

45

Tabela 3 – Dimensionamento do OTA

Dimensionamento Valor

S1

1,34

S3

15,3

S5

13,6

S6

96

S7

42,7

I5

55 µA

I7

17,6 µA

Fonte: O autor

3.4 Circuitos de suporte

Para testar o OTA, foi utilizado o circuito da figura 27. Neste caso, o amplificador

está em malha aberta e precisa de correção de offset para funcionar em ganho máximo,

portanto foi feito primeiro uma simulação DC para extrair o offset, para que então as

outras simulações fossem feitas. Foram feitos 4 testes a seguir a configuração de cada teste:

• Resposta DC: fontes: DC: V 1 = sweep de 0 a 1, 6 V, V 2 = 0 V;

• Resposta AC e Ruído: fontes: DC: V 1 = (0, 8 V + offset), V 2 = 0, 8 V; AC: V 2 = 1

V;

• Transiente: fontes: DC: V 1 = 0, 8 V + offset, V 2 = 0, 8 V; VSIN: V 2 = [VP P = 1, 6

V, f = 1 MHz];

A tensão Vbias usada para gerar as correntes I7 e I5 foi gerada a partir de um

espelho de corrente conforme figura 28. Nota-se que as proporções de M 7 e M 5 ja foram

calculadas para que com a mesma tensão Vbias , ambos forneçam as correntes calculadas.

A proporção W/L do transistor M pol é igual a M 7, e a corrente I7 é a corrente que

deseja que passe por M 7. Sabe-se que este espelho de corrente não é preciso, pois devido

aos efeitos de modulação do canal, as tensões VGS de M pol e M 7 acabam não sendo

exatamente iguais, portanto sabe-se que os valores de W/L de M pol terão de ser ajustados

para fornecer a corrente calculada no dimensionamento.

Capítulo 3. Projeto do OTA

46

U1

C1

V1

V2

Figura 27 – Circuito de teste usado para testar o OTA

Fonte: O autor

I7

Mpol

M7

M5

Figura 28 – Circuito de espelho de corrente usado para gerar Vbias

Fonte: O autor

Capítulo 3. Projeto do OTA

47

3.5 Resultados Obtidos

Primeiro foi feita uma simulação da curva DC do circuito, porém observou-se que

as correntes I5 e I7 estavam abaixo do valor calculado, para chegar no valor da tabela 4

foi preciso diminuir W/L do transistor M pol para ((W/L)7 /1.3). As correntes medidas

foram:

• I5 = 13,55 µA

• I7 = 60,73 µA

O comprimento de canal dos transistores M 3, M 4, M 5, M 7 e M pol foram aumentados para 360nm, para reduzir os efeitos de modulação do canal, já que todos eles funcionam

como espelhos de corrente. Os valores de W/L foram arredondados, para facilitar o layout.

Nas primeiras simulações AC, constatou-se que a frequência de ganho unitário estava

abaixo do calculado, esta estava abaixo de 25 MHz, porém a margem de fase estava em

70◦ , acima do calculado. O valor do capacitor Cc foi então reduzido para 200 pF, para

aumentar a frequência GB.

Os valores finais de dimensionamento são os seguintes:

Tabela 4 – Dimensionamento do OTA após correções

Dimensionamento

Valor

W/L1

2 (L=120nm)

W/L3

15 (L=360nm)

W/L5

14 (L=360nm)

W/L6

96 (L=120nm)

W/L7

43 (L=360nm)

W/Lpol

33 (L=360nm)

Cc

200 pF

I5

13,55 µA

I7

60,73 µA

Fonte: O autor

Na figura 29 temos o comportamento DC do OTA. Pode-se extrair desta curva o

offset, o swing de tensão de saída e a faixa de tensão de modo comum. Os valores portanto

são os seguintes:

• Offset = 8,7 mV

• Output swing = 0, 05 − 1, 55 V

• Common mode range = 795 − 825 mV

Capítulo 3. Projeto do OTA

48

DC Response

1.75

Mon Dec 5 01:0...1

1.5

Vout (V)

1.25

M1: 808.70667mV 800.02359mV

1.0

.75

.5

.25

0.0

-.25

700.0

750.0

800.0

Vin (mV)

850.0

900.0

Figura 29 – Curva de comportamento DC do OTA

Fonte: O autor

Na figura 30 temos a resposta em frequência do OTA. Pode-se extrair desta curva o

ganho diferencial, a frequência de ganho unitário e a margem de fase. Os valores portanto

são os seguintes:

• Ganho diferencial = 41,37 dB

• Frequência de ganho unitário = 44,3 MHz

• Margem de fase = 52◦

A frequência de ganho unitário é maior que a frequência de amostragem (25 MHz)

e ainda temos uma margem caso o circuito venha a ser usado com um pouco de ganho.

A margem de fase está abaixo de 60◦ , porém como já havia sido comentado, o circuito

irá funcionar realimentado, portanto esta margem de fase não deve ser um problema. O

ganho diferencial está abaixo dos valores citados pela literatura (60 a 80 dB). O ganho é

baixo devido a exigência de consumo do circuito, também devido ao tamanho pequeno

da tecnologia usada, pois nesta topologia o L dos transistores é diretamente proporcional

ao ganho do circuito. Se houvesse necessidade de aumentar o ganho, poderia ser avaliada

outra topologia, melhor adaptada a transistores com o L da tecnologia utilizada.

Na figura 31 temos a resposta transiente do OTA operando em saturação. Pode-se

extrair desta curva o slew-rate, que observa-se que é diferente para a saturação positiva e

negativa. Os valores são os seguintes:

• Slew-rate de saturação positiva = 66 V/µs

• Slew-rate de saturação negativa = 26 V/µs

Capítulo 3. Projeto do OTA

49

phase(GainAC)

Mon Dec 5 01:0...1

V1

50.0

50.0

Gain (dB)

-50.0

Phase (deg)

0.0

25.0

0.0

-100.0

-25.0

-150.0

-200.0

-50.0

M2: 44.2353MHz -128.009deg

-250.0

-75.0

-300.0

2

10

3

10

4

10

5

6

7

10 10 10

freq (Hz)

8

10

9

10

10 10

Figura 30 – Resposta em frequência do OTA, curvas de ganho e fase

Fonte: O autor

O circuito havia sido calculado para um slew-rate de 40 V/µs, portanto o valor

está um pouco diferente, mas ainda assim aceitável para as utilizações que se espera do

circuito. É possível que a diferença de subida e decida de saturação seja em função da

diferença no gds dos transistores M 3 e M 1 no estágio de entrada, se houver necessidade

de regular o slew-rate, alterações finas no dimensionamento do circuito podem ser feitas.

Transient Response

1.75

Mon Dec 5 00:5...1

1.5

Vout (V)

1.25

1.0

dx: 35.48891ns

dy: 886.883mV

s: 24.99044MV/s

.75

.5

.25

0.0

-.25

0.0

.5

1.0

time (us)

1.5

2.0

Figura 31 – Resposta transiente do OTA

Fonte: O autor

Na figura 32 temos a resposta de ruído do OTA, vista da saída do circuito e

também da entrada do circuito. Para comparação o ruído em 1 KHz é de −106 dB, que é

comparável aos −140 dB típicos ((ALLEN; HOLBERG, 2002)).

A partir da curva de ruído, pode-se calcular a figura de ruído para uma carga de

50 Ω a partir da equação 3.35 (GU, 2006). A figura 33 possui a figura de ruído do OTA. É

possível observar o ruído 1/f , porém a frequência de corner está bem acima do esperado (

próximo de 10 Mhz ), isso se deve muito provavelmente pelo fato de estarmos trabalhando

Capítulo 3. Projeto do OTA

50

output noise; V / sqrt(Hz)

-50.0

1

-75.0

-100.0

-125.0

-150.0

-175.0

-200.0

1.0kHz

-225.0

2

10

3

10

V1

-90.0

-65.46204dB

Vin/sqrt(Hz) (dB)

Vout / sqrt(Hz) (dB)

Mon Dec 5 01:0...1

V1

4

10

-100.0

-106.8363dB

-110.0

-120.0

-130.0

-140.0

1.0kHz

-150.0

5

6

7

10

10

10

freq (Hz)

8

10

9

10

10

2

10

3

10

10

4

5

10

(a)

6

7

10

10

10

freq (Hz)

8

10

9

10

10

10

(b)

Figura 32 – Resposta de ruído do ota a) Visto de Vout b) Visto de Vin

Fonte: O autor

com uma tecnologia muito pequena. Pode-se futuramente avaliar se um aumento no L dos

transistores do OTA causam uma melhora na resposta ao ruído.

N F = (Vin2 /Hz)db − (−174 − 30 − 10log10 (50))

(3.35)

1

V1

90.0

NF (dB)

80.0

80.0957dB

70.0

60.0

50.0

40.0

1.02187kHz

30.0

2

10

3

10

4

10

5

6

7

10

10

10

freq (Hz)

8

10

9

10

10

10

Figura 33 – Figura de ruído do OTA

Fonte: O autor

A figura 34 possuí as curvas de IMD1 e IMD3 e o ponto de encontro entre as duas

é o IIP3 do OTA em malha aberta. Este portanto possui um IIP3 de 24,1 dBm.

Capítulo 3. Projeto do OTA

51

1

V1

50.0

1dB/dB

Pout (dBm)

25.0

0.0

-25.0

3dB/dB

-50.0

M5: 24.14794dBm 5.877818dBm

-75.0

3rd Order freq = 900K

1st Order freq = 1M

-100

-10.0

0.0

10.0

PI (dBm)

20.0

Figura 34 – Calculo do IIP3 do OTA

Fonte: O autor

30.0

52

4 Modelo comportamental do OTA

Foi feita uma análise do código do modelo de AMP-OP do Cadence e chegou-se

no circuito da figura 35. A corrente de entrada é limitada pelo parâmetro IIN_MAX. A

corrente na saída é limitada por gm∗(Vout (max)−Vdd +Vsof t ) e gm∗(Vout (min)−Vss −Vsof t ).

Voffset

Vin_p

- +

Cout

+

R in

+

Vout

Vin

g mVin

Vin_n

R out

-

RI C I

-

Figura 35 – Circuito equivalente do modelo OTA do Cadence

Fonte: O autor

A resistência R1 , a capacitância C1 e gm são calculados pelos seguintes cálculos

com os parâmetros fornecidos:

IIN _M AX

SR

(4.1)

gm = 2π(GB)(C1 )

(4.2)

C1 =

r1 =

GAIN

gm

(4.3)

4.1 Dimensionamento

Os parametros do modelo foram encontrados a partir de técnicas de bottom-up,

onde os valores foram alterados sistematicamente até que a curva transiente do modulo

se comportasse similar a curva de OTA com transistores. Os valores dos parâmetros do

OTA modelo estão na tabela 5. Nem todos os parâmetros do modelo foram utilizados,

observa-se que o modelo possui valores padrão para todos os parâmetros, portanto, aqueles

parâmetros que não influenciaram nas analises realizadas ficaram com os valores padrões.

Capítulo 4. Modelo comportamental do OTA

53

Tabela 5 – Parâmetros do OTA utilizado de modelo

Parâmetros

Valor

Ganho

117,1(41,37 dB)

GB

44,26 MHz

offset

8,7 mV

Slew-Rate

26 V/µs

vsof t

0,1 V

Fonte: O autor

4.2 Resultados Obtidos

Na figura 36 temos a resposta em frequência do modelo do ota. Pode-se observar

que o comportamento dos dois é muito próximo até a frequência de ganho unitário, com

exceção da margem de fase, pois infelizmente este modelo não permite que se altere a

margem de fase e este também não possui opção de adicionar mais polos a função de

transferência do OTA.

Mon Dec 5 01:5...1

-160.0

40.0

-180.0

20.0

-200.0

0.0

-220.0

-20.0

-240.0

-40.0

-260.0

Phase (deg)

Gain (dB)

phase(GainAC)

60.0

-60.0

-280.0

2

10

3

10

4

10

5

6

7

10 10 10

freq (Hz)

8

10

9

10

10 10

Figura 36 – Resposta em frequência do modelo do OTA

Fonte: O autor

Na figura 37 temos a resposta transiente do OTA operando em saturação. O

slew-rate acaba se comportando igual na subida e na descida do sistema, porém o ota

dimensionado possui valores diferentes de slew-rate para subida e descida. Isto pode vir a

influenciar a resposta do filtro, caso este venha a carregar grandes cargas nos capacitores,

porém em funcionamento padrão, este não deve ser um problema, pois assume-se que os

capacitores vão operar sempre carregados. A valor de Vsat (max) = 1, 58 V, ficou muito

próximo do valor 1, 55 V encontrado no OTA dimensionado, este valor foi regulado variando

a variável Vsof t .

Capítulo 4. Modelo comportamental do OTA

Transient Response

1.75

54

Mon Dec 5 01:5...1

1.5

Vout (V)

1.25

1.0

.75

.5

.25

0.0

0.0

.5

1.0

time (us)

1.5

2.0

Figura 37 – Resposta transiente do modelo do OTA

Fonte: O autor

55

5 Conclusão

Este foi um projeto completo, envolvendo o estudo de sinais e sistemas e também

o projeto de um OTA, com especificações voltadas para funcionar como filtro IIR em

frequência de amostragem de 25 MHz. O OTA projetado apresentou valores consistentes

com os valores da literatura, com exceção do ganho diferencial, que ficou abaixo da média.