Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

I.1. O SER HUMANO E O COMPUTADOR

Desde o seu aparecimento na Terra o homem percebeu que para dominar a natureza e os outros

animais necessitava de ferramentas (próteses) para ampliar sua capacidade física. Desta forma, inventou

a alavanca, o machado, a lança e a faca, entre outras ferramentas.

Com a evolução o homem começou a construir objetos que o auxiliavam no cálculo, como, por

exemplo o ábaco. E desde então o homem vem tentando construir máquinas cada vez mais poderosas

que sejam como próteses para o seu próprio cérebro, auxiliando-o na solução de problemas cada vez

mais complexos.

De forma simplificada, e sem preocupação com exatidão biológica, podemos analisar o homem

segundo o esquema abaixo:

M

O

CÉREBRO

SENTIDOS

PARTE

DECISÓRIA

MEMÓRIA

MÚSCULOS

E

N

SER HUMANO

I

O

E

X

T

E

R

Figura I.1

Como visto acima, o homem é composto de sentidos, cérebro e músculos. O cérebro, por sua

vez, é subdividido em memória e parte decisória.

Através dos sentidos o homem recebe do meio externo todas as informações. Estas podem ser

captadas por meio da visão, da audição, do olfato, do paladar e do tato.

As informações podem ser armazenadas na memória, que pode guardar informações visuais

(memória visual), auditivas (memória auditiva) e assim por diante.

Os músculos, que são comandados pela parte decisória do cérebro, são os instrumentos através

dos quais o homem age sobre o meio externo.

Um exemplo de comportamento pode mostrar de que forma se relacionam os quatro

componentes básicos do ser humano. Um centro-avante de futebol, dentro da pequena área adversária vê

uma bola alta que lhe é cruzada da linha de fundo. Na memória deste jogador existe a lembrança de que,

toda vez que a bola vem pelo alto, ele deve pular e cabecea-la de encontro ao gol adversário. Em frações

de segundo ele busca na memória esta informação e a parte decisória de seu cérebro decide que ele deve

pular. O cérebro então comanda os músculos de seu corpo a saltar e atingir a bola com a cabeça, de

forma a marcar o gol.

O computador é muito semelhante a este esquema simplificado do ser humano. Um computador

é composto basicamente de processador, memória, dispositivos de entrada e dispositivos de saída. A

seguir temos o esquema simplificado de um computador.

___________________________________________________________________________________

I.1

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

O

DISPOSITIVOS

M

DISPOSITIVOS

PROCESSADOR

DE

DE

ENTRADA

SAÍDA

N

E

MEMÓRIA

COMPUTADOR

I

R

O

E

X

T

E

Figura I.2

O processador é a parte do computador que faz os cálculos e controla todas as outras partes.

Podemos fazer uma analogia entre o processador e a parte decisória do cérebro humano.

A memória do computador funciona de forma semelhante à memória do homem, guardando

informações que podem ser colocadas e retiradas pelo processador a qualquer momento.

Através dos dispositivos de entrada é possível fazer entrar informações no computador. Como

um exemplo de dispositivo de entrada temos o teclado. Através do teclado uma pessoa pode digitar

informações que serão utilizadas pelo computador. Como outros exemplos de dispositivos de entrada

temos "mouse", "scanner", unidade de disco flexível, "joystick" etc. Comparando com os seres

humanos, os dispositivos de entrada são os sentidos (visão, audição etc).

Os dispositivos de saída são os responsáveis pela atuação do computador no mundo externo (da

mesma forma que os músculos no ser humano). Como exemplos de dispositivos de saída temos:

impressora, "plotter", monitor de vídeo, unidade de disco flexível etc.

A relação entre as partes do computador pode ser exemplificada na figura I.3.

Uma secretária digita um relatório utilizando um teclado (dispositivo de entrada). O processador

controla a entrada do texto e armazena-o organizadamente na memória. Ao final da digitação, a

secretária digita um comando para imprimir o relatório. Este comando é interpretado pelo processador,

que irá transferir o texto, que está na memória, para a impressora (dispositivo de saída). Após isto a

secretária pode digitar um outro comando para salvar (gravar) em disco este relatório.

___________________________________________________________________________________

I.2

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

RELATÓRIO

astrudud

astrudud

astrudud

SECRETÁRIA

PROCESSADOR

IMPRESSORA

TECLADO

RELATÓRIO

HD... CD...PD

(memória de massa)

askskclclclcl

askskclclclcl

askskclclclcl

askskclclclcl

MEMÓRIA

Figura I.3

___________________________________________________________________________________

I.3

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

I.2. O SURGIMENTO DOS COMPUTADORES

Em 1822, o matemático inglês Charles Babage criou uma máquina que executava

automaticamente uma seqüência pré definida de operações matemáticas. Esta máquina é considerada

como o primeiro computador e é conhecida hoje como máquina de Babage. A máquina de Babage era

inteiramente mecânica, e deste fato resultava em uma precisão pequena devido às dificuldades

tecnológicas da época. No entanto o que diferia a máquina de Babage das calculadoras mecânicas, já

existentes na época de suainvenção era a introdução do conceito de programação. Este conceito muito

importante só veio a ser implementado na prática mais de um século depois.

Durante a Segunda Grande Guerra, esforços de ambas as partes resultaram na construção de

computadores eletromecânicos que eram usados para cálculos de balística.

O computador eletrônico surgiu dois anos após o fim da guerra, em 1947. Dois pesquisadores da

Universidade da Pensilvânia desenvolveram um computador que chamaram de ENIAC. O ENIAC

possuía nada menos de 18.000 válvulas a vácuo. Por ser totalmente eletrônico as informações eram

transferidas em velocidade milhares de vezes maior que nos seus precursores eletromecânicos.

Os mesmos pesquisadores que criaram o ENIAC começaram a desenvolver uma nova versão de

computador eletrônico que foi comercializada pela Sperry Rand Corporation em 1951, sendo portanto o

primeiro computador comercial.

Com o surgimento e aplicação da tecnologia dos semicondutores as válvulas dos computadores

foram substituídas por circuitos transistorizados, diminuindo o tamanho e o consumo dos computadores.

Desde o inicio dos anos 50 até os dias de hoje, empresas como a IBM, a Burroughs, entre outras

milhares de empresas no mundo todo, vêm lançando todo ano computadores cada vez mais velozes, que

consumem cada vez menos energia elétrica e ocupam espaços cada vez menores.

___________________________________________________________________________________

I.4

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

I.3. OS SISTEMA DE NUMERAÇÃO E O COMPUTADOR:

I.3.1. O SISTEMA DECIMAL

O sistema de numeração que usamos no dia-a-dia é o decimal, ou sistema de base 10. A origem

do sistema decimal foi o costume adquirido pelos homens de contar usando os dedos das mãos. Como

são dez dedos o sistema decimal possui dez dígitos ou algarismos (0,1,2,3,4,5,6,7,8,9). No sistema

decimal cada algarismo tem um valor absoluto e um valor relativo. O valor absoluto do algarismo é a

quantidade que o algarismo representa. Já o valor relativo depende da posição em que o algarismo está

colocado dentro do número. Para esclarecer melhor o valor relativo dos algarismos dentro de um

número, vejamos o seguinte exemplo:

O número 8579 possui 4 algarismos. O algarismo "9", que está colocado mais a direita,

representa a quantidade de unidades, o algarismo "7" representa a quantidade de dezenas, o "5" a

quantidade de centenas e o "8" a quantidade de milhares. Podemos então afirmar que 8579 são 8

milhares (ou 8 conjuntos de mil unidades) mais 5 centenas (ou 5 conjuntos de cem unidades) mais 7

dezenas (ou 7 conjuntos de dez unidades) mais 9 unidades, ou seja:

8579 = 8 X 1000 + 5 X 100 + 7 X 10 + 9 X 1

ou

8579 = 8 X 103 + 5 X 102 + 7 X 101 + 9 X 100

Portanto, qualquer número decimal pode ser decomposto em componentes de potências de base

10.

I.3.2. O SISTEMA BINÁRIO

Um computador para armazenar números em base 10 teria de ser capaz de possuir circuitos que

assumissem dez estados de tensão distintos, que representariam os algarismos decimais (0,1,..,9). É

óbvio que um computador assim seria de implementação complicada. Por esta razão, desde o início os

computadores foram idealizados para que as quantidades neles armazenadas estivessem em sistema

binário (base 2), onde só existem dois algarismos (0 e 1) e, portanto, os circuitos eletrônicos só

necessitam assumir dois estados distintos.

Assim como na base 10, os algarismos em base 2 têm um valor absoluto e um valor relativo que

depende da posição em que o algarismo está colocado no número.

Também de forma similar ao sistema decimal, qualquer número no sistema binário pode ser

decomposto em componentes de base 2, como por exemplo:

(1101)2 = 1 X 23 + 1 X 22 + 0 X 21 + 1 X 20

ou

(1101)2 = 1 X 8 + 1 X 4 + 0 X 2 + 1 X 1 = 13

Como no exemplo acima, toda vez que representarmos um número em uma base que não a base

10, este número estará entre parênteses e com a base expressa à direita e abaixo do parêntese mais à

direita. Outra notação utilizada para representar um número binário é a colocação de uma letra bê

___________________________________________________________________________________

I.5

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

minúscula ("b") ou maiúscula ("B") ao final da seqüência de algarismos binários. Veja o exemplo

abaixo:

(1101)2 = 1101b = 1101B

I.3.3. CONVERSÃO DE DECIMAL PARA BINÁRIO E VICE VERSA

A decomposição de um número binário em suas componentes de base 2, como visto no exemplo

anterior, é a forma de conversão da base 2 para a base 10. Portanto, o número binário (1101)2 equivale a

13 em decimal.

A conversão de decimal para binário é realizada dividindo-se sucessivamente o número decimal

que se deseja converter por 2 até que o resultado da divisão seja 0. O número binário convertido é

composto pelos restos das divisões sucessivas postos em ordem inversa. Vejamos o exemplo da

conversão do número decimal 13 para base 2:

13

2

1

6

2

0

3

2

1

1

2

1

0

Ou seja (13)10 = (1101)2

Esta regra é uma regra de conversão geral da base 10 para qualquer base. Para mostrar que esta

regra é correta podemos fazer a conversão de um número decimal para a própria base 10. Embora isto

não tenha utilidade prática nenhuma, esta conversão poderá ajudar a esclarecer o porquê da regra.

4813 10

3 481 10

1

48 10

8

4

10

4

0

___________________________________________________________________________________

I.6

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

I.3.4. O SISTEMA HEXADECIMAL:

Outra base muito utilizada pelo computador é a base 16 ou sistema hexadecimal.

O sistema hexadecimal possui 16 algarismos (0,1,2,3,4,5,6,7,8,9,A,B,C,D,E e F). Pode parecer

estranho à primeira vista termos letras como algarismos, mas como a base 16 começou a ser usada com

o advento do computador e como na época só haviam disponíveis 10 algarismos indo-arábicos

(0,1,2,.,8,9), havia a opção de se criar mais 6 representações nova para os 6 algarismos restantes, no

entanto optou-se por utilizar as 6 primeiras letras do alfabeto.

Como fomos treinados desde pequenos a raciocinar na base 10 a tabela abaixo nos mostra o

valor absoluto em decimal de cada algarismo hexadecimal.

Hexadecimal

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

Decimal

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Como na base 10, os números hexadecimais são compostos por algarismos justapostos onde a

posição de cada algarismo representa o seu valor relativo. Portanto, o número (9A5C)16 pode ser

decomposto em componentes de potências de base 16, como visto a seguir:

(9A5C)16 = 9 X 163 + A X 162 + 5 X 161 + C X 160

ou

(9A5C)16 = 9 X 4096 + 10 X 256 + 5 X 16 + 12 X 1

= 39516

No exemplo acima utilizamos a notação de colocarmos o número hexadecimal entre parênteses e

a indicação da base 16 como subescrito. A outra forma de representarmos um número hexadecimal é

colocando-se a letra agá maiúscula ("H") ou minúscula ("h") no final da seqüência de algarismos

hexadecimais. Veja o exemplo abaixo:

(9A5C)16 = 9A5Ch = 9A5CH

___________________________________________________________________________________

I.7

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

I.3.5. CONVERSÃO DE DECIMAL PARA HEXADECIMAL E VICE VERSA

A conversão de decimal para hexadecimal e de hexadecimal para decimal segue as mesmas

regras que as conversões de binário para decimal e de decimal para binário.

Para converter um número hexadecimal para decimal basta decompor o número em

componentes de potências de base 16, como já visto em exemplo anterior.

Para converter um número decimal para hexadecimal basta dividir sucessivamente o número por

16 até que o resultado da divisão seja zero. Os restos das divisões sucessivas postos em ordem inversa

formam o número em hexadecimal. Vejamos o exemplo abaixo:

39772 16

12 2485 16

(C)

5 155 16

11

(B)

9

16

9

0

Ou seja (39772)10 = (9B5C)16

I.3.6. CONVERSÃO DE HEXADECIMAL PARA BINÁRIO E VICE VERSA

Podemos notar pela tabela abaixo que com 4 algarismos binários se pode representar

quantidades de 0 a 15 em decimal ou de 0 a F em hexadecimal.

Binário

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

Hexadecimal

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

Decimal

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Utilizando esta propriedade podemos converter números binários em números hexadecimais

com o simples agrupamento de conjuntos de 4 algarismos binários e utilizando a tabela acima para

converter estes conjuntos de algarismos binários em algarismos hexadecimais. Por exemplo:

___________________________________________________________________________________

I.8

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

(0111110011011000)2

(0111 1100 1101 1000)2

↓

(7

↓

C

↓

D

↓

8)16

Para converter de hexadecimal para binário utilizamos o processo inverso substituindo cada

algarismo hexadecimal pelo conjunto de 4 algarismos binários correspondentes.

Não é por acaso que utilizamos o sistema hexadecimal quando lidamos com o computador. Na

verdade, todos os valores guardados e processados pelo computador estão no sistema binário. No

entanto quantidades muito grandes necessitam de sequências muito grandes de algarismos binários. Só

para termos uma noção, para armazenarmos o número 39516 no computador precisamos da seguinte

seqüência de algarismos binários:

1001101001011100

É claro que ao entrarmos estas sequências de zeros e uns no computador a possibilidade de

cometermos um erro é muito grande. O sistema hexadecimal, ao agrupar conjuntos de 4 algarismos

binários, torna-se uma forma mais resumida de se introduzir os dados nos computadores. É muito mais

simples digitarmos "9A5C", que é a representação hexadecimal da quantidade 39516, do que

"1001101001011100", que é a representação binária desta mesma quantidade. Como o computador

internamente só armazena valores 0 ou 1, após digitarmos os algarismos hexadecimais tem que haver

internamente uma conversão automática para a seqüência de algarismos binários correspondente.

I.3.7. O SISTEMA OCTAL:

Outra base utilizada em sistemas computacionais é a base 8 ou sistema octal. A base 8 é

utilizada na programação dos PLCs da Sistema.

O sistema octal possui 8 algarismos (0,1,2,3,4,5,6 e 7). Portanto um número representado na

base 8 não pode ter os algarismos 8 e 9 , que são utilizados somente nas bases 10 e 16.

Os valores absolutos dos algarismos na base 8 são exatamente os mesmos que na base 10, como

podemos ver na tabela abaixo. A única diferença é que na base 8 os valores acima de 7 não são

representados por um único algarismo e sim por um conjunto de algarismos.

Octal

0

1

2

3

4

5

6

7

Decimal

0

1

2

3

4

5

6

7

___________________________________________________________________________________

I.9

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

Como na base 10, os números octais são compostos por algarismos justapostos onde a posição

de cada algarismo representa o seu valor relativo. Portanto, o número (7452)8 pode ser decomposto em

componentes de potências de base 8, como visto a seguir:

(7452)8 = 7 X 83 + 4 X 82 + 5 X 81 + 2 X 80

ou

(7452)8 = 7 X 512 + 4 X 64 + 5 X 8 + 2 X 1

= 3882

I.3.8. CONVERSÃO DE DECIMAL PARA OCTAL E VICE VERSA

A conversão de decimal para octal e de octal para decimal segue as mesmas regras que as

conversões de binário para decimal e de decimal para binário.

Para converter um número octal para decimal basta decompor o número em componentes de

potências de base 8, como já visto em exemplo anterior.

Para converter um número decimal para octal basta dividir sucessivamente o número por 8 até

que o resultado da divisão seja zero. Os restos das divisões sucessivas postos em ordem inversa formam

o número em octal. Vejamos o exemplo abaixo:

3882

2

8

485

5

8

60

4

8

7

8

7

0

Ou seja (3882)10 = (7452)8

I.3.9. CONVERSÃO DE OCTAL PARA BINÁRIO E VICE VERSA

Podemos notar pela tabela abaixo que com 3 algarismos binários se pode representar

quantidades de 0 a 7 em decimal ou em octal.

Binário

000

001

010

011

100

101

110

111

Octal

0

1

2

3

4

5

6

7

Decimal

0

1

2

3

4

5

6

7

___________________________________________________________________________________

I.10

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

Utilizando esta propriedade podemos converter números binários em números octais com o

simples agrupamento de conjuntos de 3 algarismos binários e utilizando a tabela acima para converter

estes conjuntos de algarismos binários em algarismos octais. Por exemplo:

(111100101000)2

(111 100 101 000)2

↓

(7

↓

4

↓

5

↓

0)8

Para converter de octal para binário utilizamos o processo inverso substituindo cada algarismo

octal pelo conjunto de 3 algarismos binários correspondentes.

Assim como o sistema hexadecimal a representação de quantidades no sistema octal é uma

forma mais resumida de introdução de dados nos sistemas computacionais.

omputadores. É muito mais simples digitarmos "7450", que é a representação octal da quantidade 3880,

do que "111100101000", que é a representação binária desta mesma quantidade. Como o computador

internamente só armazena valores 0 ou 1, após digitarmos os algarismos octais tem que haver

internamente uma conversão automática para a seqüência de algarismos binários correspondente.

I.3.10. ARITMÉTICA BINÁRIA

A aritmética binária é análoga com a aritmética decimal. Neste item iremos ver a adição,

subtração, multiplicação e divisão binária.

I.3.10.1. ADIÇÃO BINÁRIA

Assim como na adição decimal, para facilitar, podemos ter a tabuada da soma binária.

TABUADA DA SOMA

BINÁRIA:

0+0=0

0+1=1

1+0=1

1 + 1 = 0 e VAI UM

A partir da tabuada poderemos fazer qualquer adição de dois ou mais números binários com

qualquer quantidade de algarismos. O processo é semelhante a adição decimal. Coloca-se um número

em baixo do outro alinhando-se pelo algarismo de menor valor, ou seja o algarismo mais a direita. Vai

se somando dois a dois os algarismos na mesma posição em ambos os números. Quando a soma de dois

algarismos ultrapassa 1 então soma-se 1 aos algarismos da casa imediatamente a esquerda.

___________________________________________________________________________________

I.11

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

Vejamos o exemplo a seguir.

(110101010)2 + (111110011)2

110101010

+111110011

PASSO 1

______________________________

1

1 ← VAI UM

110101010

+111110011

PASSO 2

______________________________

01

1

110101010

+111110011

PASSO 3

______________________________

101

110101010

+111110011

PASSO 4

______________________________

1101

110101010

+111110011

PASSO 5

______________________________

11101

1 ←VAI UM

110101010

+111110011

PASSO 6

______________________________

011101

↓VAI UM

11

110101010

+111110011

PASSO 7

_______________________________

0011101

↓VAI UM

11

110101010

+111110011

PASSO 8

_______________________________

10011101

___________________________________________________________________________________

I.12

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

↓VAI UM

11

110101010

+ 111110011

PASSO 9

________________________________

110011101

1

110101010

+ 111110011

PASSO 10

_______________________________

1110011101

I.3.10.2. SUBTRAÇÃO BINÁRIA

Como os circuitos eletrônicos são mais apropriados para realizarem soma a subtração binária é

normalmente realizada utilizando uma regra prática que coloca o subtrator em sua representação

complemento a 2 e depois ao invés de uma subtração realizaremos uma soma.

O complemento a dois de um número binário é obtido seguindo-se os seguintes passos:

1. Coloca-se um zero não significativo a esquerda do um mais significativo do número.

2. Inverte-se todos os algarismos, ou seja, troca-se zeros por uns e uns por zeros.

3. Soma-se um.

Vejamos um exemplo:

Então 10101 é o complemento a dois de 1011 e portanto a subtração e a soma abaixo são

similares quando despreza-se o último VAI UM.

1 0 0 0 1 (17)10 1 0 0 0 1

- 1 0 1 1 (11)10 +

____________________________

0 1 1 0 (06)10

10101

____________________

100110

↑DESPREZA-SE

___________________________________________________________________________________

I.13

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

I.3.10.3. MULTIPLICAÇÃO BINÁRIA

A multiplicação binária é também muito simples. Coloca-se os dois números um em baixo do

outro, alinhado pela direita e vai se multiplicando o de cima por cada algarismo do de baixo. O resultado

de cada uma destas multiplicações vão sendo colocadas uma em baixo da outra deslocando-se sempre

uma casa para a esquerda. Abaixo fornecemos a tabuada de multiplicação binária:

TABUADA DA

MULTIPLICAÇÃO

BINÁRIA:

0x0=0

0x1=0

1x0=0

1x1=1

Vejamos o exemplo a seguir:

1100110

x

1010

PASSO 1

____________________

0000000

1100110

x

1010

PASSO 2

_____________________

0000000

1100110

1100110

x

1010

PASSO 3

____________________

0000000

1100110

0000000

1100110

x

1010

PASSO 4

____________________

0000000

1100110

0000000

1100110

1100110

x

1010

PASSO 5

_____________________

0000000

1100110

+0000000

1100110

_______________________________

1111111100

___________________________________________________________________________________

I.14

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

I.3.10.4. DIVISÃO BINÁRIA

A divisão é realizada da mesma forma que em decimal. A seguir damos um

exemplo de divisão binário 1 1 0 1 1 1 (55) ÷ 1 0 1 (5):

1 1 0'1 1 1

-101

101

PASSO 1

1

001

1 1 0 1'1 1

-101

101

PASSO 2

10

001 1

1 1 0 1 1'1

-101

101

PASSO 3

101

00111

- 101

010

110111

-101

101

PASSO 4

101 1

00111

-101

010 1

101

000

___________________________________________________________________________________

I.15

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

I.3.11 EXERCÍCIOS:

1. Converta os seguintes números binários para a base 10:

a). (10010010)2 =

b). (01100011)2 =

c). (11110010)2 =

d). (10000000)2 =

2. Converta os seguintes números decimais para a base 2:

a). 129 =

b). 35647 =

c). 65535 =

3. Converta os seguintes números hexadecimais para a base 10:

a). (9AB3)16.=

b). (12EF)16 =

c). (1000)16 =

4. Converta os seguintes números octais para a base 10:

a). (6523)8.=

b). (1267)8 =

c). (1000)8 =

5. Converta os seguintes números decimais para as bases 16 e 8:

a). 127 =

b). 4876 =

c). 13876 =

6. Converta os seguintes números de hexadecimal para binário:

a). (9AB3)16 =

b). (12EF)16 =

c). (1000)16 =

7. Converta os seguintes números de binário para hexadecima e para octal:

a). (1001101100011110)2 =

b). (110111000110011)2 =

c). (1001110011010)2 =

d). (1110000000)2 =

___________________________________________________________________________________

I.16

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

7.Efetue as seguintes operações:

b). (11001110001)2

a). (10010110)2

-

+

(01111011)2

__________________________________

(11001101110)2

__________________ ____________________

c).

(11110010)2

x (110110)2

_____________________________

d) 11011000

e). (A43C)16

+ (CDEF)16

______________________________

(

)16

1100

→ (

→+ (

)2

←

)2

______________________________________________________________

(

)2

Sugestão: Converta para a base 2, some na base 2 e converta de volta para a base 16.

___________________________________________________________________________________

I.17

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

I.4. O PROCESSADOR

O processador, normalmente chamado de CPU (Central Processing Unit) é a parte do

computador que controla todo o sistema. No entanto, não é o processador que decide o que deve ser

feito pelo sistema. O usuário, ou programador, é que deve informar ao processador quais são os passos

que ele deve executar para desempenhar uma determinada tarefa. Na realidade, o processador é um

executor de tarefas.

A seqüência de passos ou instruções (comandos) denomina-se programa e é introduzida no

computador através de um dispositivo de entrada (como, por exemplo, o teclado) e armazenada na

memória. Após armazenada na memória, o processador busca uma a uma as instruções e as vai

executando. Esta situação é semelhante a um recruta que no início do dia recebe do sargento uma série

de ordens. O recruta vai memorizando as instruções e, depois que o sargento acaba de dar as instruções,

ele inicia a execução das tarefas na ordem em que o sargento as deu.

Tem de ficar bem entendido que o processador não faz nada que não seja ordenado pelo

programa.

As instruções (de um programa) armazenadas na memória nada mais são que números binários

(ou seqüência de zeros e uns), na verdade as únicas coisas que são entendidas pelo computador.

Portanto, para cada função que queremos que o processador execute, deveremos fornecer a ele um

conjunto de zeros e uns que ele previamente conheça. Este conjunto é conhecido como código de

máquina.

Códigos de máquina

100011100

100011110

PROCESSADOR

(CPU)

MEMÓRIA

Figura I.4 - Códigos deMáquina

Quando um processador é projetado e implementado (construído), o projetista determina uma

tabela de instruções e seus respectivos códigos de máquina. Esta tabela é fornecida aos programadores,

que então podem colocar na memória uma seqüência de códigos de máquina a serem interpretados pelo

processador.

A codificação de instruções é semelhante ao cardápio de alguns restaurantes que possuem

códigos (números) para os diversos pratos servidos. O cliente pede ao garçom, por exemplo, um filé

com fritas e uma lazanha. O garçom anota o pedido pelos códigos dos pratos e então entrega esses

códigos para o cozinheiro. Este decodifica, ou seja, interpreta os pedidos e prepara a comida.

Os códigos dos pratos são diferentes para cada restaurante. Portanto, se no restaurante A o filé

com fritas tem código 23, no restaurante B o mesmo filé com fritas pode ter código 55. Imaginemos que

um garçom novato no restaurante A, que tenha trabalhado durante muito tempo no restaurante B,

___________________________________________________________________________________

I.18

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

entregue ao cozinheiro um pedido utilizando os códigos do cardápio do restaurante B. Provavelmente o

cliente não terá no final o prato desejado.

Algo semelhante acontece com os processadores. Cada processador possui seu próprio conjunto

de códigos de máquina e funções e que geralmente não coincidem com os códigos de outro processador.

Portanto uma seqüência de códigos de máquina (ou programa) "escrita" para que o processador A

execute uma determinada tarefa não irá funcionar do mesmo modo se aplicada ao processador B.

No início da utilização dos computadores, a programação era feita diretamente, escrevendo-se

em binário o código de máquina das instruções que se desejava que o processador executasse. Esta

tarefa, além de enfadonha e muito propensa a erros, possuía o inconveniente de só servir para o

processador que se estava utilizando.

Este inconveniente impossibilitava a utilização, por um processador, de programas escritos para

outro processador. Outro inconveniente em se escrever programas diretamente utilizando os códigos de

máquina é que os programas se tornam muito extensos e de difícil compreensão quando se deseja que o

computador execute tarefas mais complexas.

IBM XT

COMPILADOR

PASCAL 8088

CÓDIGO DE

MÁQUINA

8088

PROGRAMA FONTE

ESCRITO EM

PASCAL

APPLE MACINTOSH

COMPILADOR

PASCAL 68000

CÓDIGO DE

MÁQUINA

68000

Figura I.5

Para solucionar estes tipos de inconvenientes foram criadas linguagens-padrão de programação,

tais como FORTRAN, Pascal e C, cuja sintaxe independe do processador que se vai utilizar para

executar o programa. Os programas escritos nestas linguagens são iguais para qualquer tipo de

processador. A diferença só se dá no momento em que o programa é traduzido para os códigos de

máquina do processador utilizado. Esta tradução é chamada de compilação e os programas que

executam esta tradução são conhecidos como compiladores. Para cada tipo de processador existe um

compilador diferente, no entanto as linguagens-padrão (ditas de alto nível) são iguais. Por exemplo: um

mesmo programa escrito em Pascal pode ser compilado (traduzido) em código de máquina do

processador 8088 (utilizado nos microcomputadores IBM XT compatíveis) ou do processador 68000

(utilizado nos microcomputadores Apple Macintosh). A diferença é que para gerar o código de máquina

8088 é utilizado um compilador Pascal para o processador 8088 e para gerar o código de máquina

68000 é utilizado um compilador Pascal para o processador 68000, como visto na figura I.5.

___________________________________________________________________________________

I.19

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

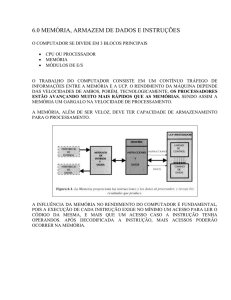

I.5. MEMÓRIA

A memória é a parte do computador que armazena informações.

Como visto no item anterior uma das funções básicas da memória é armazenar as sequências de

códigos de máquinas (ou programas), que serão interpretados e executados pelo processador.

Outra função da memória é armazenar os dados. Por dados entendem-se todas as informações a

serem processadas pelo computador, bem como as respostas deste processamento.

Por exemplo, se o processador executar um programa simples que some dois números inteiros,

tanto os dois números a serem somados quanto o resultado da soma são considerados dados e podem

ser armazenados na memória.

I.5.1. CLASSIFICAÇÃO DAS MEMÓRIAS:

A memória de um sistema computacional pode ser dividida em dois tipos básicos: memória

primária e memória secundária. A memória primária é composta de dispositivos semicondutores

("chips") que podem ser acessados, a qualquer momento, diretamente pelo processador. A memória

secundária, também conhecida como memória de massa é composta de dispositivos de armazenamento

magnético (discos flexíveis, discos rígidos ou Winchesters, fitas magnéticas, etc.) ou ótico (CD ROM)

que armazenam a maior parte das informações (programas e dados). Todos os programas que podem ser

executados pelo processador ficam guardados na memória de massa até o momento de sua execução.

Neste instante o programa é transferido da memória de massa para a memória principal e a partir desta é

executado. Por ter de armazenar muita informação a memória secundária normalmente tem uma

capacidade de armazenamento centenas ou milhares de vezes maior que a memória principal, que só

precisa guardar a cada momento os dados e o programa que estão sendo executados pelo processador.

A memória principal pode ser classificada quanto a função, volatilidade e tipo de acesso.

I.5.1.1. Quanto a função:

Quanto a função as memórias podem ser:

I.5.1.1.1. Memória de programas

As memórias de programas armazenam códigos de máquina que serão lidos e executados pelo

processador.

I.5.1.1.2. Memória de dados:

As memórias de dados armazenam dados de entrada e dados de saída do processamento.

___________________________________________________________________________________

I.20

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

I.5.1.2. Quanto ao tempo de retenção das informações (ou volatilidade):

I.5.1.2.1. Memórias permanentes:

Memórias permanentes são aquelas cuja manutenção das

informações nela armazenadas

independe do fornecimento de energia elétrica externa. Este tipo de memória só necessita de energia

elétrica externa no momento em que desejamos "escrever" (colocar) ou "ler" (retirar) as informações.

I.5.1.2.2. Memórias voláteis:

Memória volátil é aquela que só mantém as informações enquanto há alimentação de energia

elétrica externa. Como na memória permanente, as informações só podem ser lidas ou escritas com a

alimentação de energia elétrica externa.

Podemos transformar uma memória volátil em memória permanente colocando-se uma bateria

para alimentá-la. Desta forma, enquanto a bateria não perder a sua carga as informações se mantêm.

Portanto, o conjunto memória volátil mais bateria pode ser considerado como memória permanente.

I.5.1.3. Quanto ao tipo de acesso:

I.5.1.3.1. Memórias de Apenas Leitura:

As memórias de apenas leitura ou ROM (Read Only Memory) como são conhecidas

popularmente, como o próprio nome já diz só podem ser lidas pelo processador. O processador não pode

escrever informações em uma ROM. As informações são escritas na ROM durante a sua fabricação e

não podem jamais ser alteradas pelo usuário. A ROM é classificada quanto a volatilidade como

memória permanente, pois uma vez cortado o fornecimento de energia elétrica o conteúdo da ROM se

mantém intacto.

PROM (Programmable Read Only Memory):

Uma versão modificada de ROM é a PROM (Programmable Read Only Memory). Como seu

nome diz, a PROM vem vazia de fábrica e pode ser programada (ou gravada) uma única vez pelo

usuário, ou seja, pelo projetista de sistemas digitais.

As PROMs são formadas por circuitos semicondutores especiais que funcionam como fusíveis.

Assim comos os fusíveis estes circuitos especiais conduzem corrente elétrica. No entanto eles podem se

queimar interrompendo o fluxo de corrente. Os dois níveis lógicos são representados pelos fusíveis

intactos (nível lógico um) ou queimados (nível lógico zero). As PROMs são fabricadas e

comercializadas com todos estes fusíveis intactos (conduzindo corrente), ou seja, com todos os bits em

nível lógico um. Cabe ao usuário "queimar" os fusíveis, nas posições necessárias, para formar o

conteúdo desejado.

Para programar a PROM o usuário necessita de um aparelho especial. Este aparelho aplica, nas

posições desejadas, pulsos de tensão (12,5 ou 21 volts) bem acima da tensão de operação (5 volts). Estas

tensões altas fazem com que os fusíveis se queimem, por este motivo chama-se "queimar uma PROM" o

___________________________________________________________________________________

I.21

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

ato de programar através destes aparelhos especiais, que também são conhecidos vulgarmente como

queimadores de PROMs, o conteúdo de uma memória PROM. Se houver um erro na programação de

uma PROM não é possível apagar este erro e nem escrever nada por cima. A única alteração possível é

transformar o conteúdo de um bit de nível um (fusível intacto) para nível zero (fusível queimado). Como

de forma geral as alterações necessárias também envolvem transformações de zero para um o usuário,

neste caso, deverá jogar fora a PROM com o erro e gravar uma outra.

EPROM (Erasable Programmable Read Only Memory):

No sentido de se evitar o desperdício citado anteriormente, foi desenvolvida a EPROM

(Erasable Programmable Read Only Memory). A informação é gravada na EPROM com um aparelho

semelhante ao utilizado para gravação de PROMs, no entanto estas informações podem ser apagadas

expondo um pequeno orifício existente na parte superior da EPROM à luz ultravioleta. Normalmente as

EPROMs gravadas têm uma pequena etiqueta cobrindo este orifício de forma a não permitir que a luz

ultravioleta presente na luz do sol e das lâmpadas em geral, apague, com o passar dos anos, as

informações gravadas. Os circuitos semicondutores que compõem uma EPROM também podem ser

comparados a fusíveis, só que fusíveis renováveis.

E2PROM (Electrically Erasable Programmable Read Only Memory):

Uma versão melhorada e mais cara da EPROM é a EEPROM (Electrically Erasable

Programmable Read Only Memory). A única diferença entre as duas é o método de apagamento das

informações. Enquanto na EPROM a forma de se apagar é a exposição à luz ultravioleta, como descrito

acima, na EEPROM ou E2PROM (como também é conhecida) o apagamento se dá por aplicação de

pulsos elétricos.

Esta característica de poder ser apagada por pulsos elétricos permite que a E2PROM possa ter o

seu conteúdo alterado sem que seja necessário retirá-la do circuito. As memórias E2PROM são

largamente utilizadas em equipamentos de controle de processo guardando a configuração necessária ao

funcionamento do sistema.

Para alterar o conteúdo de uma posição de uma E2PROM é necessário apaga-la através de um

pulso elétrico, que nas primeiras E2PROM eram de níveis superior aos 5 volts (padrão TTL) comuns em

qualquer sistema digital, o que fazia com que os equipamentos tivessem circuitos especiais para gerar

estes níveis. Em E2PROM mais modernas o pulso de apagamento é de 5 volts e internamente a

E2PROM através de circuitos especiais gera os níveis necessários ao apagamento.

Um inconveniente das E2PROMs é que o tempo de apagamento e escrita de um novo conteúdo é

muito grande (na ordem de milisegundos) quando comparados aos tempos de acesso de memórias

RAM.

I.5.1.3.2. Memórias de Leitura e Escrita:

As Memórias de Leitura e Escrita, como o próprio nome já diz, são aquelas que podem ser

escritas e lidas pelo processador. Este tipo de memória é comum e imprecisamente chamada de RAM

(Random Access Memory - Memória de Acesso Aleatório). As RAMs necessitam sempre de energia

___________________________________________________________________________________

I.22

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

elétrica tanto para manter os dados nelas armazenados quanto para se lerem ou se escreverem

informações. Existem basicamente dois tipos de RAMs: RAM estática e RAM dinâmica.

RAM Dinâmica:

Nas RAM dinâmicas os dois nível lógicos (0 ou 1) são implementados por circuitos

semicondutores especiais, que são capazes de armazenar cargas elétricas. Então a presença ou não

destas cargas elétricas define respectivamente os níveis lógicos um e zero.

Estes circuitos especiais funcionam de forma semelhante a capacitores. Os capacitores, como

visto na figura I.6, são componentes compostos por duas placas metálicas paralelas, separadas por um

isolante elétrico. Aplicando-se cargas positivas a uma das placas, pela atração de cargas opostas

induzem-se cargas negativas na outra placa.

Carga Positiva

Placas

Metálicas

Paralelas

+ + ++ +

+ + + +

- -- - - -

Isolante Elétrico

Carga Negativa

Figura I.6 - Capacitor

A tendência natural é que as cargas sejam trocadas entre as placas até atingir-se o equilíbrio

elétrico. No entanto o isolante entre as placas impede esta troca.

Como não existe isolante elétrico perfeito as cargas, mesmo que lentamente, vão sendo trocadas

chegando-se ao equilíbrio e portanto descarregando o capacitor.

Os dispositivos semicondutores especiais que armazenam as cargas dentro das memórias

dinâmicas são capazes de manter a sua carga por apenas alguns mili segundos. Estes mili segundos que

para nós parece pouco, é muito tempo para os microprocessadores, que executam tarefas em tempos

10.000 vezes menor (centenas de nano segundos).

As RAM Dinâmicas necessitam além do fornecimento de energia elétrica, que as informações

nelas armazenadas sejam atualizadas (ou refrescadas) de tempos em tempos. O processador ou um

circuito destinado para este fim tem que de tempos em tempos ( da ordem de milissegundos) ler o

conteúdo de cada posição e reescrevê-lo. Esta função de reavivar a memória é conhecida como "refresh"

(refrescamento).

___________________________________________________________________________________

I.23

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

RAM Estática:

Ao contrário da RAM Dinâmica, a RAM Estática não perde o seu conteúdo com o tempo e

portanto não precisa ser reavivada. A RAM Estática só perde o seu conteúdo se interrompermos o

fornecimento de energia elétrica.

Enquanto a memória dinâmica armazena cargas elétricas em circuitos semicondutores especiais,

a memória estática sinaliza os dois níveis lógicos alternando o trajeto de corrente entre dois caminhos

possíveis. Esta comutação é obtida por chaves eletrônicas, que podem ser facilmente implementadas por

intermédio de transistores. Como estas chaves eletrônicas uma vez acionadas só mudam de estado

quando recebem um novo comando, não é necessário refrescamento e os dados serão mantidos enquanto

se mantiver o fornecimento de energia elétrica. Com a interrupção da energia, todos as chaves assumem

um único estado e a memória perde todos os dados.

Por ter circuitos mais elaborados as maiores memórias estáticas comerciais possuem capacidade

de armazenamento muito inferior as memórias dinâmicas comerciais.

Em 1993 a maior memória estática comercial com preço acessível era a 62256 que possui a

capacidade de armazenar 256 quilo bits, enquanto que a maior RAM dinâmica possui capacidade de 16

mega bits.

___________________________________________________________________________________

I.24

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

I.5.1.3.3. NVRAM (Non volatily RAM):

Um outro tipo de memória não volátil, também muito utilizada em equipamentos de controle de

processo é a NVRAM. As vantagens da NVRAM sobre a E2PROM é que seu acesso é feito com se a

mesma fosse uma RAM estática comum (não necessitando pulso especial de apagamento) e com um

tempo de acesso igual às memórias RAM estáticas comuns.

Na verdade a NVRAM é composta internamente por duas memórias. A figura I.6 mostra o

diagrama funcional da NVRAM X20C04 da Xicor. Ligado diretamente aos barramentos de dados e

endereço está uma memória RAM estática (SRAM = Static RAM) de 512 posições de 8 bits. Por trás

existe uma memória E2PROM de mesmo tamanho que possui uma cópia do conteúdo da SRAM. Os

valores escritos diretamente na SRAM são guardados na E2PROM através de ciclos chamados

"STORE" espaçados um do outro em pelo menos 5 ms. Por sua vez cada byte armazenado na E2PROM

é copiado para a SRAM através de ciclos chamados "RECALL" espaçados um do outro em pelo menos

5 μs.

X20C04

SELEÇÃO

DE

LINHA

A3

a

A6

CE

OE

WE

NE

A0

A1

A2

A7

A8

E2 PROM

SRAM

STORE

512 x 8

RECALL

LÓGICA DE

CONTROLE

SELEÇÃO

DE

COLUNA

I/O

D0

D7

Figura I.7 - NVRAM X20C04 - 512 x 8

As NVRAMs não substituem as E2PROM, como poderia parecer. Equipamentos de controle de

processo, como os PLCs, normalmente possuem os quatro tipos de memórias diferentes: EPROM,

RAM, E2PROM e NVRAM, como pode ser visto na figura a seguir.

No PLC da Sistema a E2PROM guarda o programa aplicativo (diagrama ladder) que o PLC irá

executar. Quando o PLC é energizado o programa é imediatamente transferido para a memória RAM, de

onde o programa (que está na EPROM), que o processador está executando, vai buscar as informações

para executar o Ladder programado pelo usuário. Estas buscas são feitas nas velocidades máximas (sem

tempo de espera) pois a memória RAM tem tempos de acessos compatíveis com o processador.

___________________________________________________________________________________

I.25

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

EPROM

SISTEMA OPERACIONAL

C

RAM

D

APLICATIVO DO USUÁRIO

(LADDER) - UTILIZADO

VARIÁVEIS DE PROGRAMA

PROCESSADOR

D

EEPROM

APLICATIVO DO USUÁRIO

(LADDER) - CÓPIA

D

NVRAM

D - Dados

C - Código de Máquina

ALTERAÇÕES NO APLICATIVO

(CÓPIA DE SEGURANÇA)

VARIÁVEIS DE RETENÇÃO

Figura I.8 - Diagrama de Memórias de um PLC típico.

Quando é necessário fazer uma mudança em algum parâmetro deste programa aplicativo esta

mudança é realizada diretamente na RAM, refletindo-se em imediata alteração na execução do programa

aplicativo. Estas mudanças são guardadas também na memória NVRAM e só então é iniciada a

gravação na E2PROM. Esta cópia na NVRAM é uma segurança para que caso haja uma falta de energia

durante a gravação das alterações na E2PROM (que leva um tempo relativamente alto) estas alterações

não sejam perdidas.

Além da cópia de segurança a NVRAM também armazena as variáveis de retenção e dos pontos

de E/S do sistema.

___________________________________________________________________________________

I.26

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

I.5.2. ENDEREÇAMENTO DE MEMÓRIA

Como vimos anteriormente, memória é o dispositivo que armazena informações. Antes de

prosseguirmos, temos que introduzir algumas definições importantes.

BIT é um algarismo binário que está armazenado na memória. O termo bit vem da abreviação

de digito binário (bynary digit). É a menor unidade de informação possível.

BYTE é o conjunto de 8 bits.

QUILO BYTE (KByte) é o conjunto de 1024 (210 ) bytes.

MEGA BYTE (MByte) é o conjunto de 1024 KBytes, ou seja

1 MByte = 1024 KBytes = 210 KBytes = 210 * 210 Bytes = 220 Bytes.

Imaginemos a memória como se fosse um grande gaveteiro. Cada gaveta pode armazenar um

certo número de algarismos binários (ou bits), como mostrado na figura I.9.

GAVETA 0 (000)

GAVETA 1 (001)

01011001

GAVETA 0 (000)

GAVETA 2 (010)

GAVETA 3 (011)

GAVETA 3 (011)

GAVETA 4 (100)

GAVETA 4 (100)

GAVETA 5 (101)

GAVETA 5 (101)

GAVETA 6 (110)

GAVETA 6 (110)

GAVETA 7 (111)

GAVETA 7 (111)

Figura I.9 - Endereçamento de Memória

Chamamos de palavra de memória o conjunto de bits que cada gaveta (ou posição de memória)

pode armazenar. Na figura I.6 a palavra de memória tem 8 bits (ou 1 byte).

Cada gaveta recebe um número que chamamos de endereço. Portanto para acessarmos o

conteúdo de uma posição de memória precisamos saber o seu endereço.

Na figura I.5 a nossa memória possui 8 posições de memória portanto com apenas 3 bits

podemos representar o endereço de qualquer posição desta memória. Com quatro bits poderíamos

representar 16 endereços diferentes de (0000)2 até (1111)2 (ou de 0 a 15).

Assim, com n bits de endereço podemos endereçar uma memória de até 2n posições.

Agora iremos analisar exemplos de memórias comerciais, mostrando suas pinagens, ciclos de

acesso, para identificarmos as principais características de cada tipo de memória.

I.5.2.1. SRAM 62256:

A SRAM 62256 que é uma memória utilizada em equipamentos industriais de um modo geral.

Cada posição de uma memória SRAM pode ter seu conteúdo lido ou escrito pelo processador. A

memória SRAM 62256 é um chip de 28 pinos, como mostra a figura I.10. A seguir, iremos analisar a

função de cada pino da memória SRAM 62256.

___________________________________________________________________________________

I.27

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

A11

A12

A7

A6

A5

A4

A3

A2

A1

A0

D0

D1

D2

Gnd

6

2

2

5

6

Vcc

A14

A13

A8

A9

WR

RD

A10

CS

D7

D6

D5

D4

D3

Figura I.10 - Pinagem da RAM 62256

Os pinos A0,A1,A2,...,A14 são os bits de endereçamento. A inicial "A" nas indicações dos pinos

vem de Address (Endereço em inglês). Como temos 15 bits de endereço a memória RAM 62256 possui

32K (32.768) posições. O conjunto destes bits de endereçamento chamamos de Via de Endereços ou

Barramento de Endereços.

Os pinos D0,D1,D2,...,D7 são os pinos onde se colocam os bits do conteúdo de cada posição da

memória. A inicial "D" nas indicações dos pinos vem de "Data" (Dado em inglês). Como são 8 pinos a

palavra de memória é de 8 bits. O conjunto destes bits de dados chamamos de Via de Dados ou

Barramento de Dados.

Portanto a memória RAM 62256 possui 32 768 posições de 8 bits cada uma, ou seja é uma

memória de 32.768 X 8 (que se lê: "memória de 32.768 por 8") ou de 32KBytes X 8 (que se lê:

"memória de 32 cá bytes por 8").

Os pinos de Vcc e Gnd são os pinos de alimentação do chip. Nestes dois pinos deverão ser

colocados respectivamente + 5 volts e terra.

O pino de WR é utilizado para ligarmos um sinal de controle que é gerado pelo processador que

irá acessar esta memória.. Um pulso de nível baixo (0) significa que o processador deseja escrever

(WRite em inglês) um dado na memória. A seqüência de escrita de um dado na memória é a seguinte:

1. O processador coloca no Barramento de Endereço (pinos A0,A1,...,A14) o endereço da

posição que ele deseja escrever. Esta ação chamamos de endereçar a memória.

2. O processador coloca no Barramento de Dados (pinos D0,D1,..,D7) o dado que ele deseja

escrever na posição endereçada.

3. O processador dá um pulso de nível baixo no pino WR .

4. A memória armazena o dado na borda de subida do pulso do pino WR .

A figura I.11 mostra o esquema de ligação do processador com a memória RAM 62256 e o

diagrama de tempo de um ciclo de escrita em memória.

___________________________________________________________________________________

I.28

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

A0

A0

P

R A1

..

O

C A14

E D0

S

S D1

A

D D7

O

R RD

..

.

..

6

A14

2

D0

..

.

D1

D7

RD

WR

BARRAMENTO DE

ENDEREÇOS

A1

2

5

6

WR

ENDEREÇO VÁLIDO

COLOCADO PELO PROCESSADOR

WR

BARRAMENTO

DE DADOS

DADO VÁLIDO

COLOCADO PELO

PROCESSADOR

Figura I.11 - Ciclo de Escrita em Memória

O pino de RD é utilizado para ligarmos um sinal de controle que é gerado pelo processador. Um

pulso de nível baixo (0) significa que o processador deseja ler (ReaD em inglês) um dado da memória.

A seqüência de leitura de um dado da memória é a seguinte:

1.

O processador coloca no Barramento de Endereço (pinos A0,A1,...,A14) o endereço

cujo conteúdo se deseja ler.

2.

O processador dá um pulso de nível baixo no pino RD .

3.

A memória coloca no Barramento de Dados (pinos D0,D1,..,D7) o conteúdo da posição

endereçada.

4.

O processador captura este dado na borda de subida do pulso do pino RD .

A figura I.12 mostra o diagrama de tempo de um ciclo de leitura de memória. Observe que o

tempo entre a colocação pelo processador do endereço da posição que ele quer acessar e a resposta por

parte da memória, colocando o dado no barramento de dados é conhecido por tempo de acesso. Os

componentes de memória vem com este tempo usualmente codificado como prefixo do número do

componente. Por exemplo um componente 62256-12 é uma memória RAM de 32K X 8 com tempo de

acesso de 120 ns.

O temp de acesso de memórias SRAM comercialmente disponíveis pode variar de 5 a 150ns.

Quanto menor o tempo de acesso, mais caras são as SRAMs. As versões de 15 a 25 ns de SRAMs são

___________________________________________________________________________________

I.29

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

utilizadas como memórias cache em placas de microcomputadores IBM compatíveis baseados nos

microprocessadores 386, 486 e Pentium e também em workstations RISC.

BARRAMENTO DE

ENDEREÇOS

ENDEREÇO VÁLIDO

COLOCADO PELO PROCESSADOR

RD

DADO VÁLIDO

COLOCADO PELA

MEMÓRIA

BARRAMENTO

DE DADOS

TEMPO DE

ACESSO

Figura I.12 - Ciclo de Leitura de Memória

Observe a direção das setas no esquema de ligação da figura I.11.

O Barramento de Endereços, bem como os sinais de RD e WR , têm sempre a mesma direção,

ou seja do processador para a memória. Por este motivo dizemos que o Barramento de Endereços e os

sinais de controle RD e WR são unidirecionais.

O Barramento de Dados pode ter duas direções. Pode estar direcionado do processador para a

memória (escrita) ou da memória para o processador (leitura). Por este motivo dizemos que o

Barramento de Dados é bidirecional.

Estados de Espera (Wait States):

Como os sinais do barramento de endereços e RD são gerados pelo processador, o tempo

decorrido desde o endereçamento até a subida do sinal de RD só dempende da velocidade do

processador. Na verdade as mudanças ocorridas nos barramentos e sinais de RD e WR são

sincronizadas por um outro sinal de entrada no processador que é o "clock". Este sinal é uma onda

quadrada que cujas subidas e descidas fazem com que uma operação do processador seja realizada. O

período deste sinal de clock da-se o nome de estado e portanto para executar um ciclo de leitura de

memória são necessários alguns estados, como visto na figura abaixo. Quanto mais rápido, ou seja

quanto maior a frequência (medida em MegaHertz) do sinal de clock, menor será o intervalo de tempo

entre o endereçamento e a subida do sinal de RD . Se a memória não for suficientemente rápida, quando

o RD subir o barramento de dados não conterá ainda o valor do conteúdo da posição acessada e

portanto o processador irá capturar o "lixo" presente no barramento na hora da subida do RD , como

visto na figura I.13.

___________________________________________________________________________________

I.30

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

ESTADO

CLK

BARRAMENTO DE

ENDEREÇOS

ENDEREÇO VÁLIDO

COLOCADO PELO PROCESSADOR

RD

Momento em que o processador captura

o conteúdo do barramento de dados (lixo)

DADO VÁLIDO

COLOCADO PELA

MEMÓRIA

BARRAMENTO

DE DADOS

TEMPO DE

ACESSO

Figura I.13 - Ciclo de Leitura com perda de informação

Existe um sinal de entrada no microprocessador que tem o nome de READY (pronto) que

possibilita a interligação de dispositivos de memória cujo tempo de acesso não é apropriado ao

funcionamento do processador. Quando o sinal de READY é mantido em nível lógico "1" o acesso a

memória se dá normalmente como visto na figura I.12. Quando o processador acessar uma memória

"lenta" (cujo tempo de acesso é maior que o pulso RD gerado pelo processador) o sinal é colocado em

nível lógico "0" até que a memória responda ao acesso de leitura quando então o sinal de READY volta

a nível lógico "1", fazendo com que o pulso de RD acabe. Veja a figura I.14. O alargamento do pulso

de RD é obtido pela inserção de um período (estado) a mais durante o ciclo de leitura. Este estado é

chamado de estado de espera, ou em inglês: "wait state". Dependendo da velocidade do processador

(frequência de trabalho) e dependendo do tempo de acesso da memória utilizada podem ser inseridos

um, dois ou mais wait states. O acesso a memória sem necessidade de estados de espera é dito um

acesso com "zero wait states".

___________________________________________________________________________________

I.31

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

ESTADO DE ESPERA

(WAIT STATE)

CLK

BARRAMENTO DE

ENDEREÇOS

RD

ENDEREÇO VÁLIDO

COLOCADO PELO PROCESSADOR

Sinal de RD alaragado pelo sinal de READY

READY

DADO VÁLIDO

COLOCADO PELA

MEMÓRIA

BARRAMENTO

DE DADOS

TEMPO DE

ACESSO

Figura I.14 - Ciclo de Leitura com Wait State.

Cabe apenas uma dúvida, mostrada no esquema da figura I.15. Quem gera o sinal de READY ?

A0

A0

P

R A1

..

O

C A14

E D0

S

S D1

A

D D7

O RD

R

..

.

A1

..

A14 2

D0

..

.

D1

D7

RD

WR

CLK

READY

6

2

5

6

WR

?

Figura I.15 - Gerador de Wait States (?).

___________________________________________________________________________________

I.32

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

Associação de Chips de Memória SRAM:

No sentido de aumentarmos a capacidade de armazenamento de um sistema utilizando

processadores podemos associar vários chips de memória. Por exemplo, se um sistema necessita de

65536 Bytes (64KBytes), podemos associar 2 RAM 62256, cada uma com 32 768 Bytes (32KBytes),

como mostra a figura I.16.

P

R

O

C

E

S

S

A

D

O

R

A0

...

..

.

A0

..

.

A12

A12

D0

D0

..

.

D1

D7

..

.

..

.

D1

D7

RD

OE

WR

WE

A15 A14 A13

CI 2

CS

..

.

A0

..

.

A12

CI 1

D0

..

.

D1

..

.

CI 3

D7

OE

CS

Figura I.16 - Associação de Memórias SRAM

O esquema da figura I.16 mostra a associação de 2 SRAM 62256. No entanto se você observar

bem existe uma dúvida a ser esclarecida. Se o processador , por exemplo, quiser escrever em um

determinado endereço um dado, ele colocará o endereço desejado no Barramento de Endereços, o dado

a ser escrito no Barramento de Dados, e dará um pulso no pino de WR . Como os Barramentos de

Endereços e Dados das duas RAM 62256 estão em paralelo o dado será escrito em ambas. A forma de

esclarecermos este problema é utilizando o único pino da 62256 que ainda não teve a sua função

explicada, ou seja, o pino CS .

O pino de CS (Chip Select = Seleção do Chip) é utilizado para que o processador selecione

entre várias memórias interligadas a ele qual será lida ou escrita. Quando o processador quer acessar

___________________________________________________________________________________

I.33

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

uma entre duas ou mais memórias ele coloca um nível baixo (0) no pino CS da memória que deseja

acessar. Se existir apenas uma memória, este pino pode ser colocado permanentemente em nível baixo.

No circuito da figura I.16, o processador tem um barramento de endereços de 16 pinos (de A0

até A15), portanto a capacidade de endereçamento é de 65.536 (do endereço 0000h até o endereço

FFFFh). O pino A15 do barramento de endereços, por ser o único pino do barramento de endereços que

não é ligado diretamente às memórias, é utilizado como entrada do circuito de seleção que irá definir

qual das memórias será acessada. Dependendo do valor de A15 o circuito de seleção irá colocar nível

baixo (0), no pino de CS de uma da outra memória 62256. Este tipo de endereçamento fará com que o

processador leia a memória 62256 de cima com A15 = 0, ou seja do endereço 0000h até o endereço

7FFFh. Quando A15 = 1, ou seja do endereço 8000h até FFFFh, o processador acessa a memória de

baixo.

O circuito de seleção que poderá ser utilizado para implementar o endereçamento descrito acima

seria simplesmente um inversor, como visto na figura I.17.

PROCESSADOR

A15

CS da (62256)

1

CS da (62256)

2

Figura I.17 - Circuito de Seleção

Circuito Gerador de Wait States:

Pode-se agora entender quem irá gerar o sinal de READY, que permite a utilização de memórias

lentas. Quando se projeta um sistema computacional se sabe a priori quais memórias necessitarão wait

states e quais serão acessada com zero wait states. Se por exemplo no sistema da figura I.16 uma das

memórias é mais lenta que a outra e necessita de um wait state, o circuito decodificador quando

selecionar a memória mais lenta irá informar ao circuito Gerador de “Wait States", como mostrado na

figura I.18. O Circuito Gerador de “Wait States” que então irá gerar o sinal READY, fazendo com que

sejam inseridos um, dois ou mais estados de espera. Nos microcomputadores pessoais o número de

"wait states" necessários para cada memória é configurada por software (setup).

___________________________________________________________________________________

I.34

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

P A0

R

...

O

C A14

E D0

S

S D1

A

D D7

O

R RD

WR

READY

..

.

A0

..

.

A14

..

.

6

D0

2

D1

2

D7

5

RD

WR

6

CS

A15

A0

..

.

A14

CIRCUITO

DECODIFICADOR

D0

2

D1

2

D7

5

RD

GERADOR DE

WAIT STATES

6

WR

6

CS

Figura I.18 - Circuito Gerador de “Wait States”.

___________________________________________________________________________________

I.35

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

I.5.2.2. EPROM 27128:

A EPROM 27128 é um chip de 28 pinos, como mostra a figura I.19, podendo armazenar 128

KBits (16 Kposições com 8 bits cada) de memória permanente de apenas leitura.

VPP

A12

A7

A6

A5

A4

A3

A2

A1

A0

D0

D1

D2

Gnd

2

7

1

2

8

Vcc

PGM

A13

A8

A9

A11

RD

A10

CS

D7

D6

D5

D4

D3

Figura I.19 - Pinagem da EPROM 27128

Os pinos A0,A1,A2,...,A13 são os bits de endereçamento. Como temos 14 bits de endereço a

memória EPROM 27128 possui 16K (16.536) posições.

Os pinos D0,D1,D2,...,D7 são os pinos onde se colocam os bits do conteúdo de cada posição da

memória.

Portanto a memória EPROM 27128 possui 16 536 posições de 8 bits cada uma, ou seja é uma

memória de 16 536 X 8 (que se lê: "memória de 16.536 por 8") ou de 16KBytes X 8 (que se lê:

"memória de 16 cá bytes por 8").

Os pinos de Vcc e Gnd são os pinos de alimentação do chip. Nestes dois pinos deverão ser

colocados respectivamente + 5 volts e terra.

O pino de RD é utilizado para ligarmos um sinal de controle que é gerado pelo processador. Um

pulso de nível baixo (0) significa que o processador deseja ler um dado da memória.

O pino CS tem a função de selecionar o chip. Se CS = 1 nenhuma das posições da EPROM

pode ser acessada.

A seqüência de leitura de um dado da memória EPROM é igual ao ciclo de acesso de um dado

contido em uma memória SRAM, e é a seguinte:

1.

O processador coloca no Barramento de Endereço (pinos A0,A1,...,A13) o endereço

cujo conteúdo se deseja ler.

2.

O processador dá um pulso de nível baixo no pino RD .

3.

A memória coloca no Barramento de Dados (pinos D0,D1,..,D7) o conteúdo da posição

endereçada.

4.

O processador captura este dado na borda de subida do pulso do pino RD .

A figura I.20 mostra o diagrama de tempo de um ciclo de leitura de uma memória EPROM.

___________________________________________________________________________________

I.36

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

A0

P A0

R A1

..

O

C A13

E

S D0

S D1

A

D D7

O

R RD

BARRAMENTO DE

ENDEREÇOS

..

.

A1

..

A13 7

D0

..

.

2

D1

D7

1

2

8

RD

ENDEREÇO VÁLIDO

COLOCADO PELO PROCESSADOR

RD

DADO VÁLIDO

COLOCADO PELA

MEMÓRIA

BARRAMENTO

DE DADOS

TEMPO DE

ACESSO

Figura I.20 - Ciclo de Leitura de Memória EPROM

O Barramento de Endereços, bem como o sinal de RD , têm sempre a direção do processador

para a EPROM.

O Barramento de Dados, que no caso da ligação do processador com uma memória SRAM é

bidirecional, no caso da interligação do processador com uma memória EPROM é unidierecional, só

que na direção inversa à do barramento de endereços, ou seja da EPROM para o processador. Isto se

deve ao fato da memória ser só de leitura e portanto nenhum dado pode sair do processador para

"entrar" na memória, o que corresponderia a um ciclo de escrita.

As memórias EPROM tem tempo de acesso maior que as memórias SRAMs. A memória

EPROM comercialmente disponível mais rápida possui tempo de acesso de 120 ns.

Os pinos de VPP e PGM são utilizados na hora de gravação do conteúdo da EPROM. A

gravação de uma EPROM é feita por um equipamento especial chamado gravador de EPROMs que

normalmente é interligado serial ou paralelamente a um microcomputador como visto na figura I.21.

___________________________________________________________________________________

I.37

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

VPP

A12

A7

A6

A5

A4

A3

A2

A1

A0

D0

D1

D2

Gnd

2

7

1

2

8

Vcc

PGM

A13

A8

A9

A11

RD

A10

CS

D7

D6

D5

D4

D3

FONTE DE

TENSÃO

12.5 V ou 21 V

GERADOR DE

PULSOS

SOQUETE ZERO FORCE

GRAVADOR DE EPROMS

PORTA SERIAL OU

PLACA DEDICADA

Figura I.21 - Gravador de EPROMs

Existem no mercado basicamente dois tipos de gravadores de EPROMs.

No primeiro tipo os sinais de VPP e PGM são gerados por circuitos que estão colocados em um

equipamento a parte, que além destes circuitos possui um soquete zero force onde será conectada a

EPROM a ser gravada, como visto na figura I.21. Existe um cabo padrão RS232 que interliga o

gravador de EPROMs à porta serial do microcomputador. Os valores a serem gravados são armazenados

temporariamente em arquivos nos discos flexíveis ou rígidos do microcomputador e transferidos

serialmente na hora da gravação.

___________________________________________________________________________________

I.38

Conceitos Gerais de Sistemas Computacionais

___________________________________________________________________________________

O segundo tipo se assemelha ao primeiro, no entanto os circuitos geradores dos sinais de VPP e

PGM estão em uma placa plugada em um dos slots de expansão dentro do microcomputador.

Externamente só existe uma caixa com um soquete zero force onde será conectada a EPROM e um cabo

de ligação próprio.

Para ambos os tipos cada byte a ser gravado necessita um ciclo de gravação que pode demorar

de 1 a 60 ms dependendo do tipo de EPROM. Durante todos os ciclos de gravação os pinos CS é

mantido em nível lógico 0 enquanto o pino VPP é mantido em uma tensão alta, que pode variar de 12.5

a 21 Volts dependendo da EPROM. Cada ciclo de gravação é seguido de um ciclo de leitura de

verificação. O ciclo de gravação se inicia com o endereçamento da posição a ser gravada, seguida da

colocação no barramento de dados do conteúdo a ser gravado nesta posição. Em seguida é gerado um

pulso de nível baixo no pino PGM , que pode durar de 1 a 60 ms seguido de um pulso de nível baixo no

pino RD que realiza a leitura de verificação. O pulso de RD é de duração igual a um ciclo de leitura

normal. Veja na figura I.22.

BARRAMENTO DE

ENDEREÇOS

BARRAMENTO

DE DADOS

ENDEREÇO DA POSIÇÃO A SER GRAVADA

DADO A SER GRAVADO

COLOCADO PELO

PROGRAMADOR DE EPROMs

DADO LIDO

COLOCADO

PELA EPROM

12.5 ou 21 V

VPP

1 a 60 ms

CS

PGM

RD

CICLO DE GRAVAÇÃO

CICLO DE LEITURA DE

VERIFICAÇÃO

Figura I.22 - Ciclos de Gravação e Verificação

A figura I.23 mostra a associação de uma EPROM 27128 e uma SRAM 62256 a um

microprocessador.

___________________________________________________________________________________

I.39

Arquitetura de Microcomputadores

Victor Paulo Peçanha Esteves

___________________________________________________________________________________

P A0

..

.

R

O A13

C A14

E D0

S

S D1

A

D D7

O

R RD

WR

..

.

A0

..

.

A13

6

A14

..

.

D0

2

D1

2

D7

5

RD

WR

6

CS

A15

A0

CIRCUITO

DECODIFICADOR

..

2

A13

7

D0

D1

D7

RD

1

2