Gerenciamento de Memória

(Paginação e Memória Virtual)

Prof. Alexandre Monteiro

Recife

‹#›

Contatos

Prof. Guilherme Alexandre Monteiro Reinaldo

Apelido: Alexandre Cordel

E-mail/gtalk: [email protected]

[email protected]

Site: http://www.alexandrecordel.com.br/fbv

Celular: (81) 9801-1878

DO QUE FALAMOS NA AULA PASSADA?

Memória

A memória pode ser vista

como um array (vetor) de

células de armazenamento

(palavras ou bytes), cada

célula com seu endereço

0

2

1

31

2

4

3

35

4

26

5

124

6

42

7

12

8

42

Memórias física, lógica e virtual

Memória física

• É a memória implementada pelo hardware, normalmente

associada a memória principal - RAM.

Memória lógica de um processo

• É a memória endereçada pelas instruções de máquina do

processo.

Memória Virtual

• É uma memória implementada pelo SO, com o auxílio da

memória secundária (disco rígido). Comumente, é

implementada através de paginação ou segmentação.

• Normalmente, é maior que a memória física do computador.

Gerência de Memória

Rotinas do SO que controlam o uso da memória.

• Controle de quais partes da memória encontram-se

livres e quais estão em uso

• Alocação da memória de acordo com as

necessidades dos processos

• Liberação da memória alocada após o término de

um processo

• Transferência do processo, ou parte dele, entre a

memória principal e a memória secundária

Multiprogramação através de

Swapping

O programa que perde a CPU é copiado p/

disco, enquanto o programa que ganha a CPU é

transferido do disco p/ a memória principal

reg.

limite

Monitor

Espaço

do

Usuário

Swap-in

U1

Swap-out

U2

Efeito da Multiprogramação

Utilização da CPU como função do grau de multiprogramação

(= número de processos na memória)

Realocação e Proteção

São dois problemas introduzidos pela Multiprogramação:

• Realocação: não se sabe de antemão em qual

região de memória o processo vai ser executado

• Proteção: evitar que um processo acesse uma

região usada por outro processo

Partições Múltiplas

Com multiprogramação, é

conveniente ter vários programas na

memória ao mesmo tempo para que a

CPU seja rapidamente alternada entre

eles.

Solução: dividir a memória em

partições (cada partição irá conter um

programa)

• partições fixas (normalmente o hw usa

registradores limite inferior e limite

superior)

• partições variáveis (normalmente o hw

usa registradores base e limite)

Memória com Partições Fixas

(a) Filas de entrada separadas: (Por tamanho de Processo x Partição)

(b) Fila única para todas as partições: (Simples de Implementar)

Partições Fixas

Exemplo: memória de 256K

•espaço do SO: 64K

•espaço para processos pequenos: 16K

•espaço para processos médios: 48K

•espaço para processos grandes: 128K

Memória sem Partições

Memória com Partições Fixas,

mas de tamanho variável

Pilha de B

Espaço para Expansão

Dados de B

Código de B

Pilha de A

Espaço para Expansão

Dados de A

Código de A

SO

Partições Variáveis

Os tamanhos das partições variam de acordo com a necessidade

Tamanho e número de partições variam dinamicamente

Elimina a fragmentação interna e introduz a fragmentação externa

Mais difícil de implementar

O SO mantém uma lista indicando quais partes da memória estão

disponíveis e quais estão ocupadas.

As áreas disponíveis são denominadas lacunas (holes)

Quando um processo chega para ser executado, a lista de lacunas é

consultada e é escolhida uma lacuna de tamanho suficiente

Partições Variáveis

JOB

1

2

3

4

5

Memória

60K

100K

30K

70K

50K

Tempo

10

5

20

8

15

0

0

monitor

0

monitor

40K

40K

Job 1

0

monitor

40K

Job 1

0

monitor

40K

40K

Job 5

Job 1

aloca job 5

job 1 termina

100K

monitor

100K

100K

100K

Job 4

90K

100K

Job 4

Job 4

aloca job 4

Job 2

200K

job 2 termina

200K

Job 3

170K

170K

170K

200K

200K

200K

Job 3

Job 3

Job 3

Job 3

230K

230K

230K

230K

230K

256K

256K

256K

256K

256K

Partições Variáveis:

Algoritmos de Alocação de área livre

First Fit – percorre a lista e aloca o primeiro espaço encontrado

Next Fit – como first Fit, só que a partir da posição na lista onde foi feita

a alocação anterior

Best Fit – percorre toda a lista e aloca o menor possível espaço e pode

deixar fragmentos muito pequenos para alocação para outros processos

Worst Fit – percorre toda a lista e aloca o maior possível espaço.

OBS. Em muitos sistemas, o overhead adicional exigido pelos

Best/Worst Fit não valem a pena para obter uma alocação mais

efetiva.

Partições Variáveis:

Algoritmos de Alocação de área livre

Qualquer um dos algoritmo anteriores é mais eficiente se:

• Houverem 2 listas: lista de partições usadas + lista de espaços livres

• Listas são mantidas ordenadas por tamanho (nr. de unidades de alocação)

Problema: há uma complexidade extra quando ocorre uma liberação de memória

(precisa-se verificar se há espaços adjacentes livres e inserir o novo espaço na

posição correta da lista).

Alternativa:

• Quick Fit: mantém listas separadas por tamanho do espaço livre (2K, 4K, 8K,

etc.)

• Problema: ao liberar memória, o novo espaço criado precisa ser inserido na

fila correspondente (possivelmente, após combinação com áreas vizinhas)

Atividade Valendo NOTA

Estude e siga as orientações descritas no material de aula.

Utilizando Listas ou Vetores, implemente os 5 algoritmos citados

anteriormente, de modo que resolvam os problemas de alocação

de espaços livres de memória.

Deve-se selecionar o algoritmo e este deve alocar corretamente

o espaço de memória mais conveniente de acordo com as regras

de funcionamento de cada uma dos algoritmos.

Apresentação ao final do semestre.

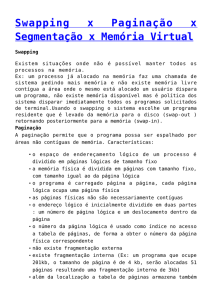

SWAPPING

Swapping

Em sistemas com compartilhamento de tempo (timesharing)

memória principal pode não ser suficiente para todos os

processos (ex. muitos processos interativos de muitos usuários)

Ideia básica: usar espaço em disco como extensão da memória

RAM, e colocar lá os processos enquanto estão bloqueados,

carregando-os de volta para a memória assim que são

desbloqueados

Duas Situações:

• Copiar a imagem inteira (Swapping)

• Permitir que processo fique parcialmente em memória,

e parcialmente em disco (paginação) -> Memória Virtual

Swapping

Quando um processo é bloqueado (espera por E/S) ele pode ser

swapped out, e depois swapped in para memória principal.

Maior número de processos ativos, aumentando a utilização da CPU

OBS 1: Buracos de memória não utilizada de tamanho qualquer

(Fragmentação de Memória)

OBS 2: Um mesmo processo pode ocupar diferentes partições ao

longo de sua execução

Fragmentação de Memória

São perdas (desperdício) de memória:

• fragmentação interna: memória é perdida dentro

da partição alocada (é um desperdício de espaço

dentro da partição usada pelo processo)

• fragmentação externa: ocorre quando existe

espaço disponível mas este é pequeno demais para

os processos que estão à espera (perda de espaço

fora das partições alocadas)

Swapping

Principal problema do swapping com partições de tamanho variável:

• Manter a informação sobre espaços não utilizados (livres)

• Evitar uma fragmentação externa da memória (= muitos

espaços pequenos não utilizados)

Compactação de memória é muito cara

– da ordem de segundos para alguns MBs de RAM.

Swapping

Como lidar com processos que crescem (em demanda de memória)?

• Tentar alocar uma partição vizinha do processo de uma partição não usada (nem sempre é possível)

• Alocar uma partição conjunta para a pilha e o heap, e fazê-los crescer em sentidos opostos.

• Se processo usa todo espaço de memória disponível, fazer um swap out, e um swap in em uma

partição maior (mas, se disco de swap está cheio, processo precisa ser terminado)

Gerenciamento de Espaço Livre

Divide a memória em unidades de alocação de n bytes e

representa a ocupação (livre/ocupado) de lotes de unidades

usando um bit map (b) ou uma lista encadeada (c).

Cada nó contém o endereço inicial e o tamanho de uma

partição ocupada ou livre.

Gerenciamento de Espaço Livre

Quando o processo é swapped out, a lacuna correspondente

precisa ser combinada com espaços vizinhos livres.

Quando processo é swapped in, percorre-se a lista buscando

um espaço livre suficientemente grande (lista geralmente

ordenada por endereços de memória)

Quando X é swapped out: quatro combinações de nós na lista

MEMÓRIA VIRTUAL

Memória Virtual

É necessária, quando o total de memória necessária para um

conjunto de processos excede o tamanho da memória física.

Também aqui, usa-se parte do disco como extensão da memória

RAM.

A grande maioria dos SO’s (exceto alguns para tempo real),

implementam Memória Virtual.

MV usa a técnica de paginação:

• Memória física e espaço de endereçamento lógico de cada

processo são divididos em partições de mesmo tamanho:

- Espaço do processo é dividido em páginas

- Memória é dividida em molduras de página

• Em vez de fazer o swap in/out de uma imagem inteira de

processo, cada página pode ser movida do disco para a memória e

vice-versa.

Paginação

Requer da existência de suporte por hardware (Memory

Management Unit - MMU)

• MMU intercepta qualquer acesso à memória (p/ instruções e dados)

• Mapeia endereços lógicos para endereços físicos (através de uma

Tabela de Página)

• Quando a página acessada não está em memória, gera uma

interrupção de falta de página (Page Fault), que causa a interrupção

do processo em execução e o seu bloqueio, até que a página tenha

sido transferida para a memória.

Paginação

A memória física é dividida em um número de partições de

mesmo tamanho, denominadas páginas físicas, quadros ou

frames ou molduras.

A memória lógica é dividida em partições do mesmo tamanho,

denominadas páginas lógicas (ou, simplesmente, páginas)

Cada página lógica é carregada em uma moldura de página

quando o processo é carregado na memória principal.

Nessa ocasião, uma Tabela de Páginas é criada.

Permite que o espaço físico ocupado por um processo seja

não contíguo.

Paginação

Exemplo: número de

páginas/processo

Processos A, B, C estão

prontos

A1

A2

A3

A

4

B

3

C

4

D

5

A4

B1

B2

B3

C1

C2

C3

C4

Paginação

B termina

D é submetido

A1

A1

A2

A2

A3

A3

A4

A4

D1

D2

D3

C1

C1

C2

C2

C3

C3

C4

C4

D4

D5

Paginação

Problemas tanto em particionamento fixo quanto dinâmico:

• fixo – fragmentação interna

• dinâmico – fragmentação externa e realocação dinâmica

Solução:

• Processo é dividido em páginas (blocos de processos)

• MP é dividida em quadros de mesmo tamanho

Páginas/quadros/molduras são de pequeno tamanho

(ex., 1K): fragmentação interna pequena.

Paginação elimina fragmentação externa.

SO mantém uma Tabela de Páginas por processo.

Paginação

Processo não precisa estar completamente na MP

(veremos adiante em Memória Virtual)

Processo não precisa ocupar área contígua em memória

Endereços são gerados dinamicamente em tempo de

execução

Somente um registrador então, não é suficiente

Tabela de Páginas

Exemplo em Memória Virtual

Espaço de

Endereçamento

Virtual

Página Virtual

Espaço de

Endereçamento

Físico

Moldura de

Página

Tabela de Páginas

Tabela de Páginas

MMU com 16 páginas de

tamanho 4 KB cada.

Endereço lógico:

Bits mais significativos = número da

página

Bits menos significativos =

deslocamento do endereço dentro

de uma página

Paginação

Se um processo tem tamanho K, os seus endereços lógicos

(endereços especificados nas suas instruções) vão desde 0 até K-1.

Este é o espaço de endereçamento do processo.

Cada endereço lógico é quebrado em duas partes:

- número da página p

- deslocamento d (offset)

Endereço lógico: composto do par (número-da-página,

deslocamento), onde número-página é usado como índice para uma

entrada na Tabela de Páginas

15

10 9

Página (p)

0

deslocamento (d)

Acontece relocação dinâmica, pois cada endereço lógico é

traduzido em endereço físico em tempo de execução

Realocação

Mapeamento de endereços virtuais em reais

necessário, pois processos são alocados em espaço de

MP dinamicamente

Ex.: processo P1

P1:

executando

novo

bloqueado

Ao voltar para MP P1 vai para end.

1024

IC - UFF

pronto

P1 em end. de MP

500

P1 passa para

suspenso

Realocação

Mapeamento eficiente

• endereço físico só calculado quando acesso a MP

• endereços definidos: lógico, relativo, físico

Registradores:

• base – armazena o endereço inicial de MP do processo (quando

o processo passa para executando)

• limite – armazena endereço final do processo

Acesso ao endereço Z no programa

IC - UFF

if (Z + base <= limite)

acesse Z+base

senão “trap”

Relocação

endereço relativo

registrador de base

PCB

somador

programa

registrador limite

comparador

endereço

absoluto

imagem do

processo na

memória

dados

int

pilha

Paginação

Paginação

Processo pode ser executado contanto que haja um número mínimo de páginas na memória (as páginas

sendo acessadas)

O espaço de endereçamento lógico é contiguo, o espaço físico equivalente é distribuído/separado.

A tradução é feita de forma transparente pela MMU, que além da TP, mantém um cache das páginas

recentemente consultadas.

Em suma Paginação

Cada processo P possui a sua Tabela de Páginas, que precisa ser carregada na MMU

a cada troca de contexto.

Para tal, cada entrada Tabela Processos(P) contém um ponteiro para a Tabela de

Páginas de P.

O dispatcher é o encarregado de "carregar" a nova tabela de páginas na MMU.

Como qualquer acesso à memória ocorre através do mapeamento pela TP. Isso

fornece também automaticamente um mecanismo de proteção...contanto que o

preenchimento da tabela de página seja feita em modo privilegiado

(supervisor)!!

=> à medida que as páginas vão sendo alocadas, o núcleo preenche as entradas na

tabela de página.

Além disto, kernel precisa manter informações sobre o conjunto de molduras livres

na memória principal:

Para isso, usa-se uma tabela de molduras (tabela de moldura de páginas), com

uma entrada por moldura, informando se o mesmo está alocado, e para qual

processo.

Tabela de Páginas – bits de controle

Cada entrada da tabela possui alguns bits adicionais para

implementar proteção

• um bit para indicar se a página é de apenas leitura

(read only)

• um bit para indicar se a página é válida ou inválida

Vejamos:

Controle de Acesso

A paginação pode ser facilmente estendida para incorporar controle de acesso

para cada página:

• além do endereço do quadro da memória, cada entrada da TP contém bits

para o tipo de acesso permitido, podendo ser: somente-leitura, leitura-eescrita ou somente-execução

• se uma instrução viola o acesso permitido, a MMU gera outra interrupção

(violação de acesso de memória)

• a validade de uma operação sob um endereço lógico pode ser testada em

paralelo com a obtenção do endereço físico correspondente.

Além disto, pode-se usar bits valido/inválido para marcar as páginas lógicas

que efetivamente compõem o espaço de endereçamento lógico do processo

• é útil para espaços de endereçamentos grandes e utilizados de forma

descontínua

• note-se que devido ao problema do não alinhamento de dados com os limites

das páginas, esse tipo de controle de acesso não é muito preciso.

Entrada da Tabela de Páginas

Cache

desabilitado

Modificada

Presente/Ausente

Número da moldura de página

Referenciada

Proteção

Implementação da Tabela de Páginas

Conjunto de registradores dedicados

Memória Principal

TLB ou Memória Associativa

Tabela de Páginas em

Conjunto de Registradores Dedicados

Na mudança de processo em execução estes registradores são

carregados com os valores correspondentes ao novo processo.

TP é mantida em um conjunto de registradores dedicados,

que são carregados através de instruções privilegiadas (ex.

DEC PDP-11)

Pró: não necessita de MMU e tradução é veloz.

Contra: número de entradas é pequeno (tipicamente, de 16 a

64)

Tabela de Páginas na

Memória Principal

Cada descritor de processo contém o endereço de sua respectiva tabela de páginas.

A UCP possui um registrador que aponta para a tabela de páginas atual

Para acessar um dado na memória são necessários dois acessos: um de

mapeamento (acesso à tabela) e outro para acessar o dado

TP é mantida em memória principal

• mantém-se um registrador com o endereço base da tabela (Process Table Base Register,

PTBR) e entrada na tabela = PTBR + #página_virtual

Prós:

• possibilita tabelas de páginas arbitrariamente grandes

• a troca de contexto envolve somente PTBR

Contras:

• tempo de acesso à memória duplica, devido ao acesso à tabela

Tabela de Páginas em

TLB ou Memória Associativa

Memória de alta velocidade (mas hardware caro), onde cada posição possui dois campos

(chave = número de página lógica, valor = página física correspondente)

Usa um Translation Look-aside Buffer (TLB, buffer para tradução de endereços) na MMU:

• TLB = vetor associativo que permite comparação paralela com suas entradas (de 8

- 128 entradas; Intel 80486 tem 32 entradas)

• mantém-se apenas as entradas da TabPaginas das páginas recentemente acessadas (

princípio de localidade)

• quando uma página lógica é acessada e seu mapeamento não está no TLB

• (TLB miss) então:

- acessa-se a TabPaginas na memória e substitui-se a entrada no TLB

- dependendo se a página está em memória ou não, continua-se a execução, ou

gera-se uma interrupção Page-fault

• a cada troca de contexto, o TLB precisa ser limpo

Vantagem: tradução rápida

Desvantagem: requer gerenciamento do conteúdo do TLB (substituição de entradas)

TLB - Translation Look-aside Buffer

Funcionamento da MMU com TLB

Ao receber um novo nº. de página (np) todas as entradas do TLB

são comparadas em paralelo:

• Se np é encontrado e tipo de acesso é válido, então usa-se a

entrada do TLB (endereço do quadro)

• Se tipo de acesso é inválido, gera-se uma falha de proteção (e

processo é abortado)

• Se np não é encontrado na TLB, (TLB miss), MMU consulta a TP em

memória, obtém o end. do quadro, e copia a entrada completa da

TP para o TLB (para agilizar acessos futuros)

• Quando houver acesso p/escrita, copia-se o flag de escrita (Modify

bit) de TLB para TP.

Obs: Pode-se aumentar a eficiência da paginação, aumentando-se

o tamanho do TLB.

TLB - Translation Look-aside Buffer

Possível configuração do TLB para um programa com:

• Um loop cujas instruções internas estão armazenadas nas

páginas 19-21, acessando um vetor nas páginas 129-130. O

índice do vetor está na pagina 140 e a pilha em 860-861.

TLB - Translation Look-aside Buffer

Em arquiteturas RISC(*), TLB misses são tratados pelo

Sistema Operacional e não pelo hardware (MMU).

Quando a MMU gera um TLB-miss, o núcleo faz o troca da

entrada da TLB.

Desvantagem: gerenciamento do TLB é muito mais lento do

que se for por hardware

Vantagem: Torna o circuito da MMU bem mais simples, e

permite a implementação em muitas arquiteturas;

Problema com Tabela de Páginas

Principal problema é que a própria TP precisa estar em memória.

-

Arquitetura de 32 bits.

Tamanho da página= 4K

Offset = 12 bits

Tabela de página = 220 entradas!

E pior, precisa-se manter uma TP por processo em execução.

Então, dependendo do número de entradas de cada TP (que

depende do tamanho da página e do número de bits da

arquitetura), pode ser inviável manter todas elas na memória do

núcleo.

O que fazer?

Tabela de Páginas Multinível

• Resolve o problema de

manter grandes tabelas de

página na memória (para

todos os processos).

• Com TP de 2 níveis, pode-se

particionar a TP principal em

páginas e manter apenas as

páginas da TP cujo

mapeamento esteja sendo

usado.

• Uma tabela de 1o. nível

contém os ponteiros para

essas partes da TP.

TP de nível 2

Tabela de Páginas Invertidas

Para arquiteturas de 64 bits, o espaço de endereçamento lógico é 264 bytes!

Exemplo: se o seu tamanho de página for 4KB, isso leva a TPs muito grandes, ex.

252 ≈ alguns Tera Bytes!).

Por isso, em alguns sistemas usa-se uma TP invertida:

Uma entrada para cada moldura de página

Cada entrada contém uma lista de pares: (processID, nº da página)

Desvantagem: a tradução de endereços lógicos para reais fica bem mais lenta.

Ex: para cada página p, precisa-se fazer uma varredura pela TP invertida para

encontrar a moldura correspondente.

Só é viável, se o TLB for usado para guardar as associações correntes. Somente

quando ocorre um TLB miss, a TP invertida precisa ser consultada.

Na maioria dos sistemas, usa-se uma função de hash para indexar as entradas da

TP invertida.

Comparação de TP tradicional e

TP invertida.

A questão do tamanho das páginas

Tamanho de página pequenos:

• Vantagens

• Melhor aproveitamento da memória física: menos fragmentação interna

• Mais programas usando a memória

• Melhor alinhamento de segmentos de código e de estruturas de dado às

páginas

• Desvantagens

• Programas precisam de mais páginas, tabelas de página maiores, mais

tempo para carregar entradas de tabela nos registradores da MMU.

• Transferência de página menor ou maior de/para disco demanda

aproximadamente o mesmo tempo (mas é feito de forma mais frequente)

Referências

Sistemas Operacionais Modernos – 3ª Edição. A.

Tanenbaum, 2008.

Modern Operating Systems 3 e. Prentice-Hall, 2008.