Trabalho de Circuitos Lógicos

Descrição VHDL e Simulação do Sistema

Prof: Adriano Cruz, auxiliar: Manuel Lois ([email protected])

Trabalho em grupos de no máximo 2 alunos. Ao entregar o trabalho, indicar os nomes.

Data de entrega do trabalho: 01/06/2000. A execução do trabalho será verificada pelo professor.

Descrição do Problema:

Um cassino (americano – porque aqui é proibido) encomenda a um analista de sistemas a construção de uma

máquina que simule a operação de jogar um dado.

Descrição da máquina: Existe um botão para apertar e simular a operação de jogar o dado (botão

“JOGAR”). Existe um mostrador (display) de sete segmentos que indica em que posição caiu o dado

(naturalmente os valores mostrados vão de 1 a 6). Existe também um botão de RESET do sistema.

Operação: O jogador aperta o botão (botão “JOGAR”) e enquanto estiver apertando é como se o dado

tivesse sido jogado e estivesse rolando pela mesa. Ao soltar o botão “jogar” o dado pára de rolar e pára numa

posição fixa, onde o valor da face superior aparece no mostrador. Se apertar de novo o botão “jogar”, o dado

é jogado novamente. Enquanto o botão de RESET está em “1”, o sistema é resetado e deverá aparecer no

f

mostrador o valor 0 (zero).

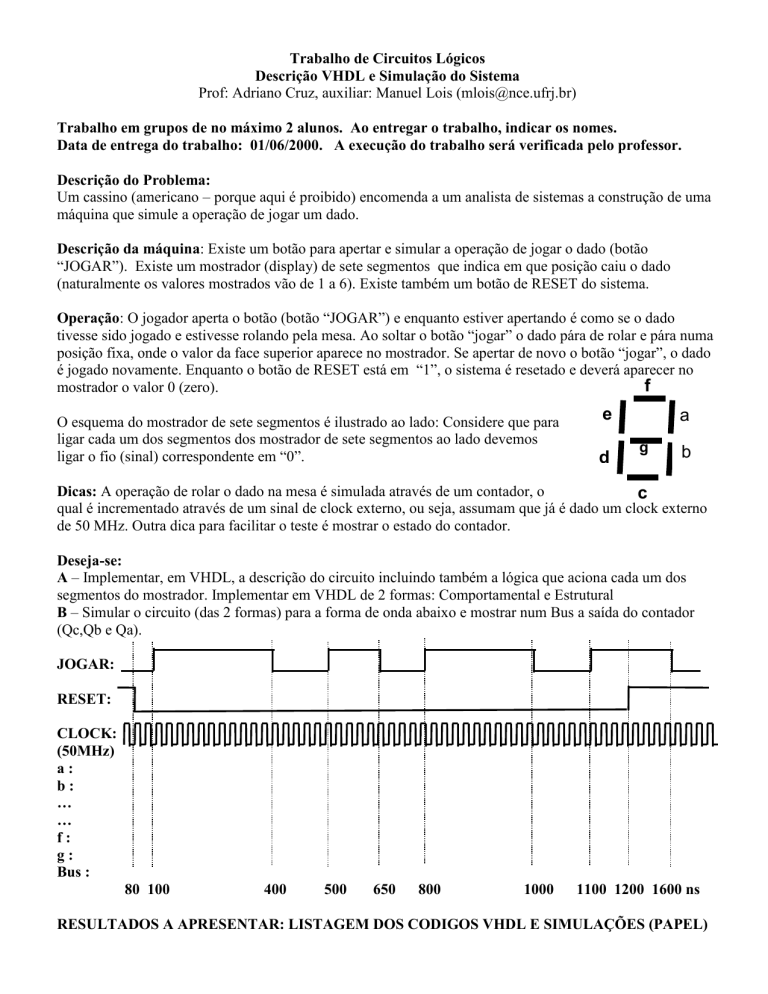

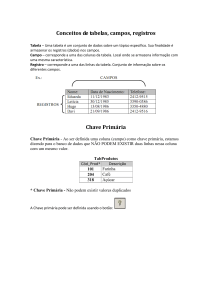

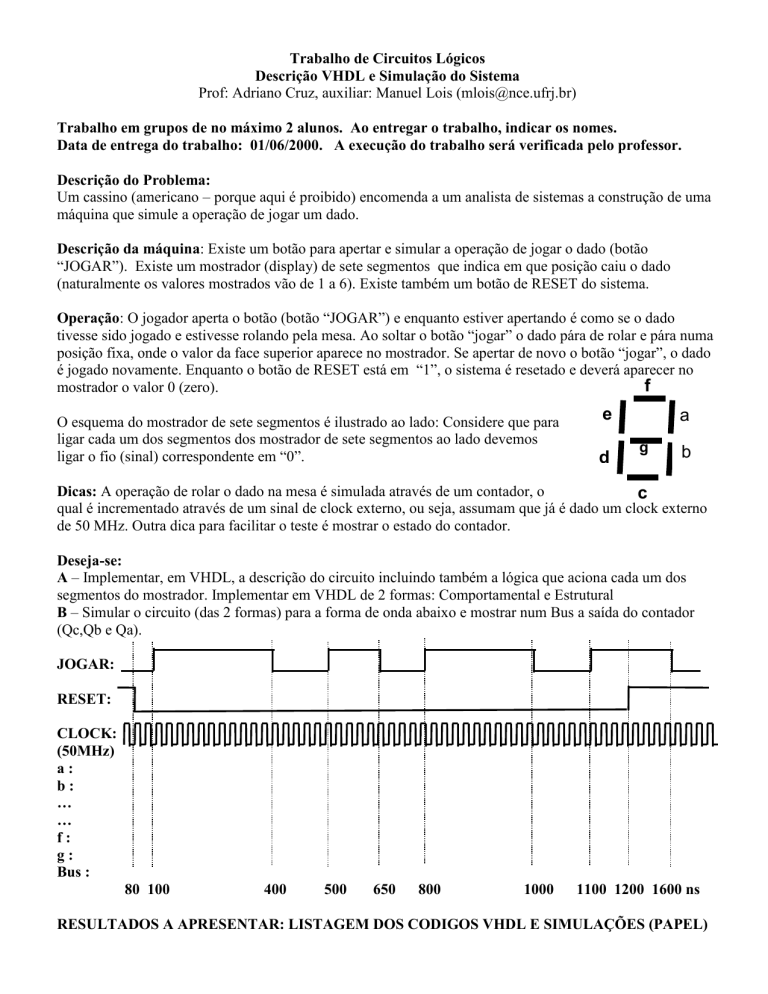

O esquema do mostrador de sete segmentos é ilustrado ao lado: Considere que para

ligar cada um dos segmentos dos mostrador de sete segmentos ao lado devemos

ligar o fio (sinal) correspondente em “0”.

e

d

a

g

b

Dicas: A operação de rolar o dado na mesa é simulada através de um contador, o

c

qual é incrementado através de um sinal de clock externo, ou seja, assumam que já é dado um clock externo

de 50 MHz. Outra dica para facilitar o teste é mostrar o estado do contador.

Deseja-se:

A – Implementar, em VHDL, a descrição do circuito incluindo também a lógica que aciona cada um dos

segmentos do mostrador. Implementar em VHDL de 2 formas: Comportamental e Estrutural

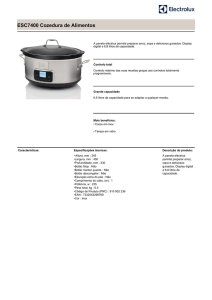

B – Simular o circuito (das 2 formas) para a forma de onda abaixo e mostrar num Bus a saída do contador

(Qc,Qb e Qa).

JOGAR:

RESET:

CLOCK:

(50MHz)

a:

b:

…

…

f:

g:

Bus :

80 100

400

500

650

800

1000

1100 1200 1600 ns

RESULTADOS A APRESENTAR: LISTAGEM DOS CODIGOS VHDL E SIMULAÇÕES (PAPEL)