UFRN – UNIVERSIDADE FEDERAL DO RIO GRANDE DO NORTE

CT – CENTRO DE TECNOLOGIA

DEE – DEPARTAMENTO DE ENGENHARIA ELÉTRICA

ELE0622 - INSTRUMENTAÇÃO ELETRÔNICA

CONVERSOR A/D POR

APROXIMAÇÕES SUCESSIVAS

ALUNOS: ANTONIO WALLACE ANTUNES SOARES

LEONARDO VALE DE ARAUJO

[email protected]

Sumário

Introdução

Conversor A/D aproximações sucessivas

Conversor D/A R-2R Ladder

Comparador

Registrador de aproximações sucessivas

Resultados obtidos

Introdução

Atualmente, existem vários tipos de sistemas que

se baseiam em grandezas analógicas, onde é

necessário que seja realizado um processamento de

dados por circuitos digitais (por exemplo, um

computador).

Para que isso ocorra, é necessário efetuar uma

conversão do sinal analógico para digital. Esta

conversão é realizada por um circuito chamado

conversor analógico/digital ("A/D converter" ou

ADC).

Introdução

Existem vários tipos de conversores A/D tais

como: comparador paralelo, rampa tipo contador,

rampa dupla tipo integrador, aproximações

sucessivas, dentre outros.

Este grupo decidiu realizar a implementação de

um conversor A/D de aproximações sucessivas

para a disciplina de Instrumentação Eletrônica

ministrada pelo professor Luciano Fontes

Cavalcanti.

Conversor A/D por aproximações sucessivas

Inicialmente, o SAR envia

metade da tensão de

referência do circuito para o

DAC.

Este valor é convertido

então é realizada a primeira

comparação com a tensão de

entrada.

Conversor A/D por aproximações sucessivas

O resultado da comparação

é enviado ao SAR que

atualiza

o

bit

mais

significativo.

Em seguida este novo valor

é convertido novamente

pelo DAC e enviado ao

comparador.

Conversor A/D por aproximações sucessivas

Após a realização deste

processo

10

vezes

(resolução adotada), o SAR

possui o valor mais

próximo da entrada.

Conversor D/A R-2R Ladder

A figura abaixo mostra um exemplo deste

conversor para 3 bits. O objetivo é encontrar a

expressão da tensão de saída.

Conversor D/A R-2R Ladder

Utilizando o teorema da superposição e analisando

primeiramente a fonte do bit mais significativo

temos que:

Q2

I=

2R

Vout

I=

Rf

Conversor D/A R-2R Ladder

Igualando as duas equações acima encontra-se

Vout. Realizando o mesmo processo acima para os

demais bits podemos chegar a seguinte equação da

tensão de saída.

Vref ∗ Rf Q0 Q1 Q2

Vout=

3

2

1

R

2

2

2

Expandindo esta fórmula para o restante dos bits

temos que:

Vref ∗ Rf Q0

Vout=

10

R

2

Q1

9

2

Q2

Q9

...

8

1

2

2

Conversor D/A R-2R Ladder

Para montar o conversor D/A foram usados dez

resistores de 100K e dez resistores de 200K.

Para o segundo DAC foram usados dez resistores

de 120K e des de 240K.

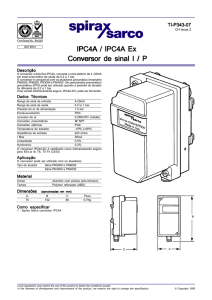

Comparador

Para o circuito do comparador de tensão utilizouse o circuito integrado LM324N.

Registrador de aproximações sucessivas

A implementação do SAR foi na linguagem de

descrição de hardware Verilog e foi simulado na

ferramenta Quartus II da Altera.

O código utilizado encontra-se em anexo no

relatório do trabalho.

A placa utilizada neste projeto foi a UP2 Altera

Max EPM7128SLC847.

Resultados obtidos

Circuito desenvolvido na Protoboard.

Resultados obtidos

Primeiro teste – Conversor A/D de 3 bits.

Resultados obtidos

Versão final do protótipo.