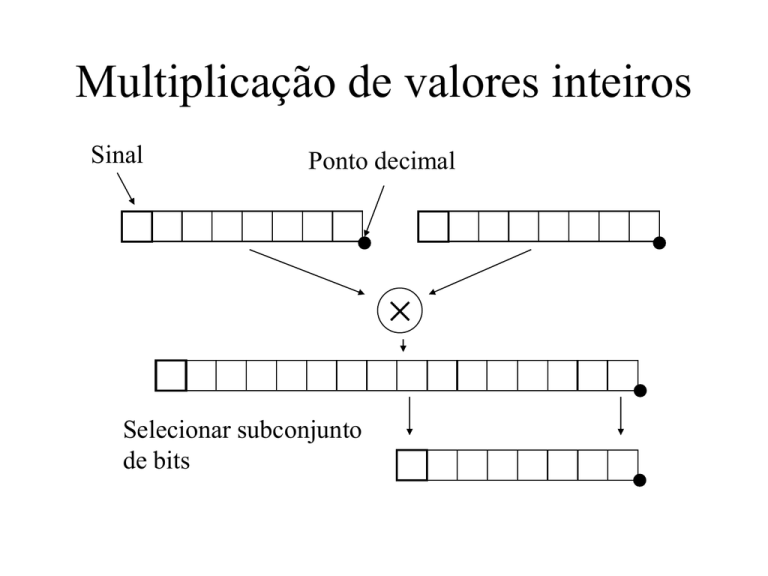

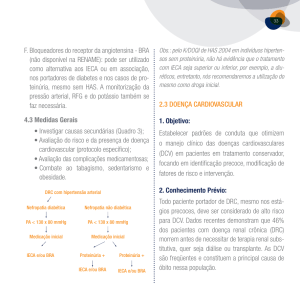

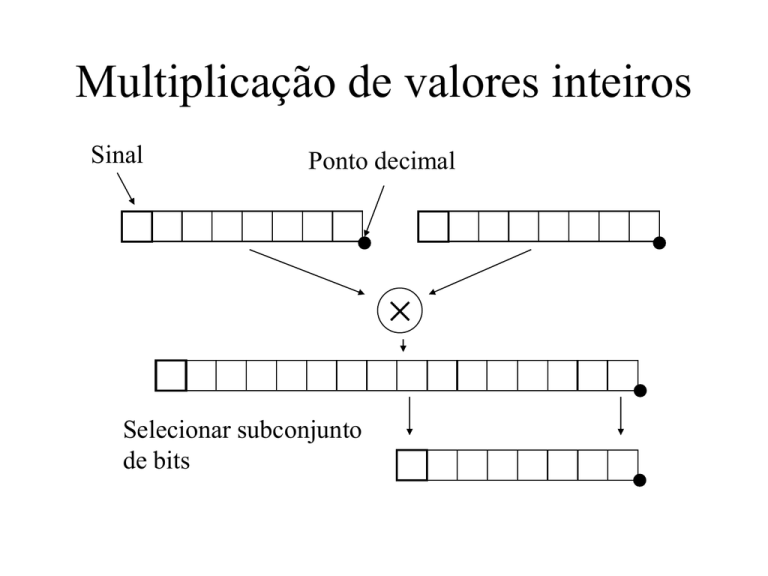

Multiplicação de valores inteiros

Sinal

Ponto decimal

Selecionar subconjunto

de bits

Soma

Multiplicação

Multiplicação de valores fracionais

Sinal

Ponto decimal

Selecionar subconjunto

de bits

Arrendondamento

A

a7

a6 a5 a4

a3 a2

a1 a0

Arredondamento para o mais próximo

B = a7:a4 + a3

B

b3

b2

b1 b0

Arredondamento convergente

if a3:a0 <> 1000

B = a7:a4 + a3

else

B = a7:a4 + a4

ULA

para

ponto

fixo

ULA

para

ponto

flutuante

Filtro FIR

(resposta finita a impulso)

Arquitetura Harvard

CPU

Barramento de Endereços A

Barramento de Dados A

Barramento de Endereços B

Barramento de Dados B

Memória A

Memória B

Modos de endereçamento

register

indirect

postincrement

Ler os dados apontados por endereço em

registrador

Depois de ter lido os dados, incremente o ponteiro

do endereço

postdecrement Depois de ter lido os dados, decremente o ponteiro

do endereço

register

postincrement

bit reversed

(borboleta

FFT)

Depois de ter lido os dados, incremente o ponteiro

do endereço de um número de posições indicado

por um registrador

Reorganize os bits de endereço para chegar

No proóximo endereço

Modos de endereçamento

Endereçamento módulo

Unidade de geração de endereços

Sem Pipelining

ciclo de relógio

1

obter

instrução

decodificar

ler/escrever

memória

executar

2

3

4

I1

5

6

7

8

I2

I1

I2

I1

I2

I1

I2

Pipelining

ciclo de relógio

obter

instrução

decodificar

ler/escrever

memória

executar

1

2

3

4

5

6

7

I1

I2

I3

I4

I5

I1

I2

I3

I4

I5

I1 I2

I3

I4

I5

I1

I2

I3

I4

8

I5

Conflito de disponibilidade

de recursos

ciclo de relógio

obter

instrução

decodificar

ler/escrever

memória

executar

1

2

3

4

5

I1

I2

I3

I4

I5

I1

I2

I3

I4

6

I2

8

I5

I1 I2 I2/3 I4

I1

7

I3

I5

I4

I5

Resolução do Conflito

usando Bloqueiamento

ciclo de relógio

obter

instrução

decodificar

ler/escrever

memória

executar

1

2

3

4

5

6

7

8

I1

I2

I3

I4

I4

I5

I1

I2

I3

I3

I4

I5

I1

I2

I2

I3

I4

I5

I1 NOP I2

I3

I4

Falha de sincronização

I1

I2

I3

MOV

SUB

MOV

R0,5678

R0,4444

X0,[R0]

Efeito de salto

ciclo de relógio

1

obter

instrução

decodificar

ler/escrever

memória

executar

2

3

4

5

BRA I2

-

-

BRA -

-

-

BRA -

-

6

7

8

N1 N2

N1 N2

-

N1 N2

BRA NOPNOPNOP N1

Solução: salto com retardo

I1

I2

I3

I4

BRA

SUB

MOV

ADD

5678

R0,R2

R3,R2

R4,R5

;salto para novo endereço

;estas três

;instruções são executadas

;antes de salto

• problema: salto condicional

Solução: salto com retardo

ciclo de relógio

1

obter

instrução

decodificar

ler/escrever

memória

executar

2

3

4

BRA I2

I3

I4 N1 N2

BRA I2

I3

BRA I2

5

6

7

8

I4 N1 N2

I3

BRA I2

I4 N1 N2

I3

I4 N1

Resumo

Diferenças entre DSP e processador comum

• DSPs são feitas para aplicações embarcadas de

processamento de sinais em tempo real

• DSPs não podem ser programado pelo usuário

(não existe UGM, nem SO, nem cache, nem multiprocessamento)

• DSPs usam alguma forma de "Arquitetura

Harvard"

• DSPs dedicam uma parte significativa de

superfície de silício para operações de

multiplicação/acumulação

Resumo (continuação)

Diferenças entre DSP e processador comum

• Programas de DSPs estão armazenadas

frequentemente em ROM on-chip

• DSPs frequentemente possuem dois RAMs

on-chip para dados

• O mecanismo de interrupção de DSPs é

simples e rápido

• DSPs são frequentemente programados em

Assembler

Resumo (continuação )

2

Diferenças entre DSP e processador comum

• Mecanismo de E/S simples

• Espaço de endereçamento reduzido

• DSPs de ponto fixo podem usar saturação em vez

de estouro

• Modos de endereçamento específicos (buffer

circular, "borboleta")

• Suporte para laços e as vezes pilha on-chip

• benchmark para DSPs são diferentes: :

– Filtro FIR/IIR, FFTs

– Convolução, Produto de vetores