Prova P4/PS

Disciplina: Organização de Computadores-EC

Professor: Ney Laert Vilar Calazans

Aluno:

30/novembro/2016

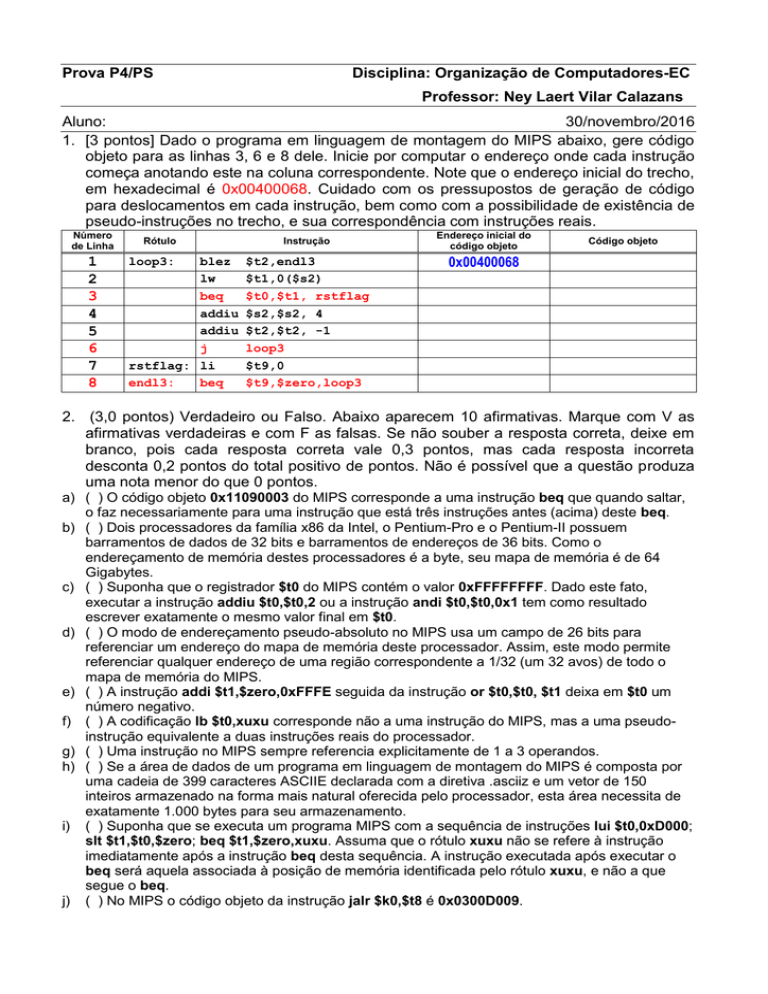

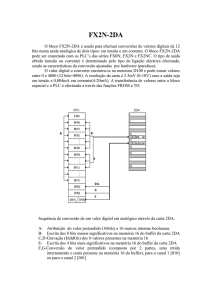

1. [3 pontos] Dado o programa em linguagem de montagem do MIPS abaixo, gere código

objeto para as linhas 3, 6 e 8 dele. Inicie por computar o endereço onde cada instrução

começa anotando este na coluna correspondente. Note que o endereço inicial do trecho,

em hexadecimal é 0x00400068. Cuidado com os pressupostos de geração de código

para deslocamentos em cada instrução, bem como com a possibilidade de existência de

pseudo-instruções no trecho, e sua correspondência com instruções reais.

Número

de Linha

1

2

3

4

5

6

7

8

Rótulo

loop3:

blez

lw

beq

addiu

addiu

j

rstflag: li

endl3:

beq

Instrução

$t2,endl3

$t1,0($s2)

$t0,$t1, rstflag

$s2,$s2, 4

$t2,$t2, -1

loop3

$t9,0

$t9,$zero,loop3

Endereço inicial do

código objeto

Código objeto

0x00400068

2. (3,0 pontos) Verdadeiro ou Falso. Abaixo aparecem 10 afirmativas. Marque com V as

afirmativas verdadeiras e com F as falsas. Se não souber a resposta correta, deixe em

branco, pois cada resposta correta vale 0,3 pontos, mas cada resposta incorreta

desconta 0,2 pontos do total positivo de pontos. Não é possível que a questão produza

uma nota menor do que 0 pontos.

a) ( ) O código objeto 0x11090003 do MIPS corresponde a uma instrução beq que quando saltar,

o faz necessariamente para uma instrução que está três instruções antes (acima) deste beq.

b) ( ) Dois processadores da família x86 da Intel, o Pentium-Pro e o Pentium-II possuem

barramentos de dados de 32 bits e barramentos de endereços de 36 bits. Como o

endereçamento de memória destes processadores é a byte, seu mapa de memória é de 64

Gigabytes.

c) ( ) Suponha que o registrador $t0 do MIPS contém o valor 0xFFFFFFFF. Dado este fato,

executar a instrução addiu $t0,$t0,2 ou a instrução andi $t0,$t0,0x1 tem como resultado

escrever exatamente o mesmo valor final em $t0.

d) ( ) O modo de endereçamento pseudo-absoluto no MIPS usa um campo de 26 bits para

referenciar um endereço do mapa de memória deste processador. Assim, este modo permite

referenciar qualquer endereço de uma região correspondente a 1/32 (um 32 avos) de todo o

mapa de memória do MIPS.

e) ( ) A instrução addi $t1,$zero,0xFFFE seguida da instrução or $t0,$t0, $t1 deixa em $t0 um

número negativo.

f) ( ) A codificação lb $t0,xuxu corresponde não a uma instrução do MIPS, mas a uma pseudoinstrução equivalente a duas instruções reais do processador.

g) ( ) Uma instrução no MIPS sempre referencia explicitamente de 1 a 3 operandos.

h) ( ) Se a área de dados de um programa em linguagem de montagem do MIPS é composta por

uma cadeia de 399 caracteres ASCIIE declarada com a diretiva .asciiz e um vetor de 150

inteiros armazenado na forma mais natural oferecida pelo processador, esta área necessita de

exatamente 1.000 bytes para seu armazenamento.

i) ( ) Suponha que se executa um programa MIPS com a sequência de instruções lui $t0,0xD000;

slt $t1,$t0,$zero; beq $t1,$zero,xuxu. Assuma que o rótulo xuxu não se refere à instrução

imediatamente após a instrução beq desta sequência. A instrução executada após executar o

beq será aquela associada à posição de memória identificada pelo rótulo xuxu, e não a que

segue o beq.

j) ( ) No MIPS o código objeto da instrução jalr $k0,$t8 é 0x0300D009.

Rs

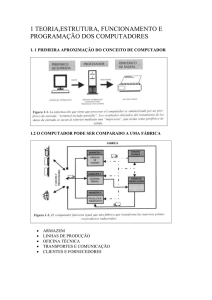

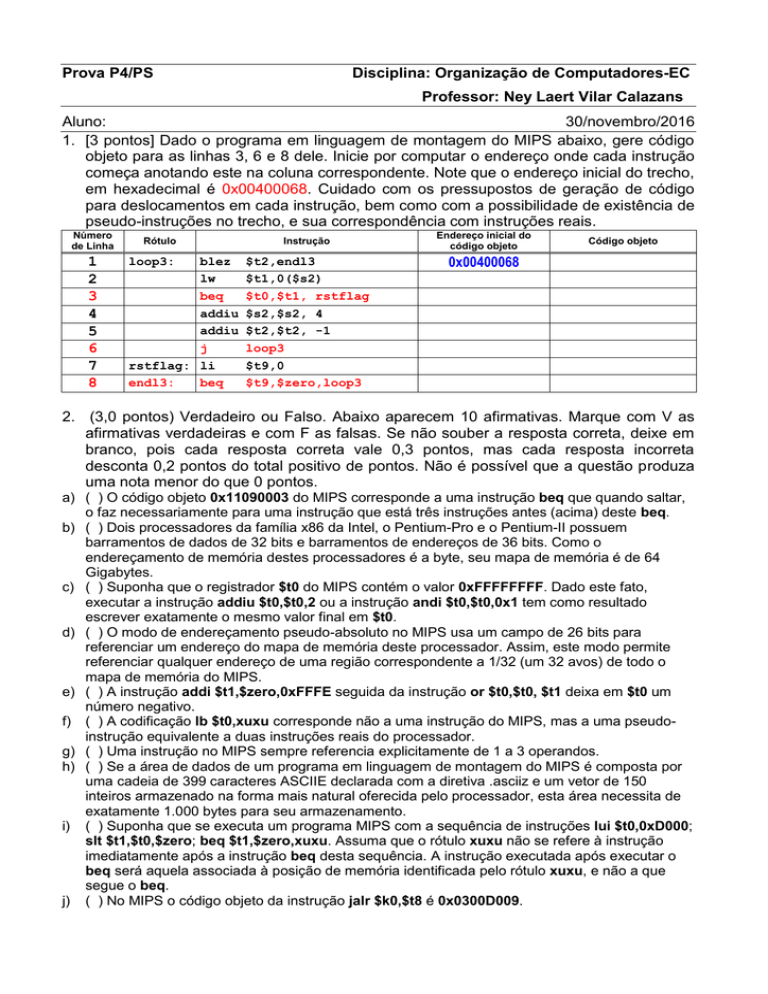

3. [4 pontos] Considere a organização do bloco de dados multiciclo, que dá suporte à

execução de um subconjunto da arquitetura do conjunto de instruções do MIPS.

Considere também como realizadas as modificações necessárias nesta organização

para dar suporte à instrução LH, similar a instrução usada no trabalho TP3 deste

semestre. Responda às questões abaixo.

end_mul

quociente

Rs

Decodificação

DIV

rst_md

11111

IR[20:16]

IR[15:11]

i

adD

NPC

PC

wpc

I/ salta_in

pc=i_address

IR[25:21]

Memória de

Instruções

dtpc

IR[20:16]

CY1

R1

Banco de

Registradores

Rs

AdRP2

R2

wreg

Rt

i

Hi

Hi

x“000000” &

data[7:0]

i

i

outalu

RALU

walu

Rt

op2

i

instruction

i

i

IR[15:0]

EXT SINAL

<< 2

IR[25:0]

IR[15:0]

“0000” &

IR[25:0] & “00”

cte_im

i

Rs

Rt

EXT ZERO

MDR

wmdr

data

rw

ce

IMED

IMED

CY2

ce rw bw

whilo

Rs

CY2

DataRP2

IR[20:16]

produto(63

downto 32)

npc

op1

AdRP1

DataRP1

i

IR_IN=IR=IR_OUT

IR

resto

comparador

CY1

pc=i_address

RIN

AdWP DataWP

adS

+4

MULT

ALU

NPC

inc_pc

produto(31

downto 0)

rst_md

i

MDR

i

Rt

MDR_int

RESULT

Memória

de Dados

NPC

npc=NPC_OUT=NPC

Lo

Lo

RALU=d_address

wreg

wpc

CY1

whilo

rw

CY2

rst_md

ce

walu

bw

wmdr

whilo

D_Lo

end_div

IR

i

D_Hi

Máquina de

Estados

salta_in=

salta=

salta_out

Rt

Rt

a) [1 ponto] Marque no desenho acima e/ou descreva com palavras todos os caminhos do

bloco de dados efetivamente usados pela instrução LH Rt, Offset(Rs). Isto significa marcar

e/ou descrever em texto todos os caminhos por onde passa informação útil relevante à

execução da instrução, ou seja, dados e sinais de controle que esta instrução realmente

necessita manipular durante sua execução.

b) [1 ponto] Diga qual operação é executada pela unidade lógica-aritmética (ALU) no terceiro

ciclo de relógio da instrução LH Rt, Offset(Rs), justificando sua resposta.

c) [1 ponto] No processo de execução da instrução LH Rt, Offset(Rs) existe alguma

modificação de hardware necessária no bloco de dados (BD) do processador? Se sim,

explique qual. Em qualquer caso, explique os motivos que levam à modificação ou não do

BD.

d) [1 ponto] Suponha que se deseja modificar o processador para poder executar esta

instrução em apenas 4 ciclos de relógio. Descreva a modificação do bloco de dados que

poderia viabilizar esta otimização.

Lista de associação de números e mnemônicos para os registradores do MIPS

Número (Decimal)

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Nome

$zero

$at

$v0

$v1

$a0

$a1

$a2

$a3

$t0

$t1

$t2

$t3

$t4

$t5

$t6

$t7

Número (Decimal)

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Nome

$s0

$s1

$s2

$s3

$s4

$s5

$s6

$s7

$t8

$t9

$k0

$k1

$gp

$sp

$fp

$ra

Prova P4/PS

Disciplina: Organização de Computadores-EC

Professor: Ney Laert Vilar Calazans

Aluno:

30/novembro/2016

Gabarito

1. [3 pontos] Dado o programa em linguagem de montagem do MIPS abaixo, gere código

objeto para as linhas 3, 6 e 8 dele. Inicie por computar o endereço onde cada instrução

começa anotando este na coluna correspondente. Note que o endereço inicial do trecho,

em hexadecimal é 0x00400068. Cuidado com os pressupostos de geração de código

para deslocamentos em cada instrução, bem como com a possibilidade de existência de

pseudo-instruções no trecho, e sua correspondência com instruções reais.

Número

de Linha

1

2

3

4

5

6

7

8

Instrução

Endereço inicial do

código objeto

$t2,endl3

$t1,0($s2)

$t0,$t1, rstflag

$s2,$s2, 4

$t2,$t2, -1

loop3

$t9,0

$t9,$zero,loop3

0x00400068

0x0040006c

0x00400070

0x00400074

0x00400078

0x0040007C

0x00400080

0x00400084

Rótulo

loop3:

blez

lw

beq

addiu

addiu

j

rstflag: li

endl3:

beq

Código objeto

0x11090003

0x0810001A

0x1320FFF8

Solução da Questão 1

Partindo do endereço inicial dado, geram-se os endereços de quatro em quatro para cada

linha do programa. A seguir, pode-se gerar o código objeto das instruções solicitadas.

a) (1,0 ponto) Linha 3: beq

$t0, $t1, rstflag. O formato da instrução beq é:

beq

rs,rt, label

0x4

rs rt offset

Número de bits/campo: 6

5 5

16

O código objeto é então: 000100 (4 em seis bits) concatenado com o endereço do Rs no banco

($t0=8 ou 01000 em binário), concatenado com o endereço do Rt no banco, 01001 ($t1=9),

concatenado com o offset. Segundo a definição da arquitetura, este é o valor de 16 bits que

corresponde à distância, em instruções, da linha abaixo do beq até a linha do rótulo rstflag ou seja,

3, ou em binário 0000 0000 0000 0011. Juntando os 32 bits (000100 01000 01001 0000 0000 0000

0011) e traduzindo-os de 4 em 4 em valores hexadecimais, obtém-se 0x11090003, no endereço da

memória de instruções 0x00400070.

b) (1,0 ponto) Linha 6: j

loop3.

O formato da instrução j é:

j label

2 address

Número de bits/campo: 6

26

O código objeto é então: 000010 (2 em seis bits) concatenado com um valor de 26 bits, que

corresponde ao bits 27 a 2 do endereço do rótulo loop3. Como loop3 está na linha cujo endereço

associado é 0x00400068, basta pegar os bits 27 a 2 deste valor de 32 bits. Juntando os 32 bits,

tem-se (000010 00000100000000000000011010) e traduzindo-os de 4 em 4 em valores

hexadecimais, obtém-se 0x0810001A, no endereço da memória de instruções 0x0040007C.

c) (1,0 pontos) Linha 8: beq

$t9, $zero, loop3.

beq

0x4

Número de bits/campo: 6

O formato da instrução beq é:

rs,rt, label

rs rt offset

5 5

16

O código objeto é então: 000100 (4 em seis bits) concatenado com o endereço do Rs no banco

($t9=25 ou 11001 em binário), concatenado com o endereço do Rt no banco, 00000 ($zero=0),

concatenado com o offset. Segundo a definição da arquitetura, este é o valor de 16 bits que

corresponde à distância, em instruções, da linha abaixo do beq até a linha do rótulo loop3. Como

loop3 está antes desta linha o valor é negativo, e vai ser -8, ou em binário 1111 1111 1111 1000.

Juntando os 32 bits (000100 11001 00000 1111111111111000) e traduzindo-os de 4 em 4 em

valores hexadecimais, obtém-se 0x1320FFF8, no endereço da memória de instruções 0x00400084.

Fim da Solução da Questão 1

2. (3,0 pontos) Verdadeiro ou Falso. Abaixo aparecem 10 afirmativas. Marque com V as

afirmativas verdadeiras e com F as falsas. Se não souber a resposta correta, deixe em

branco, pois cada resposta correta vale 0,3 pontos, mas cada resposta incorreta

desconta 0,2 pontos do total positivo de pontos. Não é possível que a questão produza

uma nota menor do que 0 pontos.

Solução da Questão 2

a) (F) O código objeto 0x11090003 do MIPS corresponde a uma instrução beq que quando saltar,

o faz necessariamente para uma instrução que está três instruções antes (acima) deste beq.

Falso. Trata-se de um beq, pois os seis primeiros bits de 0x11090003 são 000100, que é o

opcode do beq. Contudo, o deslocamento (offset) está nos 16 últimos bits do código objeto, e

vale 0x0003, um número positivo. Logo, o salto é para baixo e não para cima.

b) (V) Dois processadores da família x86 da Intel, o Pentium-Pro e o Pentium-II possuem

barramentos de dados de 32 bits e barramentos de endereços de 36 bits. Como o

endereçamento de memória destes processadores é a byte, seu mapa de memória é de 64

Gigabytes.

Verdadeiro, pois com 36 bits no barramento de endereços o mapa terá 2*36=64Giga endereços.

Como cada endereço contém 1 byte (endereçamento a byte) o tamanho do mapa é 64Gbytes.

c) (V) Suponha que o registrador $t0 do MIPS contém o valor 0xFFFFFFFF. Dado este fato,

executar a instrução addiu $t0,$t0,2 ou a instrução andi $t0,$t0,0x1 tem como resultado

escrever exatamente o mesmo valor final em $t0.

Verdadeiro. O valor inicial em $t0 é -1 em complemento de 2. Ora somar 2 a -1 gera em $t0 o

valor 1. Por outro lado, a instrução andi com uma máscara 1 em 16 bits usa extensão de 0 para

gerar 1 em 32 bits. O and deste valor com qualquer coisa gera em $t0 um valor onde todos os

bits são zero, exceto o bit 0 que é uma cópia do bit 0 do valor original, que era 1. Isto vai gerar o

mesmo número 0x00000001 em $t0.

d) (F) O modo de endereçamento pseudo-absoluto no MIPS usa um campo de 26 bits para

referenciar um endereço do mapa de memória deste processador. Assim, este modo permite

referenciar qualquer endereço de uma região correspondente a 1/32 (um 32 avos) de todo o

mapa de memória do MIPS.

Falso. Os 26 bits são sempre concatenados com dois bits 00 à direita e com os 4 bits mais

significativos do PC à esquerda. Assim o número de endereços abrangidos é 2*26, que

corresponde a 1/64 do mapa de memória. Contudo, os endereços sempre são múltiplos de 4.

Assim estes 1/64 dos endereços vão de 4 em 4 em uma região de tamanho total de 1/16 do

mapa de memória.

e) (V) A instrução addi $t1,$zero,0xFFFE seguida da instrução or $t0,$t0, $t1 deixa em $t0 um

número negativo.

Verdadeiro. A addi usa extensão de sinal. Assim, ela coloca em $t1 o resultado da soma

0x00000000(conteúdo de $zero)+0xFFFFFFFE(0xFFFE com sinal estendido)=0xFFFFFFFE. Ao

se fazer o or do valor em $t1 com o que quer que exista em $t0, todos os bits que estão em 1

de $t1 ou em $t0 ficarão em 1. Logo, dependendo do conteúdo inicial de $t0, apenas um de

dois valores pode resultar escrito em $t0: 0xFFFFFFFE ou 0xFFFFFFFF, e ambos são números

negativos.

f) (V) A codificação lb $t0,xuxu corresponde não a uma instrução do MIPS, mas a uma pseudoinstrução equivalente a duas instruções reais do processador.

Verdadeiro. Como não foi especificado um deslocamento, será gerada uma instrução lui para

carregar a parte alta do endereço xuxu em $at e este será o registrador base do lb, que terá

como deslocamento a parte baixa do endereço xuxu. As duas instruções são lui $at,parte alta

de xuxu; lb $t0, parte baixa de xuxu($at).

g) (F) Uma instrução no MIPS sempre referencia explicitamente de 1 a 3 operandos.

Falso. Um contra-exemplo é a instrução syscall, que não tem operandos explícitos.

h) (V) Se a área de dados de um programa em linguagem de montagem do MIPS é composta por

uma cadeia de 399 caracteres ASCIIE declarada com a diretiva .asciiz e um vetor de 150

i)

j)

inteiros armazenado na forma mais natural oferecida pelo processador, esta área necessita de

exatamente 1.000 bytes para seu armazenamento.

Verdadeiro. Usando a diretiva asciiz, uma cadeia ocupa exatamente um caracter a mais que o

texto que ela referencia, devido ao acréscimo automático do caractere NULL para indicar o fim

da cadeia. O formato mais natural para representar inteiros no MIPS é usar a diretiva .word, que

reserva 32 bits ou 4 bytes por numeral inteiro. Assim, a área de dados necessária é

399+1+250*4=1000 bytes.

(F) Suponha que se executa um programa MIPS com a sequência de instruções lui $t0,0xD000;

slt $t1,$t0,$zero; beq $t1,$zero,xuxu. Assuma que o rótulo xuxu não se refere à instrução

imediatamente após a instrução beq desta sequência. A instrução executada após executar o

beq será aquela associada à posição de memória identificada pelo rótulo xuxu, e não a que

segue o beq.

Falso. A instrução lui deixa em $t0 o valor 0xD0000000, que corresponde a um número

negativo em complemento de 2, pois seu bit 31 é 1. Logo, a instrução slt, que faz uma

comparação de valores considerando os mesmos como inteiros escreve em $t1 o valor

0x00000001, pois $t0 é menor que 0. Finalmente, a condição do beq será falsa, e não há salto.

(V) No MIPS o código objeto da instrução jalr $k0,$t8 é 0x0300D009.

Verdadeiro. O formato da instrução jalr usada aqui é:

jalr

0x0

rd, rs

rs 0 rd 0

9

Número de bits/campo:

6

5 5 5 5 6.

O código objeto é então: 000000 (0 em seis bits) concatenado com o endereço do rs no banco

($t8=24 ou 11000 em binário), concatenado com 5 bits em 0, concatenado com o endereço do

rd no banco, 11010 ($k0=26), concatenado com 5 bits em 0 e concatenado com 001001 (9 em

seis bits). Juntando os valores dos seis campos tem-se (000000 11000 00000 11010 00000

001001). Agrupando os bits de 4 em 4 obtém-se o código objeto no formato desejado, que é

0x0300D009.

Fim da Solução da Questão 2

3. [4 pontos] Considere a organização do bloco de dados multiciclo, que dá suporte à

execução de um subconjunto da arquitetura do conjunto de instruções do MIPS.

Considere também como realizadas as modificações necessárias nesta organização

para dar suporte à instrução LH, similar a instrução usada no trabalho TP3 deste

semestre. Responda às questões abaixo.

D_Lo

end_mul

end_div

IR

quociente

Rs

Decodificação

DIV

rst_md

RESULT

11111

IR[20:16]

IR[15:11]

i

adD

dtpc

PC

wpc

I/ salta_in

pc=i _address

DataRP1

R1

Rs

CY1

IR[20:16]

DataRP2

R2

wreg

i

CY2

AdRP2

Rt

x“000000” &

data[7:0]

outalu

RALU

walu

Rt

op2

i

instruction

i

i

IR[15:0]

EXT SINAL

<< 2

IR[25:0]

IR[15:0]

“0000” &

IR[25:0] & “00”

EXT ZERO

cte_im

i

data

Rs

Rt

salta_in=

salta=

salta_out

Rt

MDR

wmdr

Sig_extend(Data(

15 downto 0))

rw

ce

IMED

IMED

CY2

ce rw bw

Rs

i

Banco de

IR_IN=IR =IR_OUT

R egistradores

IR

Hi

whilo

i

op1

AdRP1

IR[25:21]

i

Hi

produto(63

downto 32)

npc

adS

IR[20:16]

resto

c omparador

pc =i_address

M emória de

Instruções

CY1

RIN

AdWP DataWP

NPC

MULT

ALU

NPC

inc_pc

+4

produto(31

downto 0)

rst_md

i

MDR

i

Rt

MDR_int

NPC

npc =NPC_OUT=NPC

Lo

Lo

Memória

de Dados

wreg

wpc

CY1

whilo

rw

CY2

rst_md

ce

walu

bw

wmdr

whilo

RALU=d_ address

i

D_Hi

Máquina de

Estados

Rt

a) [1 ponto] Marque no desenho acima e/ou descreva com palavras todos os caminhos do

bloco de dados efetivamente usados pela instrução LH Rt, Offset(Rs). Isto significa marcar

e/ou descrever em texto todos os caminhos por onde passa informação útil relevante à

execução da instrução, ou seja, dados e sinais de controle que esta instrução realmente

necessita manipular durante sua execução.

b) [1 ponto] Diga qual operação é executada pela unidade lógica-aritmética (ALU) no terceiro

ciclo de relógio da instrução LH Rt, Offset(Rs), justificando sua resposta.

c) [1 ponto] No processo de execução da instrução LH Rt, Offset(Rs) existe alguma

modificação de hardware necessária no bloco de dados (BD) do processador? Se sim,

explique qual. Em qualquer caso, explique os motivos que levam à modificação ou não do

BD.

d) [1 ponto] Suponha que se deseja modificar o processador para poder executar esta

instrução em apenas 4 ciclos de relógio. Descreva a modificação do bloco de dados que

poderia viabilizar esta otimização.

Solução da Questão 3

a) (1,0 ponto). Ver desenho. Depois da busca da instrução, os bits 25:21 do IR são usados para

endereçar a Porta de leitura 1 do banco de registradores, o que provoca a recuperação de

uma valor do banco, que é colocado no registrador Rs. Este valor vai para a entrada superior

da ALU. Na entrada inferior da ALU chega o deslocamento, proveniente dos bits 15:0 do IR,

que passa pelo bloco de extensão de sinal, o registrador IMED e dois multiplexadores. A

ULA soma estes valores, gerando o endereço de leitura que é enviado à memória ao ser

armazenado no registrador RALU. A memória é lida e o dado no endereço gerado é

mandado de volta ao processador. Na entrada do processador, usa-se apenas os 16 bits

inferiores do dado de 32 bits lido, que tem seu sinal estendido para gerar um valor de 32 bits.

Este é então armazenado no registrador MDR. Para finalizar, o conteúdo do MDR é escrito

no banco, no registrador endereçado pelos bits 20:16 do IR (endereço do registrador Rt).

b) (1,0 ponto). A operação executada é uma soma, conforme explicado no item a).

c) (1,0 ponto). Sim, é necessário acrescentar um módulo que faça a extensão de sinal dos 16

bits inferiores do barramento de dados (sinal data(15 downto 0). A saída deste módulo

constitui uma terceira entrada do mux que gera a entrada do registrado MDR. O mux em

questão deve obviamente ser modificado também.

d) (1,0 ponto). Isto é facilmente realizado, embora tenha um custo em termos de desempenho.

Uma solução é fazer com que a saída do novo módulo de extensão de sinal não vá para o

mux que gera a entrada do MDR, e sim para o mux que gera o sinal result. Claro que o

bloco de controle deve ser modificado para gerar os sinais de controle de acordo.

Fim da Solução da Questão 3