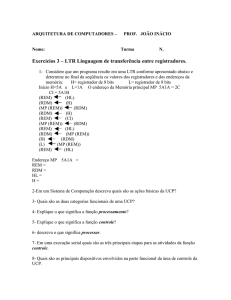

Instruções de Máquina

Operação básica (primitiva) que o hardware é

capaz de executar diretamente

◦ Conjunto de bits que indica ao processador uma

operação que ele deve realizar

O projeto de um processador é centrado no

conjunto de instruções de máquina que se

deseje que ele execute

Quanto menor e mais simples o conjunto de

instruções, mais rápido é o ciclo de tempo do

processador

Existem duas tecnologias de projeto de

computadores:

◦ Sistemas com conjunto de instruções complexo

(complex instruction set computers – CISC)

◦ Sistemas com conjunto de instruções reduzido

(reduced instruction set computers – RISC)

Um processador possui instruções capazes

de realizar:

◦ Operações matemáticas

◦ Movimentação de dados (memória – UCP e viceversa)

◦ Entrada e saída (leitura e escrita em dispositivo de

E/S)

◦ Controle (desvio de seqüência de execução, parar,

etc...)

Exemplos:

◦

◦

◦

◦

Intel 8080: 78 instruções

Intel 8088: 117 instruções

80486: 286 instruções

Pentium II: 217 instruções

Uma instrução é dividida basicamente em dois

campos:

Código de operação

ou opcode

C. Op.

Operandos

◦ Código de Operação: indica qual operação deverá

ser realizada, por exemplo:

Realizar uma operação lógica entre dois valores

Parar a execução de um programa

Testar uma condição: Se teste verdadeiro, então

desviar para outro endereço fora da seqüência

O campo código de operação possui, nos

processadores atuais, 1 byte de tamanho

Pode-se, então, ter 28 instruções diferentes

◦ Operando: indica a localização do dado que será

manipulado

O campo operando pode estar subdividido em outros

campos no caso de mais de um operando, por

exemplo:

Em uma instrução cujo código de operação é uma soma,

são necessários três operandos

Dois operandos para armazenar as parcelas

Um operando para armazenar o total

Instrução de Soma:

C. Op.

Operando 1

(operando 3)

Operando 2

Operando 3

(operando 1) + (operando 2)

Outro formato para instrução de soma que

produz o mesmo efeito:

C. Op.

Operando 1

Operando 2

(operando 1)

(operando 1) + (operando 2)

(operando 2)

(operando 1) + (operando 2)

Pode-se também usar o registrador

acumulador para representar a mesma

operação

C. Op.

ACC

Operando

ACC + (operando)

Iremos analisar as etapas realizadas pelo

processador para a execução de uma

instrução de máquina

Ciclo de

Instrução

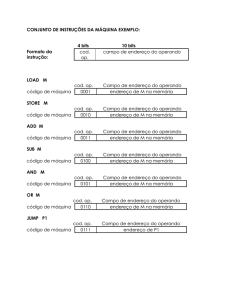

Iremos considerar um computador hipotético

com as seguintes características:

◦

◦

◦

◦

◦

Palavra de 12 bits

Endereços de 8 bits (256 células de memória)

Células de 12 bits

ACC, RI e RDM com 12 bits de tamanho

CI e REM com 8 bits de tamanho

◦ Instruções de um operando apenas

C. Op. de 4 bits e operando de 8 bits

Campo operando sempre indica o endereço de memória

do dado, exceto em instruções de desvio

C. OP.

4 bits

Operando

8 bits

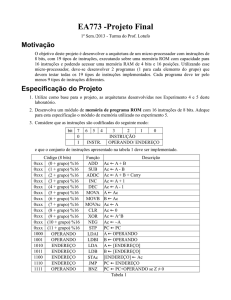

Instruções disponíveis: listadas na

tabela a seguir

C. Op.

0

Sigla

HLT

Descrição

Parar execução do programa

(HALT, em inglês)

1

LDA op ACC

(op)

(LOAD, em inglês)

2

STR op (op)

ACC

(STORE, em inglês)

3

ADD op ACC

ACC + (op)

4

SUB op ACC

ACC - (op)

5

JZ op

Se ACC = 0, então CI

op

6

JP op

Se ACC > 0, então CI

op

7

JN op

Se ACC < 0, então CI

op

8

JMP op CI

op

C. Op.

9

A

Sigla

Descrição

Ler dado da porta de entrada e armazená-lo

GET op

em Op

Colocar na porta referente à impressora o

PRT op

valor armazenado em (op)

O ciclo de instrução pode ser mais detalhado

conforme as especificações do processador

listadas anteriormente

Início

Buscar a próxima

instrução

Interpretar instrução

(decodificar)

Executar instrução

Armazenar

resultados

Buscar operandos

Fim

Início

Subciclo

de

busca

Buscar a próxima instrução

Incrementar O CI

Decodificação do C. Op.

Subciclo

de

Execução

Tem operando?

sim

Buscar e

armazenar operando

não

Executar a operação

Armazenar resultados

Fim

A fase de busca de instrução é idêntica para

qualquer instrução

A fase de decodificação e execução depende

da instrução

Vamos analisar como exemplo a execução de

duas instruções na seguinte seqüência:

LDA op e ADD op

Considere que a instrução LDA está

armazenada na MP no endereço decimal 2 (216

ou 000000102)

1B4

0001

C. Op.

10110100

Operando

B416

Considere que a instrução ADD está

armazenada na MP no endereço decimal 3 (316

ou 000000112)

3B5

0011

C. Op.

10110101

Operando

B516

00

01

02

03

B4

B5

B6

FF

1B4

3B5

1A7

07D

Valores dos registradores:

◦ CI=02 (Endereço colocado pelo sistema operacional

para iniciar a execução do programa)

◦ RI=31716 (última instrução executada)

◦ ACC=20B16 (valor obtido da execução anterior)

◦ REM=B3 e RDM=7BC

CPU

ULA

MP

ACC

CI

RDM

20B

02

7BC

00

01

02

03

1B4

3B5

B3

RI 317

UC

REM

DI

B4

B5

B6

FF

Barramento de controle

1A7

07D

A partir desta configuração, inicia-se o ciclo

da instrução LDA

◦ Busca da Instrução

A UC aciona a transferência do conteúdo de CI para

REM (endereço de LDA)

REM

CI

O conteúdo de REM é colocado no barramento de

endereços e a UC ativa a linha READ do barramento de

controle

A memória recebe o endereço e coloca

o conteúdo da célula 02 no

barramento de dados (1B4)

O conteúdo do barramento de dados

chega no RDM

◦ RDM

Mem

O conteúdo do RDM é enviado para o

RI

◦ RI

RDM

Enquanto está acontecendo a operação de

leitura na memória, o CI está sendo

incrementado

Como, no nosso exemplo, qualquer

instrução ocupa uma célula de memória, o CI

será incrementado de uma unidade (CI = 03)

para apontar para a próxima instrução

◦ CI

CI + 1

Valores dos registradores após

o subciclo de busca da instrução 1B4

CPU

ULA

MP

ACC

CI

20B

02 03

RDM

7BC 1B4

00

01

02

03

1B4

3B5

B3 02

RI 317 1B4

UC

REM

DI

B4

B5

B6

FF

Barramento de controle

1A7

07D

Decodificação de Instrução

◦ A UC emite um sinal para que o RI transfira

para o decodificador de instruções os 4 bits

do C. Op.

Decodificador

0001

◦ O decodificador seleciona, através de uma

lógica nele existente, a linha de saída

correspondente para a UC que emitirá os

sinais adequados e em uma determinada

seqüência para a execução da instrução

◦ Como na instrução LDA não há operando

a ser buscado, inicia-se então a execução

da instrução

Execução de Instrução

◦ A execução da instrução LDA resume-se

em buscar na memória o conteúdo da

célula B4

◦ A UC comanda o RI para enviar os bits

referentes ao endereço de memória para o

REM

◦ A UC ativa a linha READ do barramento de

controle

◦ A memória recebe o endereço que chega

pelo barramento de endereço, decodifica e

envia o conteúdo da célula B4 para o

barramento de dados

◦ RDM recebe o conteúdo do barramento de

dados

RDM

1A7

ACC

RDM

◦ A UC emite um sinal para o RDM enviar o

seu conteúdo para o ACC

Valores dos registradores após

a execução da instrução 1B4

CPU

ULA

ACC

MP

CI

20B 1A7 02 03

RDM

1B4 1A7

00

01

02

03

1B4

3B5

02 B4

RI 317 1B4

UC

REM

DI

B4

B5

B6

FF

Barramento de controle

1A7

07D

Considerando que ADD é a instrução

seguinte a ser executada, o CI já

contém o seu endereço

Inicia-se a busca da próxima instrução

Busca da Instrução

◦ A UC aciona a transferência do conteúdo

de CI para REM (03)

REM

CI

◦ O conteúdo de REM é colocado no

barramento de endereços e a UC ativa a

linha READ do barramento de controle

◦ A memória recebe o endereço e coloca o

conteúdo da célula 03 no barramento de

dados (3B5)

◦ O conteúdo do barramento de dados chega

no RDM

RDM

Mem

◦ O conteúdo do RDM é enviado para o RI

RI

RDM

◦ Enquanto está acontecendo a operação de

leitura na memória, o CI está sendo

incrementado, passando a valer 4

CI

CI + 1

Valores dos registradores após

o subciclo de busca da instrução 3B5

CPU

ULA

ACC

20B 1A7

MP

CI

03 04

RDM

1A7 3B5

00

01

02

03

1B4

3B5

B4 03

RI 1B4 3B5

UC

REM

DI

B4

B5

B6

FF

Barramento de controle

1A7

07D

Decodificação de Instrução

◦ A UC emite um sinal para que o RI transfira para o

decodificador de instruções os 4 bits do C. Op.

Decodificador

0011

◦ O decodificador seleciona a linha de saída

correspondente para a UC que emitirá os sinais

adequados para a busca do operando

Busca de Operando

◦ O endereço do operando a ser buscado na

MP está do RI, no campo operando (B5)

◦ UC emite sinais para que o REM receba o

operando

REM

B5

◦ REM coloca o seu conteúdo no barramento

de endereços

◦ A UC ativa a linha READ no barramento de

controle

◦ A memória recebe o endereço e coloca o

conteúdo da célula B5 no barramento de

dados (07D)

◦ O conteúdo do barramento de dados

chega no RDM

RDM

Mem

Valores dos registradores após

a busca do operando 07D

CPU

ACC

ULA

20B 1A7

MP

CI

03 04

RDM

3B5 07D

00

01

02

03

1B4

3B5

03 B5

RI 1B4 3B5

UC

REM

DI

B4

B5

B6

FF

Barramento de controle

1A7

07D

Execução de Instrução

◦ A ULA recebe o primeiro operando da

soma que está no acumulador

ULA

1A7

ACC

RDM

ULA

ACC

◦ O conteúdo do RDM (segunda parcela da

soma) é colocado no ACC

◦ A ULA recebe a segunda parcela da soma

CPU

1A7

07D

MP

ACC

CI

1A7 07D

03 04

RDM

3B5 07D

00

01

02

03

1B4

3B5

03 B5

RI 1B4 3B5

UC

REM

DI

B4

B5

B6

FF

Barramento de controle

1A7

07D

◦ A UC comanda a ULA para realizar a adição dos dois

valores

1A7 + 07D = 224

◦ O resultado da adição é colocado no ACC

ACC

224

Valores dos registradores após

a execução da instrução 3B5

CPU

ACC

ULA

MP

CI

07D 224 03 04

RDM

3B5 07D

00

01

02

03

1B4

3B5

03 B5

RI 1B4 3B5

UC

REM

DI

B4

B5

B6

FF

Barramento de controle

1A7

07D