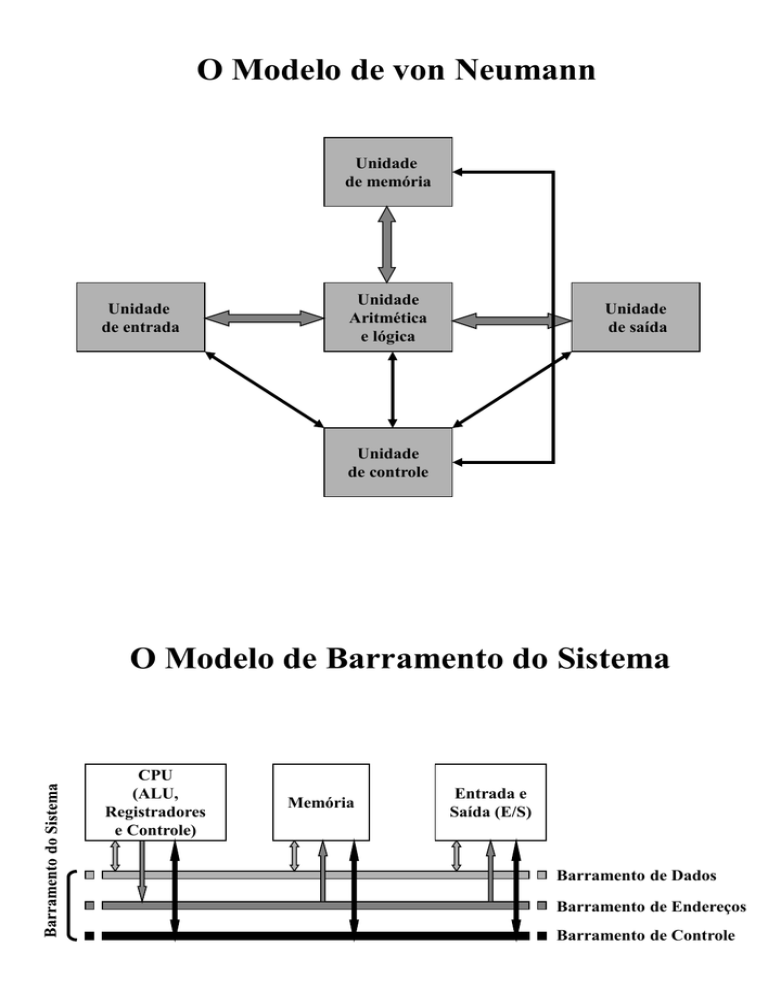

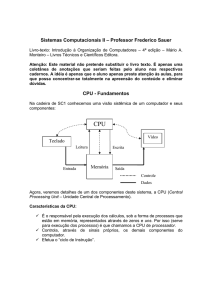

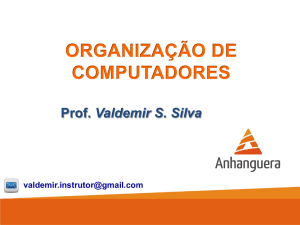

O Modelo de von Neumann

Unidade

de memória

Unidade

de entrada

Unidade

Aritmética

e lógica

Unidade

de saída

Unidade

de controle

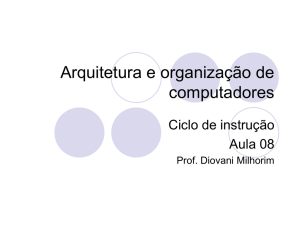

O Modelo de Barramento do Sistema

CPU

(ALU,

Registradores

e Controle)

Memória

Entrada e

Saída (E/S)

Barramento de Dados

Barramento de Endereços

Barramento de Controle

Structure of ENIAC

Card

reader

Multiplier

Divider

And

Square

rooler

Function

Tables

A1 A2

Printer

and card

punch

A30

Accumulators

Program

Lines

Master

programmer

unit

Architecture of a first-generation computer

Secondary

Memory

units

Central processing

unit

Arithmetic –

Logic

unit

Tele –

typewriter

Program

Control

Unit

Card

reader

Main

memory

Print

and card

punch

Equipamento

de entrada e

saída

Estrutura de uma CPU simples

AC = 0

C0(ADD)

C1(AND)

C2(COMP)

CIRCUITOS DE

ARITMÉTICA

E LÓGICA

C3(READ)

C12

AC

C4(WRITE)

Memória

C5

principal

M

C6

R

D

M

C7

R

E

M

C8

C11

C9

CI

RI

C10

AC = 0

UNIDADE

CONTROLE

C0

C1

C12

Sinais de controle da CPU simples

Sinal de controle

Operação Controlada

C0

AC AC + RDM

C1

AC AC ^ RDM

C2

AC ~AC (complemento)

C3

RDM M[REM] (READ M)

C4

M[REM] RDM (WRITE M)

C5

RDM AC

C6

AC RDM

C7

REM RDM (ENDEREÇO)

C8

CI RDM (ENDEREÇO)

C9

CI CI + 1

C10

REM CI

C11

RI RDM (OP.COD.)

C12

RIGHT-SHIFT AC

Structure of the extended CPU

V

AC = 0

AC < 0

C26

C27

Flags

C28

COUNT = (n-2)

C0

C1

C2

C23

ArithmeticLogic

circuits

MQ(n-1)

C14

C3

C12

C13

C16

C22

C25

COUNT

AC

C17

C20

C21

MQ

C4

C15

C6 C19

C5

Main

Memory

M

C18

DR

C11

C7

C8

IR

PC

A

R

C9

C24

C10

AC=0

AC<0

MQ(n-1)

COUNT = (n-2)

V

Microprogrammed

Control

unit

.

.

.

C0

C1

C28

Control signals of the extended CPU

Control Signal

C0

C1

C2

C3

C4

C5

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

C16

C17

C18

C19

C20

C21

C22

C23

C24

C25

C26

C27

C28

Operation Controlled

AC AC + DR

AC AC ^ DR

AC AC

DR M(AR) (READ M)

M(AR) DR (WRITE M)

DR AC

AC DR

AR DR (ADR)

PC DR (ADR)

PC PC + 1

AR PC

IR DR (OP)

RIGHT-SHIFT AC

LEFT-SHIFT AC

RIGTH-SHIFT (AC, MQ)

LEFT-SHIFT (AC, MQ)

AC 0

AC(0) AC(0) v V

MQ DR

DR MQ

MQ(n-1) 1

MQ(n-1) 0

COUNT COUNT + 1

AC AC – DR

PC IR

COUNT 0

V0

V1

FLAGS 0