EDGAR MAURICIO CAMACHO GALEANO

REFERÊNCIA DE CORRENTE CMOS

PARA APLICAÇÕES DE

ULTRABAIXO CONSUMO DE POTÊNCIA

FLORIANÓPOLIS

2004

UNIVERSIDADE FEDERAL DE SANTA CATARINA

PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

REFERÊNCIA DE CORRENTE CMOS

PARA APLICAÇÕES DE

ULTRABAIXO CONSUMO DE POTÊNCIA

TESE SUBMETIDA À

UNIVERSIDADE FEDERAL DE SANTA CATARINA

COMO PARTE DOS REQUISITOS PARA A

OBTENÇÃO DO GRAU DE

MESTRE EM ENGENHARIA ELÉTRICA

EDGAR MAURICIO CAMACHO GALEANO

FLORIANÓPOLIS, MARÇO DE 2004.

REFERÊNCIA DE CORRENTE CMOS

PARA APLICAÇÕES DE ULTRABAIXO CONSUMO DE POTÊNCIA

CANDIDATO: EDGAR MAURICIO CAMACHO GALEANO

“Esta dissertação foi julgada adequada para obtenção do título de Mestre em Engenharia Elétrica,

Área de Concentração em Circuitos e Sistemas Integrados, e aprovada em sua forma final pelo

programa de Pós Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina”

Prof. MÁRCIO CHEREM SCHNEIDER, Dr.

ORIENTADOR

Prof. Jefferson Luiz Brum Marques, Dr.

COORDENADOR DO CURSO DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

BANCA EXAMINADORA:

Prof. MÁRCIO CHEREM SCHNEIDER, Dr.

Presidente

Prof. CARLOS GALUP MONTORO, Dr.

Prof LUIS CLÉBER C. MARQUES,Dr.

FELIPE CLAYTON , Eng. BSTC Motorola.

A mis padres y Jenny Patricia,

Por su infinito amor y sacrificios.

AGRADECIMENTOS

À CAPES e ao CNPq pelo suporte financeiro para a realização deste curso.

Aos Professores, Márcio Cherem Schneider e Carlos Galup Montoro. Por me

orientar e participar neste trabalho de grande importância na minha formação.

Ao Engenheiro Alfredo Olmos por ser referência de superação.

Aos meus amigos e colegas de Florianópolis pelos bons momentos que

compartilhamos nesta encantadora ilha.

i

Sumário

Sumário .......................................................................................................................

i

Lista de Símbolos ........................................................................................................

ii

Lista de abreviações ...................................................................................................

iii

Lista de Figuras ..........................................................................................................

iv

Lista de Tabelas ..........................................................................................................

vi

Resumo ........................................................................................................................

vii

Abstract .......................................................................................................................

viii

1 Introdução ...............................................................................................................

1

1.1

Referências de corrente e tensão: Enfoque para baixo consumo ....................

2

1.2

Referências de corrente: Revisão da literatura ...............................................

3

2 Referência de corrente autônoma (SBCS) de ultrabaixo consumo de potência

8

2.1

Introdução .......................................................................................................

9

2.2

Modelo ACM : Advanced Compact Model ....................................................

10

2.3

Equações de projeto para o SCM e o VFCM .................................................

12

2.4

Circuito SBCS proposto para baixa tensão de operação ................................

14

2.5

Análise de sensibilidade .................................................................................

17

2.51 Sensibilidade a Vref ..............................................................................

17

2.52 Sensibilidade a VDD ...............................................................................

19

3 Projeto da referência de corrente e resultados ...................................................

22

3.1

Projeto para ultrabaixo consumo de potência .................................................

22

3.2

Resultados experimentais ...............................................................................

27

4 Conclusões e futuros trabalhos .............................................................................

34

Apêndice A - Layout dos circuitos de teste integrados nas tecnologias AMIS

35

1.5µm e TSMC 0.35µm.

Apêndice B - Artigo publicado: ISCAS2004 ............................................................

38

Referências Bibliográficas .........................................................................................

42

ii

Lista de Símbolos

C’ox

– capacitância do óxido por unidade de área [F/m]

ID

– corrente de dreno [A]

IF

– corrente direta [A]

if

– corrente direta normalizada ou nível de inversão

IR

– corrente reversa [A]

Iref

– corrente de referência [A]

IS

– corrente de normalização [A]

ISQ

– corrente de normalização para um transistor quadrado [A]

k

– constante de Boltzmann [J/K]

L

– comprimento do canal [m]

n

– fator de rampa

VA

– tensão de Early [V]

VDS

– tensão dreno-fonte [V]

VDSsat

– tensão dreno-fonte de saturação [V]

VDD

– tensão de alimentação [V]

VDDmin

– tensão de alimentação mínima [V]

Vref

– tensão de referência [A]

VE

– tensão de Early por unidade de comprimento do canal [V/m]

VGS

– tensão porta-fonte [V]

VT

– tensão de limiar ou de threshold [V]

W

– largura do canal [µm]

µ

– mobilidade dos portadores [m2/Vs]

φt

– tensão termodinâmica [V]

∆,δ

– Variação (delta)

iii

Lista de abreviações

ACM

– Advanced Compact Model

AMIS

– AMI Semiconductor

CMOS

– Complementary Metal Oxide Semiconductor

DC

– Direct Current

MOSFET

– Metal Oxide Semiconductor field effect transistor

M.I

– Moderade Inversion (inversão moderada)

NMOS

– Transistor MOS canal N

PMOS

– Transistor MOS canal P

PTAT

– Proportional To Absolute Temperature

RF

– Rádio Frequência

SBCS

– Self Biased Current Source

SBS

– Self Biased Structure

SCM

– Self Cascode MOSFET

S.I

– Strong Inversion (inversão forte)

TSMC

– Taiwan Semiconductor Manufacturing Company

VFCM

– Voltage-Following Current Mirror

V-I

– Tensão - Corrente

VLSI

– Very Large Scale Integration

W.I

– Weak Inversion (inversão fraca)

iv

Lista de Figuras

Figura 1.1

Referência de corrente CMOS clássica [03] .........................................

4

Figura 1.2

Referência de corrente CMOS [04-05] .................................................

5

Figura 1.3

Referência de corrente CMOS [06] .......................................................

6

Figura 1.4

Referência de corrente CMOS [07] .......................................................

7

Figura 2.1

Transistor MOS canal N (a) Corte lateral; (b) Layout (vista superior)

10

Figura 2.2

MOSFET auto cascode (SCM) ..............................................................

12

Figura 2.3

Estrutura autopolarizada (Voltage-Following Current Mirror -VFCM) ....

13

Figura 2.4

Referência de corrente autônoma (SBCS) . ...........................................

14

Figura 2.5

Transistor trapezoidal (M2 é formado por M transistores M1 em

paralelo) .................................................................................................

Figura 2.6

Sensibilidade porcentual de Iref por mV de Vx em relação a x (2.17).

(φt=26mV) .......................................................................................................

Figura 2.7

16

18

Sensibilidade porcentual/V de Iref referente a x, usando como

parâmetro

M. Utilizando como especificações e parâmetros

tecnológicos if1/if2=3.4, Lu = 6µm e VE =2V/µm...................................

21

Figura 3.1

Referência de corrente autônoma (SBCS) .............................................

22

Figura 3.2

Simulação de Vref versus VDD (AMIS 1.5) ......................................

25

Figura 3.3

Simulação de Vref versus VDD (TSMC 0.35) .....................................

25

Figura 3.4

Simulação de Iref versus VDD (AMIS 1.5), (pós-layout) ....................

26

Figura 3.5

Simulação de Iref versus VDD (TSMC 0.35), (pós-layout) ..................

26

Figura 3.6

Vref versus VDD (Topologia simétrica AMIS 1.5) ............................

28

Figura 3.7

Vref versus VDD (Topologia simétrica TSMC 0.35) ..........................

28

Figura 3.8

Iref versus VDD (Topologia simétrica AMIS 1.5) ...............................

29

Figura 3.9

Iref versus VDD (Topologia simétrica TSMC 0.35) ............................

29

v

Figura 3.10

Histograma da Vref com VDD=1.15V (TSMC 0.35) ...........................

30

Figura 3.11

Histograma de Iref com VDD=1.15V (TSMC 0.35) .............................

30

Figura 3.12

Microfotografia do chip fabricado na tecnologia AMIS 1.5µm.

(2200µm x 2200µm) ......................................................................................

31

Figura 3.13

Zoom dos circuitos testados (AMIS 1.5µm) ......................................

31

Figura 3.14

Microfotografia do chip fabricado na tecnologia TSMC 0.35µm.

(1280µm x 1280µm) .......................................................................................

32

Figura 3.15

Zoom do circuito testado. (TSMC 0.35µm) ..........................................

32

Figura A.1

Layout do chip fabricado na tecnologia CMOS AMIS 1.5µm .............

35

Figura A.2

Layout do chip fabricado na tecnologia CMOS TSMC 0.35µm ...........

35

Figura A.3

SBCS(1) simétrica na tecnologia CMOS AMIS 1.5µm ........................

36

Figura A.4

SBCS(2) simétrica na tecnologia CMOS AMIS 1.5µm ........................

36

Figura A.5

SBCS(1) simétrica na tecnologia CMOS TSMC 0.35µm .....................

37

Figura A.6

SBCS(1) simétrica projetada na tecnologia CMOS TSMC 0.35µm .....

37

vi

Lista de Tabelas

Tabela 3.1

Resumo de resultados de simulação ................... ..................................

Tabela 3.2

Dimensionamento dos transistores da topologia simétrica (AMIS 1.5).

(M=5) .....................................................................................................

Tabela 3.3

Tabela 3.4

24

24

Dimensionamento dos transistores da topologia simétrica (TSMC

0.35).(M=8) ...........................................................................................

24

Resumo de resultados experimentais ....................................................

27

vii

Resumo da Dissertação apresentada à UFSC como parte dos requisitos necessários

para a obtenção do grau de Mestre em Engenharia Elétrica.

REFERÊNCIA DE CORRENTE CMOS PARA APLICAÇÕES

DE ULTRABAIXO CONSUMO DE POTÊNCIA

Edgar Mauricio Camacho Galeano

Março/2004

Orientador: Márcio Cherem Schneider

Área de Concentração: Circuitos e Sistemas Integrados

Palavras-chave: Referência de corrente, referência de tensão PTAT, eficiência em

potência, circuitos integrados analógicos MOS, metodologia de projeto, análise de

sensibilidade, ultrabaixo consumo, baixa tensão de operação.

Número de Páginas: 43

Este trabalho apresenta uma referência de corrente CMOS eficiente para aplicações

de ultrabaixo consumo de potência. Uma metodologia de projeto é proposta para otimizar

sua operação com muito baixa tensão de alimentação. Esta metodologia é baseada em um

conjunto de equações derivadas de um modelo para o MOSFET válido em todas as regiões

de operação. Uma análise de sensibilidade orienta o projetista a fim de reduzir a

sensibilidade da corrente tanto a parâmetros de projeto como também a variações na fonte

de alimentação. O projeto da referência de corrente é validado através de simulação e

fabricação de circuitos integrados de teste nas tecnologias CMOS AMIS 1.5µm e TSMC

0.35µm. Os circuitos de referência de corrente que projetamos são capazes de operar com

tensões de alimentação de até 1,1V e com consumo da ordem de 2nW. Os resultados

experimentais mostram que a referência de corrente projetada neste trabalho supera a

performance de atuais referências de corrente reportadas na literatura.

viii

Abstract of Dissertation presented to UFSC as a partial fulfillment of the

requirements for the degree of Master in Electrical Engineering.

A CMOS CURRENT REFERENCE FOR ULTRA LOW

POWER APLICATIONS

Edgar Mauricio Camacho Galeano

March/2004

Advisor: Márcio Cherem Schneider.

Area of Concentration: Integrated Circuits and System

Keywords: Current reference, PTAT voltage reference, power efficiency, MOS analog

integrated circuits, design methodology, sensitivity analysis, ultra low-power, very lowvoltage.

Number of Pages: 43

This work presents an efficient CMOS current reference for ultra-low-power

consumption. A design methodology is proposed to allow the current reference to operate

at very low supply voltage. The design methodology is based on a set of equations derived

from a MOSFET model valid for all operating regions. A sensitivity analysis guides the

designer in order to reduce the current sensitivity to both design parameters and supply

voltage. The design of the current reference is validated by means of simulation and

fabrication of integrated circuits in both the AMIS 1.5µm and TSMC 0.35µm CMOS

technologies. The current reference circuits we have designed are capable of operating at

supply voltages down to 1.1V with consumption of the order of 2 nW. The experimental

results show that the CMOS current reference design in this work far exceeds the

performance of current references reported in the technical literature so far.

1

Capítulo 1

INTRODUÇÃO

Atualmente a tecnologia é parte essencial na vida cotidiana da humanidade. As

razões disto são claras; esta oferece um conjunto incontável de vantagens em lazer,

conforto, educação, saúde, segurança e inclusive no avanço da própria tecnologia. Por isto,

no dia a dia são muitos os dispositivos eletrônicos que usamos, até em nossas atividades

mais simples. Exemplos destes são: telefones fixos e móveis, computadores, agendas

pessoais, reprodutores de música, vídeo, TV, relógios de pulso, alarmes, caixas eletrônicas

e, também, dispositivos implantados no corpo humano. Estes últimos são encontrados

realizando funções de nosso organismo, de forma parcial ou total, para que o indivíduo

beneficiado possa seguir o seu curso de vida normal.

Fatores como conforto, funcionalidade e custo são essenciais para o avanço de

novos dispositivos eletrônicos. Portanto, a preferência do mercado por dispositivos

portáteis, leves, de fácil uso com múltiplas funções a preço razoável está aumentando mais

a cada dia.

Todos estes dispositivos eletrônicos têm um ou vários elementos em comum,

denominado circuito integrado ou chip. Um circuito integrado é um dispositivo que pode

realizar uma ou várias funções específicas, sintetizadas no nível de transistores em uma

pastilha de silício. Sem dúvida, o chip é o resultado do trabalho de projetistas de circuitos

integrados, que sente a influência de suprir as demandas do mercado gerando sistemas

eletrônicos mais integrados.

Para aumentar a viabilidade mercantil, os dispositivos eletrônicos portáteis devem

oferecer características como alimentação por bateria, ou por fontes de energia alternativas

como baterias solares e radiação RF. Estas características são atrativas para obter maior

portabilidade e menor peso, mas implicará em restrições de baixa potência e tensão. As

limitações anteriores em sistemas mais complexos interagindo com o mundo físico

levaram projetistas a optar por tecnologias que permitam integrar circuitos analógicos de

2

baixa tensão compatíveis com tecnologias de muita alta escala de integração VLSI, (Very

Large Scale Integration). Neste tipo de integração, a tecnologia CMOS (Complementary

Metal Oxide Semiconductor) nos últimos anos tem-se mostrado a mais adequada

realizando eficientes sistemas de processamento, tendo vantagem de circuitos analógicos e

digitais de baixo consumo na mesma pastilha [01].

Os circuitos digitais são favorecidos com o escalamento da tecnologia CMOS,

podendo alcançar maiores freqüências com menor tensão de operação. Por sua vez, os

circuitos analógicos começam a ser cada vez mais desafiantes para projetistas, já que a

performance do MOSFET é degradada pelo aumento de efeitos de segunda ordem tal como

menor tensão de Early, aumento das correntes de fuga (pela diminuição da tensão de

limiar – VT) e menor imunidade ao ruído, pela diminuição da tensão de alimentação, VDD.

Esta tendência leva à redução progressiva da relação VDD/VT, que força a diminuir o

número de transistores empilhados entre as linhas de alimentação no projeto de circuitos

analógicos CMOS com tecnologias submicrométricas.

Atualmente, técnicas de circuitos analógicos CMOS adequados para baixa tensão

são reduzidas e, com restrição adicional para baixo consumo, são mais escassos ainda.

Assim, novas técnicas de circuitos analógicos e de polarização são exigidas para operar

com as restrições impostas pelas novas tendências da tecnologia CMOS e do mercado. O

desafio neste caso é produzir circuitos CMOS tanto analógicos quanto digitais, de muito

baixa potência e tensão ou aproveitar circuitos já existentes, otimizando-os para baixa

potência e baixa tensão com apropriadas metodologias de projeto.

1.1. Referências de corrente e tensão: Enfoque para baixo consumo

Para polarizar adequadamente transistores e alcançar um ponto de operação estável

é necessário prover diretamente tensões e correntes que são geralmente derivadas de algum

tipo de referência externa. Tais referências são grandezas que exibem pouca sensibilidade a

variações na tensão de alimentação e parâmetros do processo, como também uma

dependência bem definida em relação à temperatura. Estas grandezas são dependentes de

parâmetros com dimensões de tensão (por exemplo, φt=kT/q [03-07]) ou corrente (I=V/R

[03-04,07], µC’oxφt2 [04-08]). Convencionalmente, as referências são externas. Estas são

ligadas ao chip por meio de um ou vários pinos e este excesso de pinos aumenta tanto o

tamanho do encapsulamento como o seu preço [14, 18], sendo um impedimento quando o

3

menor custo e maior integração são fatores indispensáveis. Em conseqüência, referências

autônomas são requeridas.

As referências de corrente e tensão são usadas em circuitos analógicos

extensivamente, para definir uma polarização DC (Direct Current) e também como

grandeza de comparação com variáveis da mesma natureza.

Polarizar circuitos analógicos CMOS com corrente é a forma mais adequada para

alcançar menor tensão de operação com baixo consumo. Desta forma é possível escalar a

corrente para alcançar uma determinada performance. Em modo corrente, o mínimo

escalamento é restringido basicamente pelas correntes de fuga na região sub-limiar e pelas

correntes de fuga das junções pn entre o substrato (ou bulk) e as regiões de difusão, as

quais variam tipicamente desde femto-Amperes até alguns pico-Amperes [02].

Uma técnica atual, baseada no conceito de nível de inversão tem sido usada para

obter circuitos analógicos CMOS de baixa tensão [05,10] e muito baixo consumo [02].

Este tipo de técnica emprega a corrente como principal variável de projeto. Portanto,

instrumentos como um modelo compacto para MOSFETs e referências de corrente “onchip” (dentro do chip) são indispensáveis para sua concretização.

Um modelo compacto para MOSFETs é ACM [09]. Este modelo permite realizar

projeto e análise de circuitos analógicos CMOS, com uma única equação para todas as

regiões de operação, ou seja, desde inversão fraca (W.I) até inversão forte (S.I). Uma breve

discussão deste modelo será feita no capítulo 2.

1.2. Referências de corrente: Revisão da literatura

Referências de corrente com baixa sensibilidade a variações na fonte de

alimentação em geral são derivadas de uma tensão de referência bem definida e um

adicional conversor tensão-corrente [03-08,17,18]. Quanto à implementação CMOS não

são muitas as topologias que usam unicamente MOSFETs [03-08]. Além disso, o número

se reduz mais ainda quando requisitos de baixa tensão [03,07] e muito baixo consumo de

potência são parte da especificação do projeto [06].

Uma referência de corrente clássica foi inicialmente proposta em [03]. Este circuito

é muito simples e consta de uma estrutura autopolarizada de quatro transistores e um

resistor. Seu esquema é mostrado na Fig. 1.1.

4

Iref

Fig. 1.1 Referência de corrente CMOS clássica [03]

Os transistores PMOS formam um espelho de corrente que força correntes iguais

em um par NMOS porta comum. Um fator de proporcionalidade K é introduzido entre as

razões de aspecto dos transistores do par acoplado NMOS e, assim, gera uma tensão de

referência PTAT (Proportional To Absolute Temperature) que é aplicada em um resistor

para produzir uma corrente. Considerando M1-M2 em inversão fraca a corrente de

referência é definida por:

I ref =

φt ln(K )

R

(1.0)

aqui, φ t é a tensão termodinâmica, cujo valor é aproximadamente 26mV para temperatura

ambiente ( T= 300οK).

Esta topologia oferece uma eficiência de 33% para produzir uma corrente de saída

igual à corrente de referência, ou seja, o consumo de corrente intrínseco da célula básica é

duas vezes a corrente de saída. Este circuito é adequado para baixa tensão de operação se

uma adequada metodologia de projeto é usada. Porém, este esquema não é adequado para

gerar pequenas correntes necessárias para polarizar circuitos com baixo consumo de

potência. Por exemplo, supondo K=10, é definida uma tensão de referência de 60mV. Para

gerar uma corrente de 600pA (6nA) um resistor de 100MΩ (10MΩ) é requerido. A

implementação deste resistor em uma tecnologia CMOS padrão vai preencher grande área

de silício. Além disso, o valor absoluto de resistores em processos CMOS tem tolerâncias

da ordem de 10-30%.

Na literatura, até agora são poucos os circuitos de referência de corrente CMOS

autônomos reportados que sejam baseados em propriedades físicas intrínsecas [05-08], sem

5

depender de nenhuma tensão de limiar. Estes circuitos empregam unicamente MOSFETs e

apresentam a mesma dependência à temperatura, definida por T2-m, onde m é o coeficiente

de temperatura da mobilidade. Este parâmetro varia com a tecnologia, entre 1,5 a 2,0. No

caso de m ≅ 2 , razoável independência com a temperatura pode ser alcançada.

A primeira deste tipo de referências de corrente é introduzida por [04], e

reapresentada em [05]. O principio de funcionamento deste circuito é comparar as tensões

dos nós intermediários vx e vy de MOSFETs polarizados na inversão fraca e inversão forte,

respectivamente. E assim, produzir uma corrente proporcional à corrente específica, Is

[05]. Este circuito foi inspirado na referência de corrente mencionada anteriormente [03], e

é uma estrutura com baixa eficiência em potência. O motivo desta reduzida eficiência é

atribuído ao uso de grandes relações de corrente, que são implementadas com um espelho

de corrente PMOS convencional.

Fig. 1.2 Referência de corrente CMOS [04] - [05]

No exemplo da Fig. 1.2 [04], é gerada uma corrente de saída igual a Iref, e a célula

básica consume uma corrente de 111 vezes Iref, equivalente a uma eficiência de 0,9%.

A segunda referência de corrente autônoma é apresentada em [06], a qual foi

também inspirada na estrutura clássica de [03]. Como foi mencionado antes, o resistor

pode ser uma desvantagem em muitas aplicações. Portanto, os autores de [06] usam um

MOSFET operando na região de triodo em inversão forte para substituí-lo, como ilustrado

na Fig. 1.3.

6

Fig. 1.3 Referência de corrente CMOS [06]

Embora seja uma estrutura simples, esta foi indicada em [07] como não adequada

para aplicações com muita baixa tensão de operação. Os motivos não são mencionados,

mas nos resultados experimentais uma regulação da corrente de 20%/V e dispersão desde o

valor nominal até 90% podem ser razões suficientes. Também, o número dominante de

transistores trabalhando no regime de inversão forte reduz as possibilidades de este circuito

ser um candidato para baixa tensão de operação.

No circuito da Fig. 1.3, os autores realizam uma análise usando um modelo não

compacto e, portanto, pontos de operação indesejáveis (Iref=0) não são restringidos pelo

equacionamento.

Para exemplificar na Fig. 1.3 fazendo N=1 e K2=1, o equacionamento em [06]

prevê um valor de corrente finito diferente de zero. Porém, na prática sob estas condições

não existe tal ponto de operação. A razão disto é que, neste caso, o transistor Mb tenderia a

saturar para alcançar a corrente de referência. Mas como sua tensão de saída é restrita a

Vref, então, a corrente (e VGN) começa a ser reduzida até Ma-b entrar na região de inversão

fraca, onde esta se reduz a zero rapidamente (exponencialmente). Equacionando este

circuito com um modelo compacto para MOSFETs (por exemplo, ACM), restringe N.K2≥4

e, assim, Mb poderá trabalhar na região de triodo em inversão forte.

Uma terceira referência de corrente autônoma é introduzida em [07]. Esta é uma

estrutura um pouco mais complexa que as mencionadas previamente. Este circuito usa um

MOSFET auto cascode (SCM - self-cascode MOSFET) polarizado em inversão forte com

uma referência de tensão PTAT gerada por meio de uma relação de corrente, como

ilustrado na Fig. 1.4. Também emprega uma realimentação local para balancear a estrutura

7

e melhorar a rejeição à fonte de alimentação. Embora seja apropriada para baixa tensão de

operação, sua eficiência de potência não é muito alta, devido ao uso de fatores de corrente

relativamente grandes e operação de alguns transistores na inversão forte.

Fig. 1.4 Referência de corrente CMOS [07]

Por exemplo, no projeto proposto em [07], a eficiência da célula básica para

produzir uma corrente de saída igual à menor corrente de referência é de 5%. Além disso,

em determinados casos um capacitor de compensação deve ser usado para garantir

estabilidade, gerando um aumento adicional na área de silício.

Por último, em [08,13] são apresentados circuitos que não são adequados para baixa

tensão de operação. Nestes circuitos é dominante a polarização de MOSFETs na região de

inversão forte e são empilhadas até três tensões porta-fonte (VGS). Como um dos objetivos

deste trabalho é o de gerar correntes com tensão de alimentação ligeiramente menor que

duas tensões de limiar CMOS ou um pouco maior que uma tensão de limiar mais uma

tensão VDssat, os trabalhos de [08] e [13] não são candidatos à implementação da referência

de corrente.

Existem outras alternativas para gerar correntes em tecnologia CMOS. Uma forma

tradicional é usar referências de tensão bandgap [15-16]. Porém, o consumo de potência é

alto se for comparado com todas as topologias anteriores. Referências de bandgap em

tecnologia CMOS são baseadas em transistores bipolares parasitas, que possuem baixo

ganho de corrente e, portanto, não é possível escalar fortemente a corrente para polarizálos como no caso de MOSFETs. Algumas destas estruturas usam amplificadores

operacionais para aplicar a tensão de bandgap em um resistor [17] ou em um MOSFET

operando na região de triodo [18], aumentando o consumo de potência e área do circuito.

8

Portanto, o uso de amplificadores operacionais pode não ser uma boa opção para circuitos

de polarização de ultrabaixo consumo.

Neste trabalho é proposta uma referência de corrente autônoma, baseada em

propriedades intrínsecas da tecnologia CMOS, para polarizar MOSFETs em um nível de

inversão constante. E tem como objetivo gerar correntes de forma simples na faixa de

centenas de pA, com consumo de potência bem menor que no estado da arte da

microeletrônica.

Este trabalho foi dividido em quatro capítulos. No capítulo 2 é apresentada a

topologia básica da referência de corrente autônoma, com suas correspondentes

formulações analíticas para projeto e análise de sensibilidade.

No capitulo 3, são apresentados os projetos desenvolvidos em duas tecnologias

diferentes, AMIS 1.5µm e TSMC 0.35µm. Resultados de simulação e experimentais são

apresentados para validar o funcionamento do circuito gerador de corrente.

Finalmente, no capitulo 4, as conclusões e sugestões para futuros trabalhos serão

apresentadas.

9

Capítulo 2

REFERÊNCIA DE CORRENTE AUTÔNOMA (SBCS)

DE ULTRABAIXO CONSUMO DE POTÊNCIA

2.1. Introdução

Conforme explicado no capítulo anterior, muitos CIs atuais requerem referências de

corrente autônomas (SBCS – Self Biased Current Source) com especificações para baixa

tensão e (ultra) baixo consumo de potência. Os circuitos disponíveis na literatura não

oferecem um bom compromisso entre eficiência em potência e performance para gerar

correntes autônomas de ultrabaixo valor. Neste capítulo, duas referências de corrente

CMOS eficientes em consumo de potência são introduzidas, sendo considerada sua

aplicabilidade em circuitos de ultrabaixo consumo. Na seção 2.2, inicialmente será

apresentado um modelo para MOSFETs, que será usado no equacionamento da referência

de corrente e, assim, alcançar um bom compromisso entre consumo de potência, área e

baixa tensão de operação. A referência de corrente proposta é baseada na estrutura

autopolarizada (Voltage-Following Current Mirror -VFCM) de [3,20], e também um tipo de

estrutura empilhada de dois transistores, denominada MOSFET auto cascode (SCM – Self

Cascode MOSFET), o qual é conectado como diodo com uma derivação central. Na seção

2.3, são formuladas equações para descrever o comportamento V-I destas duas estruturas.

A seção 2.4 descreve o funcionamento e metodologia de projeto da referência de corrente.

Finalmente, na seção 2.5, uma análise de sensibilidades a vários parâmetros de projeto é

incluída.

10

2.2. Modelo ACM: Advanced Compact Mosfet [9]

O dispositivo fundamental da tecnologia CMOS é o MOSFET, o dispositivo de

quatro terminais apresentado na Fig. 2.1. O MOSFET canal-n ou NMOS (canal-p ou

PMOS) é formado por um substrato tipo p (para PMOS, substrato tipo n ou poço n). As

duas regiões altamente dopadas (n+ para NMOS e p+ para PMOS) são chamadas fonte

(source) e dreno (drain), e entre estas é formado um canal. A parte superior do canal de

silício é coberta por um isolante fino (dióxido de silício) que realiza contato físico com um

eletrodo de baixa resistividade (Al, polisilício n+), denominado porta (gate).

(a) Corte lateral

(b) Layout (vista superior)

Fig.2.1. Transistor MOS canal N

Para realizar de forma eficiente o projeto de circuitos CMOS é necessário um

modelo para MOSFETs, que relacione suas propriedades físicas e elétricas com expressões

únicas, simples e contínuas, válidas em todas as regiões de operação. Um modelo para

MOSFETs com esta descrição é ACM [9], o qual preserva as propriedades fundamentais,

tais como simetria entre dreno e fonte e a conservação da carga.

ACM é um modelo baseado em corrente que usa o conceito de nível de inversão,

para determinar a região de operação do MOSFET. Neste modelo [9] a corrente pode ser

dividida em uma corrente direta (IF – forward current) e uma corrente reversa (IR - reverse

current).

(

I D = I F − I R = I S i f − ir

)

(2.1)

11

IF(IR) depende das tensões de porta (VG) e fonte, VS (dreno, VD), referenciadas ao

terminal de substrato como indicado na Fig. 2.1. Para a equação (2.1) na saturação IF>>IR,

a corrente de dreno pode ser expressa apenas em termos da corrente direta. Desta forma a

seguinte aproximação será adotada na saturação:

ID ≅ IF

(2.2)

A corrente de dreno pode ainda ser escrita em forma normalizada, usando o

conceito de corrente específica, IS:

ID ≅ IS ⋅ i f

(2.3)

onde if é a corrente normalizada direta, também conhecida como grau ou nível de inversão.

A corrente de normalização é dada por:

W

I S = I SQ

L

(2.4)

φ t2

2

(2.5)

'

I SQ = µC ox

n

sendo ISQ a corrente de normalização para um transistor quadrado (IS para W=L). A

corrente IS constitui o parâmetro fundamental do modelo ACM, contendo as informações

básicas sobre o dispositivo, tais como tecnologia, geometria e temperatura [09]. Aqui, µ, n,

C’ox, φt, e W/L=S são a mobilidade, fator de rampa, capacitância/área da porta, tensão

termodinâmica e a relação de aspecto, respectivamente. Por exemplo, ISQ’s em tecnologia

de 0.35µm para os transistores P e N são da ordem de 30nA e 70 nA, e estes valores

tendem a aumentar com o escalamento da tecnologia CMOS.

A relação entre corrente e tensão é dada [09] por:

VP − VS ( D)

φt

(

)

= 1 + i f ( r ) − 2 + ln 1 + i f ( r ) − 1

VP ≅

VG − VT 0

n

(2.6.a)

(2.6.b)

onde VP , é a tensão de pinch-off e VT0 é a tensão de limiar para VSB=0. Mais detalhes sobre

(2.1)-(2.6) podem ser encontrados em [09].

12

2.3. Equações de projeto para o SCM e o VFCM

O elemento principal da SBCS é um SCM, o qual é mostrado na Fig. 2.2. A

característica V-I do SCM é bastante apropriada para construir circuitos analógicos de

baixa tensão, tal como referências de corrente e tensão PTAT sub-100mV [03-07].

As equações de projeto (2.7)-(2.9) que descrevem a característica V-I do SCM

foram deduzidas usando (2.1)-(2.6) e o esquema da Fig. 2.2.

Fig.2.2. MOSFET auto cascode (SCM).

De acordo com (2.1), as correntes de dreno de M1 e M2 podem ser expressas em

função dos níveis de inversão direta e reversa. Como M2 está em saturação:

I 2 ≅ I F 2 = I S 2i f 2

(2.7)

I D1 = I F 1 − I R1 = I S1 (i f 1 − ir1 ) = I 2 + I x

(2.8)

Para M1:

Dado que VP1=VP2=VP e VD1=VS2, então ir1= if2; Assim, desde (2.7) e (2.8) pode-se

encontrar a relação entre if1 e if2

if1

if 2

S I

= 1 + 2 1 + x

S1 I 2

(2.9)

A relação IX/I2 é definida pelo ganho de um espelho de corrente PMOS. Assim, a

expressão (2.9) pode ser usada como parâmetro de projeto independente da polarização e

tecnologia.

Aplicando (2.6.a) a M2 resulta em

VP − Vx

+1 =

φt

( 1+ i

f2

) (

)

− 1 + ln 1 + i f 2 − 1

(2.10)

13

enquanto que, para M1

VP

+1 =

φt

( 1+ i

f1

) (

)

− 1 + ln 1 + i f 1 − 1

(2.11)

As equações (2.9), (2.10) e (2.11) com cinco incógnitas (VP, if1, if2, IX/I2 e Vx) são

fundamentais para o desenvolvimento da metodologia de projeto da SBCS. Assumindo que

um gerador de tensão estabelece Vx em um valor dado, e um espelho de corrente (PMOS)

define IX/I2, tanto os níveis de inversão if1 e if2, como também as correntes são facilmente

determinadas.

A seguir, será apresentada a implementação para a tensão de referência Vx.

Fig.2.3. Estrutura autopolarizada (Voltage-Following Current Mirror -VFCM)

A estrutura autopolarizada VFCM [03-20] na Fig. 2.3 pode ser usada para gerar Vx

no nó intermediário do SCM. A tensão Vref pode ser calculada usando (2.6.a) e assumindo

M8-M9 saturados e em inversão fraca (W.I - Weak Inversion). A condição de inversão fraca

(if<1) é estabelecida pela corrente nos transistores e suas razões de aspecto. Nota-se que

para VP8=VP9, ID8=ID9, S8=KS9 e Vref=VS8, então:

Vref = VS 9 + φt ln (K )

(2.12)

Devido ao lento crescimento da função logaritmo natural, os valores adequados

para φtln(K) quando VS9=0 devem ser menores que 100mV.

Nesta topologia, VS9 pode ser zero (ground) ou uma tensão PTAT gerada por meio

de um segundo SCM operando na inversão fraca (SCM(W.I)), como mostrado na Fig.2.4.

Aplicando as expressões (2.9)-(2.11) ao SCM(W.I) composto de M3 e M4 ( Fig.2.4), resulta

em

S

VS 9 = φ t ln1 + 2 4

S3

(2.13)

14

Ambas tensões de referência expressas por (2.12) e (2.13) são imunes às variações

da fonte de alimentação, como também a parâmetros tecnológicos, desde que os

transistores operem na inversão fraca. De acordo com a expressão (2.13), o SCM(W.I)

pode operar como uma referência PTAT de muito baixa tensão, independente do nível de

corrente e da tecnologia.

As equações anteriores e algumas considerações de projeto para o SBCS serão

usadas na próxima seção para desenvolver uma metodologia que seja apropriada para baixa

tensão e potência.

2.4. Circuito SBCS proposto para baixa tensão de operação

Uma versão simples do circuito SBCS proposto é mostrado na Fig.2.4 [11], onde

VS9 pode ser zero ou Vx(W.I). Nesta estrutura, o resistor da implementação em [03] é

substituído por um SCM operando na inversão moderada (SCM(M.I)), para alcançar os

requisitos de baixa corrente e tensão de operação.

Fig.2.4. Referência de corrente autônoma (SBCS)

Quando a chave na Fig.2.4 é ligada à terra, a referência de tensão PTAT é

produzida por um offset intencional (K≠1 Fig.2.4) entre os dispositivos acoplados por porta

M8 e M9, ambos polarizados na inversão fraca. Neste caso, a tensão PTAT é dada por

(2.12), com VS9=0. Esta simples topologia é apropriada para aplicações onde moderada

performance é tolerada. Também, este circuito é estável para K>1.

15

Como indicado na seção anterior, outra forma para a implementação da referência

de tensão PTAT faz uso de um segundo SCM (M3-4) polarizado na inversão fraca

(SCM(W.I)), e K=1; assim; Vref=VS9, com VS9 dado por (2.13). Esta segunda topologia

resulta em melhor simetria e casamento, permitindo implementar M8-M9 com transistores

trapezoidais idênticos [12], para melhorar a regulação do circuito de referência de corrente,

sem demandar grande área de silício.

Uma metodologia de projeto apropriada para baixa tensão e consumo de potência é

descrita a seguir.

As especificações de projeto de um circuito referência de corrente são usualmente a

mínima tensão de operação (VDDmin), dissipação de potência, área de silício e

sensibilidades, como também o próprio valor da corrente.

A metodologia de projeto pode ser baseada no máximo consumo de potência ou no

valor da corrente de referência (Iref), e as dimensões dos transistores são otimizadas para

alcançar baixa tensão de operação. Esta metodologia pode ser aplicada à topologia simples

(chave ligada à terra), ou para a topologia simétrica (chave ligada ao nó Vx(W.I)) na Fig.2.4.

A mínima tensão de alimentação, a qual é determinada pelas limitações impostas

pelos dois ramos mais à esquerda na Fig.2.4, pode ser escrita como

VDD ≥ max{ VDSsat , P + VGS , M 1 , VGS , P + VDSsat , M 8 + Vx }

(2.14)

onde VDSsat,M8≅100mV dado que M8 opera na inversão fraca. Os transistores canal-p são

dimensionados para operar na inversão fraca, com um nível de inversão perto de 1 ou

menor; portanto, VDSsat,P ≅ 100 mVe VGS,P ≅ VTP.

Visto que Vx é menor que 100mV, e M1 será projetado para operar na inversão

moderada com VGS,M1 ≅ VTN + 100 mV, pode-se usar como aproximação de primeira ordem

VDD ≥ max{VTP ,VTN } + 200mV

(2.15)

para a mínima tensão de alimentação. Certamente, a expressão (2.15) é uma grosseira

aproximação quando cálculos mais precisos sejam necessários.

Na metodologia que adotamos o SCM(M.I) opera na inversão moderada

( 1 ≤ i f ≤ 100 ) com if2=3 ou, equivalentemente, VP2= Vx(M.I)=Vref (ver (2.10)). Se VS9=0,

podemos calcular if1 desde a equação (2.11) com VP/φt=ln(K) ou, equivalentemente,

resolver

1 + Vref φt ≡ 1 + ln( K ) = x + ln( x)

(2.16)

16

onde

(

)

x = 1+ i f 1 −1

(2.17)

é a densidade de carga (qSI) de inversão na fonte de M1.

Uma vez que x foi calculado para um valor específico de K, por exemplo K=10,

pode-se proceder a calcular S2/S1 desde (2.9)

S 2 (x + 1)2 − 4

=

S1

3(1 + 1 N )

(2.18)

onde S2 é calculado observando que ID2=NIref=ISQS2.if2 com if2=3. Portanto, sendo M2

NMOS→ ISQ=ISQN:

S2 =

NI ref

3I SQN

(2.19)

Para uma corrente de referência Iref<< ISQN, por exemplo, Iref <<ISQN_AMIS-1.5µ=30nA

ou Iref <<ISQN_TSMS-0.35µm=70nA, a escolha de S9=1 garante que M9 esteja na inversão fraca,

e o fator N define um compromisso entre consumo de potência e área.

A relação de aspecto (SP) dos transistores PMOS M5-M7 (M10) é calculada usando

(2.3) e (2.4), com nível de inversão menor que 1, usual para aplicações de baixa tensão.

Para o projeto da topologia simétrica usa-se a mesma metodologia anterior com

K=1, e S3, S4 são calculados desde (2.13) para um determinado valor de VS9.

A sensibilidade da SBCS à fonte de alimentação é associada com o efeito Early de

M7 e M8. O efeito Early pode ser reduzido usando comprimentos de canal (L) muito

longos, porém demanda grande área de silício. Uma técnica apropriada para baixa tensão

que permite obter comprimentos de canal muito longos com moderada área, é o transistor

trapezoidal, proposto em [12]. Esta é uma estrutura empilhada de dois transistores, com o

transistor associado ao dreno mais largo que o transistor ligado à fonte, como ilustrado na

Fig. 2.5. A relação de aspecto equivalente do transistor trapezoidal é (M+1).Wu/MLu.

Fig.2.5. Transistor trapezoidal (M2 é formado por M transistores M1 em paralelo)

17

Na seção seguinte, uma análise de sensibilidade da referência de corrente à fonte de

alimentação como também a outros parâmetros de projeto são brevemente discutidos.

2.5. Análise de sensibilidade

É uma exigência na geração de referências de corrente que a variação da corrente a

possíveis fontes de erro seja bastante menor que seu próprio valor absoluto. Tal requisito é

particularmente difícil de ser atendido quando as correntes são da ordem de pA.

Uma análise de sensibilidade a fontes de variação e parâmetros de projeto é

mandatário no projeto de fonte de corrente.

Devido à corrente ser expressa por equações paramétricas, as sensibilidades são

calculadas por derivadas com variáveis intermédias. Portanto, para calcular a sensibilidade

da corrente à tensão de referência e de alimentação, é considerada a seguinte seqüência de

dependência:

∆VDD →∆Vx→∆x→∆Iref

(2.20)

Ou seja, uma determinada variação na tensão de referência (Vx(M.I)) aplicada no

SCM(M.I), vai produzir uma variação na variável intermédia x (densidade de carga de

inversão na fonte de M1) que, por sua vez, varia a corrente. Uma variação em Vx(M.I) pode

ser causada por variações na tensão de alimentação ou por algum tipo de offset devido a

mismatch.

2.5.1. Sensibilidade a Vref

Para fazer este cálculo, considera-se tanto a tensão de alimentação quanto a

corrente específica constantes. Então, a sensibilidade normalizada da corrente de referência

pode ser escrita como:

δiref iref

δV x

=

1 δiref δx

.

.

iref δx δV x

(2.21)

as anteriores variações são calculadas desde as equações (2.9-2.11), resultando em:

δiref

iref

=2

δV x

1

φt

(x + 1)2 − 1

(x + 1) − 1 +

(1 + i f 1 i f 2 )

(2.22)

18

A tendência porcentual da equação (2.22) referente a x, é representada na Fig. 2.6, para

uma variação na tensão de referência de 1mV (δVx =1mV). Observar que a sensibilidade

tende a infinito para (x+1)→1, ou seja, M1,2 entrando na região de canal fracamente

invertido. Este resultado é previsível, pois o circuito de referência de corrente é baseada na

operação dos transistores M1-2 em regime de inversão que não o de inversão fraca, já que

quanto menor o nível de inversão, menor a densidade de carga no canal para formar uma

corrente e, por conseguinte, maior a sensibilidade da corrente a Vx.

Para reduzir a sensibilidade da corrente com relação à tensão de referência é

necessário um valor de x não muito baixo. Isto estabelece um compromisso entre área e

performance, (2.16). Por exemplo, assumindo if1/if2=3,4, para garantir sensibilidade menor

que 6%/mV de Vx, devemos ter x>2,0 ou K>5 na topologia simples. A topologia simétrica

define um melhor compromisso nesse aspecto, dado que para a mesma sensibilidade:

S4/S3=(K-1)/2. Outro aspecto importante é a dispersão da corrente do circuito. Para

maiores valores de x, mais estável é a referência de corrente, como ilustrado na Fig. 2.6, a

custas de maior consumo e de maior tensão VGS para M1 e M2.

Fig.2.6. Sensibilidade porcentual de Iref por mV de Vx em relação a x (2.17). (φt=26mV)

Como regra de projeto, pode ser adotado K=5-10 ou S4/S3=2-5 com if1/if2=3,4, para garantir

uma sensibilidade menor que 6%/mV. E if1/if2=3,4, é definido para N=1 e S2/S1=1,2.

19

2.5.2. Sensibilidade a VDD

A sensibilidade da corrente de referência à fonte de alimentação, está relacionada,

em primeira ordem, à variação da tensão de referência com a tensão de alimentação. Como

dito na seção anterior, esta dependência é causada pela limitada tensão Early de M7 e M8.

Esta sensibilidade pode-se escrever como:

δiref iref

δVDD

(x + 1)2 − 1

1 δiref δVx

2

.

.

=

= (x + 1) − 1 +

1+ if1 if 2

iref δVx δVDD φt

(

−1

)

δV x

.

δVDD

(2.23)

Na equação (2.23), o termo δVx δVDD é desconhecido. Então, a seguir vai ser

exposto brevemente seu cálculo.

Assumindo M8-9 e M6-7 na inversão fraca e saturação, com condutância de saída

finita, então, a relação V-I canal longo destes é governada pela lei exponencial e pela

dependência da tensão de Early, como indicado nas equações (2.24-2.25) e (2.26-2.27),

respectivamente:

V − VTN

I D 6 = I D8 = KI SN exp G 8

nN φt

V

V V

exp − X ( M .I ) 1 + D8− X ( M . I )

V AN

φt

V − VG 7 + VTP

I D 6 = I SP exp DD

n pφ t

V −V

I D 7 = I D 9 = I SN exp G 8 TN

nN φt

VDD − VD 6

1 +

V AP

(2.25)

V

V V

exp − X (W .I ) 1 + G 8− X (W . I )

VAN

φt

V −V +V

I D 7 = I SP exp DD G 7 TP

n pφt

(2.24)

VDD − VD 7

1 +

V AP

(2.26)

(2.27)

onde VAN e VAP são a tensão de Early dos transistores NMOS e PMOS, respectivamente.

Considerando que as variações na corrente causadas principalmente por M7 e M8

através de Vx são opostas, podemos normalizá-las como:

I D 6 I D8

=

I D7 I D9

(2.28)

Simplificando termos e aproximando (1+a)/(1+b)≅1+(a-b) para a,b<<1; resulta em:

[

V X ( M . I ) − V X (W . I ) VD8 − VG 8 − V X ( M .I ) − V X (W .I )

= 1 +

K exp

φt

V AN

].1 + V

− VD 6

V AP

D7

(2.29)

20

assumindo que V X ( M .I ) − V X (W .I ) << 1 , e VD8=VD6 variam diretamente com a tensão de

alimentação para VG8 constante,então, δVD8/δVDD=δVD6/δVDD≅1. Portanto, a sensibilidade

da tensão de referência à fonte de alimentação pode ser expressa como:

V X ( M . I ) − V X (W . I ) 1

K δV X ( M . I )

1

≅

+

.

. exp

φ t δVDD

φt

V AN V AP

(2.30)

onde ,

V X ( M .I ) − V X (W . I ) I D8

≅

≅1

K . exp

φt

I D9

(2.31)

E, finalmente, chegamos ao seguinte resultado:

δV X ( M . I )

δVDD

1

1

+

. ≅ φ t .

V AN V AP

1

1

= φ t

+

LN VEN LPVEP

(2.32)

onde LN e LP são os comprimentos de canal NMOS e PMOS, respectivamente, e VEN, VEP

são suas respectivas tensões de Early por unidade de comprimento do canal.

O interessante desta expressão é sua independência do tipo de topologia usada;

portanto, deve-se notar que a sensibilidade à tensão de alimentação pode ser reduzida sem

comprometer a funcionalidade dos circuitos.

Agora, substituindo este resultado em (2.23), é completada a variação normalizada

da corrente à fonte de alimentação, sendo como:

δiref iref

δVDD

1

1

= 2

+

LN VEN LPVEP

(x + 1)2 − 1

(x + 1) − 1 +

1+ i f 1 i f 2

(

)

−1

(2.33)

De (2.33) conclui-se que quanto menor a sensibilidade a Vref, melhor a regulação à

fonte de alimentação. Como dito anteriormente, usando transistores trapezoidais pode-se

reduzir ainda mais este resultado, mantendo constante o nível de inversão. Portanto,

assumindo-se LN VEN = LPVEP = L VE e L = MLu , a equação (2.33) pode ser escrita como:

δiref iref

δVDD

2

= 2

MLuVE

(x + 1)2 − 1

.(x + 1) − 1 +

1+ if1 if 2

(

)

−1

(2.34)

A Fig. 2.7 representa a regulação do circuito referência de corrente em função do

fator x. Observa-se que para valores de x>2,5 ou equivalentemente if1>11, pouco

21

melhoramento na regulação é obtido. Este comportamento é ainda mais evidente para

menores valores de M. Porém, deve-se ter senso na escolha de M, tendo em conta que

grandes valores de M melhoram o casamento entre transistores. Além disso, maiores níveis

de inversão aumentam a tensão de alimentação mínima como previsto em (2.14). Portanto,

valores de if1 entre 7 e 15 com fatores de 3<if1/if2 <5 são adequados para manter M1-2 em

inversão moderada e, assim, obter um bom compromisso entre área, performance e a

mínima tensão de alimentação na geração de pequenas correntes.

Os anteriores resultados também se aplicam a um transistor único ou associação

serie de transistores com equivalente comprimento de canal L=MLu. Portanto, por cada

duplicação do comprimento de canal uma redução de 2%/V é alcançada.

Fig.2.7. Sensibilidade porcentual/V de Iref referente a x, usando como parâmetro M.

Utilizando como especificações e parâmetros tecnológicos if1/if2=3.4, Lu = 6µm e VE =2V/µm.

Neste capítulo foram introduzidas duas eficientes topologias referências de

corrente. Também, foi desenvolvida uma metodologia de projeto enfocada para baixa

tensão com ultrabaixo consumo de potência. Com objetivo de otimizar a operação dos

circuitos a variações na fonte de alimentação e tensão de referência, um estudo de

sensibilidades é incluído para auxiliar a desenvolver critérios de projeto.

No próximo capítulo são realizados projetos dos circuitos propostos aqui, para

validar a técnica como também a fundamentação analítica que os suporta.

22

Capítulo 3

PROJETO DA REFERÊNCIA DE CORRENTE E

RESULTADOS

As referências de corrente autônomas apresentadas neste trabalho são estruturas

bastante simples que permitem polarizar circuitos analógicos CMOS de baixíssimo

consumo com alta eficiência de potência.

Neste capítulo, a primeira seção apresenta os projetos das referências de corrente

em duas diferentes tecnologias CMOS. Na seção 3.2, os resultados de simulação e

experimentais validam a técnica e a metodologia adotada para ultrabaixo consumo.

Entretanto, é importante destacar que estes circuitos podem ser usados para gerar maiores

correntes, segundo as necessidades da aplicação.

3.1. Projeto da referência de corrente para ultrabaixo consumo

Utilizando a metodologia proposta no capítulo anterior [11], foram projetadas as

duas topologias da Fig.2.4(3.1), nas tecnologias CMOS AMIS 1.5µm e TSMC 0.35µm.

Fig.3.1. Referência de corrente autônoma (SBCS)

23

Neste caso, as especificações iniciais foram adotadas em termos dos valores

absolutos da tensão de referência Vref<100mV e a corrente de referência Iref=400pA com a

menor tensão de alimentação possível.

O projeto começa por calcular o valor de K para uma tensão de referência menor

que 100mV com VS9=0. Para isto, é usada a equação (2.16), a qual prevê valores de K<50.

Isto determina que x<3,6 e, assim, desde (2.17) é obtido if1<20. A escolha de if1 deve ser

escolhida com base nos requisitos de mínima tensão VGS, a área necessária de M1-2 para

gerar uma corrente Iref=400pA e sensibilidade a Vx. É obvio que, na geração de pequenas

correntes com muita baixa tensão de operação, o melhor compromisso é estabelecido pelo

menor nível de inversão que possa ser usado na inversão moderada. Assim, sabendo de

(2.9) que if1>if2, na metodologia da seção 2.4 foi adotado if2=3. Se if2=3, (2.10) indica que

VP= Vx(M.I)=Vref . Sendo escolhido K=9 para gerar uma tensão de referência Vref=57mV,

então, x=2,345 e de (2.11) if1=10,2, que garante uma sensibilidade na corrente à tensão de

alimentação menor que 5%/V como previsto por (2.33) e Fig.2.6, assumindo-se

dispositivos canal longo. Como o projeto foi definido para mínimo consumo de potência,

faz-se N=1. Em seguida, obtemos S2/S1 desde a expressão (2.18). Então S2 é calculado de

(2.19) para a tecnologia AMI 1.5µm onde ISQN_

AMI

1.5µm=30nA.

Portanto,

S2=1*400pA/(3*30nA)=1/225 e, em conseqüência S1=1/270. Para evitar efeitos de canal

estreito é definido W1,2=4µm. Fazendo S9=1 e S8=KS9 garantimos que M8,9 estejam na

inversão fraca, já que Iref<<ISQN. Adotamos L8=L9=10µm para redução de efeitos canal

curto nestes dispositivos. As dimensões para o espelho de corrente são calculadas desde

(2.3) na inversão fraca (if <1) e ISQP_ AMI 1.5µm=10nA, como indicado na tabela 3.2.

A topologia simétrica é projetada usando a mesma metodologia anterior, fazendo

VS9=VX(W.I) e calculando a relação entre M3-4 como: S4/S3=(K-1)/2=4.

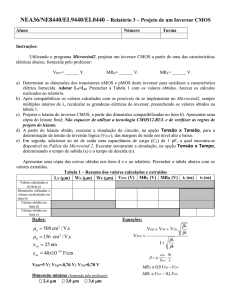

Simulações foram realizadas usando parâmetros BSIM3V3 fornecidos pela MOSIS

para as duas tecnologias. Os resultados de simulação são confrontados na tabela 3.1 e Figs.

3.2-3.5, para uma corrente de referência de Iref=400pA, N=1, K=9→x=2,345, S9=1,

S2/S1=1,2 e para S4/S3=4. As dimensões dos transistores do projeto nas tecnologias CMOS

AMIS 1.5µm e TSMC 0.35µm, são dadas na tabela 3.1 e 3.2, respectivamente. Visando

melhorar a regulação à fonte de alimentação, os transistores M8-9 e o espelho de corrente

PMOS são implementados usando estruturas trapezoidais, com M=5. Estes podem também

ser implementados usando estruturas retangulares que oferecem um melhor casamento

entre dispositivos.

24

Parâmetro

Tecnologia

Max{VTN+|VTP|}

VDDmin

Potência (VDDmin)

Eficiência Iref/Itotal

Sensibilidade de Vref

a VDD

Sensibilidade de Vref

à Temperatura

Sensibilidade de Iref

a VDD

Sensibilidade de Iref

à Temperatura

Topologia simples

K=9

0.35µ

1.5µ

1.30

1.55

0.8

1.1

1.0

1.65

25

25

Topologia simétrica

K=1

0.35µ

1.5µ

1.30

1.55

0.8

1.1

1.35

2.1

20

20

Unidade

V

V

nW

%

+0.55

+0.9

+0.50

+0.70

%/V

+0.30

+0.32

0.30

0.32

%/oC

+3.1

+4.5

+2.5

+3.5

%/V

+0.060

+0.047

+0.060

+0.047

%/oC

I SQN ( P ) 0.35 u = 70(30)nA

I SQN ( P )1.5 u = 30(10)nA n=1.2

n=1.2

Tabela. 3.1. Resumo de resultados de simulação.

A corrente de normalização dos transistores canal-n e canal-p é calculada desde os

parâmetros da tecnologia usando a equação (2.5). Neste cálculo, assume-se n=1,2 e

φt=26mV.

Como verificado na tabela anterior, os resultados de simulação são bastante

próximos às especificações iniciais do projeto. Os circuitos possuem um consumo de

potência ultrabaixo, o qual é eficiente em relação à corrente de saída de aproximadamente

400pA. Além disso, estas topologias são fortes candidatas para polarizar circuitos

analógicos CMOS operados à bateria (1.2 V).

Parâmetro

M1

M2

4

4

W [µm]

18x60

15x60

L [µm]

W.I M.I S.I W.I M.I S.I W.I

Regime

M3

10

10

M4

4x10

10

M5-7(10)

4. (M+1)

16.M

M8-9

10.(M+1)

10.M

M.I S.I W.I M.I S.I W.I M.I S.I W.I M.I S.I

10.2

3

0.02

0.0025

0.16

0.01

if

Tabela. 3.2. Dimensionamento dos transistores da topologia simétrica (AMIS 1.5). (M=5)

Parâmetro

M1

M2

2

2

W [µm]

6x180

5x180

L [µm]

W.I M.I S.I W.I M.I S.I W.I

Regime

M3

6

6

M4

4x6

6

M5-7(10)

4. (M+1)

10.M

M8-9

6.(M+1)

6.M

M.I S.I W.I M.I S.I W.I M.I S.I W.I M.I S.I

10.2

3

0.01

0.00125

0.05

0.005

if

Tabela. 3.3. Dimensionamento dos transistores da topologia simétrica (TSMC 0.35).(M=8)

25

0.07

0.06

Vref [mV]

0.05

0.04

0.03

0.02

0.01

0

0

0.4

0.8

1.2

1.6

VDD [V]

2

2.4

2.8

Fig. 3.2. Simulação de Vref versus VDD (AMIS 1.5)

0.07

0.06

Vref [mV]

0.05

0.04

0.03

0.02

0.01

0

0

0.4

0.8

1.2

1.6

VDD [V]

2

2.4

Fig. 3.3. Simulação de Vref versus VDD (TSMC 0.35)

2.8

26

-10

6

x 10

5

Iref [A]

4

3

2

1

0

0

0.5

1

1.5

VDD [V]

2

2.5

3

Fig. 3.4. Simulação de Iref versus VDD (AMIS 1.5), (pós-layout).

6

x 10

-10

5

Iref [A]

4

3

2

1

0

0

0.5

1

1.5

VDD [V]

2

2.5

Fig. 3.5. Simulação de Iref versus VDD (TSMC 0.35), (pós-layout).

3

27

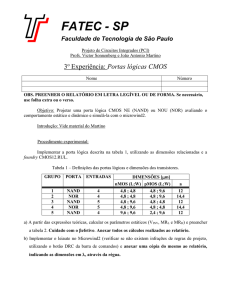

3.2. Resultados experimentais

Para validar o funcionamento dos circuitos e sua performance, foram integrados os

projetos da seção anterior, nas tecnologias CMOS AMIS 1.5µm e TSMC 0.35µm. A

integração foi realizada através de MOSIS satisfatoriamente, e foram recebidas 5 amostras

da tecnologia CMOS de 1.5µm e 40 da tecnologia de 0.35µm. Os chips implementados

contêm circuitos de teste, com acesso a vários de seus terminais para realizar uma análise

do ponto de operação e permitir caracterização de transistores.

A caracterização dos circuitos foi realizada com o analisador de parâmetros

HP4145B, para fazer o traçado das curvas (Iref,Vref) versus a tensão de alimentação e o

ponto de operação DC. O resumo dos dados experimentais é apresentado na tabela 3.4 e

Figs. 3.6-3.9. Estes resultados representam o valor médio de cada parâmetro analisado

entre as amostras disponíveis. Em relação à mínima tensão de alimentação, esta foi

definida para um PSRR (DC+) maior que 40dB, e o valor da corrente específica é extraída

usando (2.19).

Parâmetro

Tecnologia

Max{VTN+|VTP|}

VDdmin

Potência (VDDmin)

Eficiência Iref/Itotal

Sensibilidade de Vref

a VDD

Sensibilidade de Iref

a VDD

Topologia

simples K=9

1.5µ

1.52

1.15

1.5

25

Topologia simétrica

K=1

0.35µ

1.5µ

1.25

1.52

1.05

1.15

1.7

2.3

20

20

Unidade

V

V

nW

%

+1.6

+0.85

+1.3

%/V

+8.0

+4.0

+6.0

%/V

I SQN ( P ) 0.35 u = 68(30)nA

I SQN ( P )1.5 = 32(12)nA

u

Tabela. 3.4. Resumo de resultados experimentais.

O projeto feito na tecnologia AMIS 1.5µm ocupa uma área de silício de 200µm

x230µm (0.046mm2). Enquanto, para a tecnologia TSMC 0.35µm a área ocupada é de

134µm x 196µm (0.0263mm2), o qual corresponde em uma redução de 1,8 vezes. As

microfotografias dos chips fabricados e circuitos testados são ilustradas nas Figs. 3.123.15. O layout correspondente é incluído no Apêndice A

28

0.07

Vref [mV]

0.065

0.06

0.055

0.05

0.045

0.04

0

0.5

1

1.5

VDD [V]

2

2.5

Fig. 3.6. Vref versus VDD (Topologia simétrica AMIS 1.5)

0.07

0.065

0.06

0.055

0.05

0.045

0.04

1

1.5

2

2.5

Fig. 3.7. Vref versus VDD (Topologia simétrica TSMC 0.35).

3

29

6

x 10

-10

5

Iref [A]

4

3

2

1

0

0

0.4

0.8

1.2

1.6

VDD [V]

2

2.4

2.8

Fig. 3.8. Iref versus VDD (Topologia simétrica AMIS 1.5).

-10

4.5

x 10

4

3.5

Iref [A]

3

2.5

2

1.5

1

0.5

0

-0.5

0

0.5

1

1.5

VDD [V]

2

2.5

Fig. 3.9. Iref versus VDD (Topologia simétrica TSMC 0.35).

3

30

Os resultados anteriores indicam alta correlação entre os dados experimentais, de

simulação e analíticos, validando a técnica de gerar correntes na ordem de centenas de pA,

com tensão de alimentação ligeiramente menor que a soma de duas tensões de limiar

CMOS (VTN+|VTP|). As topologias propostas são adequadas para operar com tensões tão

baixas ou menores que 1.0 Volt em novas tecnologias submicrométricas.

Para verificar a precisão da referência de corrente é realizada uma análise estatística

dos circuitos implementados na tecnologia CMOS TSMC 0.35µm. Estes resultados são

apresentados nas Figs. 3.10 e 3.11, para 96% das amostras.

Fig. 3.10. Histograma de Vref com VDD=1.15V (TSMC 0.35).

Fig. 3.11. Histograma de Iref com VDD=1.15V (TSMC 0.35).

31

A corrente de referência apresentou uma variabilidade entre amostras de 36pA com

média aritmética de 361pA, correspondendo a um coeficiente de variação de 10%. O valor

médio também exibe um afastamento de 10% de seu valor nominal. Com relação à tensão

de referência PTAT, esta manifestou um desvio padrão de 1,7%, com respeito a sua média

aritmética de 58.77mV. Entretanto, os circuitos fabricados na tecnologia AMIS 1.5µm,

apresentaram uma média aritmética de 410pA. Estes resultados demonstram a robustez dos

circuitos.

Fig. 3.12. Microfotografia do chip fabricado na tecnologia AMIS 1.5µm. (2200µm x 2200µm)

200µm

230µm

Fig. 3.13. Zoom dos circuitos testados (AMIS 1.5µm).

32

Fig. 3.14. Microfotografia do chip fabricado na tecnologia TSMC 0.35µm. (1280µm x 1280µm)

135µm

200µm

Fig. 3.15. Zoom do circuito testado. (TSMC 0.35µm).

As semelhanças entre os histogramas da tensão e corrente de referência com

coeficiente de correlação de 0,43 indicam que o parâmetro dominante na dispersão da

corrente é devido à variação na tensão de referência PTAT. Esta variação na corrente é de

aproximadamente 20pA/mV ou 5%/mV. A corrente é afastada desde seu valor nominal por

um offset de valor médio 1,8mV, na tensão de referência . Este offset é originado pelo

descasamento entre as tensões de limiar dos transistores M3 e M4, e pelo descasamento

entre as correntes da estrutura VFMC. O fator com menor erro inserido na dispersão da

corrente foi a corrente específica de M1,2, o qual é estimado ser menor que 3% entre as

33

amostras da mesma rodada. O afastamento da corrente específica desde seu valor de

simulação é devido principalmente a variações na mobilidade e C’ox, como também à

incerteza no valor do fator rampa.

Um aumento na tensão mínima do circuito projetado em TSMC 0.35 foi observado,

o qual não é relacionado à metodologia adotada. Este foi devido a um leve incremento nas

tensões de limiar no processo de fabricação. Detectamos, posteriormente, um erro de

layout na realização dos transistores M1-2 (TSMC 0.35) em forma de serpentina que

embora não tenha impedido o funcionamento do circuito, impedia que tensões de

alimentação da ordem de 0.8V, previstas teoricamente para o funcionamento da fonte de

corrente autopolarizada. No caso na tecnologia AMIS 1.5 os resultados do ponto de

operação DC são muito próximos dos esperados. Porém, um aumento na regulação da

corrente foi obtido, dado pela não adequada modelagem da condutância de saída dos

MOSFETs.

Os erros anteriores podem ser reduzidos ainda mais. Para isto, um melhor

casamento entre os transistores críticos deve ser empregado. Por exemplo, os transistores

com porta comum podem usar uma estrutura centróide, com dimensões não mínimas, para

diminuir offset. Para o caso do espelho de corrente, é conveniente evitar erros de

descasamento globais (global mismatching) [19], mantendo os transistores mais próximos.

Uma associação série-paralela de um número considerável de transistores pode ser uma

boa alternativa. Em relação à corrente específica, é recomendável não usar W mínimo em

M1,2, para garantir baixa dispersão na corrente.

34

Capítulo 4

CONCLUSÕES E FUTUROS TRABALHOS

Apresentamos neste trabalho duas novas topologias referências de corrente

eficientes em potência, otimizadas para gerar correntes na ordem de centenas de pA com

bastante baixa tensão de operação. Sua funcionalidade e performance foram validadas

através de simulações e testes experimentais, nas tecnologias CMOS AMIS 1.5µm e

TSMC 0.35µm. Os circuitos apresentaram robustez, com alta correlação entre resultados

experimentais, de simulação e analíticos. Uma análise de sensibilidades com verificação

experimental é também incluída.

Uma referência de tensão PTAT adicional de ultrabaixo consumo é também

disponível, sendo que este tipo de referência possui uma ampla aplicação em projeto de

circuitos integrados CMOS.

Os circuitos apresentados são aptos para serem usados em polarização de circuitos

CMOS de baixo ou ultrabaixo consumo de potência, operados a bateria. Estes também são

potencialmente apropriados para operar com fontes de alimentação a partir de 0.7V em

tecnologias CMOS de 0.18µm. Além disso, são simples e de fácil projeto

Resultados experimentais mostram que a referência de corrente projetada neste

trabalho supera a performance de atuais referências de correntes reportadas na literatura.

Sugere-se, no futuro, verificar sua funcionalidade a variações de temperatura, como

também otimizar o projeto para reduzir ainda mais sua regulação com a fonte de

alimentação, e introduzir uma análise de mismatch e de ruído. Além disso, melhorar o

matching no layout para reduzir a dispersão da corrente entre amostras e verificar a

precisão das estruturas em várias rodadas das tecnologias CMOS já usadas.

De forma satisfatória foram realizadas integrações gratuitas através de MOSIS

representando um grande avanço para o desenvolvimento e treinamento de recursos

humanos na área de microeletrônica no Brasil.

35

Apêndice A

LAYOUT

DOS

CIRCUITOS

INTEGRADOS

NAS

TECNOLOGIAS CMOS AMIS 1.5µm e TSMC 0.35µm

2200µm

Fig. A.1. Layout do chip fabricado na tecnologia CMOS AMIS 1.5µm

1280µm

Fig. A.2. Layout do chip fabricado na tecnologia CMOS TSMC 0.35µm

36

M3-4

PMOS

M2

M1

200µm

M8-9

250µm

Fig. A.3. SBCS simétrica na tecnologia CMOS AMIS 1.5µm

220µm

200µm

Fig. A.4. SBCS simples na tecnologia CMOS AMIS 1.5µm

d

37

PMOS

PMOS

M8-9

M3-4

M2

M1

135µm

200µm

Fig. A.5. SBCS(1) simétrica na tecnologia CMOS TSMC 0.35µm

PMOS

PMOS

M8-9

M3-4

M2

M1

200µm

Fig. A.6. SBCS(1) simétrica projetada na tecnologia CMOS TSMC 0.35µm

130µm

38

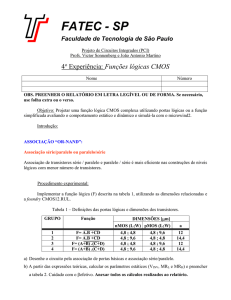

Apêndice B - Artigo publicado: ISCAS2004

DESIGN OF AN ULTRA-LOW-POWER CURRENT SOURCE

Edgar Mauricio Camacho-Galeano, Carlos Galup-Montoro, and Márcio Cherem Schneider

Departamento de Engenharia Elétrica, Universidade Federal de Santa Catarina, Brazil.

ABSTRACT

This paper presents the design of an ultra low-power self-biased

current source. We have designed a 400pA current reference in

both 1.5µm and 0.35µm CMOS technologies. The association of

a very simple topology, an efficient design methodology, and low

output conductance trapezoidal transistors has resulted in area of

0.046mm2 and power consumption around of 2nW. Experimental

results for the 1.5µm CMOS technology validate the design and

show that the current source can operate from supply voltage

down to 1.2V with a regulation better than 8%/V of supply

voltage.

1. INTRODUCTION

The increasing demand for inexpensive very-low-power portable

and implantable medical applications has resulted in the

integration of low-voltage CMOS analog circuits compatible

with standard VLSI technologies [1], [7]. This tendency has

motivated the development of systematic methodologies for

analog design. Furthermore, efficient, simple and easy-to-design

analog circuit structures are highly desirable [2], [4], [6].

CMOS analog design based on the inversion level technique

has been shown to be a robust alternative for high performance in

very-low-power [3] and low-voltage circuits [2]. This technique

uses the current as the main design variable. Thus, analog circuits

based on such a design technique require a self-biased current

source (SBCS) to operate at the nominal inversion level.

Moreover, the generation of on-chip current references avoids the

need for an extra pad to communicate with the external

environment.

Several SBCS circuits are found in the literature [4] - [7], but

a design methodology for easy reuse or design is not available

yet. Our SBCS is based on the circuits proposed in [4], [5], [6],

and [7], which have the same current dependence on temperature.

Despite the simplicity of the circuit proposed in [4], it uses a

resistor that for small currents (pA-nA) consumes a very large

silicon area. To avoid the need for a resistor, the authors of [6]

use a MOSFET working in the triode region to replace the

resistor. Even though simple, the SBCS of [6] is not suitable for

low voltage operation, as pointed out in [7]. Another

implementation of an SBCS is presented in [5] but the large

current gains and operation in strong inversion of some of its

transistors degrade its power efficiency. Reference [7] presents

another proposal of an SBCS, a less simple structure than the

previously mentioned ones. The circuit in [7] uses a self-cascode

MOSFET (SCM) in strong inversion and a PTAT voltage

reference generated by means of a current ratio. Although

appropriate for low voltage operation, the power efficiency of the

current source in [7] is not high due to the use of slightly more

complex structures and operation in strong inversion of some

transistors.

This paper presents the design of a self-biased current source

dedicated to technology-independent inversion level biasing,

which is suitable for low-voltage and very low power

applications. Our SBCS circuit uses MOSFET’s only and can

operate down to 1V supply voltage (in sub-0.18µm technologies

this circuit can operate from 0.6V) and exhibits low sensitivity to

supply voltage.

In Section 2, the ACM model [8] and the concept of inversion

level are summarized. We develop the basic design equations for

the SBCS using the ACM model in Section 3. Section 4

introduces the low-voltage CMOS SBCS. The design

methodology to obtain the dimensions of the MOSFET’s is

formulated in Section 5. As a design example, a very low power

SBSC is implemented in both 1.5µm and 0.35µm CMOS

processes and the associated simulation and experimental results

are presented in Section 6. Finally, concluding comments are

presented in Section 7.

2.

THE ACM MODEL

In the design methodology of the self-biased current source, we

have employed ACM, a current-mode MOSFET model that uses

the concept of inversion level [8]. According to the ACM model,

the drain current can be split into the forward ( I F ) and reverse

( I R ) currents

I D = I F − I R = I S (i f − i r )

(1)

W

I S = I SQ = I SQ (S )

L

(2.a)

where

I SQ = µC ' ox n

φt 2

2

(2.b)

I F ( I R ) depends on gate and source (drain) voltages. In forward

saturation, I F >> I R ; consequently, I D ≅ I F = I S i f . I S is the

normalization (specific) current and I SQ is the sheet specific

current ( I S for W = L ), i f (r ) is the forward (reverse) inversion

level, and µ, n, C’ox , φ t , and W/L=S are the mobility, slope

factor, gate oxide capacitance/area, thermal voltage, and the

transistor aspect ratio, respectively. The relationship between

current and voltage is given [8] by

VP − VS ( D )

φt

(

)

= 1 + i f ( r ) − 2 + ln 1 + i f ( r ) − 1

(3)

39

VP ≅

VG − VT 0

n

(4)

where VP is the pinch-off voltage and VTO is the zero bias

threshold voltage. More details about (1)-(4) can be found in [8].

The self-biased current-source circuit proposed here is an

extractor of normalization (specific) current ISQ [5] optimized for

low-voltage and very low power applications.

3.

DESIGN EQUATIONS FOR SCM AND SBS

Figure 2. Self-biased structure (SBS)

The core of the SBCS is the SCM shown in Figure1. The V-I

characteristic of the SCM is very appropriate for building lowvoltage analog blocks such as current references and sub-100mV

PTAT voltage references [3] – [7].

The self-biased structure in Fig. 2 can be used to generate VX

at the intermediate node of the SCM [4]. The voltage Vref can be

calculated using (3) and assuming M8-M9 in weak inversion

saturation. Noting that VP8=VP9, ID8=ID9, and Vref =VS8, then

S

8

Vref = VS 9 + φ t ln(K ) where K = S

9

(10)

In our circuit topology, VS9 can be either zero or a PTAT

voltage generated by means of a second SCM operating in weak

inversion, as shown in Fig. 3. The application of expressions (79) to the SCM composed of M3 and M4 operating in weak

inversion gives

S

VS 9 = φt ln 1 + 2 4

S3

Figure 1. Schematic of the SCM connected in diode

configuration (VB1=VB2=0).

The design equations (7)-(9) that describe the V-I

characteristic of the SCM have been deduced using (1)-(3) and

the schematic in Fig. 1. According to (1), the drain currents of M1

and M2 can be expressed as functions of the forward and reverse

inversion levels

I 2 ≅ I F 2 = I S 2i f 2

(5)