Linearity of phase detectors used in PLL systems.

Luiz Carlos Kretly1, Rômulo Mota Volpato2

1

IEEE, Campinas, Brasil, [email protected]

2

SBM, SRS, Brasil, [email protected]

Abstract

The performance of PLL systems, have been depended of the

linearity of the phase detector, in this way, this paper will

discus the linearity of the phase detector and propose one

method for quick measure it. For test this method we will

compare one common phase detector for industrial use and

the classic topology made in BiCMOS .35 technology with

four flip-flop´s D type. For the more facility we will use a

low pass filter type one in both configurations and the result

will be interesting for

make choice the phase detector

topology.

Word key: Phase detector.

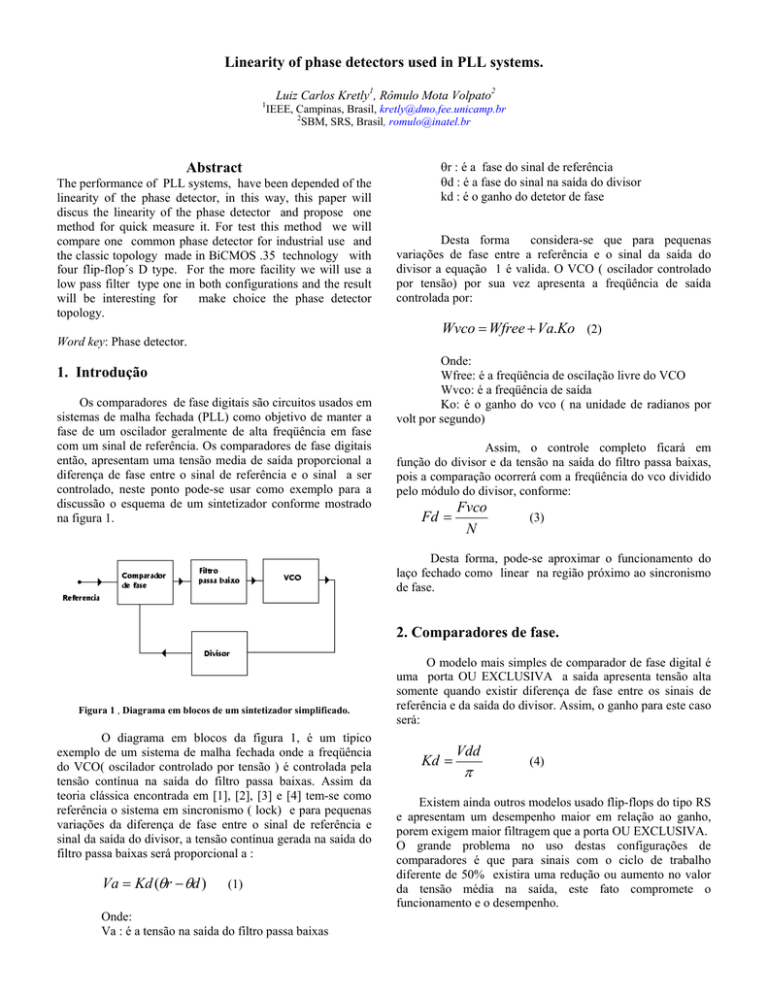

1. Introdução

Os comparadores de fase digitais são circuitos usados em

sistemas de malha fechada (PLL) como objetivo de manter a

fase de um oscilador geralmente de alta freqüência em fase

com um sinal de referência. Os comparadores de fase digitais

então, apresentam uma tensão media de saída proporcional a

diferença de fase entre o sinal de referência e o sinal a ser

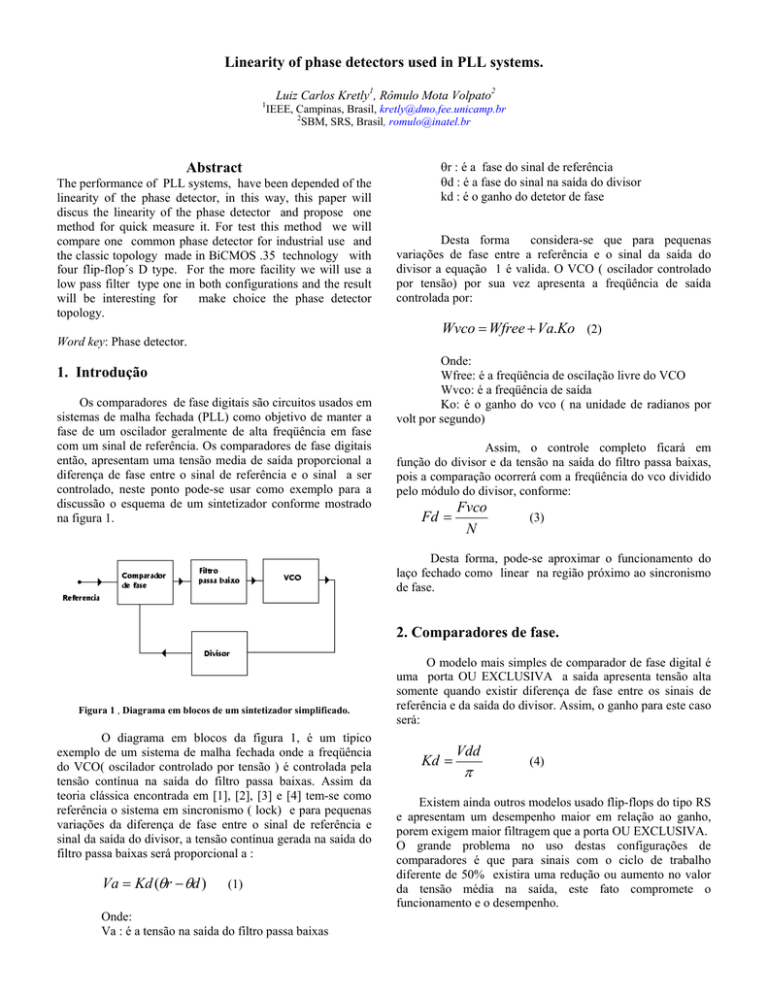

controlado, neste ponto pode-se usar como exemplo para a

discussão o esquema de um sintetizador conforme mostrado

na figura 1.

θr : é a fase do sinal de referência

θd : é a fase do sinal na saída do divisor

kd : é o ganho do detetor de fase

Desta forma

considera-se que para pequenas

variações de fase entre a referência e o sinal da saída do

divisor a equação 1 é valida. O VCO ( oscilador controlado

por tensão) por sua vez apresenta a freqüência de saída

controlada por:

Wvco = Wfree + Va.Ko (2)

Onde:

Wfree: é a freqüência de oscilação livre do VCO

Wvco: é a freqüência de saída

Ko: é o ganho do vco ( na unidade de radianos por

volt por segundo)

Assim, o controle completo ficará em

função do divisor e da tensão na saída do filtro passa baixas,

pois a comparação ocorrerá com a freqüência do vco dividido

pelo módulo do divisor, conforme:

Fd =

Fvco

N

(3)

Desta forma, pode-se aproximar o funcionamento do

laço fechado como linear na região próximo ao sincronismo

de fase.

2. Comparadores de fase.

Figura 1 . Diagrama em blocos de um sintetizador simplificado.

O diagrama em blocos da figura 1, é um típico

exemplo de um sistema de malha fechada onde a freqüência

do VCO( oscilador controlado por tensão ) é controlada pela

tensão contínua na saída do filtro passa baixas. Assim da

teoria clássica encontrada em [1], [2], [3] e [4] tem-se como

referência o sistema em sincronismo ( lock) e para pequenas

variações da diferença de fase entre o sinal de referência e

sinal da saída do divisor, a tensão contínua gerada na saída do

filtro passa baixas será proporcional a :

Va = Kd (θr − θd )

(1)

Onde:

Va : é a tensão na saída do filtro passa baixas

O modelo mais simples de comparador de fase digital é

uma porta OU EXCLUSIVA a saída apresenta tensão alta

somente quando existir diferença de fase entre os sinais de

referência e da saída do divisor. Assim, o ganho para este caso

será:

Kd =

Vdd

π

(4)

Existem ainda outros modelos usado flip-flops do tipo RS

e apresentam um desempenho maior em relação ao ganho,

porem exigem maior filtragem que a porta OU EXCLUSIVA.

O grande problema no uso destas configurações de

comparadores é que para sinais com o ciclo de trabalho

diferente de 50% existira uma redução ou aumento no valor

da tensão média na saída, este fato compromete o

funcionamento e o desempenho.

A solução para este problema é usar a configuração

de dois flip-flops do tipo D ou JK conforme configuração

mostrada na figura 2.

Figura 4. Lay Out do Comparador de fase com flip-flops tipo D.

Figura 2 .Comparador de fase com flip flops tipo D.

Porem esta configuração necessita de grande filtragem

para retirar o nível continuo necessário aplicado no VCO.

Desta forma a configuração com quatro flip flops tipo D com

fontes de corrente, apresenta melhor desempenho.

Figura 3 . Comparador de fase com quatro flip flops tipo D e fonte de

corrente.

3. Construção do comparador.

O comparador mostrado na figura 2, foi construído com a

tecnologia BiCMOS .35 e o lay out é mostrado na figura 4.

.

Para verificar as características do comparador, foi

aplicado dois sinais em fase, sincronizados externamente. Isto

foi feito através do uso de geradores de sinais com entrada de

sincronismo externa, desta forma o gerador mestre envia sinal

de sincronismo para o gerador escravo. Esta configuração

apresentou pequeno offset de fase, da ordem de 10,3 ns.

Assim para conseguir a característica estática do comparador

foi colocado na saída do gerador de charge pump ( fonte de

corrente) um filtro passa baixas. A figura 5 ilustrar o arranjo

usado na medição da característica estática do Comparador.

Figura 5. Diagrama em blocos para medição das características do

Comparador.

O procedimento para conseguir as características

comparador foi manter a freqüência dos geradores iguais e

variar o retardo do gerador escravo. Desta forma é possível

medir a tensão contínua gerada na saída do filtro passa baixas,

que neste caso foi um resistor de 10 kΩ e um capacitor de

10nF. O resultado da variação de fase é mostrado na figura 6.

Observe que mesmo quando a freqüência de trabalho

(Freqüências de 1kHz indicada na curva inferior e 5 kHz

indicada na curva superior mostradas na figura 6 ) é

modificada a linearidade permanece.

700

4. Conclusões

600

Neste experimento, verificou-se que a configuração do

comparador influencia na linearidade do ganho. Esta não

linearidade terá influencia direta na estabilidade do sistema,

visto que o ganho do comparador Kd afeta diretamente a

freqüência de trabalho do VCO. Desta forma se for possível

conhecer o ponto de operação exato do VCO e o ganho do

comparador de fase, o funcionamento do sistema na condição

de sincronismo ficará mais estável.

Tensão [mv]

500

400

300

200

100

25

0

23

0

21

0

19

0

17

0

14

0

12

0

10

0

80

60

40

0

20

0

Tempo [ms]

Figura 6. Resultado da medição de fase do comparador.

Da teoria clássica de comparadores de fase, para

pequenas variações de fase entre o sinal de referência e o

sinal da saída do divisor, o sinal gerado na saída do filtro

passa baixas é linear e proporcional ao ganho do comparador.

Este fato foi comprovado para a variação de fase de 10

em 10 ns até o limite de 250 ns. Desta forma o procedimento

de projeto e o funcionamento sincronizado estão coerentes,

para esta configuração, entretanto a título de comparação,

também foi levantado as características de um comparador de

fase integrado comercial, CD 4046B. Foi usado neste

experimento o comparador de fase II com a mesma tensão de

alimentação de 3,3 V contínuo, e o resultado usado o mesmo

procedimento é mostrado na figura 7.

3000

Tensão [mv]

2500

5. Trabalhos futuros

A construção do comparador de fase usando quatro flipflops tipo D com fonte de corrente na tecnologia BiCMOS .35

mostrou-se bastante atraente no quesito linearidade, entretanto

a tensão inicial foi de aproximadamente 200mV, este fato não

ficou completamente esclarecido, pois o offset do retardo está

entorno de 10,3 ns. Desta forma , na região do entorno de

zero volt não foi avaliada, assim a conclusão da melhoria da

linearidade não está completa, pois não se sabe com ocorrerá

a variação do retardo abaixo de 10 ns. Existe ainda a hipótese

da tensão de 200 mV ser gerada pelo charge pump (Gerador

de corrente).

6. Agradecimentos

Especial agradecimentos ao programa PMU/FAPESP

pelo suporte na confecção do circuito integrado e ao CenPRA

pela grande apoio na simulação e construção do lay out e ao

professor L.C Kretly, sem os quais este trabalho não seria

possível.

2000

Referências Bibliográficas

1500

1000

[1] Rhode, Urich L. RF/microwave circuit design for

wireless aplication, John Wiley & Soon, 2000.

500

0

25

0

23

0

21

0

19

0

17

0

14

0

12

0

10

80

60

40

20

0

0

Tempo [ns]

Figura 7. Resultado da medição de fase para o comprador comercial.

Na figura 7, observa-se que para valores de retardo até 70

ns existe um ganho maior, assim da teoria clássica, não se

pode considerar o ganho constante para a condição de

sincronismo, entretanto, para valores de retardo acima de 80

ns existe linearidade para os três valores de freqüência

usadas no experimento.

[2] Young, Paul H. P.E., Electronic communication

techniques, Prentice Hall,1999.

[4] Modelling the PLL,AN 178, Phillips Semiconductors

[5] Austriamicrosystems, “ 0,35µm HBT BiCMOS RF

SPICE Models,” Rev :2.0

[6] Austriamicrosystems, “ 0,35µm HBT BiCMOS

Process Parameters,” Rev: 3.0

[7] Austriamicrosystems, “ 0,35µm HBT Design

Rules,”Rev: 5.0

[8] Freescale Semiconductor,” Datasheet MC 145202-1”

[9] Gerry C. T. Leung e Howard C. Luong, “ A 1-V 5.2

GHz CMOS Synthesizer for ALAN Applicantions,” em IEEE

J. Solid-state circuits, vol 39, pp1873 a 1881.

[10] Pietro Andreani, “On the Phase-Noise and PhaseError Performances of Multiphase LC CMOS VCOs,” IEEE J.

Solid-sate circuits, vol 39, pp1883-1893.

[11] Peng-Un Su, “A 0,25µm CMOS OPLL Transmitter

IC for GSM and DCS Applications,” IEEE T. Microwavw

theory and techniques, vol 53, pp 462-471.

[12] L. C. Kretly, “ Notas complementares,” FEECUNICAMP 2° S/2002, IE 327.