UNIVERSIDADE FEDERAL DE LAVRAS

DEPARTAMENTO DE CIÊNCIA DA COMPUTAÇÃO

Orientador: Prof Wilian Soares Lacerda

Desenvolvimento de uma Unidade

Processadora Discreta Microprogramável

Bolsista: Edna Mie Kanazawa

Relatório Final apresentado à

Universidade Federal de Lavras, como

parte das exigências do PIBIC/CNPq,

referente ao período de setembro/1999

à julho/2000.

LAVRAS

MINAS GERAIS – BRASIL

AGOSTO/2000

UNIVERSIDADE FEDERAL DE LAVRAS

DEPARTAMENTO DE CIÊNCIA DA COMPUTAÇÃO

Desenvolvimento de uma Unidade Processadora Discreta Microprogramável

RESUMO DOS OBJETIVOS E RESULTADOS

Atualmente, com os computadores digitais fazendo parte do nosso cotidiano, se faz

necessário o perfeito entendimento de seu funcionamento tanto interno, como sua interação

com o mundo externo. Mais e mais desenvolvem-se tecnologias para que se obtenha

processamentos mais velozes. Mas entre todas as tecnologias já desenvolvidas, observa-se

que a arquitetura dos computadores digitais atuais segue a arquitetura dos primeiros

computadores eletrônicos: Arquitetura de Von Newmann.

Neste projeto, objetivou-se o estudo e o desenvolvimento de um protótipo de

processador utilizando-se esta arquitetura, para a implantação de novas técnicas de

processamento. O projeto dividiu-se em: estudo das arquiteturas existentes,

desenvolvimento do processador com base no estudo realizado, elaboração dos circuitos

eletrônicos, simulação dos circuitos, estudo e criação das instruções do processador,

montagem em wire-wrap utilizando-se chips comerciais e teste do protótipo. Os circuitos

dividiram-se em: Contador de programa e Apontador de pilha, Contador em anel, Gerador

de clock e inicialização, Registrador de endereço de memória, Microprogramação, Unidade

lógica aritmética e Portas de entrada e saída. Utilizou-se o software de simulação

MAXPLUS II da ALTERA, para verificar o perfeito funcionamento dos circuitos

desenvolvidos. As instruções implementadas em microprograma dividiram-se em:

Instruções aritméticas (ADI, SUB, INC, DEC e CMP), Instruções lógicas (ANI, ORI, XRI,

XRA e CMA), Instruções de transferência de dados (LDA, LDI e STA), Instruções de

desvio (JMP, JZ, JEQ, JS, JNZ, JNEQ e JNS) e Instruções de chamadas e retorno de subrotinas (CALL e RET). Através destas instruções desenvolveu-se programas em assembly

para execução no protótipo.

O protótipo montado tem atendido as expectativas esperadas conforme a simulação,

além de poder proporcionar um método de estudo e desenvolvimento de novas técnicas de

arquiteturas de processadores digitais.

___________________________

Prof. Wilian Soares Lacerda

Orientador

___________________________

Edna Mie Kanazawa

Bolsista

2

AGRADECIMENTOS

Ao orientador, Wilian Soares Lacerda que tornou possível o desenvolvimento da

Unidade Processadora Discreta Microprogramável.

Aos professores, que ajudaram de diversas formas a implementar e a construir o

protótipo.

3

Índice

1 Introdução

06

2 Revisão de Literatura

08

3 Caracterização do Problema e sua Importância

09

4 Objetivos

09

5 Metodologia

10

6 Resultados e Discussões

10

6.1 Funcionamento

10

6.2 Unidade de Controle

13

6.3 Memória

13

6.4 Unidade Lógica Aritmética

14

6.5 Registrador de Endereços

15

6.6 Contador de Programa e Apontador de Pilha

15

6.7 Descrição simplificada dos componentes utilizados no projeto

16

6.7.1 Descrição do CI 74161

16

6.7.2 Descrição do CI 74191

18

6.7.3 Descrição do CI 74173

19

6.7.4 Descrição do CI 74157

19

6.7.5 Descrição do CI 74181

20

6.8 Tabela de instruções

20

6.9 Descrição dos sinais ativos durante o ciclo de busca

22

6.10 Descrição dos sinais ativos durante a instrução ADI <valor>

23

6.11 Descrição dos sinais ativos durante a instrução LDA <endereço>

26

6.12 Descrição dos sinais ativos durante a instrução STA <valor>

27

6.13 Descrição dos sinais ativos durante a instrução SUBI <valor>

29

6.14 Descrição dos sinais ativos durante a instrução INC A

30

6.15 Descrição dos sinais ativos durante a instrução DCR A

30

6.16 Descrição dos sinais ativos durante a instrução LDI <valor>

30

6.17 Descrição dos sinais ativos durante a instrução ANI <dado>

30

6.18 Descrição dos sinais ativos durante a instrução ORI <dado>

31

6.19 Descrição dos sinais ativos durante a instrução XRI <dado>

31

6.20 Descrição dos sinais ativos durante a instrução XRA

31

4

6.21 Descrição dos sinais ativos durante a instrução CMA

31

6.22 Descrição dos sinais ativos durante a instrução JMP < endereço >

32

6.23 Descrição dos sinais ativos durante a instrução JZ, JC, JS,JEQ <endereço> 32

6.24 Descrição dos sinais ativos durante a instrução CALL < endereço >

33

6.25 Descrição dos sinais ativos durante a instrução RET

33

6.26 Descrição dos sinais ativos durante a instrução CMP <dado>

33

6.27 Descrição dos sinais ativos durante a instrução ADD < endereço >

34

6.28 Descrição dos sinais ativos durante a instrução SUB <endereço>

34

6.29 Descrição dos sinais ativos durante a instrução INA

34

6.30 Descrição dos sinais ativos durante a instrução IND

34

6.31 Descrição dos sinais ativos durante a instrução OUTA

35

6.32 Descrição dos sinais ativos durante a instrução OUTD

35

6.33 Descrição dos sinais ativos durante a instrução HALT

35

6.34 Descrição dos sinais ativos durante a instrução PUSH

35

6.35 Descrição dos sinais ativos durante a instrução POP

35

7 Referências Bibliográficas

37

Anexos

A - Esquemas dos circuitos eletrônicos

B - Tabelas de códigos das instruções

C - Resultados da simulação

D - Folha de dados dos componentes eletrônicos

5

1 Introdução

A Unidade Processadora Discreta Microprogramável é um protótipo desenvolvido

dentro do estudo de várias arquiteturas de processadores digitais. Neste estudo observou-se

que a maioria das arquiteturas segue a arquitetura dos primeiros computadores eletrônicos,

ou seja, na Arquitetura de von Neumann. O objetivo do projeto baseia-se no

desenvolvimento de um protótipo de um microprocessador com uma arquitetura simples e

de fácil entendimento, para o desenvolvimento de tecnologias mais avançadas.

Na figura 1 apresentamos blocos com as partes básicas que constituem o protótipo

do microprocessador. Observa-se que o processador gerencia todos os componentes

externos (portas de entrada /saída e memória).

Figura1 – Componentes que constituem o protótipo do microprocessador

Em geral o computador básico constitui-se de 3 partes: Unidade Central de

Processamento (CPU), Portas de Entrada /Saída e Memórias.

A CPU contém elementos de armazenamento (registradores), circuitos

computacionais representado pela Unidade Lógica Aritmética (ULA), Circuitos de

Controle e Temporização.

As funções primárias da CPU são:

- Buscar, decodificar, e executar instruções do programa armazenado na

memória;

- Transferir dados da e para memória e para portas de entrada e saída;

- Prover os sinais de controle e temporização para todo o sistema.

A Unidade Lógica Aritmética da CPU executa operações como somar, deslocar,

rodar, comparar, incrementar, decrementar, negar, AND, OR, XOR, complementar e zerar.

Para a execução de uma operação de soma, a ULA utiliza dois registradores (Acumulador

e Temporário). O conteúdo do Acumulador é somado com o conteúdo do registrador

temporário e o resultado é enviado ao acumulador. De grande importância para o

programador é o registrador de código de condição dos flags. Os flags incluem indicadores

de zero, de resultado negativo, de vai-um, etc. Os flags são usados para tomadas de decisão

quando posteriormente, se usam instruções de desvio.

Os registradores temporário e acumulador podem ser considerados parte da

ULA.

6

A seção de CONTROLE E TEMPORIZAÇÃO é a parte mais complexa e afeta

todos os eventos da CPU no microcomputador. Cada instrução do programa pode ser

dividida em estágios de busca, decodificação e execução. Esses pequenos estágios ainda

podem ser subdivididos em outros passos que podem ser chamadas de microprograma. O

microprograma para cada instrução reside na seção de decodificação de instruções e é

executado pela seção de controle e temporização da CPU.

A sequência de busca-decodificação-execução de instrução é fundamental para a

operação do computador. A primeira instrução buscada da memória de programa é tomada

como sendo o código de operação da primeira instrução e é colocada no registrador de

instruções pela seção de controle da CPU. O código, é então, interpretado pelo

decodificador de instrução. O decodificador de instruções identifica o microprograma que

a seção de controle e temporização deve seguir para executar uma instrução específica.

Existe um conjunto de instruções que o microprocessador pode executar.

As instruções podem ser classificadas de diversas maneiras:

1. Instruções aritméticas

2. Instruções lógicas

3. Instruções de transferência de dados

4. Instruções de desvio

5. Instruções de chamada de sub-rotina

6. Instruções de retorno

7. Instruções de pilha

1.

2.

3.

4.

5.

6.

Nas instruções aritméticas temos:

Somar, Somar com vai -um

Subtrair, Subtrair com vai-um , Empréstimo

Incrementar

Decrementar

Comparar

Negar

1.

2.

3.

4.

Nas instruções lógicas temos:

AND

OR

XOR

NOT

1.

2.

3.

4.

Nas instruções de transferência e dados temos:

Carregar

Armazenar

Mover

Zerar

1.

2.

3.

4.

5.

6.

Nas instruções de desvio temos:

Desvio Incondicional

Desvio de zero

Desvio se não zero

Desvio se igual

Desvio se desigual

Desvio se positivo

7

7. Desvio se negativo

Nas instruções de pilha temos:

1. Empilhar

2. Desempilhar

2 Revisão de Literatura

Segundo Tokheim, “Em relação à Eletrônica, o estudante de hoje ou o especialista

de amanhã deve ter um conhecimento de microprocessadores e de sistemas baseados em

microprocessadores. Isto inclui conhecimentos tanto em software como de hardware. O

microprocessador é a base de toda uma linguagem de máquinas e dispositivos inteligentes.

O microprocessadores serão encontrados em diversos produtos: de brinquedos a

processadores de palavras; de computadores de bolso a eletrodomésticos; de robôs

industriais a termostatos. Com o advento de microprocessadores microprogramáveis

espera-se no futuro uma aceleração do desenvolvimento das máquinas inteligentes. ”

Nosso cotidiano está sendo domado cada vez mais por máquinas inteligentes e para

desenvolvimento de máquinas mais velozes e mais eficientes temos que ter um

conhecimento básico de como a informação é processada por essas máquinas.

Vários autores [TOKHEIM, TAUB, MALVINO] descrevem as seguintes

arquiteturas: 8080/8085 da Intel e 6800 da Motorola, pois não apresentam tanta

sofisticação e apresentam-se adequadas para apresentação introdutória a microprocesadores

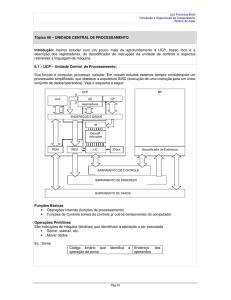

Segundo Stalling, a organização básica de um sistema de computador constitui-se

de Unidade Central de Processamento conectada aos barramentos de dados, endereços e

controle, como ilustrado na figura 2.

Figura 2 – Organização básica de um computador

A estrutura é o caminho pelo qual os componentes são relacionados e a função é

operar cada componente individualmente como parte da estrutura.

Operações básicas em um computador:

- Processamento de dados;

- Armazenamento de dados;

- Transferência de dados;

- Controle.

A estrutura deve compor-se de 4 componentes:

- Unidade Central de Processamento (CPU);

- Memória Principal;

8

-

I/O – Transfere dados entre o computador e o meio externo;

Sistema de comunicação.

A parte mais complexa do processador (CPU) é a sua unidade de controle

responsável pela geração dos sinais de sincronismo de todos os circuitos do processador.

Na literatura [ZUFFO, HAYES] temos descrito várias soluções para implementação da

unidade de controle. Algumas técnicas permitem que a unidade de controle seja mais

versátil para modificações e ampliação, como a técnica de microprogramação. Por isto o

processador desenvolvido é microprogramável.

Hennessy e Patterson descrevem em suas obras detalhes para projeto de

processadores mais rápidos, utilizando técnicas de pipeling. O projeto do processador se

torna bem mais complexo, para se conseguir este objetivo. No protótipo desenvolvido, esta

técnica não foi utilizada por dificuldades de implementação.

3 Caracterização do Problema e sua Importância

O desenvolvimento do protótipo da Unidade Processadora Discreta

Microprogramável, divide-se em diversas partes funcionais tais como: Contador de

Programa e Apontador de Pilha, Contador em Anel, Gerador de Clock, Registrador de

Endereço, Microprogramação, Unidade Lógica Aritmética e Portas de Entrada/Saída. Cada

parte foi devidamente estudada, esquematizada, simulada e implementada dando origem ao

sistema. Esta divisão é importante, pois ao analisar o processamento de uma instrução é

possível identificar quais partes estão sendo envolvidas para execução da instrução.

A compactação das arquiteturas de computadores atuais e a velocidade com que as

informações são processadas, dificulta a visualização e o entendimento do seu

funcionamento. Com o Desenvolvimento da Unidade Processadora Microprogramável, que

possui uma arquitetura simples e onde a velocidade e a compactação dos circuitos não são

itens essenciais, é possível verificar e entender como as informações são processadas.

Com o protótipo em funcionamento, torna-se possível este entendimento básico de

processamento e muitos caminhos poderão ser abertos para o desenvolvimento de outras

arquiteturas com tecnologias mais avançadas, pois o requisito básico já foi fixado.

4 Objetivos

O presente projeto tem como meta os seguintes objetivos:

-

Estudo das técnicas de arquitetura para processador digital.

Desenvolvimento de um protótipo de processador digital.

Implementação de várias técnicas de arquitetura de processadores digitais.

Testes de novas técnicas de arquitetura.

Divulgar o estudo e pesquisa na área de arquitetura de processadores digitais dentro e

fora do departamento.

Formar uma equipe de pesquisa no departamento para atuar na área de arquitetura de

processadores e computadores.

Propor novas pesquisas na área de projetos e desenvolvimentos de arquitetura de

processadores e computadores.

9

5 Metodologia

Para atender os objetivos do presente projeto, foi adotado a seguinte metodologia:

a) O estudo das técnicas de arquitetura de processadores foi realizado através de pesquisa

bibliográfica em livros, artigos, revistas, e internet. Também foram feitos contatos com

pesquisadores da área para troca de informações, visando um intercâmbio e

aproximação com pessoas da área.

b) O projeto do protótipo do processador digital desenvolveu-se inicialmente através do

detalhamento em diagrama de circuitos eletrônicos. O circuito eletrônico foi desenhado

em computador PC utilizando-se a ferramenta específica denominada Tango.

c) Com o circuito definido, passou-se para a fase de simulação em computador utilizandose software com esta finalidade (Maxplus II).

d) Retornou-se a etapa de projeto para correção dos circuitos, devido a alguns problemas

apresentados durante a simulação.

e) Sanados todos os problemas de simulação, iniciou-se a fase de implementação do

circuito eletrônico utilizando-se montagem em placas de wire-wrap.

f) Terminado a montagem, passou-se para a etapa de testes em laboratório com o uso de

instrumentos de medição (multímetros, osciloscópios).

g) Problemas ocorridos durante os teste em laboratório, fez rever e corrigir a simulação e

a etapa de projeto.

6 Resultados e Discussões

Estudou-se várias arquiteturas de processadores já existentes e sua evolução,

observando as características de cada arquitetura concluiu-se que a maioria seguem a

arquitetura de Von Newmann.

Após estudos realizados, foram feitos diagramas que descrevem o funcionamento

geral e um diagrama detalhado de cada bloco. Abaixo segue a descrição do funcionamento.

6.1 Funcionamento

Na figura 3 temos o diagrama em blocos do protótipo do processador.

10

Figura 3 – Diagrama em blocos do protótipo

Os sinais gerados pelo circuito de sincronismo afeta todos os eventos da CPU. Por

isso antes de explicar o funcionamento do projeto daremos uma breve explicação no

circuito de sincronismo.

O Gerador de Clock e Contador em Anel fazem parte do circuito de sincronismo.

Na figura 4 temos o diagrama em blocos do circuito de sincronismo, e também os sinais

gerados em cada bloco.

O Gerador de Clock possui duas opções: clock automático, onde temos um onda

quadrada de 1kHz, e o clock manual onde pulsos são gerados através de uma chave. Com o

clock manual podemos executar uma instrução passo a passo.

No Contador em Anel temos as saídas T1, T2, T3, T4 que determinam o ciclo de

busca e execução da instrução. A saída do Contador em Anel pode ser visualizada na

figura 5. Observe que T4 permanece em nível alto até que as microinstruções da instrução

sejam executadas.

11

Figura 4 – Diagrama em blocos do circuito de Sincronismo

Figura 5 – Formas de onda dos sinais de sincronismo

Em T1 o endereço apontado pelo Contador de Programa é armazenado no

registrador de endereços. Em T2 o Contador de Programa é incrementado, ou seja aponta

para o endereço da próxima instrução. Em T3 o endereço armazenado no Registrador de

Instruções é transferido para o barramento de endereços e a memória é habilitada para

leitura. O conteúdo da memória deve corresponder a um código de uma instrução, cujo

valor é armazenado no Registrador de Instruções. T4 corresponde ao ciclo de execução da

instrução. O ciclo de execução pode durar até 13 ciclos de clock, controlados por um

contador, ou seja em T4 são executadas as microinstruções de uma instrução. A sequência

de microinstruções é executada até que o sinal de controle FIM seja ativado pelo circuito

de microprogramação, e um novo ciclo de busca e execução é iniciado.

No circuito de microprogramação projetado podemos ter 127 instruções diferentes.

Cada instrução pode desenvolver-se dentro de 13 ciclos de microinstruções. O ciclo de

busca, corresponde à três ciclos de clock. Se o bit mais significativo do código da instrução

estiver ativo, ou seja em 1 (um) teremos instruções de desvio condicional.

12

6.2 Unidade de Controle

A Unidade de Controle é composta pelo Registrador de Instruções, Contador

Síncrono e por Memórias Eprom’s, conforme figura 6.

Em T1 o contador é zerado e em T4 a instrução é carregada no registrador de

instruções.

O bit MA11 = 1 indica que temos uma instrução de desvio condicional será

executada. E o bit MA4 indicará o estado do flag que estará sendo analisado. Pelas linhas

MA5 e MA6 estaremos selecionando o flag desejado.

MA5

0

0

1

1

MA6

0

1

0

1

Flag

/VAI-UM

IGUAL

/ZERO

SINAL

O Multiplexador foi colocado para minimizar os endereços redundantes

apresentados quando uma instrução de desvio for executada.

Sinais de controle:

- /RICARGA – Armazena o conteúdo do barramento de dados, no registrador de

instruções, na transição positiva do /CLOCK e quando T4 estiver ativo.

Figura 6 – Diagrama em blocos da Unidade de Controle

6.3 Memória

No circuito da Memória RAM é possível programá-la por meio de chaves. Assim é

possível o armazenamento de programas. Além disso temos 8 páginas de memórias que

podem ser selecionadas por meio de chaves.

Sinais de controle:

- MEMHAB – Habilita a memória

- MEML/E – Em nível alto temos leitura, onde o conteúdo do endereço

selecionado é transferido para o barramento de dados, caso contrário temos

escrita em memória, onde o conteúdo do barramento de dados é armazenado no

endereço indicado.

As linhas de endereço de A7 à A10 determinam as páginas de memória.

13

Figura 7 – Diagrama em blocos da Memória

6.4 Unidade Lógica Aritmética

A Unidade Lógica Aritmética, mostrada na fugura 8, é responsável em realizar as

diversas operações do processador.

Sinais de controle:

- /RACARGA – Habilita a transferência do conteúdo do barramento de dados

para o Acumulador, quando houver uma transição positiva do /CLOCK.

- /RBCARGA - Habilita a transferência do conteúdo do barramento de dados

para o Acumulador, quando houver uma transição positiva do /CLOCK.

- MODOULA – Define o modo (aritmético = 1 ou lógico = 0) de operação da

ULA.

- S0, S1, S2 – define o tipo de operação a ser realizada.

- /FLAG – Armazena o estado dos flags no registrador de flags.

- /UM – Define o carry-in.

- /ULALER – Habilita a transferência do resultado para barramento de dados.

Figura 8 – Diagrama em blocos da Unidade Lógica Aritmética

14

6.5 Registrador de Endereços

No Registrador de Endereços (figura 9) temos armazenado o conteúdo do Contador

de Programa.

Sinais de controle:

- /RECARGA – Habilita o armazenamento do dado no registrador.

- /RELER – Habilita a transferência do conteúdo armazenado para o barramento

de endereços.

Figura 9 – Diagrama em blocos do Registrador de Endereços

6.6 Contador de Programa e Apontador de Pilha

O Contador de Programa indica o endereço da próxima instrução a ser executada. O

Apontador de Pilha indica o endereço da pilha onde foi armazenado o valor do Contador de

Programa antes dele iniciar uma subrotina. Ele também é utilizado nas instruções de PUSH

e POP, onde os dados são armazenados e/ou retirados de uma pilha. Vide figura 10.

Sinais de controle:

- /CPCARGA – Carrega o contador com o dado do barramento de dados.

- CPHAB – Habilita a contagem.

- /CPLER – Habilita a transferência do dado do contador para o barramento de

dados.

- /LIMPA – O contador é zerado.

- /APCARGA - Carrega o apontador de pilha com dado do barramento de dados.

- APD/I – Habilita contagem crescente ou decrescente.

- /APLER – Habilita a transferência do dado do contador para o barramento de

dados.

15

Figura 10 - Diagrama em blocos do Contador de Programa e Apontador de Pilha

Baseado no resultado acima obtido, realizou-se um estudo de quais tipos e

especificações de componentes poderiam ser utilizados na elaboração da Unidade

Processadora Discreta Microprogramável.

Tendo todos os dados necessários para o detalhamento do diagrama dos circuitos

eletrônicos e utilizando-se a ferramenta TANGO, esquematizou-se todos os circuitos

necessários para o funcionamento da Unidade Processadora Discreta Microprogramável.

Os esquemas dos circuitos eletrônicos encontram-se no ANEXO A.

Na fase de simulação, utilizou-se a ferramenta MAXPLUS II. Simulou-se cada

circuito separadamente, controlando as linhas de controle manualmente.

Muitos problemas encontrados na simulação, foram corrigidos aperfeiçoando-se os

circuitos. Devido a correção de muitos erros na simulação, obteve-se uma maior facilidade

na montagem dos circuitos.

Encontrou-se problemas de atrasos provocados pelos componentes reais, que não

foram detectados durante a simulação, e que foram sanados com o estudo de outros

componentes que foram inseridos para correção dos erros reais.

Atualmente o protótipo encontra-se montado e em funcionamento, conforme

previsto. Foram realizados testes com a implementação das instruções a nível de

microprogramação.

6.7 Descrição simplificada dos integrados utilizados no projeto

6.7.1 Descrição do CI 74161 – Contador binário de 4 bits crescente préestabelecível

Figura 11 – Principais pinos do CI 74161

16

A, B, C, D

QA, QB,

QC, QD

CLK

CLR

LOAD

ENP, ENT

Entrada da contagem inicial

Saída da contagem

Entrada de clock ; sensível a transição positiva

Entrada de controle; ativa em nível lógico zero; quando

ativado leva as saídas a nível lógico zero; não depende do

clock

Entra de controle; ativo em nível lógico zero; quando

ativado desabilita a contagem e carrega as saídas com o

valor das entradas na transição positiva do clock

Entradas de controle; ativo em nível alto; ambas devem

estar ativadas para habilitar a contagem; ENT desativado

força a saída RCO para nível lógico zero

Tabela 1 – Descrição dos principais pinos do CI 74161

17

6.7.2 Descrição do CI 74191 – Contador de 4 bits crescente/decrescente préestabelecível sensível à transição positiva do clock

Figura 12 - Principais pinos do CI 74191

/CTEN

D/U

LOAD

MAX/MIN

/RCO

QA, QB,

QC, QD

A, B, C, D

entrada de controle; nível lógico zero habilita contagem; nível

lógico um desabilita a contagem; trocas de nível devem ser feitas

apenas quando a entrada de clock está em nível um

entrada de controle; nível lógico zero a contagem é crescente;

nível lógico um a contagem é decrescente; deve-se evitar troca de

nível enquanto o clock está em nível lógico zero

entrada de controle; nível lógico zero faz com que o dado de

entrada seja carregado na saída independente do clock

saída; produz nível lógico um com um período ciclo de clock

quando a contagem é 0000 ou 1111; é utilizado para permitir

“look - ahead”para operação alta velocidade

saída; produz um nível lógico zero com uma largura igual a

porção nível zero do clock quando a saída é 0000 ou 1111; é

utilizado para ligar dois mais contadores em cascata através de

CTEN ou CLK; poderá ocorrer um falso RCO se o clock e CTEN

são zero e D/U é um durante um pulso de LOAD

saída de contagem, 4 bits, flips-flops mestre escravo; muda de

estado na transição positiva do clock

entrada de dados; é carregado para a saída quando a entrada

LOAD vai para nível lógico zero

Tabela 2 – Descrição dos principais pinos do CI 74161

18

6.7.3 Descrição do CI 74173 – Registrador de 4 bits

Figura 13 - Principais pinos do CI 74173

D

Q

CLK

CLEAR

G1, G2

M, N

Entrada de dados

saída e dados

Entrada de clock; sensível a transição positiva

Entrada de controle; ativo em nível alto; limpa as saídas de

daos; não depende do clock

Entradas de seleção; o dado só será registrado ne transição

positiva do clock se estas duas entradas estiverem em nível

lógico zero

Entradas de controle; ativas em nível lógico um; se uma destas

entradas for para um, então as saídas Q irão para tree-state.

Tabela 3 – Descrição dos principais pinos do CI 74173

6.7.4 Descrição do CI 74157 – Multiplexador 2x1

Figura 14 - Principais pinos do CI 74157

19

Y

A

B

G

A/B

Saída de dados (4 bits)

Entrada de dados (4 bits)

Entrada de dados (4 bits)

Entrada de controle; ativo em nível baixo; responsável

pela seleção do chip; em nível alto força as saídas Y

para nível zero

Entrada de controle; seleciona qual entrada de dados

será aplicada na saída

Tabela 4 – Descrição dos principais pinos do CI 74157

6.7.5 Descrição do CI 74LS181 – Unidade Lógica Aritmética

Figura 15 - Principais pinos do CI 74181

A0 – A3

B0 – B3

S0 – S3

F0 – F3

Cn

Cn+4

A=B

M

Entrada de dados

Entrada de dados

a partir destas entradas seleciona-se as operações

Saídas de dados

Carry de entrada

Carry de saída

Indica o estado do carry de igualdade

Um nível lógico alto desabilita o carry interno

Tabela 5 – Descrição dos principais pinos do CI 74181

Os componentes utilizados têm seus dados descritos com mais detalhes nas folhas

de dados dos componentes no Anexo C.

6.8 Tabela de Instruções

Na Tabela 6 temos descritas as instruções desenvolvidas para o protótipo, bem

como seu código e sua descrição. No Anexo B apresenta-se com todas as palavras de

controle geradas pela Unidade de Controle por cada uma das instruções desenvolvidas.

20

Instrução

ADI, <valor>

SUBI, <valor>

INC A

DCR A

LDI <valor>

LDA <endereço>

STA <endereço>

ANI <dados>

ORI <dados>

XRI <dados>

XRA

CMA

JMP <endereço>

JZ <endereço>

JC <endereço>

JS <endereço>

JEQ <endereço>

JNZ <endereço>

JNC <endereço>

JNS <endereço>

JNEQ <endereço>

CALL endereço

RET

CMP <dado>

ADD <endereço>

SUBD <endereço>

INA

IND

OUTA

OUTD

HALT

Código

05

06

07

08

04

09

10

11

12

13

14

15

16

82

91

A7

E5

B3

C1

D6

F4

17

18

19

20

21

22

23

24

25

26

Descrição

A <- A + <valor>

A <- A - <valor>

A <- A + 1

A <- A - 1

A <- <valor>

A <- conteúdo do endereço

<endereço> <- conteúdo do acumulador

A <- A AND <dados>

A <- A OR <dados>

A <- A XOR <dados>

A <- A XOR A (zera o acumulador)

A <- complemento de A

PC <- endereço

se /ZERO = 0 PC <- endereço

se /VAI-UM = 0 PC <- endereço

se SINAL = 1 PC <- endereço

se IGUAL =1 PC <- endereço

se /ZERO =1 PC <- endereço

se /VAI-UM = 1 PC <- endereço

se SINAL = 0 PC <- endereço

se IGUAL = 0 PC <- endereço

PC <- endereço / AP <- PC

CP <- AP

compara A com <dado> e seta flag de igual se A = dado

A <- A + conteúdo do endereço

A <- A - conteúdo do endereço

A <- entrada analógica

A <- entrada digital

saída analógica <- A

saída digital <- A

Parada

Tabela 6 – Tabela de Instruções

21

6.9 Descrição dos sinais ativos durante o ciclo de busca

No ciclo de busca o código da instrução é carregado no Registrador de instruções

para que as microinstruções sejam executadas. A seguir descreve-se as fases do ciclo de

busca.

Primeira fase do ciclo busca, sinais ativos:

- /CPLER – o conteúdo do contador de programa é transferido para o barramento

de dados

- /RECARGA – o dado disponível no barramento de dados é carregado no

registrador de endereços

Segunda fase do ciclo busca, sinais ativos:

- CPHAB – o contador de programa é incrementado

Terceira fase do ciclo busca, sinais ativos:

- /RELER – o conteúdo armazenado no registrador de endereços é transferido

para o barramento de endereços

- MEMHAB – habilita a memória RAM para leitura, transferindo o conteúdo do

endereço disponibilizado para o barramento de dados (o conteúdo corresponde

ao código de uma instrução)

- /RICARGA – o dado é carregado no registrador de instruções

Após a execução do ciclo de busca executa-se as microinstruções da instrução

carregada no registrador de instruções.

Na Figura 16a, 16b, 16c é possível visualizar os sinais ativos do ciclo de busca a

cada ciclo de clock.

22

16a – Primeira fase do ciclo de busca

16b – Segunda fase do ciclo de busca

16c- Terceira fase do ciclo de busca

6.10 Descrição dos sinais ativos durante a instrução ADI <valor>

Na instrução ADI <valor> o valor indicado é imediatamente somado ao conteúdo

do acumulador. A seguir descreve-se as microinstruções executadas a cada ciclo de clock

da instrução ADI <valor>.

Primeira microinstrução da instrução ADI <valor>, sinais ativos:

- /CPLER – o conteúdo do contador de programa é transferido para o barramento

de dados

- /RECARGA – o dado disponível no barramento de dados é carregado no

registrador de endereços

23

Segunda microinstrução da instrução ADI <valor>, sinais ativos:

- /RELER – o conteúdo armazenado no registrador de endereços é transferido

para o barramento de endereços

- MEMHAB - habilita a memória RAM para leitura, transferindo o conteúdo do

endereço disponibilizado para o barramento de dados

- /RBCARGA – o dado disponível no barramento de dados é transferido para o

registrador B

Terceira microinstrução da instrução ADI <valor>, sinais ativos:

- S0, S1, S2, S3 – são setados para realizar a operação de soma, que corresponde

ao código 9 em binário, ou seja 1001

- /MODOULA – modo de operação da ULA (1 – Lógico e 0 – Aritmético)

- /FLAG – armazena-se no registrador de flags o estados destes ao realizar a

operação

Quarta microinstrução da instrução ADI <valor>, sinais ativos:

- S0, S1, S2, S3 – são setados para realizar a operação de soma, que corresponde

ao código 9 em binário, ou seja 1001

- /MODOULA – modo de operação da ULA (1 – Lógico e 0 – Aritmético)

- /ULALER – o resultado da operação é transferido para o barramento de dados

- /RACARGA – armazena-se no acumulador o resultado da operação

Quinta microinstrução da instrução ADI <valor>, sinais ativos:

- CPHAB – o contador de programa é incrementado

Sexta microinstrução da instrução ADI <valor>, sinais ativos:

- FIM – finalização da instrução, início de um novo ciclo de busca

Na Figura 17a, 17b, 17c, 17d, 17e é possível visualizar os sinais ativos da instrução

ADI <valor>.

24

17a – Primeira microinstrução da instrução ADI <valor>

17b – Primeira microinstrução da instrução ADI <valor>

17c – Segunda microinstrução da instrução ADI <valor>

17d – Terceira microinstrução da instrução ADI <valor>

17e – Quarta microinstrução da instrução ADI <valor>

25

6.11 Descrição dos sinais ativos durante a instrução LDA <endereço>

Na instrução LDA <endereço>, o conteúdo pertencente ao endereço especificado é

transferido para o acumulador. A seguir descrevemos as microinstruções executadas a cada

ciclo de clock da instrução LDA <endereço>.

Primeira microinstrução da instrução LDA <endereço>, sinais ativos:

- /CPLER – o conteúdo do contador de programa é transferido para o barramento

de dados

- /RECARGA – o dado disponível no barramento de dados é carregado no

registrador de endereços

Segunda microinstrução da instrução LDA <endereço>, sinais ativos:

- /RELER – o conteúdo armazenado no registrador de endereços é transferido

para o barramento de endereços

- MEMHAB - habilita a memória RAM para leitura, transferindo o conteúdo do

endereço disponibilizado para o barramento de dados

- /RECARGA – o dado disponível no barramento de dados é carregado no

registrador de endereços

Terceira microinstrução da instrução LDA <endereço>, sinais ativos:

- /RELER – o conteúdo armazenado no registrador de endereços é transferido

para o barramento de endereços

- MEMHAB - habilita a memória RAM para leitura, transferindo o conteúdo do

endereço disponibilizado para o barramento de dados

- /RACARGA – o dado disponível no barramento de dados é carregado no

acumulador

Quarta microinstrução da instrução LDA <endereço>, sinais ativos:

- CPHAB – o contador de programa é incrementado

Quinta microinstrução da instrução LDA <endereço>, sinais ativos:

- FIM – finalização da instrução, início de um novo ciclo de busca

Na Figura 18a, 18b, 18c, 18d é possível visualizar os sinais ativos da instrução

LDA <endereço>.

26

18a – Primeira microinstrução da instrução LDA <endereço>

18b – Segunda microinstrução da instrução LDA <endereço>

18c – Terceira microinstrução da instrução LDA <endereço>

18d – Quarta microinstrução da instrução LDA <endereço>

6.12 Descrição dos sinais ativos durante a instrução STA <endereço>

Na instrução STA <endereço>, o conteúdo do acumulador é transferido para o

endereço especificado. A seguir descrevemos as microinstruções executadas a cada ciclo

de clock da instrução STA <endereço>.

Primeira microinstrução da instrução STA <endereço>, sinais ativos:

- /CPLER – o conteúdo do contador de programa é transferido para o barramento

de dados

- /RECARGA – o dado disponível no barramento de dados é carregado no

registrador de endereços

27

Segunda microinstrução da instrução STA <endereço>, sinais ativos:

- /RELER – o conteúdo armazenado no registrador de endereços é transferido

para o barramento de endereços

- MEMHAB - habilita a memória RAM para leitura, transferindo o conteúdo do

endereço disponibilizado para o barramento de dados

- /RECARGA – o dado disponível no barramento de dados é carregado no

registrador de endereços

Terceira microinstrução da instrução STA <endereço>, sinais ativos:

- /RELER – o conteúdo armazenado no registrador de endereços é transferido

para o barramento de endereços

- /RALER – disponibiliza o conteúdo do acumulador para o barramento de dados

- MEMHAB - habilita a memória RAM

- MEML/E – habilita a memória TAM para escrita

Quarta microinstrução da instrução STA <endereço>, sinais ativos:

- CPHAB – o contador de programa é incrementado

Quinta microinstrução da instrução STA <endereço>, sinais ativos:

- FIM – finalização da instrução, início de um novo ciclo de busca

Na Figura 19a, 19b, 19c, 19d é possível visualizar os sinais ativos da instrução STA

<endereço>.

28

19a – Primeira microinstrução da instrução STA <endereço>

19b – Segunda microinstrução da instrução STA <endereço>

19c – Terceira microinstrução da instrução STA <endereço>

19d – Quarta microinstrução da instrução STA <endereço>

6.13 Descrição dos sinais ativos durante a instrução SUBI <valor>

Na instrução SUBI <valor>, temos o conteúdo pertencente ao acumulador

subtraído ao valor especificado. Na Tabela 7 temos os sinais ativos em cada microinstrução

da instrução SUBI <valor>.

1a

2a

3a

/CPLER

/RELER

S0...S3 = 6

/RECARGA MEMHAB MODOULA = 0

/RBCARGA /FLAG

/UM

4a

5a

6a

S0...S3 =6

CPHAB FIM

MODOULA = 0

/ULALER

/RACARGA

/UM

Tabela 7 – Sinais ativos das microinstruções da instrução SUBI <valor>

29

6.14 Descrição dos sinais ativos durante a instrução INC A

Na instrução INC A temos o conteúdo pertencente ao acumulador incrementado de

1. Na Tabela 8 temos os sinais ativos em cada microinstrução da instrução INC A.

1a

2a

3a

S0...S3 = 0 S0...S3 = 0 FIM

/UM

/UM

/FLAG

/ULALER

/RACARGA

Tabela 8 – Sinais ativos das microinstruções da instrução INC A

6.15 Descrição dos sinais ativos durante a instrução DCR A

Na instrução DCR A temos o conteúdo pertencente ao acumulador decrementado

de 1. Na Tabela 9 temos os sinais ativos em cada microinstrução da instrução INC A.

2a

3a

1a

S0...S3 = 15 S0...S3 = 15 FIM

/FLAG

/ULALER

/RACARGA

Tabela 9 – Sinais ativos das microinstruções da instrução DCR A

6.16 Descrição dos sinais ativos durante a instrução LDI <valor>

Na instrução LDI <valor> o valor especificado transferido para o acumulador. Na

Tabela 10 temos os sinais ativos em cada microinstrução da instrução LDI <valor>.

1a

2a

3a

4a

/CPLER

/RELER

CPHAB FIM

/RECARGA MEMHAB

/RACARGA

Tabela 10 – Sinais ativos das microinstruções da instrução LDI <valor>

6.17 Descrição dos sinais ativos durante a instrução ANI <dado>

Na instrução ANI <dado> realiza-se a operação lógica E com o conteúdo do

acumulador e o dado especificado. Na Tabela 11 temos os sinais ativos em cada

microinstrução da instrução ANI <dado>.

1a

2a

3a

4a

5a

6a

/CPLER

/RELER

S0...S3 = 11

S0...S3 = 11

CPHAB FIM

/RECARGA MEMHAB MODOULA = 1 MODOULA = 1

/RBCARGA /FLAG

/ULALER

/RACARGA

Tabela 11 - Sinais ativos das microinstruções da instrução ANI <dado>

30

6.18 Descrição dos sinais ativos durante a instrução ORI <dado>

Na instrução ORI <dado> realiza-se a operação lógica OU com o conteúdo do

acumulador e o dado especificado. Na Tabela 12 temos os sinais ativos em cada

microinstrução da instrução ORI <dado>.

1a

2a

3a

4a

5a

6a

/CPLER

/RELER

S0...S3 = 14

S0...S3 = 14

CPHAB FIM

/RECARGA MEMHAB MODOULA = 1 MODOULA = 1

/RBCARGA /FLAG

/ULALER

/RACARGA

Tabela 12 – Sinais ativos das microinstruções da instrução ORI <dado>

6.19 Descrição dos sinais ativos durante a instrução XRI <dado>

Na instrução XRI <dado> realiza-se a operação lógica XOR com o conteúdo do

acumulador e o dado especificado. Na Tabela 13 temos os sinais ativos em cada

microinstrução da instrução XRI <dado>.

1a

2a

3a

4a

5a

6a

/CPLER

/RELER

S0...S3 = 6

S0...S3 = 6

CPHAB FIM

/RECARGA MEMHAB MODOULA = 1 MODOULA = 1

/RBCARGA /FLAG

/ULALER

/RACARGA

Tabela 13 – Sinais ativos das microinstruções da instrução XRI <dado>

6.20 Descrição dos sinais ativos durante a instrução XRA

Na instrução XRA realiza-se a operação lógica XOR com o conteúdo do

acumulador e seu próprio conteúdo, ou seja o conteúdo do acumulador é zerado. Na Tabela

14 temos os sinais ativos em cada microinstrução da instrução XRI <dado>.

1a

2a

3a

4a

/RALER

S0...S3 = 6

S0...S3 = 6

FIM

/RBCARGA MODOULA = 1 MODOULA = 1

/FLAG

/ULALER

/RACARGA

Tabela 14 – Sinais ativos das microinstruções da instrução XRA

6.21 Descrição dos sinais ativos durante a instrução CMA

Na instrução CMA, o conteúdo do acumulador é complementado. Na Tabela 15

temos os sinais ativos em cada microinstrução da instrução CMA.

31

1a

3a

4a

S0...S3 = 0

S0...S3 = 0

FIM

MODOULA = 1 MODOULA = 1

/FLAG

/ULALER

/RACARGA

Tabela 15 – Sinais ativos das microinstruções da instrução CMA

6.22 Descrição dos sinais ativos durante a instrução JMP <endereço>

Na instrução JMP <endereço> temos um salto incondicional. Na Tabela 16 temos

os sinais ativos em cada microinstrução da instrução JMP <endereço>.

1a

2a

3a

/CPLER

/RELER

FIM

/RECARGA MEMHAB

/CPCARGA

Tabela 16 – Sinais ativos das microinstruções da instrução JMP <endereço>

6.23 Descrição dos sinais ativos durante a instrução JZ, JC, JS, JEQ <endereço>

Na instrução JZ <endereço> temos um salto condicional. Se o flag /ZERO = 0

teremos o salto para o endereço especificado, ou seja, o contador de programa passa a

executar a instrução que estará no endereço especificado, caso contrário, se /ZERO = 1 o

contador de programa será incrementado executando a próxima instrução. Na Tabela 17 e

18 temos os sinais ativos em cada microinstrução da instrução JZ <endereço>.

1a

2a

3a

/CPLER

/RELER

FIM

/RECARGA MEMHAB

/CPCARGA

Tabela 17 – Sinais ativos das microinstruções da instrução JZ <endereço>,

se o flag /ZERO = 0

1a

2a

CPHAB FIM

Tabela 18 – Sinais ativos das microinstruções da instrução JZ <endereço>,

se o flag /ZERO = 1

Na instrução JC <endereço> (flag /VAI-UM) teremos as mesmos sinais ativos da

Tabela 17 se o flag /VAI-UM = 0 e a próxima instrução a ser executada estará no endereço

especificado. Teremos os sinais ativos da Tabela 18 se o flag /VAI-UM = 1, onde a

próxima instrução a ser executada será o próximo endereço do contador de programa.

Na instrução JS <endereço> (flag de SINAL) teremos os sinais ativos da Tabela 17

se o flag SINAL = 1, e o salto para o endereço especificado ocorrerá, caso contrário, se

SINAL = 0 teremos os sinais ativos descrita na Tabela 18, observando que o salto não

ocorrerá.

Na instrução JEQ <endereço> (flag IGUAL) teremos os sinais ativos da Tabela 17

se o flag IGUAL =1, ocorrendo o salto para o endereço especificado, caso contrário, se o

32

flag IGUAL = 0 teremos os sinais ativos descrita na Tabela 18, observando que o salto não

ocorrerá. Para a instrução JEQ <endereço> deve-se primeiro realizar a instrução CMP

<dado>, ou seja deve haver uma comparação entre dois dados para que o flag IGUAL seja

ativado.

6.24 Descrição dos sinais ativos durante a instrução CALL <endereço>

Na instrução CALL <endereço> teremos uma chamada a uma subrotina. O

endereço apontado pelo contador de programa é armazenado na pilha e a próxima instrução

a ser executada estará no endereço especificado. Na Tabela 19 temos os sinais ativos em

cada microinstrução da instrução CALL <endereço>.

1a

2a

3a

4a

5a

6a

7a

/APHAB /APLER

/RELER

/CPLER

/RELER

/APHAB FIM

/RECARGA /CPLER

/RECARGA MEMHAB

MEMHAB

/CPCARGA

MEML/E

Tabela 19 – Sinais ativos das microinstruções da instrução CALL <endereço>

6.25 Descrição dos sinais ativos durante a instrução RET

Na instrução RET teremos o retorno ao programa principal. O endereço

armazenado na pilha quando executa-se a instrução CALL <endereço> retorna ao

contador de programa, assim teremos o retorno ao programa principal. Na Tabela 20 temos

os sinais ativos em cada microinstrução da instrução RET.

1a

2a

3a

4a

5a

/APHAB /APLER

/RELER

/CPHAB FIM

APD/I = 0 /RECARGA MEMHAB

/CPCARGA

Tabela 20 – Sinais ativos das microinstruções da instrução RET

6.26 Descrição dos sinais ativos durante a instrução CMP <dado>

Na instrução CMP <dado> teremos o conteúdo do acumulador sendo comparado

com o dado especificado. Na realidade teremos uma subtração sendo executada. O objetivo

desta instrução é setar o flag IGUAL se o resultado da operação é igual a zero. Na Tabela

21 temos os sinais ativos em cada microinstrução da instrução CMP <dados>.

1a

2a

3a

4a

5a

/CPLER

/RELER

S0...S3 = 6 /CPHAB FIM

/RECARGA MEMHAB /FLAG

/RBCARGA

Tabela 21 – Sinais ativos das microinstruções da instrução CMP <dados>

33

6.27 Descrição dos sinais ativos durante a instrução ADD <endereço>

Na instrução ADD <endereço> teremos o conteúdo do acumulador somada com o

conteúdo do endereço especificado, colocando-se o resultado no acumulador. Na Tabela 22

temos os sinais ativos em cada microinstrução da instrução ADD <endereço>.

1a

2a

3a

4a

5a

6a

7a

/CPLER

/RELER

/RELER

S0...S3 = 9

S0...S3 = 9

CPHAB FIM

/RECARGA MEMHAB MEMHAB MODOULA=0 MODOULA=0

/RECARGA /RBCARGA /FLAG

/ULALER

/RACARGA

Tabela 22 – Sinais ativos das microinstruções da instrução ADD <endereço>

6.28 Descrição dos sinais ativos durante a instrução SUB <endereço>

Na instrução SUB <endereço> teremos o conteúdo do acumulador subtraída do

conteúdo do endereço especificado, colocando-se o resultado no acumulador. Na Tabela 23

temos os sinais ativos em cada microinstrução da instrução SUB <endereço>

1a

2a

3a

4a

5a

6a

7a

/CPLER

/RELER

/RELER

S0...S3 = 6

S0...S3 = 6

CPHAB FIM

/RECARGA MEMHAB MEMHAB MODOULA=0 MODOULA=0

/RECARGA /RBCARGA /FLAG

/ULALER

/RACARGA

Tabela 23 – Sinais ativos das microinstruções da instrução ADD <endereço>

6.29 Descrição dos sinais ativos durante a instrução INA

Na instrução INA teremos a leitura do dado da entrada analógica e armazenado no

acumulador. Na Tabela 24 temos os sinais ativos em cada microinstrução da instrução

INA.

1a

2a

/BEALER

FIM

/RACARGA

Tabela 24 – Sinais ativos das microinstruções da instrução INA

6.30 Descrição dos sinais ativos durante a instrução IND

Na instrução IND teremos a leitura do dado da entrada digital e armazenado no

acumulador. Na Tabela 25 temos os sinais ativos em cada microinstrução da instrução

IND.

1a

2a

/BEDLER

FIM

/RACARGA

Tabela 25 – Sinais ativos das microinstruções da instrução IND

34

6.31 Descrição dos sinais ativos durante a instrução OUTA

Na instrução OUTA teremos o conteúdo do acumulador transferido para a saída

analógica. Na Tabela 26 temos os sinais ativos em cada microinstrução da instrução

OUTA.

1a

2a

/RALER

FIM

/RSACARGA

Tabela 26 – Sinais ativos das microinstruções da instrução OUTA

6.32 Descrição dos sinais ativos durante a instrução OUTD

Na instrução OUTD teremos o conteúdo do acumulador transferido para a saída

digital. Na Tabela 27 temos os sinais ativos em cada microinstrução da instrução OUTD.

1a

2a

/RALER

FIM

/RSDCARGA

Tabela 27 – Sinais ativos das microinstruções da instrução OUTD

6.33 Descrição dos sinais ativos durante a instrução HALT

Na instrução HALT teremos o clock interrompido. Na Tabela 28 temos os sinais

ativos em cada microinstrução da instrução halt.

1a

/PARAR

Tabela 28 – Sinais ativos das microinstruções da instrução HALT

6.34 Descrição dos sinais ativos durante a instrução PUSH

Na instrução PUSH teremos o conteúdo do acumulador transferido para o endereço

indicado pelo Apontador de Pilha. Na Tabela 29 temos os sinais ativos em cada

microinstrução da instrução push.

1a

/APHAB

2a

/APLER

/RECARGA

3a

/RELER

MEMHAB

MEML/E = 0

/RALER

4a

FIM

Tabela 29 – Sinais ativos das microinstruções da instrução PUSH

6.35 Descrição dos sinais ativos durante a instrução POP

Na instrução POP teremos o conteúdo do endereço apontado pelo Apontador de

Pilha transferido para o acumulador. Na Tabela 30 temos os sinais ativos em cada

microinstrução da instrução pop.

35

1a

/APLER

/RECARGA

2a

/RELER

MEMHAB

MEML/E = 1

/RACARGA

3a

/APHAB

APD/I = 1

4a

FIM

Tabela 30 – Sinais ativos das microinstruções da instrução POP

36

7 Referências Bibliográficas

STALLINGS, WILLIAM. Computer Organization and Architecture – Designing for

Performance. Fourth Edition. Prentice Hall, 1996.

HENNESSY, J. L. & PATTERSON, D. A. Computer Organization and Design – The

Hardware/Software Interface. Second Edition. Morgan Kaufmann Publishers, Inc,

1998.

PATTERSON, D. A. & HENNESSY, J. L. Computer Architecture a Quantitative

Approach. Second Edition. Morgan Kaufmann Publishers, Inc, 1990,1996.

TOKHEIM, L. R. Introdução aos Microprocessadores. MacGraw-Hill do Brasil, São

Paulo, 1985.

ZUFFO, João Antônio. Fundamentos da Arquitetura e Organização

Microprocessadores. Editora Edgard Blucher Ltda, São Paulo, 1978.

dos

ZUFFO, João Antônio. Microprocessadores: Dutos de Sistema, Técnicas de Interface e

Sistemas de Comunicação de Dados. Editora Edgard Blucher Ltda, São Paulo, 1981.

TAUB, Herbert. Circuitos Digitais e Microprocessadores. Editora McGraw-Hill, São

Paulo, 1984.

LANGDON Jr, G. G. e FREGNI, E. Projeto de Computadores Digitais. Edgard Blucher

Ltda, 1990.

MALVINO, A. Microcomputadores e Microprocessadores. McGraw-Hill, São Paulo,

1986.

TANEMBAUM, A. S. Organização Estruturada de Computadores. Prentice Hall do Brasil,

São Paulo, 1984.

HAYES, John P. Computer Architecture and Organization. McGraw-Hill, São Paulo,

1988.

37