Autarquia Educacional do Vale do São Francisco – AEVSF

Faculdade de Ciências Aplicadas e Sociais de Petrolina – FACAPE

Ciência da Computação

Arquitetura e Organização de Computadores

Prof. Sérgio F. Ribeiro

Lista de Exercícios 2

Obs.: Para as questões a seguir, considere, como referência, a Microarquitetura IJVM Mic-1.

1o) Descreva, resumidamente, de quais fatores depende o projeto do Nível da Microarquitetura.

2o) Qual a composição básica e quais as funcionalidades dos elementos que formam o Mic-1 (Figura 2)?

3o) Um registrador pode ser lido e escrito no mesmo ciclo de clock sem produzir lixo? Por que?

4o) Descreva o que ocorre durante cada subciclo em um ciclo do caminho de dados.

5o) Cite todos os pares de registradores do MIC-1 para tratar dados, endereços e microinstruções.

Diferencie-os.

6o) Qual o objetivo de uma microinstrução? Descreva a função dos sinais que compõem uma palavra de

controle (microinstrução)?

7o) O fato de o MAR trabalhar com palavras enquanto a memória física trabalha com bytes é suportado

por um artifício muito interessante. Explique.

8o) Como a arquitetura IJVM divide a memória? Caracterize cada uma das partes.

F0 F1 ENA ENB INVA INC FUNÇÃO

0 1

1

0

0

0 A

0 1

0

1

0

0 B

0 1

1

0

1

0 A

1 0

1

1

0

0 B

1 1

1

1

0

0 A+B

1 1

1

1

0

1 A+B+1

1 1

1

0

0

1 A+1

1 1

0

1

0

1 B+1

1 1

1

1

1

1 B–A

1 1

0

1

1

0 B–1

1 1

1

0

1

1 –A

0 0

1

1

0

0 A AND B

0 1

1

1

0

0 A OR B

0 1

0

0

0

0 0

0 1

0

0

0

1 1

0 1

0

0

1

0 –1

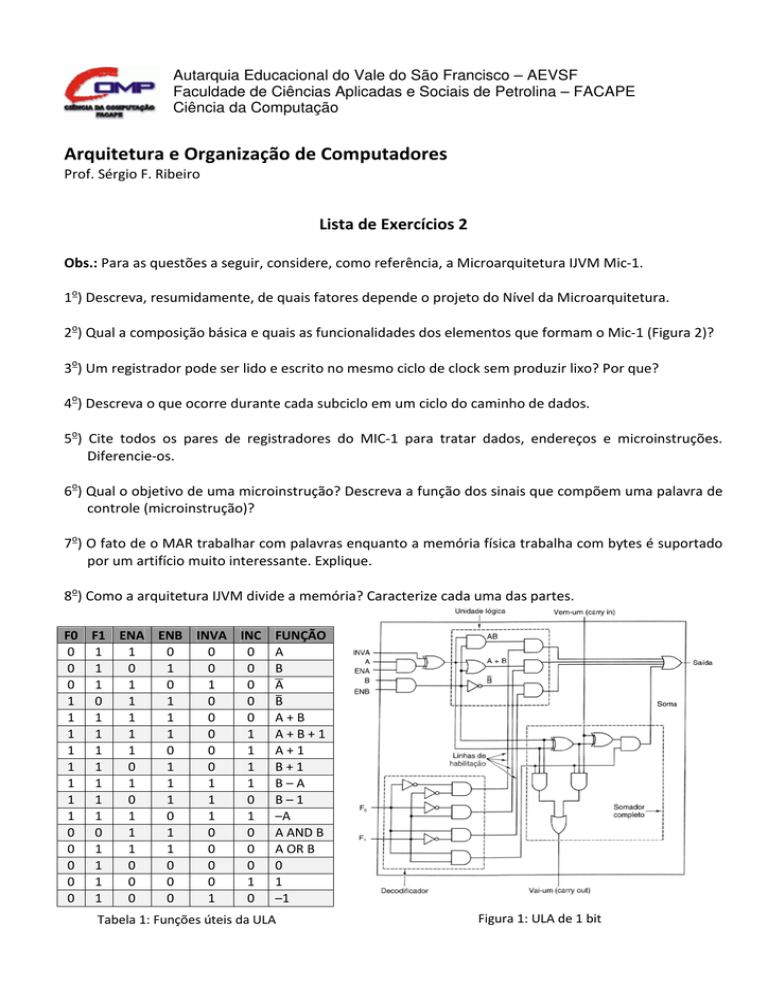

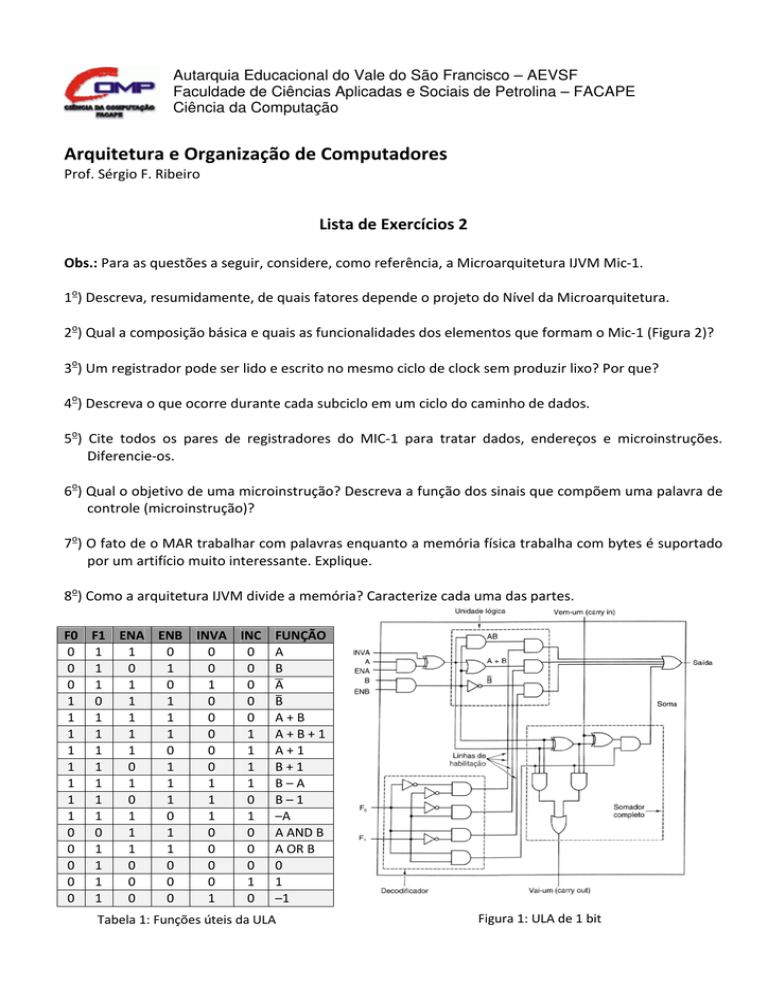

Tabela 1: Funções úteis da ULA

Figura 1: ULA de 1 bit

Figura 2: Diagrama de blocos do MIC-1

9o) A Tabela 1 mostra uma maneira de fazer com que A apareça na saída da ULA. Sabendo que cada uma

das 32 ULA de 1 bit é implementado conforme a Figura 1, determine outra combinação binária que

desempenhe a mesma função.

10o) Com base no diagrama da Figura 1, demonstre qual função a ULA deve desempenhar quando:

F0 F1 ENA ENB INVA INC

1 1

0

1

1

1

11o) Após implementar o MIC-1 em laboratório (Figura 2), você mede os tempos de propagação do

circuito e averígua que o mesmo gasta 1ns para carregar o MIR, 1ns para habilitar um registrador

para que este coloque seu conteúdo no barramento B, 3ns aguardando a operação da ULA e do

deslocador, e 1ns para que os resultados se propaguem de volta aos registradores. Se o intervalo

alto do clock não pode ser inferior a 2ns para que o sequenciador funcione corretamente, determine

a máxima frequência de clock com que seu microprocessador será capaz de operar (despreze os

tempos de transição de borda). Justifique sua resposta através de um diagrama de tempo indicando

cada intervalo da temporização.

12o) Na Figura 2 o campo da microinstrução que controla o acesso ao barramento B está codificado em

4 bits. Mas o campo do barramento C é controlado por um mapa de bits (cada sinal de controle é

representado por um bit da microinstrução). Explique por quê.

13o) Quando o campo JMPC de uma microinstrução é habilitado, o conteúdo do MBR passa pela função

OR (caixa com um círculo) junto com o campo NEXT_ADDRESS para formar o endereço da próxima

microinstrução. Existe alguma circunstância na qual faz sentido o campo NEXT_ADDRESS ser igual a

0x1FF e usar JMPC?

14o) Determine o código em linguagem de montagem resultante da compilação do código Java abaixo.

Assuma que o compilador utilizado otimiza o código gerado.

i = j + k;

if (i==3)

i = 0;

k = 0;

else

j = j – 1;

15o) Considere o seguinte comando Java: i = j + k + 4; Encontre duas traduções diferentes

desse comando para a linguagem de montagem do IJVM.

16o) Encontre o comando Java que produziu o seguinte código IJVM:

ILOAD j

ILOAD k

ISUB

BIPUSH 6

ISUB

DUP

IADD

ISTORE i

17o) Ao traduzir o comando MAL

if(Z) goto L1; else goto L2

para binário, L2 deve estar nas 256 palavras mais baixas da memória de controle. Seria igualmente

possível L1 estar, digamos, em 0x40 e L2 em 0x140? Justifique sua resposta.

18o) Quanto tempo demora para que uma implementação do MIC-1 rodando a 200 MHz execute o

comando Java abaixo? (a resposta deve ser dada em nanossegundos).

i = j + k;

19o) Considere que a palavra de memória seja de 32 bits e que SP = 0x215 e PC = 0x100 (endereço da 1ª

instrução bipush). Apresente as microinstruções necessárias para a execução do programa IJVM

abaixo. Uma vez executado o programa, mostre o conteúdo dos registradores envolvidos e as

alterações na pilha a cada passo. Considere que a ordenação dos bytes na memória seja do tipo

Little Endian.

BIPUSH 0x42

BIPUSH 0x25

SWAP

IAND

IFEQ 0x0123

Obs: consulte o microprograma para o MIC-1 no livro-texto (Tanenbaum – fig. 4.17)