Projeto de um Processador RISC Dedicado a

Aplicações Multimídia

Dulcinéia Oliveira da Penha 1, Milene Barbosa Carvalho2, Carlos Augusto P. S. Martins3

Laboratório de Sistemas Digitais e Computacionais (LSDC) - Instituto de Informática

Pontificia Universidade Católica de Minas Gerais

Av. Dom José Gaspar, 500- Coração Eucarístico - CEP 30535-610

Belo Horizonte - Minas Gerais

{[email protected]}1 - { [email protected]} 2 - { [email protected]} 3

processador proposto possibilitaria a análise, através de

simulações, de técnicas usadas atualmente em vários

processadores. O estudo do paralelismo subword através da

monografia determinou o tipo do processador: um

Processador RISC Dedicado a Aplicações Multimídia. Este

processador implementaria paralelismo subword e as

aplicações multimídia foram escolhidas pelas características

de seus dados, forma como os mesmos são manipulados e

possibilidades de uso de paralelismo.

O objetivo do trabalho foi projetar um microprocessador

dedicado a aplicações multimídia e realizar sua validação

através de simulação funcional. Outro objetivo era a

aplicação prática de paralelismo subword. Uma vez que o

projeto foi desenvolvido dentro de uma disciplina de

graduação, não foi objetivo desenvolver um processador

com características comerciais, que competisse com os

processadores atuais disponíveis no mercado.

O processador apresenta uma série de limitações devido

aos fatores anteriormente citados. Não são propostas novas

técnicas e/ou tecnologias, somente foram aplicadas técnicas

presentes nos processadores comerciais [LEE 96][RAM 00]

[TER 96]. Outras limitações foram impostas pelo tipo de

simulação proposta e pelo tempo reduzido para a

implementação do simulador.

ResumoEste trabalho apresenta um processador RISC dedicado a

aplicações multimídia, projetado em uma disciplina de

graduação. Para validação do processador foi implementado

um simulador funcional c, ao longo do trabalho, os resultados

da validação são apresentados c discutidos.

Palavras-chav~ Processador multimídia, Processador

com conjunto de instruções de aplicação específica,

Computador com conjunto de instruções reduzido.

AbstractThis work presents the project of a RISC ASIP

Multimedia proccssor in ISA levei, dcvcloped in onc

graduation discipline. This processor is validatcd through the

implemcntation of a functional simulator and validation

rcsults are prescntcd and argucd.

Keyword~'-- Multimcdia proccssor, Application spccific

instruction sct proccssor, Rcduccd instruction sct computcr.

I.

INTRODUÇÃO

Esse artigo apresenta um microprocessador RISC

(Reduced lnstruction Set Computer) dedicado a aplicações

multimídia, desenvolvido na disciplina Arquitetura de

Computadores [ARQ OI][TAN 98] do Curso de Ciência da

Computação da Pontifícia Universidade Católica de Minas

Gerais, no segundo semestre de 2000. Nesta disciplina foi

proposto o projeto de um processador no nível ISA

(/nstruction Set Architecture) e, para sua validação, a

implementação de um simulador funcional do processador.

Na mesma disciplina foi proposta uma pesquisa para o

desenvolvimento de uma monografia sobre tema relativo a

qualquer assunto da área de Arquitetura de Computadores.

Durante o curso, foi apresentada a teoria de paralelismo,

mas não de forma prática. Além disso, algumas formas de

paralelismo não foram estudadas detalhadamente. Surgiu

então o interesse em fazer uma pesquisa sobre alguns tipos

de paralelismo expostos em sala de aula. Desse modo, o

tema da monografia foi "Paralelismo" [HW A 97].

O tema da monografia influenciou no projeto do

processador: um RISC, com conjunto de instruções de

aplicação específica (ASIP - App/ication Specijic

Instruction set Processor). A aplicação de paralelismo no

11. PROPOSTA DO PROCESSADOR

O processador projetado [SIM OI] é um RISC, seguindo

a tendência dos processadores atuais. Um dos princípios de

projeto RISC [HEN 96][TAN 98], sugere que apenas

instruções do tipo Load e Store acessem a memória. Assim,

no processador projetado, somente as instruções de

transferência de dados entre memória e processador

acessam a memória, como pode ser observado na Tabela I.

Essa tabela, apresenta algumas instruções do processador

proposto que serão descritas no decorrer da apresentação do

processador. Como podem ser observadas nesta tabela, as

únicas instruções que acessam a memória são LOAD e

STO. A primeira carrega no registrador, que é o primeiro

operando, a palavra armazenada no endereço de memória

indicado pelo conteúdo do registrador que é o segundo

150

operando. Já a segunda armazena na posição de memória

indicada pelo primeiro registrador o conteúdo do segundo.

As instruções anteriormente descritas usam modo de

endereçamento indireto, no qual o endereço da posição da

memória a ser acessada está armazenado no registrador que

é operando da instrução. ·Além do indireto, no processador

proposto ainda são usados os endereçamentos por

registrador e imediato. O primeiro tem como operandos

registradores contendo os dados que serão manipulados

pelas instruções aritméticas, lógicas e de deslocamento. O

segundo tem como operandos os dados que serão usados

nas instruções de transferência de dados imediata, nas

instruções de desvio e de sub-rotina.

O processador possui 32 registradores de propósito

geral que são usados como operandos das instruções. Além

dos registradores de propósito geral, o processador ainda

possui registradores específicos: um registrador de

instruções (IR - lnstruction Register), um registrador de

pilha (SP - Stack Pointer), um contador de programa (PC Program Counter) e 4 registradores de jlag: Carry, Zero,

Sinal e Paridade. Estes possuem seus valores alterados

quando são executadas instruções lógicas ou aritméticas,

que serão descritas posteriormente. O registrador de

instruções contém a instrução que "está sendo executada", o

contador de programa contém o endereço da próxima

instrução a ser executada e o registrador de pilha indica o

endereço do topo da pilha de memória.

A pilha de memória é usada para armazenar os

endereços de retomo das sub-rotinas. Para implementá-las,

o processador projetado possui as instruções CALL e RET.

A primei ra possui como operando o endereço de memória

do início da sub-rotina. Quando essa instrução é executada,

o endereço contido em PC é armazenado na pilha, SP é

decrementado e o endereço operando é colocado em PC.

Quando uma instrução RET é executada, o endereço que

está no topo da pilha é carregado no contador de programa.

A memória possui 65536 células de 64-bits, sendo

necessários então, 16 bits para endereçá-la. Assim, as

instruções que têm como operandos endereços de memória,

utilizam apenas os últimos 16 bits do operando. Uma

instrução é constituída de seu opcode e seus operandos

quando esses últimos existirem. Esse formato determina o

tamanho das instruções, que é de 27-bits. O tamanho da

memória pode ser facilmente alterado, acarretando apenas

modificação do tamanho das instruções.

Aplicações multimídia geralmente utilizam dados

inteiros pequenos, assim o processador, que é um ASIP

multimídia, manipula dados de 8-, 16- ou 32-bits. Outra

característica destas aplicações é a presença de laços de

repetição. Nesses laços, uma mesma instrução é executada

sobre uma grande quantidade de dados. Uma técnica usada

para acelerar a execução de aplicações com laços desse

tipo, é o paralelismo SIMD (Single-/nstruction MultipleData) [FLY 72], onde uma mesma operação é efetuada em

mais de um dado simultaneamente. Para implementar o

paralelismo SIMD no processador projetado foi aplicado o

paralelismo subword.

O paralelismo subword consiste em "empacotar" dois

ou mais dados de tamanho menor que o da palavra do

processador (subword) em "pacotes" de tamanho igual ao

da palavra do processador e depois processá-los como se

fosse uma palavra [LEE 96]. Para que isso seja possível, os

registradores devem possuir tamanho superior ao tamanho

dos dados manipulados e a ALU (Arithmetic Logic Unit)

deve ser diferenciada para operar os subwords em paralelo.

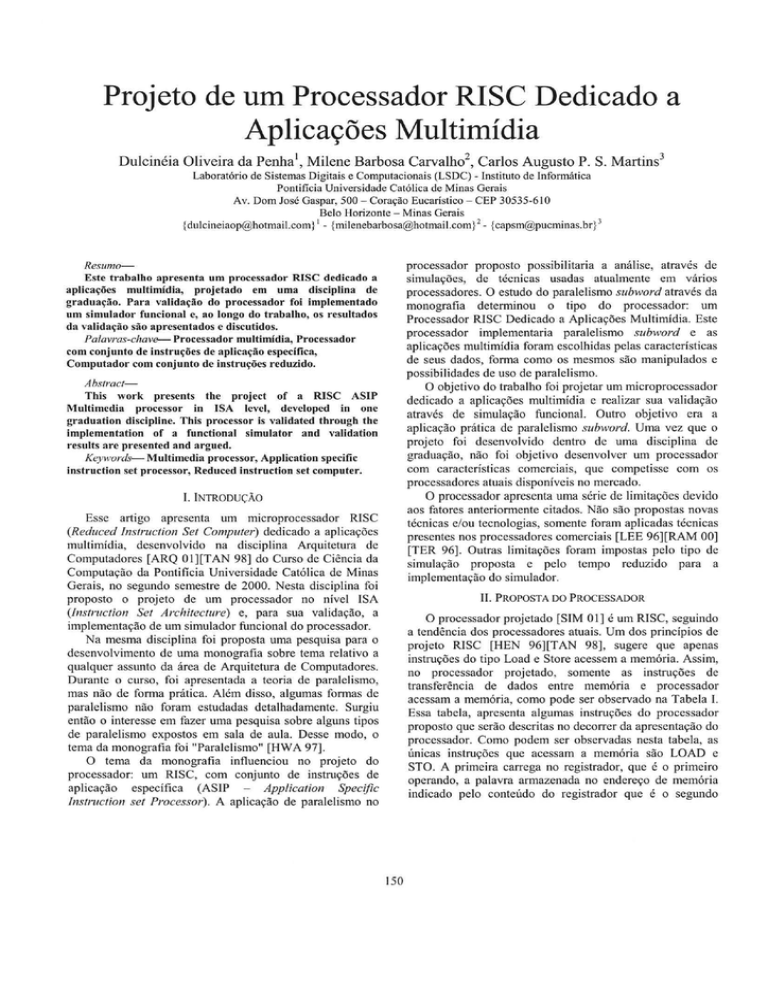

Assim, os 32 registradores de propósito-geral do

processador projetado têm largura de 64-bits, permitindo à

ALU manipular simultaneamente 2 dados de 32-bits, ou 4

dados de 16-bits, ou ainda 8 dados de 8-bits (a Figura I

apresenta registradores de propósito geral com dados de 16,bits). É necessário então, que se informe à ALU qual o

tamanho dos dados que serão manipulados. Isso é fei to

através de instruções diferenciadas para cada tamanho de

subword. Assim, cada instrução aritmética, ou de

transferência de dados imediata para registrador, ou rotação

de bits das palavras que o processador suporta, possui um

opcode diferenciado para cada tamanho de dados

manipulados (como pode ser verificado na Tabela 1).

As instruções de transferência de dados imediata para

registrador carregam o registrador que é o primeiro

operando com o valor que é o segundo operando. A

instrução que faz a transferência de dados de um registrador

para outro é utilizada para qualquer tamanho de dados

suportados pelo processador.

TABELA I

PRINC IPAIS INSTRUÇÕES DO PROCESSADOR

Instruções

LOAD

STO

ADD8

ADD 16

ADD32

MULAS

MULB8

ANO

Opcode

100001

1000 10

000000

00000 1

000010

000 11 0

000111

001110

Operandos

RI, R2

RI , R2

RI, R2, R3

RI , R2, R3

RI , R2, R3

RI , R2, R3

RI, R2, R3

RI, R2, R3

Ação

RI <- [R2]

[RI ] < - R2

RI < - R2 + R3

Rl <- R2 + R3

RI <- R2 + R3

RI <- R2a * R3a

RI <- R2b * R3b

RI <- R2 ANO R3

As instruções aritméticas são do tipo adição, subtração,

divisão e multiplicação. Elas afetam todos os registradores

de jlag e possuem como operandos, três registradores. No

primeiro é armazenado o resultado da operação e os outros

dois contêm os operandos da mesma. As instruções de

multiplicação permitem que dados do mesmo tamanho

sejam multiplicados, gerando dados com o dobro do

número de bits dos operandos. Por isso, a multiplicação é

dividida em dois tipos de instrução: MUL A e MUL B. A

15 1

assembly, juntamente com o código de máquina, são

exibidos. A memória pode ser visualizada em uma janela

secundária do simulador. Além disso, é possível executar

todo o programa ou executá-lo instrução a instrução. Para

avaliar as instruções, é possível observar o conteúdo da

memória e dos registradores, tanto de propósito geral,

visualizados em grupos de quatro, como os de jlag Carry e

Zero, de instrução e o contador de programa. No entanto, o

registrador de pilha e os demais registradores de jlags ainda

não foram implementados. Isso, porém, não comprometeu a

validação do processador, já que os registradores de jlags

Sinal e Paridade apresentam o mesmo comportamento dos

jlags Carry e Zero. Como a simulação de instruções que

utilizam a pi lha da memória é um pouco mais complexa

que as demais, essas ainda não foram simuladas.

Algumas instruções ainda não são simuladas, mas todas

elas possuem execução semelhante a outras implementadas

no simulador. Isso aconteceu, pela dificuldade de

manipulação de certos dados, como a multiplicação de

dados de 32-bits, ou pela limitação de tempo para a

implementação do simulador.

Para a validação e apresentação das vantagens do

processador projetado, pode-se observar a Tabela 11. Ela

apresenta parte da repetição utilizada para adicionar doi s

vetores de dados de 8-bits. O lado esquerdo da tabela

apresenta o código para um processador GPP (General

Purpose Processar) hipotético, RISC, e o lado direito o

código para o processador projetado. Os registradores R2 e

R3 contêm o endereço inicial dos vetores a serem somados

e R4 o endereço inicial do vetor resultante. Após a

execução do código exibido, os conteúdos desses

registradores são incrementados. Existe também um

contador, inicialmente igual ao tamanho dos vetores, que

controla o número de vezes que a repetição é executada.

primeira multiplica a primeira metade dos registradores e a

segunda a outra metade.

Como o processador é um ASIP multimídia, as

instruções de adição e subtração possuem um recurso

adicional: elas aplicam a técnica de saturação. Assim, em

caso de ocorrência de um overflow/underflow, o dadoresultado recebe como valor, o valor máximo/ mínimo

permitido para operações com dados do tamanho definido

pelo tipo de instrução. Uma operação com saturação é

apresentada na Figura I a. A Figura I b apresenta a mesma

operação realizada sem a implementação da saturação. Este

exemplo apresenta uma soma, onde a ALU trata o conteúdo

do registrador de acordo com o número de subwords

indicado pelo tipo de instrução. Neste caso, os dados são de

16-bits e a eles é somado o valor IO.

l6553o Ioo 145 1540251 o8o79l l6553o Ioo 1451540251 o8o79l

165535 I oo 155 I 54035 I o8o89l

Ioooo41 oo 155 1540351 o8o89l

a

b

Fig. I Adição a)com saturação b)sem saturação

As instruções lógicas possuem, assim como as

aritméticas, três operandos registradores e o primeiro é o

destino. Elas afetam todos os registradores de jlag sendo

que o Cany sempre recebe o valor zero. As operações

lógicas implementadas são: XOR, OR, ANO e NOT. Estas

instruções não são d iferenciadas para o tamanho dos dados,

já que são realizadas bit-a-bit.

As outras instruções do processador são: zerar o

registrador de jlag Carry, HALT e rotação de palavras

dentro de um registrador. Além dessas, existem instruções

de rotação de bits das palavras, com ou sem carry (bit do

registrador Carry), à direita ou esquerda. Como a rotação

ocorre em cada palavra do registrador, essas instruções de

rotação de bits são diferentes para cada tamanho de dado.

TABELA 11

111 . V ALIDAÇÀO

C ó DIGOS-EXEMPLO

A validação do processador foi realizada através da

implementação de um simulador funcional [SIM OI]. Como

o projeto e implementação do simulador foram feitos em

uma disciplina da graduação, a simulação apresenta

algumas limitações. No entanto, elas não comprometeram a

va lidação do processador projetado.

O Simulador foi implementado em C++, porque era

uma linguagem que atendia aos objetivos do trabalho e que

não despenderia tempo com aprendizado de uma nova

linguagem. O compilador escolhido foi o Borland C++

Builder, já que com ele seria fácil implementar uma

interface gráfica amigável.

A interface com o usuário é bastante simples e, para

facilitar a implementação de programas para o processador,

foi implementado um montador assembler. No simulador é

possível abrir um programa escrito na linguagem assembly

própria do processador projetado, e então o código

Loop :

Loop :

LOAD R5 , [R2)

LOAD R6 , [R3 )

ADD R7 , R6, R5

LOAD

LOAD

ADDB

STO

JNC

Label2

MVI

R7 , MAX

R5, [R2)

R6 , [R3)

R7, R6 , R5

[R4 ) , R7

Label2 :

STO

[R4] , R7

Esse pequeno código demonstra duas grandes vantagens

do processador projetado: o paralelismo subword e a

saturação. O paralelismo subword implementado (neste

exemplo na instrução ADD8) permite que o laço de

repetição seja executado 8 vezes menos que o mesmo laço

em um processador sem essa característica. As instruções

com saturação (também na instrução ADD8) tomam

desnecessários saltos (instrução JNC) para a verificação de

overjlow, reduzindo o número de instruções e desvios.

152

Um programa de realce de contraste de imagens com

resolução 256x256 e 8-bits por pixel, executado num

processador sem técnicas de paralelismo subword gera

65536 acessos à memória para ler os pixels da imagem e

mais 65536 operações aritméticas para fazer o realce. No

processador projetado seriam necessários apenas 8 192

acessos e operações para a mudança de contraste.

processador e o simulador podem ser usados como

ferramenta de aprendizado, já que demonstram, de maneira

prática, conceitos apenas teoricamente apresentados.

Como ferramenta de aprendizado, o processador pode

ser utilizado não só em disciplinas como Arquitetura de

Computadores, que estuda diretamente os processadores e

suas características, mas também em outras disciplinas que

utilizam algumas dessas características dos processadores.

Dentre essas disciplinas, pode-se citar Compiladores,

Sistemas Operacionais e Processamento de Imagens.

Como o processador projetado possui limitações, entre

os trabalhos futuros pode-se destacar a sua melhoria com a

inclusão de instruções do tipo MAC (Multiply and

Accumulate). Para melhorar o simulador, pode-se

implementar todas as instruções e a pilha de memória.

Pode-se ainda estender o processador colocando nele

registradores para aplicações gerais que não envolvem

paralelismo. O processador ainda pode ser descrito em

VHDL (VHSIC Hardware Description Language) e

implementar protótipos usando-se síntese e dispositivos

programáveis FPGA (Field Programmable Gate Array).

Analisando as diversas fases do projeto do processador,

percebe-se que o trabal ho superou a proposta inicial da

disciplina Arquitetura de Computadores, resultando na

formação de recursos humanos, através da aquisição de

conhecimentos relativos a multimídia, processadores RISC

dedicados e paralelismo subword. Pode-se também destacar

a pesquisa para a realização do projeto do processador e do

simulador como motivação para desenvolvimento dos

trabalhos que estão sendo realizados atualmente: monitoria

e propostas de projetos de iniciação científica para serem

submetidos à Pró-Reitoria de Pesquisa e Pós-Graduação da

PUC Minas no próximo semestre.

IV. CONCLUSÃO

Através dos resultados da validação foi possível

concluir que o processador projetado funciona corretamente

e melhora o desempenho de aplicações multimídia através

das técnicas nele presentes: ( I) As instruções dedicadas

substituem várias instruções dos conjuntos não dedicados;

(2) O paralelismo nas instruções permite a execução de

várias operações ao mesmo tempo, aumentando o

desempenho do processador; (3) Além disso, o processador

possui instruções que implementam operações com

saturação, facilitando a utilização de instruções que geram

ovetflow/underflow eliminando a necessidade de testes

condicionais após essas operações.

Foi projetado um processador RISC dedicado a

aplicações multimídia aplicando paralelismo subword, e sua

validação foi realizada através de um simulador projetado e

implementado para validar este processador. Conclui-se

então que o projeto alcançou seus objetivos iniciais.

Ao longo do projeto, percebeu-se que foram alcançados

êxitos que não faziam parte dos objetivos iniciais. Dentre os

quais podemos destacar: ( l) a implementação do montador

assembler que facilitou o desenvolvimento de programasexemplo, já que eliminou a necessidade de codificação em

código de máquina. Isso facilita a utilização do simulador e

o entendimento do funcionamento do processador; (2) além

disso, concluiu-se que o processador projetado pode ser

usado como um microprocessador dedicado ou como um

núcleo processador inserido em processadores de propósito

geral. Essa técnica é utilizada atualmente na maioria dos

processadores de propósito geral do mercado para melhorar

a performance em aplicações multimidia.

Em todos os semestres em que foi proposto o projeto de

processadores na disciplina Arquitetura de Computadores,

este foi o primeiro projeto de um processador dedicado a

aplicações multimídia. Anteriormente já foram projetados

outros processadores ASIP e implementados outros tipos de

paralelismo, como o pipeline. Porém as características das

aplicações multimídia permitiram a aplicação do

paralelismo subword, que era uma técnica nova na

disciplina, e pouco conhecida pelos alunos.

Apesar das limitações do simulador implementado, a

simulação pode proporcionar uma base para aprendizado e

análise das vantagens do uso de um processador dedicado,

como o proposto, e da aplicação de paralelismo em certos

tipos de aplicação, como pode ser verificada através da

implementação do paralelismo subword. E, por isso, o

REFERÊNCIAS

[ARQ OI] http://www.dcc.pucmg.br/computacao/di sciplinas/ac/

[FLY 72] FLYNN, M. J., Some Computer Organizations and

Their Effectiveness, IEEE Trans. on Computers, V. C2 1' 1972, p.948-960.

[H EN 96] HENNESSY, John L.; PATTERSON, David A.,

"Computer Architecture a Quantitative Approach",

Morgan Kaufmann, 1996.

[HWA 97] HW ANG, Kai; ZHIWEI, Xu, Scalable Parallel

Computing: technology, architecture, programming.

McGraw-Hill, 1997.

[LEE 96] LEE, Ruby B. Subword Parallelism with MAX-2.

IEEE Micro, V.l6, n.4, Ago 1996.

[RAM 00] RAMAN Srinivas K.; PENTKOVSKJ Vladimir;

KESHA VA Jagannath. lmplementing Streaming

SIMD Extensions on the Pentium Ill Processor. IEEE

Micro, V.20, n.4, Jul/Aug 2000.

[SIM OI] http://www. lsdc.inf.pucminas.br/projetos/ PASIPMM

[TAN 98) TANENBAUM, Andrew S. Structured Computer

Organiza/íon. 4th edition, Prentice Hall, 1998.

[TRE 96) TREMBIAY, Marc et ai. VIS Speeds New Media

Processing. IEEE Micro, V.l6, n.3, Ago 1996.

153