XIV ERI-PR 2007

ISBN: 978-85-7669-115-0

Sistema Operacional Integrado Simulado:

Módulo de Entrada e Saída

Eduardo H. M. Cruz, Valdemir P. Silva, Ronaldo A. L. Gonçalves

Departamento de Informática - Universidade Estadual de Maringá

Zona 07 - Av. Colombo 5790 - CEP 87020-900 - Maringá – PR

{eduardo.cruz,valdps,ronaldo}@din.uem.br

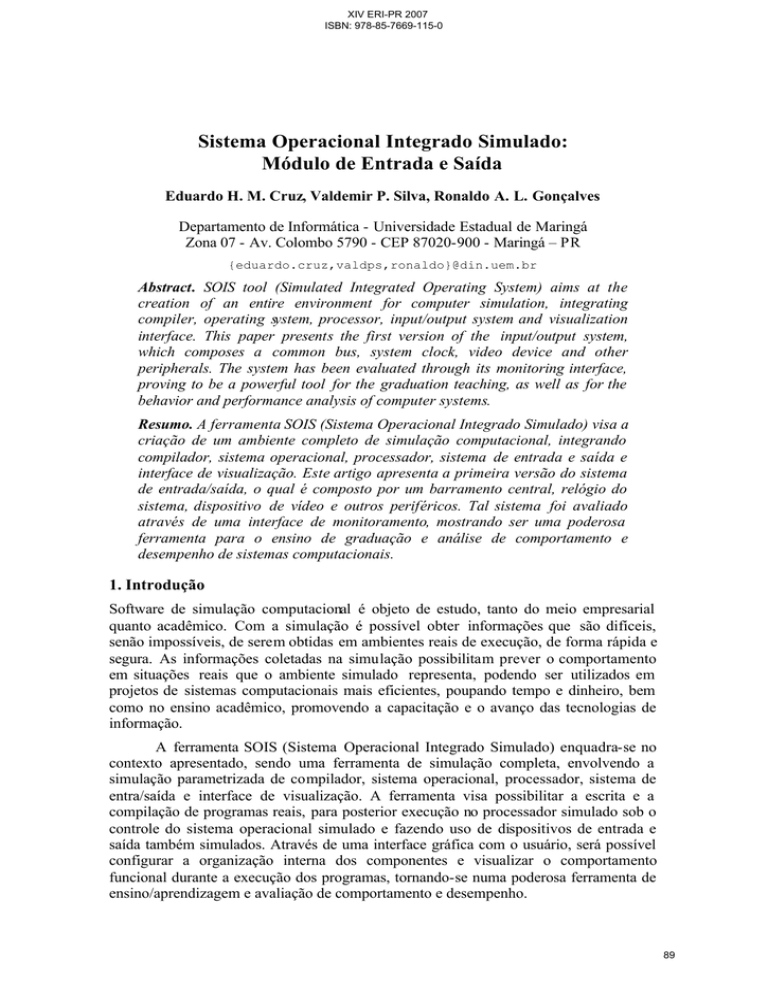

Abstract. SOIS tool (Simulated Integrated Operating System) aims at the

creation of an entire environment for computer simulation, integrating

compiler, operating system, processor, input/output system and visualization

interface. This paper presents the first version of the input/output system,

which composes a common bus, system clock, video device and other

peripherals. The system has been evaluated through its monitoring interface,

proving to be a powerful tool for the graduation teaching, as well as for the

behavior and performance analysis of computer systems.

Resumo. A ferramenta SOIS (Sistema Operacional Integrado Simulado) visa a

criação de um ambiente completo de simulação computacional, integrando

compilador, sistema operacional, processador, sistema de entrada e saída e

interface de visualização. Este artigo apresenta a primeira versão do sistema

de entrada/saída, o qual é composto por um barramento central, relógio do

sistema, dispositivo de vídeo e outros periféricos. Tal sistema foi avaliado

através de uma interface de monitoramento, mostrando ser uma poderosa

ferramenta para o ensino de graduação e análise de comportamento e

desempenho de sistemas computacionais.

1. Introdução

Software de simulação computacional é objeto de estudo, tanto do meio empresarial

quanto acadêmico. Com a simulação é possível obter informações que são difíceis,

senão impossíveis, de serem obtidas em ambientes reais de execução, de forma rápida e

segura. As informações coletadas na simulação possibilitam prever o comportamento

em situações reais que o ambiente simulado representa, podendo ser utilizados em

projetos de sistemas computacionais mais eficientes, poupando tempo e dinheiro, bem

como no ensino acadêmico, promovendo a capacitação e o avanço das tecnologias de

informação.

A ferramenta SOIS (Sistema Operacional Integrado Simulado) enquadra-se no

contexto apresentado, sendo uma ferramenta de simulação completa, envolvendo a

simulação parametrizada de compilador, sistema operacional, processador, sistema de

entra/saída e interface de visualização. A ferramenta visa possibilitar a escrita e a

compilação de programas reais, para posterior execução no processador simulado sob o

controle do sistema operacional simulado e fazendo uso de dispositivos de entrada e

saída também simulados. Através de uma interface gráfica com o usuário, será possível

configurar a organização interna dos componentes e visualizar o comportamento

funcional durante a execução dos programas, tornando-se numa poderosa ferramenta de

ensino/aprendizagem e avaliação de comportamento e desempenho.

89

XIV ERI-PR 2007

ISBN: 978-85-7669-115-0

SOIS é um projeto iniciado em 2004 [1] e devido a sua abrangência e

complexidade continua ainda em desenvolvimento. O núcleo básico do processador

SOIS [2] foi implementado e compõe-se basicamente de código para a decodificação e

execução da maioria das instruções IA-32. O módulo que simula o sistema de

entrada/saída [3] também foi desenvolvido, embora sobre um conjunto de instruções

simplificado para facilitar detecção de erros, precisando ser reajustado ao processador

SOIS. O objetivo deste artigo é apresentar este módulo.

Este artigo está organizado da seguinte forma. A seção 2 apresenta conceitos

sobre o sistema de entrada/saída. A seção 3 contextualiza o estado da arte, mostrando

alguns trabalhos relacionados. A seção 4 apresenta o projeto e implementação do

sistema de entrada/saída. As conclusões e trabalhos futuros são esboçados na seção 5 e

as referências bibliográficas aparecem no final do texto.

2. Sistema de Entrada/Saída

Para executar uma função útil, os processadores devem ser capazes de interagir com o

mundo externo e os dispositivos além da memória [4]. Sistema de entrada/saída define a

arquitetura do relacionamento e comunicação entre todos os componentes do

computador, provendo o transporte de informações e os seus métodos. Um dispositivo

externo se comunica com o processador por um canal de E/S, utilizado para controlar e

acessar o status e dados dos dispositivo s chamados comumente de periféricos [5].

Existem 3 principais modelos de entrada/saída [6]: programada, baseada em interrupção

e via DMA.

Na E/S programada, a verificação do status das operações, isto é, quando iniciar,

transmitir ou finalizar, é feita por software. Com isso, o processador fica continuamente

verificando as portas de comunicação com o dispositivo para realizar as operações

desejadas, perdendo tempo com verificações e esperas inúteis (busy wait). Apesar da

simplicidade de implementação, este método tende a deixar o sistema muito lento [7].

Na E/S com interrupção, o processador não precisa verificar constantemente o

status das operações, sendo de responsabilidade da interface do dispositivo interromper

o processador quando uma requisição estiver concluída. Com isso, o processador fica

liberado para realizar computação útil durante a ocupação do dispositivo. Ainda que

este método seja mais eficiente que a entrada/saída programada, ele ainda é bastante

oneroso no caso da transferência de um bloco contíguo de informações entre memória e

o dispositivo, pois todos os dados devem ser lidos da memória, movidos internamente

no processador e depois enviados ao dispositivo.

Para minimizar este problema usa-se a entrada/saída via DMA (acesso direto a

memória). Neste caso, o processador envia uma requisição de transferência em bloco ao

dispositivo e segue seu processamento normal, tal como na entrada/saída com

interrupção. O dispositivo se responsabiliza em tratar a transferência diretamente com o

sistema de memória, reservando o barramento e transferindo, ininterruptamente, todo o

bloco de dados. Após o término, o processador é interrompido uma única vez.

O gerenciamento das operações de entrada/saída, feitas pelas aplicações, é

realizado pelo sistema operacional [8], que disponibiliza rotinas de entrada/saída de alto

nível, escalona processos para receber o atendimento das requisições e aciona as

funções básicas fornecidas pelo circuito controlador do dispositivo ou as funções mais

elaboradas fornecidas pelo programa controlador do dispositivo (drivers).

90

XIV ERI-PR 2007

ISBN: 978-85-7669-115-0

Os processadores normalmente apresentam duas instruções de entrada/saída em

nível de máquina : in (para ler dados de uma porta) e out (para escrever dados em uma

porta). Cada dispositivo possui um conjunto de portas que pode ser manipulado com

estas instruções, incluindo porta de dados, porta de controle e porta de status. Cada

porta possui um endereço tal como uma posição de memória.

Existem vários componentes de um sistema de entrada/saída, entre eles, a

interface controladora, o barramento, o relógio central e os periféricos. A interface

controladora tem como principal função tornar transparente para o processador os

detalhes de operação e controle dos periféricos. O barramento é o canal comum de troca

de informações entre os dispositivos conectados, sendo composto de três principais vias

de comunicação: endereço, controle e dados. Pelo fato do barramento permitir um único

acesso de cada vez, existe a necessidade de um árbitro para controlar a ordem de

atendimento segundo alguma prioridade.

O relógio central [9] é um circuito oscilador que define segmentos de tempos,

sendo considerado como referência de tempo do sistema. É muito útil em Sistemas

Operacionais Multitarefas na determinação do tempo designado a cada processo. Os

periféricos são dispositivos conectados a um computador que permitem e este a

realização de atividades externas.

3. Trabalhos Relacionados

Vários trabalhos relacionados a simulação de sistemas computacionais são encontrados

na literatura. Nachos [10], por exemplo, é um sistema operacional simulado que executa

no nível do usuário como um processo do Unix. Ele permite simular a CPU,

dispositivos, processos, threads, RPC, hierarquia de memória, programação orientada a

objetos e computação distribuída. Possui interface amigável e é direcionado ao ensino

de graduação da disciplina de sistemas operacionais, permitindo ilustrar conceitos e

princípios importantes.

Ramses [11] é um computador hipotético desenvolvido também para o ensino,

bastante simplificado, que possui um conjunto de 16 instruções, trabalha com dados e

endereços de 8 bits, possui apenas 4 registradores de 8 bits e um registrador de status de

operação. Suas instruções são de um ou dois bytes. O primeiro byte contém o código de

operação, o identificador do registrador e o modo de endereçamento. O segundo byte

contém um endereço ou um dado imediato. Sua utilização é direcionada para aulas

introdutórias nas disciplinas de arquiteturas de computadores.

Em [12], Maia e Pacheco apresentam um simulador de sistema operacional com

capacidades vis uais, denominado SOsim, capaz de gerenciar processos e memória de

forma multiprogramada, mostrando a dinâmica interna do sistema operacional. O

simulador foi apresentado e avaliado por alunos de graduação, que concluíram que o

mesmo facilita o aprendizado dos conceitos. A interface é simples e apenas alguns

módulos do simulador foram implementados. Além disso, SOsim não executa

aplicações que possam ser desenvolvidas sobre algum tipo de hardware simulado. Sua

idéia principal se baseia no aprendizado construtivista.

Outro projeto interessante, chamado PortOS [13], foi desenvolvido para

complementar o ensino de graduação e de pós-graduação para a disciplina de Sistemas

Operacionais. PortOS é uma ferramenta que guia os próprios alunos no

desenvolvimento de um sistema operacional para equipamentos móveis do tipo PDA,

91

XIV ERI-PR 2007

ISBN: 978-85-7669-115-0

permitindo trabalhar com threads, concorrência, escalonamento, sistema de arquivos,

sincronização e comunicação ponto a ponto. PortOS visa prover uma plataforma de

software que permita aos estudantes desenvolver um sistema operacional real, em nível

de usuário e com toda a segurança.

Abacus [14], desenvolvido pelo professor Roberto M. Ziller, simula o

processador 8085 da Intel®. Possui uma interface gráfica através da qual mostra o

conteúdo de seus registradores, os flags, o conteúdo da memória e o código em

execução para que o usuário possa escrever seus programas, executá- los passo a passo

ou continuamente, visualizar o comportamento do programa e as alterações que suas

instruções causam às estruturas internas ao processador e ao conteúdo da memória.

Criado especificamente para a plataforma Windows, o Winmips64 [15] permite

executar instruções do processador Mips. Com ele é possível ao aluno aprender

visualmente o conceito de pipeline. O usuário pode executar passo a passo as instruções

e acompanhar o funcionamento interno de um processador Mips simulado. Em outro

trabalho [16], um simulador foi desenvolvido para permitir aos usuários explorar

entrada/saída concorrente no Unix. O simulador pode execut ar programas

desenvolvidos pelo usuário e mostrar o relacionamento entre as várias estruturas de

dados envolvidas na entrada/saída, incluindo a tabela de descritores de arquivos, a

tabela de arquivos abertos do sistema, os i- nodes e os dados armazenados no disco. O

usuário pode executar o programa lentamente, avançar ou retroceder para analisar os

dados detalhadamente.

Em 2004, o simulador SOS [1] foi desenvolvido e se tornou o precursor da

ferramenta SOIS. SOS foi especificado em dois grandes componentes. No primeiro

componente havia um processador simulado para um conjunto próprio de instruções e

um montador de mnemônicos. No segundo componente havia o sistema operacional

simulado propriamente dito, sendo este composto de vários módulos de gerenciamento

comumente existentes em um sistema operacional, além de uma interface gráfica. A

Figura 1 mostra seus principais componentes e relacionamentos. A principal deficiência

do SOS era o conjunto reduzido de instruções disponíveis e a dificuldade de agregar

novos componentes ao sistema, motivo pelo qual ele foi abandonado e um novo

processador [2] foi implementado com um subconjunto de instruções IA-32. A Figura 2

mostra a visão interna do processador simulado.

Figura 1. SOS em Camadas – Precursor da Ferramenta SOIS

92

XIV ERI-PR 2007

ISBN: 978-85-7669-115-0

Um outro projeto bastante similar ao presente projeto, intitulado Trimaran [17],

proposto por um consórcio entre a HP e universidades, visa o desenvolvimento de uma

infra-estrutura de compilação sobre a plataforma EPIC, voltada para a exploração de

paralelismo em nível de instrução (ilp). Trimaran compõe-se de facilidades de descrição

de arquiteturas ilp, uma arquitetura ilp parametrizada, um compilador C e uma interface

gráfica do usuário.

Figura 2. Visão Interna do Processador Simulado

4. Projeto e Implementação do Sistema de Entrada/Saída

O simulador de entrada/saída desenvolvido não tem como base alguma arquitetura em

particular, sendo a generalização de várias teorias descritas na literatura especializada.

O projeto é focado nos princípios básicos comuns à maioria dos sistemas de

computadores. Os dispositivos principais de um computador simples foram criados:

disco, vídeo, teclado, um barramento central, um relógio do sistema e um dispositivo

para dar suporte ao tratamento de interrupções e recursos de DMA, com todas as

funções de gerenciamento e transferência de dados. O usuário pode interferir no

funcionamento do sistema de entrada e saída, realizar experiências e criar um arquivo de

log para acompanhar o funcionamento interno.

O recurso central do simulador é o barramento. Não há qualquer tráfego direto

de informação entre os dispositivos, devendo todo envio e recebimento de dados ser

feito através do barramento do sistema. O modelo de entrada/saída adotado é a de

interrupção. Para facilitar a implementação de tal projeto, o mesmo não foi

implementado de forma integrada ao processador SOIS, que por si só já possui uma

complexidade que dificultaria a detecção e recuperação de erros de simulação. O

simulador de entrada/saída opera sobre um processador próprio constituído de um

conjunto mínimo de instruções. Entretanto, agora que o mesmo já está operacional e

depurado, a integração do mesmo ao processador SOIS será mais fácil. A Figura 3

ilustra como deverá ficar esta integração.

93

XIV ERI-PR 2007

ISBN: 978-85-7669-115-0

Figura 3. Integração Processador e Sistema de Entrada/Saída

Todos os componentes do sistema de entrada/saída se comunicam entre si

através do barramento. O simulador define três variáveis para comunicação com os

dispositivos: Dados, Status e Endereço, os quais servem para simular o funcionamento

de um barramento real. Todas as interfaces do simulador têm características comuns,

sendo dotadas de registradores de funções, números de portas de endereçamento,

funções de entrada e saída, um buffer e um temporizador para simular tempos de

resposta diferentes. O algoritmo básico é apresentado na Figura 4.

Acabou a espera?

sim

Decrementa delay

início

sim

não

Barramento

ocupado?

Sai do ciclo

Interface ocupada?

não

sim

Envia dado

requerido pelo

barramento

não

não

Barramento com

dados para esta

interface?

Executa ação de

acordo com a porta

de E/S

sim

Segura o delay por

mais um ciclo

Guarda a

requisição do

barramento

Libera barramento

ofe

Ajusta delay de

acordo com o

periférico

req

Barramento

oferecendo ou

requerendo dado?

Figura 4. Fluxograma de Funcionamento Padrão das Interfaces

A lógica do código de todos os componentes é a mesma; uma vez compreendida

uma interface, todas funcionam do mesmo modo, facilitando o aprendizado e

diferenciando apenas nas particularidades inerentes a cada função que aquela interface

94

XIV ERI-PR 2007

ISBN: 978-85-7669-115-0

executa com o periférico. Cada dispositivo tem uma interface específica que faz a

comunicação com o barramento central. As interfaces têm um número limitado de

portas e cada porta tem uma função diferente. Isto é necessário para realizar as várias

tarefas designadas aos periféricos.

O sistema de vídeo não possui modo gráfico, trabalhando somente em modo

texto com resolução de 40x12 caracteres. A controladora tem 10 páginas de vídeo e

cada página ocupa 480 bytes de memória, sendo um byte para cada posição no vídeo. É

possível ter apenas uma página ativa por vez, permitindo um melhor suporte para o

sistema operacional multitarefa. O hardware do simulador tem 2 discos rígidos, cada um

com capacidade de 4MB de espaço para armazenamento. Este espaço é dividido em

blocos de memória de 1KB, fazendo com que cada HD simulado tenha 4096 blocos.

Os discos têm 4 pratos de face única com 1 mega cada de espaço divididos em

64 cilindros, e cada cilindro com 16 blocos. Quando a interface de disco recebe alguma

ordem do processador, o primeiro passo executado é liberar o barramento. A interface

controladora de disco funciona exatamente como qualquer interface genérica. Há a

opção de utilizar DMA para transferências. Se o DMA está executando alguma função,

o processador pode executar outras instruções normalmente, competindo com a

controladora de DMA pelo barramento.

A controladora de teclado, a cada ciclo, verifica se foi pressionada alguma tecla.

Se isso não ocorreu, o ciclo é abandonado. Caso tenha sido pressionada, os dados em

formato de caractere ASCII são armazenados em um buffer da interface. Esse buffer tem

um tamanho de 256 caracteres. Se o buffer está cheio os novos dados teclados são

ignorados e uma chamada de interrupção é enviada ao tratador de interrupção. Quando o

sistema operacional puder tratará a interrupção do teclado.

A arbitragem adotada pelo tratador de interrupção é por prioridade. Todos os

componentes têm um número associado no tratador de interrupção, no qual o mesmo

representa uma posição no vetor de interrupções. Através desse número é possível

saber qual o dispositivo que está requisitando uma interrupção e a sua prioridade. Como

o processador tem prioridade máxima, o seu número no tratador de interrupção é 0.

A controladora de DMA do simulador está implementada dentro da controladora

de disco. Uma particularidade deste projeto em relação à maioria dos projetos reais de

computadores é que o DMA não tem o modo “Hold State”, ou seja, o DMA não tem

controle exclusivo do barramento no momento da sua operação. Quando o DMA está

executando alguma função, o processador, juntamente com todos os outros dispositivos,

continua executando e concorrendo ao barramento.

O processador é tratado pelo sistema como mais uma interface. A única

diferença é a prioridade no tratador de interrupção. Qualquer interface controladora

poderá enviar e receber dados do processador como se estivesse acessando qualquer

outra interface de forma transparente. O funcionamento do processador é baseado em

ciclos, conforme mostra a Figura 5.

O Relógio do sistema é bastante simples, possuindo apenas a função de contar

ciclos. Quando o contador de ciclos chega ao final, seu va lor é reinicializado e é enviada

uma interrupção de relógio para o processador. Dessa forma, o “Time Slice” é simulado,

dando suporte ao sistema operacional multitarefa. O simulador tem um megabyte de

espaço em memória e a pilha utiliza as últimas posições. Não há proteção na área da

95

XIV ERI-PR 2007

ISBN: 978-85-7669-115-0

pilha, podendo ser escrito nesta área. Como visto, o processador tem acesso direto à

memória do sistema, mas é possível utilizar as instruções in e out para acessar ou enviar

dados através do barramento, concorrendo com outros periféricos.

sim

início

Wait state?

sim

sim

Recebe dados /

Libera barramento

não

não

Trata interrupção

Dado liberado no

barramento?

Há interrupção a

tratar?

Requer dados ao

barramento

(wait state)

Sai do wait state

Envia dados ao

barramento

Sai do ciclo

não

Lê instrução da

memória

Sai do ciclo

in

out

não

Executa instrução

Instrução de E/S?

Barramento livre?

não

Reinicia no próximo

ciclo

sim

Figura 5. Funcionamento do Ciclo do Processador

Uma interface de visualização, baseada em caracteres, que permite rapidez na

manipulação e compatibilidade com diferentes sistemas hospedeiros, foi desenvolvida

como solução provisória para o acompanhamento e monitoramento do sistema de

entrada/saída. Esta interface não se refere à interface principal do simulador, a qual

ainda será desenvolvida como um módulo a parte. A tela principal da interface do

sistema de entrada/saída é dividida em 4 partes, conforme abaixo, sendo mostrada na

Figura 6.

•

Display da interface de vídeo – onde os resultados das ações executadas pelo

sistema de vídeo do simulador podem ser visualizados.

•

Interfaces – onde o funcioname nto interno dos dispositivos de E/S do

simulador pode ser visualizado, estando a interface de vídeo, teclado, disco e

DMA representados graficamente.

•

Registradores – onde as ações e movimentos de dados entre os regis tradores

podem ser acompanhados, inclusive o ponteiro de pilha, contador de

programa e flag.

•

Componentes – onde todos os outros componentes do simulador são

acompanhados, permitindo a visualização do funcionamento do Barramento,

as instruções do processador e seu estado atual, memória e outros.

No término da execução de todos os ciclos, o sistema grava em um arquivo os

dados obtidos, contendo uma tabela com todas as informações necessárias para o

acompanhamento do funcionamento do simulador. O simulador foi testado em diversas

situações e se mostrou eficiente e adequado ao ensino de graduação. A Figura 6 mostra

um snapshot da execução de um programa de “jogo de rebate bola”, o qual foi

96

XIV ERI-PR 2007

ISBN: 978-85-7669-115-0

apresentado durante a defesa do trabalho de conclusão de curso e aprovado pela banca

examinadora.

Figura 6. Tela Principal do Simulador de Entrada/Saída

5. Conclusões e Trabalhos futuros

Existem várias ferramentas disponíveis voltadas à simulação de arquiteturas de

hardware quanto de software, mas existem poucas ferramentas com a capacidade de

simular um sistema computacional completo, mantendo a simplicidade de

funcionamento e com código aberto para alterações e experiências de laboratório. Neste

contexto, a ferramenta SOIS tem importância contextualizada e o presente trabalho

contribui com o desenvolvimento do sistema de entrada/saída desta ferramenta.

O módulo de simulação do sistema de entrada/saída possui uma interface

simples de visualização, provisória, que permite ao aluno de graduação entender de

forma simples as operações realizadas internamente no hardware, durante as operações

de entrada/saída. O simulador permite visualizar o fluxo de informações no barramento,

nas portas e nos dispositivos. O simulador foi testado na execução de “jogo de rebate

bola” e seu funcionamento foi avaliado e aprovado através da análise das telas de

monitoração e dos arquivos de log.

Como trabalhos futuros, o módulo de simulação de entrada/saída deverá ser

readequado ao processador simulado IA-32 e as funções de sua interface com o usuário

deverão ser incorporadas à interface gráfica da ferramenta SOIS, a ser ainda

desenvolvida.

97

XIV ERI-PR 2007

ISBN: 978-85-7669-115-0

Referências Bibliográficas

[1] Gonçalves, Rogério A.; Mulati, Mauro H.; Silva, Valdemir P. da; Gonçalves, Ronaldo A. L.

Sistema Operacional Simulado: Ferramenta para o Ensino de Graduação. In: XXIV

Congresso da SBC/XII WEI - Workshop de Educação em Informática, Salvador, 2004.

[2] Gonçalves, R. A.; Gonçalves, R. A. L. Sistema Operacional Integrado Simulado: Projeto e

Implementação do Módulo Processador. Escola Regional de Informática Paraná (ERIPR). FFALM. Bandeirantes. 2006.

[3] Silva, V. P.; Gonçalves, R. A. L. Ferramenta SOIS: Simulação de Interfaces, Periféricos e

Dispositivos de Entrada e Saída. Trabalho de Conclusão de Curso. Universidade Estadual

de Maringá. Departamento de Informática. 2006.

[4] Carpinelli, J. Computer Systems Organization & Architecture, Addison Wesley. 2000.

[5] Lorin, H. Introduction to Computer Architecture and Organization. John Wiley

Professional, 1989.

[6] Stallings, W. Computer Organization and Architecture. Prentice-Hall. 2002.

[7] Carter, N. Arquitetura de Computadores. Editora Bookman. 2003.

[8] Tanenbaum, A. S. Modern Operating Systems. Prentice-hall. 2001.

[9] Langdon, G. G. Projeto de Computadores Digitais. Editora Edgard Blucher. 1977.

[10] Christopher, W. A., Procter, S. J. and Anderson, T. E. “The Nachos Instructional Operating

System”. University of California, Berkeley. Technical Report CSD-93-739, 1993.

[11] Weber, R. F. Fundamentos de Arquitetura de Computadores. 1ª Edição, Séries Livros

Didáticos. Instituto de Informática da UFRGS: Editora Sagra Luzzatto, Porto Alegre,

2000.

[12] Maia, L. P. and Pacheco, A. C. “A Simulator Supporting Lectures on Operating Systems”.

Proceedings of the 33rd ASEE/IEEE Frontiers in Education Conference, November 5-8,

Boulder, CO, USA, 2003.

[13] Atkin, B. and Sirer, E.G. “PortOS: An Educational Operating System for the Post-PC

Environment”. Computer Science Department, Cornell University. Proceedings of the

33rd ACM Technical Symposium on Computer Science Education, 2002.

[14] Ziller, Roberto M. Microprocessadores: Conceitos Importantes. 2ª Edição. EEL – UFSC,

Florianópolis, ISBN: 85-901037-2-2, SC, 2000.Florianópolis, ISBN: 85-901037-2-2, SC,

2000.

[15] Scott, M. Using WinMIPS64 Simulator: A Simple Tutorial. Disponível no site

http://www.computing.dcu.ie/~mike/winmips64.html em 2006.

[16] Robbins, S. A UNIX Concurrent I/O Simulator. Proceedings of the SIGCSE (Technical

Symposium on Computer Science Education), Houston, Texas, USA, March 2006.

[17] Trimaran Compiler: Research Infraestructure for Instruction Level Paralellism. Tutorial

disponível em 20/05/2007 no endereço www.trimaran.org

98