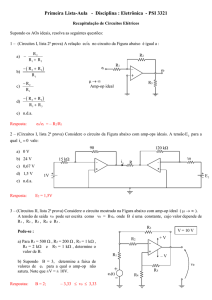

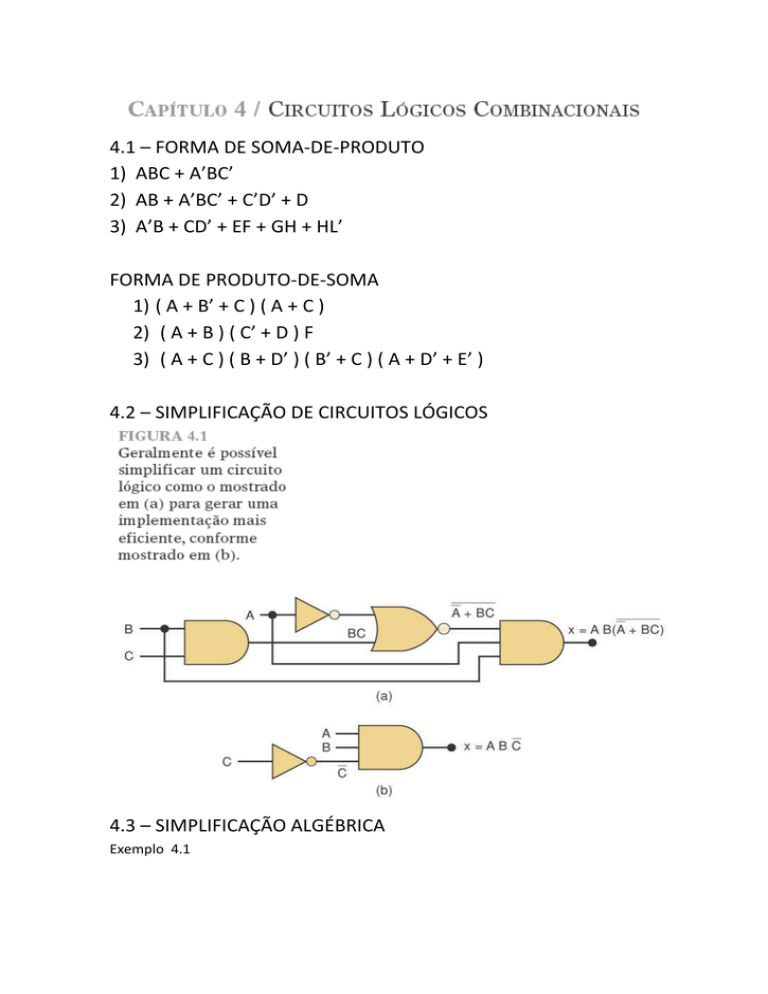

4.1 – FORMA DE SOMA-DE-PRODUTO

1) ABC + A’BC’

2) AB + A’BC’ + C’D’ + D

3) A’B + CD’ + EF + GH + HL’

FORMA DE PRODUTO-DE-SOMA

1) ( A + B’ + C ) ( A + C )

2) ( A + B ) ( C’ + D ) F

3) ( A + C ) ( B + D’ ) ( B’ + C ) ( A + D’ + E’ )

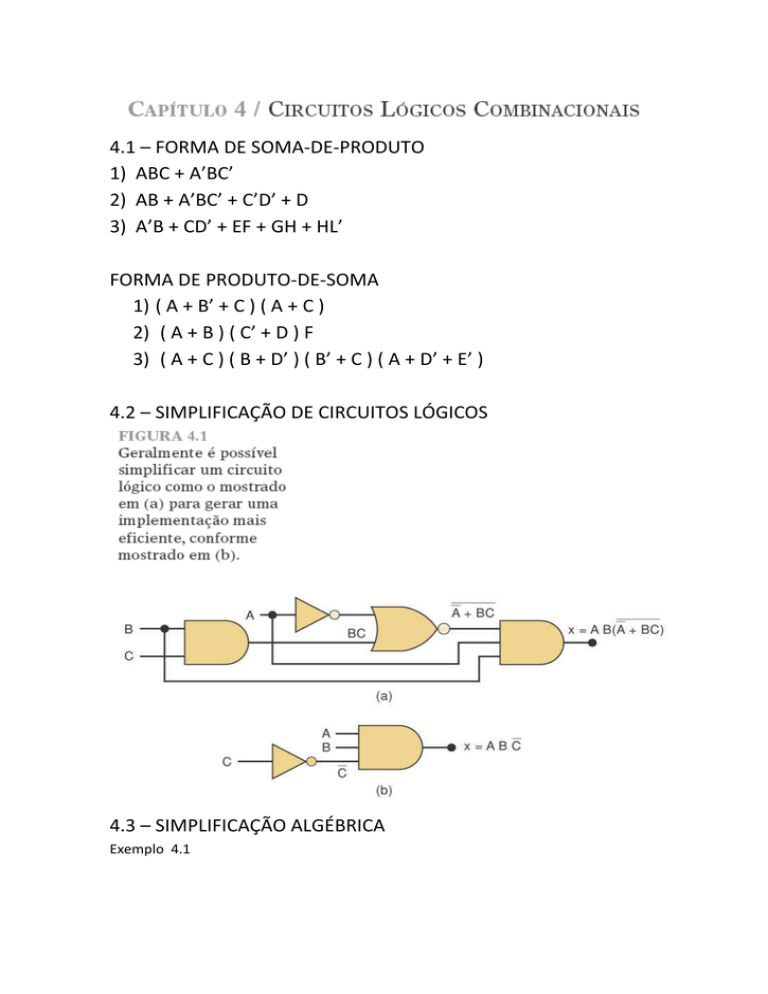

4.2 – SIMPLIFICAÇÃO DE CIRCUITOS LÓGICOS

4.3 – SIMPLIFICAÇÃO ALGÉBRICA

Exemplo 4.1

Exemplo 4.5

4.4 – PROJETANDO CIRCUITOS LÓGICOS COMBINACIONAIS

Exemplo 4.7 – Projete um circuito lógico com três estradas, A,B e C, cuja saída será

nível ALTO apenas quando a maioria das entradas for nível ALTO.

Obs. Fazer a tabela verdade, obter a equação e simplificar.

Exemplo 3.8 – Obter valores maiores que seis.

Obs. Deve ser simplificado em sala de aula.

Exemplo 4.9 – Veja a figura abaixo. Em uma máquina copiadora, um sinal de parada. S,

é gerado para interromper a operação da máquina e ativar um indicador luminoso

sempre que uma das condições a seguir ocorrer: (1) a bandeja de alimentação de

papel estiver vazia; ou (2) as duas microchaves sensoras de papel estiveram

acionadas, indicando um atolamento de papel. A presença de papel na bandeja de

alimentação é indicada por um nível ALTO no sinal lógico P. Cada uma das microchaves

porduz sinais lógicos (Q e R) que vão para nível lógico ALTO sempre que um papel

estiver passando sobre a chave, que é ativada. Projete um circuito lógico que gere uma

saída S em nível ALTO para as condições estabelecidas e implemente-os usando o CI

CMOS 74HC00 que contém quatro portas NAND de duas entradas.

Obs. Fazer a tabela verdade

O circuito final é mostrado abaixo

4.5 – MÉTODO DO MAPA KARNAUGH

2.5 – O CÓDIGO GRAY (revisão)

Agrupamento de dois quadros (pares)

Agrupamento de quatro quadros (quartetos)

Agrupamentos de oito quadros

(oct

Exemplo 4.10

Exemplo 4.14

CONDIÇÕES DE IRRELEVÂNCIA ( DON’T-CARE )

EXEMPLO 4.15 – Vamos projetar um circuito lógico que controla uma porta de

elevador em um prédio de três andares. O circuito na fig. 4.19(a) tem quatro entradas.

M é um sinal lógico que indica quando o elevador está em movimento (M=1) ou

parado (M=0). F1, F2 e F3 são os sinais indicadores dos andares que são normalmente

no nível BAIXO, passando para o nível ALTO, apenas quando o elevador estiver

posicionado em um determinado andar. Por exemplo, quando o elevador estiver no

segundo andar, F2=1 e F1=F3=0. A saída do circuito é o sinal ABRIR que normalmente

é nível BAIXO e vai para nível ALTO quando a porta do elevador tiver que ser aberta.

Análise através da forma PRODUTO-DE-SOMA.

4.6 – CIRCUITO EXCLUSIVE-0R (OU-EXCLUSIVO) E EXCLUSIVE-NOR

74LS86, 74C86 e 74HC86 são CIs com quatro XOR

74LS266, 74C266 e 74HC266 são CIs com quatro XNOR

Exemplo 4.16

Exemplo 4.17 – Compara quando dois números com dois bits são iguais.

Exemplo 4.18

Z = ABCD + AB’C’D + A’D’

Z = AD(BC + B’C’) + A’D’

Z = AD(B©C)’ + A’D’

4.7 – CIRCUITOS GERADORES E VERIFICADORES DE PARIDADE

2.9 –DETECÇÃO DE ERRO PELO MÉTODO DA PARIDADE

4.8 – CIRCUITOS PARA HABILITAR/DESABILITAR

Exemplo 4.21 – Projete um circuito lógico que permita a passagem de um sinal para a

saída apenas quando as entradas de controle B e C forem ambas nível ALTO; caso

contrário, a saída permanecerá em nível BAIXO. Obs. Figura (a)

Exemplo 4.22 – Projete um circuito lógico que permita a passagem de um sinal para a

saída apenas quando uma, mas não ambas, for nível ALTO; caso contrário, a saída

permanecerá em nível ALTO. Obs. Figura (b)

Exemplo 4.23 – Projete um circuito lógico com um sinal de entrada A, entrada de

controle B e saídas X e Y que operam da seguinte forma:

a) Quando B=1, a saída X segue a entrada A, e a saída Y é “0”.

b) Quando B=0, a saída X é “0”, e a saída Y segue a entrada A.

4.9 – CARACTERÍSTICAS BÁSICAS DE CIs DIGITAIS

(NÃO VISTO EM ELE0515 – CIRCUITOS LÓGICOS)

4.10 – ANÁLISE DE DEFEITOS EM SISTEMAS DIGITAIS

(NÃO VISTO EM ELE0515 – CIRCUITOS LÓGICOS)

4.11 – FALHAS INTERNAS DOS CIS DIGITAIS

(NÃO VISTO EM ELE0515 – CIRCUITOS LÓGICOS)

4.12 – FALHAS EXTERNAS

(NÃO VISTO EM ELE0515 – CIRCUITOS LÓGICOS)

4.13 – ESTUDO DE UM CASO DE ANÁLISE DE DEFEITO

(NÃO VISTO EM ELE0515 – CIRCUITOS LÓGICOS)

4.14 – DISPOSITIVOS LÓGICOS PROGRAMAVÉIS (PLD)

(NÃO VISTO EM ELE0515 – CIRCUITOS LÓGICOS)

Projeto e processo de desenvolvimento

(NÃO VISTO EM ELE0515 – CIRCUITOS LÓGICOS)

4.15 – REPRESENTANDO DADOS EM HDL

Matrizes de bits/vetores de bits.

TABELA-VERDADE USANDO VHDL: ATRIBUIÇÃO DE SINAL

SELECIONADA VHDL

ENTITY fig4_51 IS

PORT ( a,b,c : IN BIT;

-- declara bits de entrada individual

Y

: OUT BIT);

END fig4_51;

ARCHITECTURE truth OF fig5_51 IS

SIGNAL in_bits : BIT_VECTOR (2 DOWNTO 0 );

BEGIN

In_bit <= a & b & c ; -- concatena bits de entrada bit_vector

WITH in_bits SELECT

Y<= ‘0’ WHEN “000”

‘0’ WHEN “001”

‘0’ WHEN “010”

‘1’ WHEN “011”

‘0’ WHEN “100”

‘1’ WHEN “101”

‘1’ WHEN “100”

‘1’ WHEN “111”

END truth;

4.17 – ESTRUTURAS DE CONTROLE DE DECISÃO EM HDL

IF/ELSE ( IF/THEN e IF/THEN/ELSE )

Para usar a estrutura de controle IF/THEM/ELSE, o VHDL exige que o código

seja colocado dentro de um PROCESS. As declarações que ocorrem dentro de

um processo são seqüenciais, ou seja, a ordem em que são escritas afeta o

comportamento do circuito.

Exemplo 4.8 – Relembrando o exemplo de um circuito lógico para indicar um

número binário com quatro bits maior que seis.

Resolvendo o problema em VHDL com estrutura IF/THEN/ELSE

ENTITY fig4_22 IS

PORT ( valor_digital : IN INTEGER RANGE 0 TO 15;

z : OUT BIT);

END fig4_55 IS;

ARCHITECTURE decision OF fig1_55 IS

BEGEN

PROCESS ( valor_digital )

BEGIN

IF (valor_digital > 6 ) THEN

Z <= ’1’ ;

ELSE

Z <= ‘0’ ;

ED IFN;

END PROCESS;

END decision;

ELSIF

EXEMPLO DE ELSIF USANDO VHDL

ENTITY fig4_59 IS

PORT (valor_digital: IN INTEGER RANGE 0 TO 15; --declara entrada

Frio_demais, ideal, quente_demais: OUT BIT);

END fig4_59;

ARCHITECTURE howhot OF fig4_59 IS

SIGNAL status : BIT_VECTOR (2 downto 0);

BEGIN

PROCESS (valor_digital)

BEGIN

IF (valor_digital <=8 ) THEN status<=”100”;

ELSIF (vavor_digital > 8 AND valor_digital < 11 ) THEN

Status <= “010”;

ELSE status <= “001”;

END IF;

END PROCESS;

Frio_demais <= status (2): --atribui a status bits para a saída

Ideal

<= status (1);

Quente_demais <= status (0);

END howhot:

CASE

EXEMPLO DE CASE USANDO VHDL