Construção e Teste de um Protótipo de Conversor

Matricial

Luís Miguel Rosa Colaço

Dissertação para obtenção do Grau de Mestre em

Engenharia Electrotécnica e de Computadores

Júri

Presidente:

Prof. Paulo José da Costa Branco

Orientadores: Prof. José Fernando Alves da Silva

Prof(a). Sónia Maria Nunes dos Santos Paulo Ferreira Pinto

Vogal:

Prof. Joaquim José Rodrigues Monteiro

Outubro de 2011

Agradecimentos

Agradeço a todas as pessoas que me apoiaram e ajudaram no decorrer da execução deste

trabalho de dissertação.

Quero começar por agradecer aos professores que me orientaram e acompanharam na

realização desta tese de mestrado, pois sem eles tudo teria sido muito mais difícil. Um muito

obrigado ao Prof. Fernando Silva, à Prof. Sónia Pinto e ao Prof. Joaquim Monteiro, pela

constante disponibilidade, dedicação e paciência que sempre demonstraram para comigo.

Em segundo lugar, quero agradecer à D. Noémia pelo apoio e pela disponibilidade na resolução

dos assuntos administrativos e ainda ao Sr. Duarte que sempre disponibilizou as ferramentas

necessárias para a execução do trabalho laboratorial.

Um obrigado muito especial a todos os meus colegas do Instituto Superior Técnico, pelo

companheirismo e amizade partilhada durante todos os anos do meu percurso académico.

Por último e não menos importante, queria deixar um especial agradecimento à minha família,

pelo apoio prestado durante a execução deste trabalho de dissertação.

A todas estas pessoas o mais sincero obrigado!

II

Resumo

O objectivo deste trabalho é projectar, construir e testar um protótipo laboratorial de um

conversor de potência AC/AC directo, designado por Conversor Matricial (CM). Espera-se que

protótipo tenha maior rendimento do que os actuais conversores AC/AC indirectos, reduzindo o

custo, volume e peso.

Durante este trabalho, foi dimensionado e construído um conversor matricial composto por um

circuito de potência que engloba: os módulos de potência que realizam os interruptores

bidireccionais (IB), os circuitos de disparo dos semicondutores de potência, circuitos de

protecção contra sobretensões com díodos zener e varistores do tipo MOV e um filtro LC passabaixo de ligação à REE. De forma a garantir que as comutações dos semicondutores são

realizadas em segurança é utilizado um processo de comutação a quatro passos, baseado no

sinal das correntes de carga, implementado numa FPGA. O circuito de controlo digital,

implementado num DSP, executa a técnica de modulação PWM de Venturini. Para garantir o

adequado funcionamento do conversor é efectuada a aquisição das correntes de carga,

necessárias ao processo de comutação a quatro passos, e das tensões de entrada, necessárias

ao processo de modulação.

O CM construído foi testado, alimentando uma carga indutiva a partir da REE. Dos resultados

obtidos conclui-se que este funciona de acordo com o esperado, apresentando na saída tensões

comutadas e correntes sinusoidais típicas de um Conversor Matricial.

Palavras-Chave:

Conversor Matricial, Semicondutores de Potência, Interruptores

Bidireccionais, Modulação PWM de Venturini.

III

Abstract

The aim of this work is to design, build and test a prototype of a direct AC/AC power converter,

usually known as Matrix Converter (MC). When compared to an AC/AC indirect converter, it is

expected that the efficiency of this converter is higher, guaranteeing at the same time reduced

cost, volume and weight.

In this work the power module of the matrix converter is sized and built. This module includes the

association of power semiconductors performing as bidirectional switches, the semiconductors

driving circuits, the over voltage protection circuits using zener diodes and MOV varistors and a

low pass filter used to connect the converter to the grid. To guarantee the semiconductors safe

switching, a four step commutation strategy based on the load currents signals is used and

implemented in a FPGA. The digital control circuit is implemented in a DSP, using the Venturini

PWM modulation strategy. To guarantee the converter adequate operation, the load currents and

the grid voltages are measured as they are necessary to guarantee the semiconductors

commutation process, and necessary to the high frequency modulation strategy.

The matrix converter was tested feeding an inductive load from the grid. The obtained results are

according to the expected, showing the load switched voltages and nearly sinusoidal currents.

Keywords:

Matrix Converter, Power Semiconductors, Bidirectional Switches, Venturini PWM

Modulation.

IV

Índice

1. Introdução ........................................................................................................................................ 1

1.1 Enquadramento do tema de dissertação .............................................................................. 2

1.2 Objectivos da dissertação .................................................................................................... 3

1.3 Organização da dissertação ................................................................................................. 3

2. Dimensionamento de um Conversor Matricial .............................................................................. 4

2.1 Esquema Geral do Conversor Matricial ................................................................................ 4

2.1.1 Circuito de Potência ...................................................................................................... 5

2.1.2 Circuito de Comando .................................................................................................... 7

2.1.3 Circuito de Controlo ...................................................................................................... 8

2.1.4 Circuitos de Aquisição................................................................................................. 10

2.2 Dimensionamento .............................................................................................................. 12

2.2.1 Semicondutores de Potência ...................................................................................... 12

2.2.2 Dissipador ................................................................................................................... 13

2.2.3 Filtro de Entrada ......................................................................................................... 14

2.2.4. Circuitos de Protecção Contra Sobretensões ............................................................ 18

2.2.5 Dimensionamento do Circuito de Disparo ................................................................... 20

2.2.6 Fontes de Alimentação Comutadas ............................................................................ 25

2.2.7 Circuitos Auxiliares de Aquisição de tensões e correntes ........................................... 26

3. Circuito Impresso para o Conversor Matricial ............................................................................ 28

3.1. Esquema Geral da Placa de Circuito Impresso ................................................................. 28

3.2. Medidas a considerar para redução do ruído EMI............................................................. 29

3.3. Determinação da largura das pistas .................................................................................. 30

3.4. Determinação do espaçamento entre pistas ..................................................................... 32

3.5. Circuito de disparo ............................................................................................................ 32

3.6. Circuito do filtro de entrada e circuito de protecção .......................................................... 35

3.7. Layout global da placa de circuito impresso ...................................................................... 38

4. Ensaios Laboratoriais do Conversor Matricial ........................................................................... 39

4.1 Introdução .......................................................................................................................... 39

4.2. Teste de validação do circuito de disparo ......................................................................... 39

V

4.3. Teste de validação do circuito de aquisição das correntes ................................................ 42

4.4. Teste do funcionamento global do Conversor Matricial ..................................................... 43

5. Conclusões e Perspectivas de Trabalho Futuro ......................................................................... 45

5.1 Conclusões ......................................................................................................................... 45

5.2 Perspectivas de trabalho futuro .......................................................................................... 45

Referências......................................................................................................................................... 47

Anexos ................................................................................................................................................ 48

A: Lista de Componentes ......................................................................................................... 48

B: Datasheet do Módulo Integrado DANFOSS 1200V/25A (Interruptores Bidireccionais) ....... 50

C: Datasheet do Acoplador Óptico TLP250(INV) ..................................................................... 51

D: Datasheet das Fontes de Alimentação Comutadas NMV0515SC ....................................... 52

E: Datasheet do Módulo Integrado (dispositivo similar considerado no cálculo de perdas dos

módulos de potência) ............................................................................................................... 54

F: Programa de cálculo dos parâmetros do filtro de entrada .................................................... 55

G: Datasheet do Transdutor de Corrente (LA 25-NP) .............................................................. 57

H: Datasheet do Transdutor de Tensão (LV 25-P) ................................................................... 58

I: Datasheet do Varistor (V420LA20AP) ................................................................................... 59

J: Datasheet do Díodo de Zener (1N4647A) ............................................................................ 60

K: Layout do circuito impresso das camas “top layer” e “bottom layer” .................................... 62

K1 – Camada “top layer” ...................................................................................................... 62

K2 – Camada “bottom layer” ................................................................................................ 63

L: Fotografia do Conversor Matricial construído ....................................................................... 64

M: Condensadores do filtro de entrada e Circuito de Protecção .............................................. 64

VI

Lista de Figuras

Figura 2.1 – Esquema geral do Conversor Matricial ...................................................................... 4

Figura 2.2 – Esquema do circuito equivalente do Módulo Integrado (MI) – Interruptores

Bidireccionais (extraído do anexo B). ............................................................................................. 5

Figura 2.3 – Circuito de protecção da porta de comando do SP, com diodos de Zener em antisérie................................................................................................................................................ 7

Figura 2.4 – Comutação entre dois IB (sentido positivo da corrente) ............................................ 9

Figura 2.5 – Comutação entre dois IB (sentido negativo da corrente). ........................................ 10

Figura 2.6 - Esquemático do circuito de aquisição de correntes (extraído de [Anibal Menido e

José Antunes, 2002]).................................................................................................................... 11

Figura 2.7 – Esquema monofásico do filtro LC à entrada do Conversor Matricial, com resistência

de amortecimento representada por Z Rf, em paralelo com a bobine. ........................................... 14

Figura 2.8 – Resistências de descarga colocadas em paralelo com os condensadores do filtro de

entrada. ........................................................................................................................................ 17

Figura 2.9 – Representação do Circuito de Protecção a Varistores à entrada e saída do

Conversor Matricial....................................................................................................................... 18

Figura 2.10 – Curva característica do díodo de Zener................................................................. 20

Figura 2.11 – Circuito de disparo dos semicondutores de potência (extraído do datasheet do

integrado com a referência TLP250(INV), 2009). ......................................................................... 21

Figura 2.12 – Circuito de entrada do acoplador óptico. ............................................................... 21

Figura 2.13 – Resistência porta-emissor, RGE, para descarga das capacidades parasitas na

porta de comando do SP. ............................................................................................................. 22

Figura 2.14 – Circuito de análise do regime transitório do semicondutor de potência IGBT (J.

Silva, 2009)................................................................................................................................... 23

Figura 2.15 – Circuito RLC na porta de comando do IGBT. ........................................................ 24

Figura 2.16 – Esquema representativo dos pontos de emissor comum entre os semicondutores

de potência de cada um dos MI de potência. ............................................................................... 25

Figura 3.1 – Esquema Geral do Conversor Matricial. .................................................................. 28

Figura 3.2 – Diagramas para determinação das larguras das pistas do CI (extraído da norma

IPC-IC2221, 1998: 38) .................................................................................................................. 30

Figura 3.3 – Esquemático do circuito de disparo de um dos módulos de potência. .................... 33

Figura 3.4 – Layout do circuito de comando (face superior). ....................................................... 34

Figura 3.5 – Layout do circuito de comando (face inferior). ......................................................... 34

Figura 3.6 – Esquemático das fases de entrada e saída do Conversor Matricial ........................ 35

Figura 3.7 – Esquemático do circuito do filtro de entrada com resistências de descarga, R D, e

circuito de protecção com varistores. ........................................................................................... 36

Figura 3.8 – Layout do circuito do filtro de entrada com resistências de descarga, R D, e circuito

de protecção com varistores......................................................................................................... 37

Figura 3.9 – Layout global da placa de circuito impresso do Conversor Matricial (dupla camada).

..................................................................................................................................................... 38

VII

Figura 4.1 – Esquema da montagem laboratorial realizada para teste do CM............................. 39

Figura 4.2 – Esquema genérico do circuito de disparo (extraido do datasheet do acoplador óptico

com a referência TLP250(INV) da TOSHIBA)............................................................................... 40

Figuras 4.3 – Sinal de entrada do circuito de disparo, fornecido pelo circuito de controlo. .......... 40

Figura 4.4 – Sinal de comando imposto pelo circuito de disparo na porta de comando do

semicondutor de potência IGBT.................................................................................................... 41

Figura 4.5 – Sinal de entrada (CH1) e sinal de comando (CH2). ................................................. 41

Figura 4.6 – Teste do circuito de identificação do sentido e da localização das correntes de

carga. ............................................................................................................................................ 42

Figura 4.7 - Tensão simples de saída. ......................................................................................... 43

Figura 4.8 - Tensão composta de saída. ...................................................................................... 44

Figura 4.9 - Corrente de saída do Conversor Matricial. ............................................................... 44

VIII

Lista de Tabelas

Tabela 1 – Resultados obtidos no dimensionamento do filtro. ..................................................... 16

Tabela 2 - Resistências de amortecimento das oscilações. ......................................................... 25

Tabela 3 – Quadro resumo do número de fontes de alimentação. .............................................. 26

Tabela 4 – Conversões de unidades............................................................................................ 31

Tabela 5 - Níveis de afastamento entre as diversas pistas segundo diversos níveis de tensões

(tabela 6-1 Electrical Conductor Spacing página 39).................................................................... 32

IX

Lista de Símbolos

Factor de amortecimento

C

Constante de tempo de carga/descarga do condensador

Resistência equivalente interna do conversor

Frequência natural das oscilações não amortecidas

C

Capacidade

C

Capacidade equivalente (ligação em triângulo)

CCE

Capacidade equivalente parasita colector-emissor

CCG

Capacidade equivalente parasita colector-porta

Ceq

Capacidade equivalente

Cf

Condensador do filtro de entrada (capacidade)

CGE

Capacidade equivalente parasita porta-emissor

CISS

Capacidade de entrada

COSS

Capacidade de saída

CRSS

Capacidade de transferência inversa

Cs

Capacidade parasita equivalente

CY

Capacidade equivalente (ligação em estrela)

fC

Frequência de corte

FP

Factor de potência

frede

Frequência da rede

fS

Frequência de comutação

ICC

Corrente de Curto-Circuito

Ief

Valor eficaz da corrente

IF

Corrente de Threshold de entrada

Io

Corrente de saída

IPN

Corrente nominal no primário

Is

Corrente na fase do Conversor Matricial

ISN

Corrente nominal no secundário

IZ

Corrente de zener

Lf

Bobine do filtro de entrada (indutância)

X

LS

Indutância parasita equivalente

Po

Potência de saída

PRd

Potência da resistência de descarga

PVA

Potência (Volt-Ampere)

PW

Potência (Watt)

PZ

Potência dissipada no díodo de zener

Q

Factor de qualidade

Rd

Resistência de descarga (do condensador do filtro de entrada)

Rf

Resistência de amortecimento do filtro de entrada

RG

Resistência de amortecimento das oscilações de porta

RG2

Resistência de amortecimento das oscilações de porta

RGE

Resistência de descarga porta-emissor

RIN

Resistência de entrada do circuito de disparo

Rths-a

Resistência térmica dissipador-ambiente

Tj

Temperatura de junção

VCA

Tensão de circuito aberto

VCC

Tensão de curto-circuito

VCC

Tensão de alimentação do fotodiodo

VDC

Tensão da fonte DC

Vef

Valor eficaz de tensão

VLED

Tensão de polarização do LED

VLSTTL

Tensão de polarização da porta inversora

Vo

Tensão de saída

Vs

Tensão composta nas fases do Conversor Matricial

VV

Tensão de trabalho do varistor

VZ

Tensão de Zener

Zcarga

Impedância de Carga

ZCf

Impedância do condensador (filtro de entrada)

Zf

Impedância característica do filtro de entrada

ZLf

Impedância da bobine (filtro de entrada)

XI

ZRf

Impedância da resistência de amortecimento (filtro de entrada)

Zth

Impedância de Thévenin

XII

Lista de Acrónimos

AC

Alternating Current

CI

Circuito Impresso

CM

Conversor Matricial

DC

Direct Current

DIR

Direction Control Input

DSP

Digital Signal Processor

EMI

Electromagnetic Interference

FPGA

Field Programmable Gate Array

GND

Ground

GS

Gerador Síncrono

IB

Interruptor Bidireccional

IGBT

Insulated Gate Bipolar Transistor

LED

Light Emitting Diode

MC

Matrix Converter

MIDA

Máquina de Indução Duplamente Alimentada

MOV

Metal Oxide Varistor

OE

Output Enable

PWM

Pulse Width Modulation

REE

Rede de Energia Eléctrica

SEE

Sistema de Energia Eléctrica

SP

Semicondutor de Potência

SPC

Semicondutor de Potência Comandado

SVM

Space Vector Modulation

XIII

1. Introdução

Os conversores electrónicos de potência AC-AC permitem transferir energia de uma fonte

alternada sinusoidal para uma carga, sob a forma de grandezas eléctricas alternadas sinusoidais,

com tensões, correntes ou frequência diferentes da fonte. De uma forma genérica, estes

conversores são constituídos por semicondutores de potência que operam em comutação, a uma

frequência que deverá ser muito superior à frequência fundamental das grandezas (tensões e

correntes) de entrada e de saída do conversor.

Os conversores AC-AC podem ser classificados em dois grupos distintos: os conversores

indirectos (AC-DC-AC) e os conversores AC-AC directos. De um modo geral, os conversores

indirectos são constituídos pela associação de dois conversores: um rectificador (conversão ACDC) e um inversor (conversão DC-AC). Estes dois conversores são ligados através de um andar

intermédio DC de armazenamento de energia, habitualmente constituído por condensadores

electrolíticos, que aumentam de forma considerável o peso e as dimensões do conversor,

originando também perdas adicionais, com consequente redução do rendimento global.

Nas últimas décadas, o desenvolvimento da indústria de semicondutores tem permitido a sua

operação a tensões, correntes e frequências de comutação mais elevadas. Simultaneamente, o

aparecimento de módulos integrados de semicondutores de potência, que permitiram o aumento

de densidade de potência e a redução de efeitos parasitas, associado à melhoria dos circuitos de

comando e controlo, têm tornado cada vez mais atractiva a utilização dos conversores AC/AC

directos.

Os Conversores Matriciais ou conversores AC/AC directos, não têm andar DC intermédio de

armazenamento de energia, podendo garantir rendimentos elevados, maior densidade de

potência, com consequente diminuição do peso, dimensões e custo. Têm, no entanto, a

desvantagem de serem mais sensíveis às perturbações das tensões / correntes de entrada e de

saída do conversor. Esta desvantagem é minimizada através da utilização de filtros, circuitos de

protecção e controladores adequados.

Os Conversores Matriciais são também conhecidos por conversores directos de frequência sem

restrições, uma vez que são caracterizados por permitir a variação da frequência fundamental

das tensões de saída, sem qualquer restrição em relação à frequência da fonte sinusoidal de

entrada (as limitações são impostas unicamente pela frequência de comutação dos

semicondutores e pelos circuitos de comando e de disparo utilizados). Estes conversores

permitem ainda regular o valor eficaz das tensões aplicadas na carga e o factor de potência de

entrada e de saída (Pinto, 2003), garantindo o trânsito bidireccional de energia (à semelhança

dos conversores AC-DC-AC usuais). A comutação a frequências elevadas permite que o ruído de

comutação seja superior à banda de frequências áudio.

1

O sistema de potência que constitui o conversor tem de ser comandado e é necessário utilizar

uma estratégia de comutação que permita colocar, em segurança, os semicondutores no estado

de funcionamento pretendido (ao corte ou à condução). Existem algumas técnicas de comando,

sendo a técnica de modulação PWM de Venturini uma das mais utilizadas, uma vez que

apresenta bons desempenhos e o algoritmo de controlo pode ser facilmente implementado em

DSP (Watthanasam et al, 1996). Por esse motivo, será esta a técnica de modulação utilizada nos

ensaios de teste deste Conversor Matricial.

Os conversores matriciais têm uma vasta gama de utilização, nomeadamente em sistemas de

velocidade variável, como são os sistemas de centrifugação, elevadores, escaladores e ainda, os

sistemas de geração de energia eólica, baseados em geradores síncronos e máquinas de

indução duplamente alimentadas (MIDA) (http://www.yaskawa.com/site).

É com o objectivo de estudar e de adquirir competências relacionadas com a Conversão Matricial

que, neste trabalho de dissertação, se irá construir e testar um protótipo laboratorial de um

conversor matricial para posterior avaliação de desempenho e análise de resultados.

1.1 Enquadramento do tema de dissertação

Nos últimos anos, o aumento da carga eléctrica aliado ao facto dos combustíveis fósseis

(petróleo, carvão, o gás natural, e produtos nucleares) serem uma fonte de energia poluente e

não renovável, têm motivado um aumento substancial do interesse em fontes de energia

alternativas. Tem crescido, assim, a aposta no desenvolvimento de soluções tecnologicamente

inovadoras, aplicáveis aos processos de conversão de energia eléctrica, a partir de matériasprimas não poluentes e renováveis.

As melhorias tecnológicas dos equipamentos têm possibilitado aumentar a integração e melhorar

a eficiência de novos centros de produção, no Sistema de Energia Eléctrica (SEE), tendo como

base as energias renováveis, não poluentes e baratas.

Este trabalho de dissertação vai ao encontro desta nova orientação adoptada pelas sociedades

actuais, em que se pretende o desenvolvimento de competências e de soluções tecnológicas que

potenciem a área das energias renováveis, obtendo-se resultados cada vez mais satisfatórios e

benéficos às sociedades que nelas apostam.

É neste contexto actual, que se pretende, neste trabalho de dissertação, projectar, construir e

testar um protótipo laboratorial de Conversor Matricial (conversor electrónico de potência AC/AC

directo), que em desenvolvimentos futuros, possa ser aplicado e testado nesta situação.

2

1.2 Objectivos da dissertação

Este trabalho, tem como principal objectivo a construção e validação de um protótipo laboratorial

de um conversor electrónico de potência AC/AC directo, normalmente designado por Conversor

Matricial, o que inclui:

- o projecto, dimensionamento e construção do Conversor Matricial;

- implementação laboratorial do Conversor Matricial;

- teste, avaliação de desempenho do protótipo laboratorial e respectiva análise de

resultados.

1.3 Organização da dissertação

Esta dissertação está organizada em seis capítulos, bibliografia e anexos.

No Capítulo I é realizada a introdução ao tema deste trabalho de dissertação. É feito um

enquadramento do tema de dissertação como sendo uma inovação tecnológica que poderá

potenciar a área das energias renováveis, tema este que tem sido bastante debatido pelas

sociedades actuais. São ainda revelados os objectivos deste trabalho e a sua organização;

No capítulo II, que constitui o capítulo fundamental desta tese, é apresentado o esquema geral

do Conversor Matricial. De seguida, são explicados todos os dimensionamentos realizados para

os diferentes circuitos do conversor, tendo sempre como objectivo optimizar o seu

funcionamento.

No Capítulo III são apresentados os esquemáticos e respectivo layout para construção da placa

de circuito impresso, que será a base para a construção do Conversor Matricial. São indicados

os cuidados tidos em conta na concepção das placas de circuito impresso de forma a minimizar o

ruído resultante das interferências electromagnéticas entre as pistas dos diferentes circuitos.

No Capítulo IV são descritos os ensaios laboratoriais realizados e apresentados os respectivos

resultados obtidos.

No Capítulo V são apresentadas as conclusões resultantes do trabalho desenvolvido e ainda as

perspectivas de trabalho futuro.

3

2. Dimensionamento de um Conversor Matricial

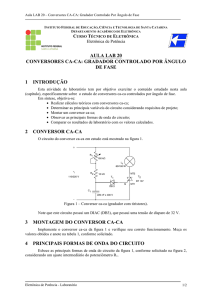

Neste capítulo é apresentado o esquema geral do Conversor Matricial, com uma breve descrição

do mesmo. De seguida, são apresentados todos os dimensionamentos referentes aos circuitos

do conversor a construir.

2.1 Esquema Geral do Conversor Matricial

A figura 2.1 apresenta a composição geral do Conversor Matricial a construir, incluindo uma

perspectiva geral da interligação dos diferentes circuitos.

Dissipador

Filtro de Entrada

Semicondutores de Potência

(Interruptores Bidireccionais)

S11

Circuito de

Protecção

(entrada)

R

Circuito de

Protecção

(saída)

R

S12

W

S13

W

S21

U

S22

S

S

U

S23

S31

V

S32

V

S33

T

T

Isolamento Galvânico

1

Fontes de

Alimentação

Comutadas

...

18

Circuito de Comando

(Acopladores Ópticos)

+15V

0V

-15V

1

Circuitos de

Aquisição de

Tensões

...

18

Estratégia de

Comutação a Quatro

Passos

(FPGA)

1

...

18

Modulação PWM de

Venturini

(DSP)

Circuito de Controlo

Figura 2.1 – Esquema geral do Conversor Matricial

4

Circuitos de

Aquisição de

Correntes

Circuito de

detecção do

sinal de

corrente

No esquema geral do conversor, há quatro tipos de circuitos a destacar. São eles o circuito de

potência, o circuito de comando, o circuito de controlo e os circuitos auxiliares de aquisição.

2.1.1 Circuito de Potência

Do circuito de potência fazem parte: os semicondutores de potência, o filtro de entrada LC e os

circuitos de protecção dos semicondutores.

Semicondutores de Potência

No Conversor Matricial pretende-se que o processamento de energia eléctrica seja efectuado de

forma bidireccional, ou seja, tanto da REE para a carga como da carga para a REE. Para que

isto seja possível têm de ser utilizados dois semicondutores de potência comandados ligados em

anti-série, com dois diodos em anti-paralelo (Fig. 2.2), de modo que as correntes com sentidos

diferentes atravessem transístores e diodos diferentes. Formam-se assim Interruptores

Bidireccionais, ou seja, com comando à condução e ao corte e a possibilidade de ser percorridos

por correntes e suportar tensões nos dois sentidos, garantindo o trânsito bidireccional de energia.

Neste trabalho, para realização dos IB, utilizaram-se módulos integrados de potência da

DANFOSS (anexo B). Cada um destes módulos inclui três Interruptores Bidireccionais, estando

os respectivos semicondutores comandados, transístores IGBT, ligados em colector comum, de

acordo com a figura 2.2.

Figura 2.2 – Esquema do circuito equivalente do Módulo Integrado (MI) – Interruptores Bidireccionais

(extraído do anexo B).

5

A utilização destes módulos integrados de potência traz vantagens na implementação prática do

Conversor Matricial, pois permitem reduzir significativamente o volume do circuito de potência,

reduzindo substancialmente o tamanho do protótipo laboratorial.

Filtro de Entrada

No interface entre a Rede de Energia Eléctrica (REE) e os semicondutores de potência que

compõem os interruptores bidireccionais, utilizou-se um filtro passa-baixo LC. Com este filtro

pretendem minimizar-se as harmónicas de alta frequência das correntes de entrada, que

resultam do processo de comutação dos semicondutores dos IB, de forma a preservar a

qualidade da energia do SEE. Por isso, é necessário realizar um dimensionamento criterioso do

filtro, de forma a que este contribua para uma melhoria significativa do desempenho do conversor

matricial a construir.

De entre várias topologias possíveis, escolheu-se a topologia LC com resistência de

amortecimento em paralelo com a bobine (Fig. 2.1) porque, apesar de outras soluções

permitirem igualmente reduzir o conteúdo harmónico das correntes de entrada, em geral, esta

topologia com a resistência de amortecimento em paralelo com a bobina é a que permite

minimizar as perdas (Pinto, 2003). Consequentemente, consegue obter-se um maior rendimento

do Conversor Matricial.

Circuitos de Protecção

O circuito de protecção tem como finalidade proteger os semicondutores de potência de

sobretensões aos seus terminais. Durante o processo de comutação dos semicondutores, no

caso de ocorrer uma falha de comutação entre os IB que leve ao corte das correntes de carga

indutivas (variação muito rápida da corrente na carga, ou seja, derivada de corrente de valor

elevado), existe um crescimento abrupto da tensão aos terminais dos semicondutores. Estes

crescimentos de tensão podem levar a que sejam ultrapassados os valores máximos suportáveis

pelos IGBT (sobretensões), e consequentemente dar origem à sua destruição.

No protótipo laboratorial utilizam-se varistores de potência, como circuito de protecção contra

sobretensões. Os varistores de potência são componentes electrónicos, normalmente utilizados

para protecção de dispositivos semicondutores de potência, e são caracterizados por limitarem

tensões ao valor definido pelo fabricante. Caso a tensão aos seus terminais exceda o valor para

o qual foi dimensionado, essa sobretensão é dissipada na forma de calor pelo varistor, dando-se

um aquecimento da sua cápsula. Caso a sobretensão permaneça, o varistor limita o valor de

tensão funcionando como uma fonte de tensão com uma resistência interna e o dispositivo a

proteger é salvaguardado. Os varistores utilizados neste trabalho, têm a referência V420LA20AP

e são varistores do tipo MOV (Metal Oxide Varistor). Com estes varistores de potência, é

6

possível reduzir significativamente o volume do circuito de protecção diminuindo, de igual forma,

as dimensões do Conversor Matricial.

Por outro lado, em caso de ocorrência de sobretensões na porta do IGBT, sobretudo devido à

existência de indutâncias parasitas nas pistas entre o circuito de disparo e os semicondutores, é

aplicada uma tensão na porta do semicondutor superior ao admissível o que pode causar a sua

destruição. Tratando-se, neste caso, de tensões bastante menores, a protecção do terminal de

comando do IGBT pode ser realizada colocando entre os terminais porta-emissor do

semicondutor dois diodos de zener dispostos em anti-série, em ligação de ânodo comum. Os

diodos de zener criam um caminho alternativo para a corrente sempre que ocorre uma

sobretensão entre os seus terminais, limitando e estabilizando a tensão na porta de comando

dos IGBT.

RGE

Figura 2.3 – Circuito de protecção da porta de comando do SP, com diodos de Zener em anti-série.

2.1.2 Circuito de Comando

O circuito de disparo tem como função colocar à condução ou ao corte os semicondutores dos

IB, utilizando a informação que é fornecida pelo circuito de controlo. Este circuito é, basicamente,

constituído por acopladores ópticos que garantem o isolamento galvânico entre o circuito de

potência e o circuito de controlo.

Acoplador Óptico

Os acopladores ópticos são dispositivos constituídos por um diodo emissor de luz LED e por um

fotodiodo ou fototransistor. As entradas e saída dos acopladores ópticos encontram-se isoladas

electricamente. O funcionamento deste dispositivo baseia-se na energia libertada pelo LED sob a

forma de fotões que, atravessando o meio electricamente isolante, colocam o fotodíodo ou

fototransistor em condução (J. Silva, 2009).

7

Uma vez que no circuito de potência existem tensões elevadas não referenciadas ao mesmo

ponto de massa que o circuito de comando, com a utilização destes acopladores ópticos

consegue-se promover um isolamento galvânico entre os dois circuitos.

O acoplador óptico utilizado neste trabalho, tem a referência TLP250(INV) (anexo C).

Fontes de Alimentação Comutadas

Estas fontes de alimentação são isoladas, isto é, os terminais de polarização (primário) estão

galvanicamente isolados dos terminais de saída (secundário). Têm como objectivo alimentar os

circuitos de disparo e o número de fontes de alimentação necessárias depende da topologia dos

IB e é dimensionado no capítulo 2.2.

As fontes de alimentação isoladas utilizadas neste trabalho têm a referência NMV0515SC (anexo

D).

Octal Bus Transciever

Estes dispositivos funcionam como buffers dos sinais provenientes do circuito de controlo (FPGA

+ DSP).

2.1.3 Circuito de Controlo

O circuito de controlo é constituído por um DSP, onde estão implementados os algoritmos de

modulação, e por uma FPGA programada para realizar a estratégia de comutação a quatro

passos, garantindo que a comutação entre os semicondutores de potência é feita em segurança.

Modulação PWM de Venturini

Nos processos de modulação a alta frequência existentes para o Conversor Matricial, os

algoritmos que apresentam melhores desempenhos são: a modulação PWM de Venturini

(Alesina et al, 1981) e a modulação vectorial SVM (Huber, Borojevic, 1992). Ambos os processos

de modulação podem ser facilmente implementados em DSP (Watthanasarn et al,1996)

permitindo velocidades de processamento adequadas.

Em ambos os processos de modulação as tensões pretendidas na saída são obtidas a partir de

fracções das tensões de entrada do conversor. As correntes pretendidas na entrada são obtidas

a partir de fracções das correntes de saída do conversor.

Neste trabalho utiliza-se o método de modulação PWM de Venturini, uma vez que apresenta

baixos conteúdos harmónicos tanto nas tensões de saída como nas correntes de entrada e

permite um factor de potência quase unitário (ou ajustável) na ligação à REE (J. Monteiro, 2010).

8

Estratégia de Comutação a 4 Passos

Esta estratégia de comutação pode ser baseada na detecção do sentido da corrente de carga ou

na detecção do sinal das tensões compostas de entrada aplicadas aos IB envolvidos no

processo de comutação.

A estratégia utilizada neste trabalho foi a de comutação a quatro passos, baseada no sentido da

corrente na carga e implementada em FPGA (Monteiro, 2010). Esta escolha deve-se ao facto de

ser a estratégia que garante maior segurança nas transições e ainda evita a circulação de

corrente entre os IB que se encontram em comutação (Monteiro, 2010).

Quando é dada ordem a um IB para conduzir, ambos os IGBT que o constituem estão à

condução, independentemente do sinal de corrente na carga. Supondo que se pretende comutar

a corrente do IB1 para o IB2 e que o sentido da corrente de carga é positivo, a comutação

realizada em quatro passos, correspondentes a quatro ciclos de relógio (quatro ciclos

temporizados pela FPGA) (Monteiro, 2010), é feita da seguinte forma:

Figura 2.4 – Comutação entre dois IB (sentido positivo da corrente)

1º - O semicondutor T1, que não participa no processo de condução, é desligado;

2º - Para se garantir a continuidade da corrente, o semicondutor T4 do IB2, é colocado à

condução;

3º - De seguida, coloca-se o semicondutor T2 do IB1, que estava no estado de condução, ao

corte;

4º - Por fim, coloca-se o semicondutor T3 do IB2, à condução;

9

Se o sentido da corrente de carga for negativo a comutação é também realizada em quatro

passos, no entanto a sequência destes é diferente da realizada para o caso com corrente de

carga com sentido positivo, ou seja:

Figura 2.5 – Comutação entre dois IB (sentido negativo da corrente).

1º - O semicondutor T2, que não participa no processo de condução, é desligado;

2º - Para se garantir a continuidade da corrente, o semicondutor T3 do IB2, é colocado à

condução;

3º - De seguida, coloca-se o semicondutor T1 do IB1, que estava no estado de condução, ao

corte;

4º - Por fim, coloca-se o semicondutor T4 do IB2, à condução;

Quando o sentido da corrente de carga se alterada durante o processo de comutação, este é

finalizado considerando o sinal inicial da corrente. Só no ciclo de comutação seguinte é que se

irá actualizar o sinal da corrente.

2.1.4 Circuitos de Aquisição

Os circuitos de aquisição, designados também por circuitos auxiliares, têm a função de obter

imagens das tensões e correntes, na entrada e saída do conversor. É com base nesta

informação que se torna possível realizar o controlo das comutações dos semicondutores de

potência do CM.

10

Circuito de Aquisição de Correntes

É com base no circuito de aquisição das correntes que é possível identificar as zonas das

correntes de saída e determinar o sentido das correntes de carga, necessário ao processo de

comutação a quatro passos.

Para leitura das correntes são utilizados transdutores de corrente LEM, cuja referência é LA 25NP. Este componente permite realizar a medição electrónica de correntes, em circuitos de

potências elevadas, garantindo o isolamento galvânico entre o circuito de potência e o circuito de

comando. Na entrada é ligado o circuito de potência, onde está a grandeza a medir, e a saída

liga-se ao circuito electrónico, que no caso deste trabalho, é o circuito de controlo.

A partir da leitura realizada pelo transdutor de corrente, utiliza-se o circuito de acondicionamento

de sinal (Menino, Antunes, 2002) representado na Fig. 2.6 e descrito de seguida.

Bloco 1

Bloco 2

Bloco 3

Figura 2.6 - Esquemático do circuito de aquisição de correntes (extraído de [Anibal Menido e José

Antunes, 2002]).

De seguida, descrevem-se os blocos do circuito que implementa as funções de identificação do

sentido e de localização das correntes de carga. Assim, temos:

- No bloco 1, o circuito apresentado realiza o cálculo de uma tensão cujo valor é

proporcional ao valor da corrente que o percorre. Os díodos colocados em anti-paralelo permitem

adicionar uma tensão, positiva ou negativa de acordo com o sinal da corrente adquirida, de forma

a tornar mais acentuadas as transições da corrente entre o sentido negativo e o positivo,

tornando-se mais fácil detectar a passagem por zero;

11

- No bloco 2 está realizado o circuito onde são calculadas as tensões proporcionais às

correntes;

- No circuito do bloco 3 são determinados os sinais das correntes e os sinais das diferenças das

correntes, adquiridas pelos blocos 1 e 2 através de comparadores regenerativos não inversores.

Circuito de Aquisição de Tensões

Com o circuito de aquisição de tensões, pretende-se adquirir uma imagem das tensões

compostas entre as fases de entrada do conversor. O valor desta imagem irá servir para realizar

o processo de modulação do Conversor Matricial, segundo a estratégia de comando PWM de

Venturini.

Para aquisição das tensões de entrada, utilizam-se transdutores de tensão LEM, com a

referência LV 25-P. Este componente, permite realizar a medição de tensões, em circuitos de

potências elevadas, garantindo o isolamento galvânico entre o terminal primário (tensões

elevadas) e o secundário (baixas tensões). No primário é ligado o circuito de potência e no

circuito secundário, o circuito electrónico, que no caso deste trabalho, é o circuito de controlo.

2.2 Dimensionamento

Neste subcapítulo são realizados todos os dimensionamentos necessários à construção do

conversor de potência. Nos dimensionamentos efectuados são indicadas as aproximações

consideradas os resultados obtidos.

2.2.1 Semicondutores de Potência

Os semicondutores a escolher para realização dos Interruptores Bidireccionais do circuito de

potência são escolhidos tendo em consideração as condições de funcionamento pretendidas

para o conversor de potência, que são:

- Correntes nominais IN = 10A;

- Tensão nominal de entrada UN = 400VAC;

- Frequência de comutação da ordem de f S = 5kHz.

12

Tendo em conta estes valores e, de modo a garantir menor volume do conversor e melhor

desempenho, escolheram-se módulos integrados de potência da DANFOSS de 1200V, 25A, que

permitem obter frequências de comutação na gama pretendida. Estes módulos integram

transístores IGBT, com ligação em colector comum e respectivos díodos em anti-paralelo,

formando três interruptores bidireccionais.

Para construir um Conversor Matricial Trifásico, são necessários três destes módulos de potência

(1 braço de potência por cada uma das fases).

2.2.2 Dissipador

O dimensionamento do dissipador a utilizar é realizado considerando as perdas dos

semicondutores do Conversor Matricial. Sabendo que tipicamente os semicondutores de

potência IGBT suportam temperaturas de junção, Tj, de 125ºC antes da sua destruição, é

imperativo que o dissipador possua uma resistência térmica R ths-a (dissipador - meio ambiente)

que permita dissipar a potência de perdas resultante dos processos de comutação e condução

dos semicondutores de potência existentes em cada um dos módulos de potência.

Uma vez que o conversor foi dimensionado para uma potência de saída de 6kVA, admitindo que

o conversor tem um rendimento mínimo de 90%, ou seja, um máximo de 10% de perdas, entre

os dissipadores disponíveis no mercado selecciona-se um que permita dissipar este valor de

perdas sem que seja atingido a temperatura máxima admissível para o correcto funcionamento

dos semicondutores de potência, ou seja, sem que ocorra a sua destruição.

Assim, considerando um dissipador disponível no mercado com uma resistência térmica de

0,075ºC/W, o aumento de temperatura a que os semicondutores estarão sujeitos é obtida de

acordo com (2.1), onde PW representa a potência de perdas, PVA é a potência aparente e F P é o

factor de potência do conversor.

(2.1)

Considerando-se um factor de potência do conversor aproximadamente unitário, podemos dizer

que a potência activa de perdas tem o mesmo valor da respectiva potência aparente:

(2.2)

assim,

600W 0.075º C / W 45º C

13

(2.3)

Tendo em conta uma temperatura laboratorial ambiente de 25ºC, uma elevação de temperatura

de 45ºC fará com que o dissipador fique a uma temperatura máxima de 70ºC, permitindo o

funcionamento dos semicondutores até à temperatura de junção máxima admissível, ou seja,

125ºC.

Consultando-se o catálogo de fabrico do módulo integrado de um dispositivo similar (anexo E),

verifica-se que as perdas de comutação mais as perdas de condução, por módulo de potência,

para as condições nominais de funcionamento do módulo (VCE = 1200V, I = 25A, fs = 5 kHz), são

de 180W, ou seja:

(2.4)

Como são necessários três módulos de potência, no total teremos 540W de perdas, o que

permite confirmar que são esperadas sensivelmente 10% de perdas, tal como referido

anteriormente.

2.2.3 Filtro de Entrada

O filtro de entrada utilizado no Conversor Matricial é idêntico ao filtro LC representado no

esquema monofásico da figura 2.2.

ZRf

Conversor Matricial

I0

ZLf

U

ZCf

ri

V0

Figura 2.7 – Esquema monofásico do filtro LC à entrada do Conversor Matricial, com resistência de

amortecimento representada por ZRf, em paralelo com a bobine.

As impedâncias representativas de cada um dos componentes do filtro são descritas pelas

equações (2.5), (2.6) e (2.7), onde

:

(2.5)

(2.6)

(2.7)

14

Para determinação dos parâmetros do filtro é necessário determinar a sua função de

transferência, que se obtém fazendo:

(2.8)

Tendo em conta que se trata de um filtro passa baixo de segunda ordem, os seus parâmetros

podem ser determinados igualando os quocientes do polinómio denominador da equação (2.8)

com os quocientes da equação canónica de segunda ordem, dada por (2.9).

;

(2.9)

O filtro LC pode ser caracterizado pela frequência das oscilações não amortecidas (2.10) e pela

impedância característica (2.11):

(2.10)

(2.11)

Para se garantir o amortecimento

desejado, a resistência de amortecimento será dada por:

;

(2.12)

Consequentemente, de (2.10) e (2.11) obtêm-se os outros parâmetros do filtro:

(2.13)

(2.14)

Para além destes parâmetros, podemos calcular ainda o factor de qualidade que caracteriza o

filtro de entrada através da seguinte expressão:

(2.15)

De forma a obtermos um filtro de segunda ordem à entrada do Conversor Matricial, é necessário

realizar o dimensionamento de

garantindo que o filtro consegue atenuar as harmónicas de alta

frequência introduzidas pela comutação dos semicondutores. Para isto, a frequência de corte

15

escolhida para o filtro em questão deverá estar uma década acima da frequência da rede

(

) e uma década abaixo da frequência de comutação dos semicondutores, que é

:

(2.16)

Ou seja,

(2.17)

Assim, foi escolhida para o filtro LC uma frequência de corte de

Para determinação da resistência equivalente do conversor,

.

, considera-se que o sistema de

controlo do Conversor Matricial impõe um factor de potência quase unitário, ou seja:

(2.18)

(2.19)

Obtendo-se para resistência equivalente do conversor:

;

(2.20)

Para o correcto funcionamento do filtro de entrada, a impedância característica deste deverá ser

muito inferior à impedância equivalente do conversor

.

(2.21)

Dimensionando o filtro de entrada para uma potência de saída de 2 kW (

, com

uma tensão composta de 400V e considerando um factor de potência aproximadamente unitário,

os valores calculados para os parâmetros são os apresentados na tabela 1:

Valores Considerados

0.5

500

Resultados

2000

8

13.3

2.5

Tabela 1 – Resultados obtidos no dimensionamento do filtro.

Estes resultados foram obtidos por intermédio de um programa realizado em MATLAB,

realizando-se a simulação dos resultados da tabela 1 para diversos valores de potência de saída

do Conversor Matricial (anexo F).

16

É preciso ter em atenção que os valores obtidos pelo programa são referentes a um filtro ligado

em estrela. Para se determinar o valor de capacidade referente à ligação em triângulo é

necessário dividir o valor obtido no programa (anexo B), por três, ou seja:

(2.22)

Paralelamente aos condensadores de polipropileno do filtro de entrada (Fig. 2.8), é necessário

introduzir uma resistência adicional, denominada por resistência de descarga, que tem como

finalidade dissipar a energia armazenada no condensador depois do conversor ser desligado.

R

RD

RD

S

RD

T

Figura 2.8 – Resistências de descarga colocadas em paralelo com os condensadores do filtro de

entrada.

A resistência de descarga é dimensionada considerando que, no processo de descarga, o

condensador atinge a tensão residual aos seus terminais em 20 segundos.

A constante de tempo de descarga de um condensador é dada por:

(2.23)

De forma a dimensionar a resistência, define-se que:

(2.24)

Considerando os resultados obtidos para o condensador do filtro, a resistência de descarga é

dada por (2.25):

(2.25)

Para o cálculo da resistência, para além do tempo de descarga do condensador também é

necessário calcular a potência que a resistência terá de dissipar quando ligada aos terminais do

17

condensador do filtro de entrada. Essa potência de perdas é dada por (2.26), onde Vef representa

o valor eficaz da tensão composta aos terminais da resistência RD.

(2.26)

Assim, as perdas na resistência de descarga são dadas por (2.27):

(2.27)

Tendo em conta as resistências existentes no mercado, selecciona-se uma resistência de

descarga com o valor de 1,5M, de potência 0,5W.

2.2.4. Circuitos de Protecção Contra Sobretensões

Varistores

Para protecção dos semicondutores de potência contra sobretensões são ligados três varistores

entre as fases de entrada do conversor e também são ligados três varistores entre as fases de

saída do conversor (figura 2.9).

Is

Vs

Conversor

Matricial

Circuito de

protecção

(entrada)

Circuito de

protecção (saída)

Figura 2.9 – Representação do Circuito de Protecção a Varistores à entrada e saída do Conversor

Matricial.

Para a correcta escolha dos varistores a utilizar, estes devem ser dimensionados tendo em conta

os seguintes critérios (J. Silva, 2009):

- A tensão de trabalho do varistor,

, deve ser superior à tensão máxima da fonte de

alimentação;

18

- Deve suportar, durante a duração , o transitório mais desfavorável com a tensão de

trabalho

, a corrente , que resulta desse transitório;

- Deve poder dissipar a energia do transitório mais gravoso:

(2.28)

De acordo com as condições referidas anteriormente, para realizar dimensionamento dos

varistores calcula-se a quantidade de energia susceptível de ser dissipada, num ciclo de rede,

em caso de sobretensão entre fases de entrada ou saída do conversor matricial. Assim, seja a

tensão composta entre cada duas fases:

(2.29)

Sabendo que nos ensaios experimentais as correntes nas fases não excederão

, a

energia que os varistores terão de dissipar num ciclo da rede, será dada por (2.30):

(2.30)

Tendo em conta o valor de energia a dissipar, com base nos valores dos catálogos fornecidos

pelos fabricantes (anexo I), selecciona-se um varistor com a capacidade de dissipação de

energia logo acima de

.

Diodos de Zener

Os diodos de zener devem ser escolhidos de acordo com os seguintes critérios:

- A tensão de zener, VZ (Fig. 2.10) cujo valor é especificado no respectivo datasheet

(anexo J) para uma determinada corrente de zener de teste, IZT;

- A corrente de zener, IZ;

- E a sua potência de dissipação, PZ, dada por:

(2.31)

Para assegurar que o diodo de zener não é destruído, é necessário garantir que a sua potência

de dissipação não é ultrapassada.

19

Figura 2.10 – Curva característica do díodo de Zener.

Uma vez que se irá aplicar na porta de comando do IGBT uma onda quadrada de amplitude

15V , deve escolher-se um díodo com uma tensão de zener que assegure a protecção do

IGBT, ou seja, que limite a tensão na porta do IGBT para um valor inferior ao admissível por este

e um pouco superior à amplitude máxima da onda quadrada.

Relativamente ao valor de potência de dissipação a escolher para o diodo de zener, uma vez que

se pretendem limitar tensões baixas, na ordem dos

as correntes são bastante baixas, da ordem dos

com potências de dissipação de

15V , e tendo em conta que na porta do IGBT

mA , podem escolher-se diodos zener de sinal

1W .

2.2.5 Dimensionamento do Circuito de Disparo

Resistência limitadora da corrente de entrada do acoplador óptico

Nesta secção é realizado o dimensionamento da resistência de entrada do acoplador óptico.

Pretende-se que esta resistência limite a corrente de funcionamento do LED, em regime de

comutação, a 8mA.

20

Figura 2.11 – Circuito de disparo dos semicondutores de potência (extraído do datasheet do

integrado com a referência TLP250(INV), 2009).

Consultando o datasheet do fabricante do integrado do acoplador óptico, verifica-se que a

resistência a colocar na entrada do pino 2 (LED ANODE) do acoplador óptico tem o valor de

390. No entanto, esta resistência pode ser calculada tendo em conta o esquema da figura 2.11,

detalhado na figura 2.12.

Vcc

IF

5V

RIN

2

LED

3

NOT

Figura 2.12 – Circuito de entrada do acoplador óptico.

Realizando a malha deste circuito, obtém-se:

VCC I F R VLED VLSTTL

(2.32)

Consultando o datasheet do acoplador óptico, verifica-se que em regime de comutação o LED

necessita de uma corrente de IF=8mA. Sabe-se ainda que o LED é polarizado por uma tensão de

5V.

Considerando uma tensão típica no LED e na porta inversora LSTTL (NOT), respectivamente, de

1.5V e 0.5V obtém-se;

R

VCC VLED VLSTTL 5 1.5 0.5

375

IF

0.008

21

(2.33)

Resistência de descarga porta-emissor, RGE

Durante o processo de comutação dos semicondutores de potência, as capacidades parasitas

nos terminais dos semicondutores realizam processos de carga e descarga de energia. Para

dissipar a energia resultante dos processos de descarga da capacidade parasita de entrada do

semicondutor, é necessário colocar em paralelo com esta, uma resistência de descarga,

denominada por RGE.

CISS

RGE

Figura 2.13 – Resistência porta-emissor, RGE, para descarga das capacidades parasitas na porta de

comando do SP.

A determinação do valor desta resistência é realizado de forma aproximada, pois não dispomos

dos valores de catálogo correctos da capacidade de entrada e do tempo máximo de comutação

dos semicondutores. Devido a este facto, consultando o catálogo de um semicondutor similar,

admite-se para capacidade de entrada um valor típico para este parâmetro, ou seja,

CISS 2.5nF .

Em relação à constante de tempo de descarga da capacidade, considera-se também uma

constante de tempo típica máxima de

.

Considerando que a constante de tempo do condensador é:

(2.34)

O valor da resistência é de:

(2.35)

Escolheu-se para implementação prática, um valor de resistência, uma grandeza acima do valor

dimensionado, ou seja,

.

22

Resistência de amortecimento das oscilações do circuito LC parasita

O dimensionamento da resistência de amortecimento na porta do transístor de potência IGBT é

sempre necessário, pois não podemos desprezar os fenómenos capacitivos e de depleção que

interferem no comportamento dinâmico do transístor em regime de comutação. O processo de

comutação do IGBT é influenciado pela carga e descarga das capacidades equivalentes que o

transístor possui intrinsecamente aos seus terminais (J. Silva, 2009).

Para este dimensionamento, é necessário ter-se em consideração as capacidades equivalentes

transitórias que estão presentes nos terminais do IGBT, em regime dinâmico (figura 2.14).

CCG

CCE

CGE

Figura 2.14 – Circuito de análise do regime transitório do semicondutor de potência IGBT (J. Silva,

2009).

Para efeito de cálculo, ao consultarmos o catálogo de características dos semicondutores de

potência, as capacidades fornecidas pelo fabricante são a capacidades de entrada, C ISS, a

capacidade de transferência inversa, CRSS, e a capacidade de saída, COSS, que equivalem a:

CISS = CGE + CCG

(2.36)

CRSS = CCG

(2.37)

COSS = CCE + CCG

(2.38)

A resistência a dimensionar tem como objectivo realizar o amortecimento do circuito LC que se

cria na porta de comando do semicondutor, devido às indutâncias parasitas das ligações de porta

das ligações de porta e às capacidades anteriormente referidas.

23

RG

Ls

Cs

VG

Figura 2.15 – Circuito RLC na porta de comando do IGBT.

Assim, tendo em conta que o circuito RLC da figura 2.15 possuí um factor de qualidade dado por:

Q

LS

RG

;

(2.39)

onde,

1

;

Ls Cs

(2.40)

A indutância do circuito RLC parasita, criado aos terminais do semicondutor, é estimada

dependendo do tipo de condutor em questão. Para um circuito impresso cujos condutores são

pistas de comprimento

l , largura w e distanciados de d a indutância é dada por (J. Silva,

2009):

LS 0 d

10.1nH / cm ;

l

2

(2.41)

A capacidade equivalente de entrada do IGBT é estimada através de:

CS Ceq CISS CRSS

Considerando um factor de amortecimento óptimo de

VCG

;

VGE

(2.42)

, a resistência de amortecimento é

dada por:

RG 2

LS

CS

(2.43)

As resistências obtidas para cada uma das gates dos semicondutores de potência encontram-se

na tabela 2.

24

Módulo de

RG2 []

RG4 []

RG8 []

RG10 []

RG12 []

RG22 []

1

4.43

4.10

3.96

3.56

3.41

4.41

2

4.35

4.08

3.83

3.59

3.59

4.67

3

4.44

4.21

3.90

3.41

3.48

4.64

Potência

Tabela 2 - Resistências de amortecimento das oscilações.

Para implementação prática foi escolhida uma resistência de 6.2 para todas as situações.

2.2.6 Fontes de Alimentação Comutadas

Neste subcapítulo, é dimensionado o número de fontes de alimentação comutadas necessárias

para alimentar os dezoito acopladores ópticos dos dezoito semicondutores de potência

comandados (seis por cada um dos três módulos integrados de potência).

Tendo em conta que os IGBT que compõem os IB estão montados segundo a topologia colector

comum, o número de fontes de alimentação comutadas necessárias para os acopladores ópticos

será determinado segundo o número de pontos ligados em emissor comum.

Figura 2.16 – Esquema representativo dos pontos de emissor comum entre os semicondutores de

potência de cada um dos MI de potência.

Considerando a figura 2.16, em cada uma das fases de carga (uma por módulo de potência)

temos três IGBT ligados em emissor comum (círculo a vermelho). Para cada um destes

semicondutores utiliza-se um circuito de disparo, sendo os três circuitos de disparo alimentados

pela mesma fonte de alimentação, uma vez que o ponto de referência (o emissor) é equipotencial

25

para os três semicondutores. Como temos três fases de carga (W, U, T), para alimentar os nove

circuitos de disparo serão necessárias três fontes de alimentação.

Na fase de entrada R1 (círculo a amarelo), o IGBT, denominado na figura por T1, está em

emissor comum com os homólogos das fases de entrada (R2 e R3) dos outros dois módulos de

potência. Para alimentar os três circuitos de disparo destes semicondutores é necessária uma

única fonte de alimentação.

Para os IGBT em emissor comum nas fases de entrada S (círculo a verde) e T (círculo a azul),

aplica-se o mesmo raciocínio da fase R, sendo igualmente necessário apenas uma fonte de

alimentação para alimentar cada conjunto de três circuitos de disparo.

Pontos em Emissor

Nº de Fontes

Nº de Circuitos de

Comum

Comutadas

disparo

R1, R2, R3

1

3

S1, S2, S3

1

3

T1, T2, T3

1

3

W

1

3

U

1

3

V

1

3

TOTAL

6

18

Tabela 3 – Quadro resumo do número de fontes de alimentação.

Conclui-se então, que no total, são necessárias 6 fontes de alimentação para alimentar os

dezoito circuitos de disparo referentes aos dezoito IGBT do circuito de potência.

2.2.7 Circuitos Auxiliares de Aquisição de tensões e correntes

Circuito de Aquisição de Correntes

Por consulta do catálogo de fabricante (Anexo G), as ligações efectuadas nos terminais do

transdutor de corrente foram realizadas de forma a alcançar uma corrente nominal no primário de

. Obtém-se assim, as seguintes características do transdutor:

- Número de espiras no primário, 2;

- Corrente nominal de saída (secundário),

- Relação de Transformação,

;

26

;

- Tensão de isolamento,

( entre primário e secundário).

Respeitando a gama de valores recomendada para a resistência de medição do transdutor, e

considerando os dados anteriormente referidos, esta resistência toma o valor de 180.

Circuito de Aquisição de Tensões

Na montagem do transdutor de tensão, é necessário considerar uma resistência de medição.

Esta resistência é calculada segundo os seguintes dados de catálogo (Anexo H):

- Corrente nominal no primário,

;

- Corrente nominal secundária,

;

- Relação de transformação,

- Tensão de isolamento,

;

(entre primário e secundário).

Tendo em conta os valores pretendidos para os parâmetros anteriores, dentro da gama de

valores a considerar para a resistência de medição, escolheu-se uma resistência também de

180Ω.

27

3. Circuito Impresso para o Conversor Matricial

Neste capítulo, apresentam-se os esquemáticos e as placas de circuito impresso que constituem

o Conversor Matricial. Apresentam-se ainda todas as medidas a ter em conta no desenho do

circuito impresso do conversor, nomeadamente na redução do ruído EMI (Electromagnetic

Interferences), de modo a garantir bons desempenhos do conversor.

Posteriormente, são apresentados todos os esquemas de ligações a realizar para concretização

do layout de fabrico da Placa de Circuito Impresso (PCI).

3.1. Esquema Geral da Placa de Circuito Impresso

Na figura 3.1 apresenta-se uma perspectiva geral da distribuição dos circuitos que constituem o

Conversor Matricial (CM), na placa de circuito impresso. Este esquema serve de base para o

desenho do layout da placa de circuito impresso.

A PCI é de dupla camada (1 por face da placa), de espessura 1.6mm e possui as dimensões

referidas na figura. Estas dimensões correspondem a um circuito impresso com uma área de 516

2

cm .

24.6 cm

Filtro de Entrada LC

Fases de Saída

Fases de Entrada

Circuito de Potência (Circuito de Protecção,

Filtro de Entrada, Semicondutores)

21 cm

Módulo de Potência 1

Módulo de Potência 2

Módulo de Potência 3

Circuito de Comando

(Módulo 1)

Circuito de Comando

(Módulo 2)

Circuito de Comando

(Módulo 3)

Circuito de Comando

Figura 3.1 – Esquema Geral do Conversor Matricial.

28

Com esta disposição, pretende-se compactar ao máximo as dimensões do Conversor Matricial,

sendo necessário ter cuidados adicionais na definição das pistas de ligação dos diferentes

componentes, tanto do circuito de potência como do circuito de comando.

Teve-se ainda o cuidado de dispor de forma distinta o circuito de potência e o circuito de

comando. Com isto, pretende-se proteger o circuito de comando de possíveis interferências

electromagnéticas causadas pelo processo de comutação dos semicondutores de potência.

3.2. Medidas a considerar para redução do ruído EMI

As interferências electromagnéticas são processos de transmissão de energia electromagnética

entre

circuitos eléctricos/electrónicos susceptíveis de

degradarem significativamente

o

funcionamento dos circuitos (J. Silva, 2005).

O fenómeno de EMI é bastante crítico nos conversores electrónicos comutados devido às

elevadas frequências de comutação dos seus semicondutores. Considerando-se este facto,

desenhou-se o layout do circuito impresso do Conversor Matricial tendo em consideração um

conjunto de medidas adequadas para minimizar este fenómeno e optimizar o funcionamento do

conversor. As medidas consideradas para reduzir o efeito do ruído EMI foram:

- usar condensadores de desacoplamento, para filtrar o ruído de alta frequência presente

nas pistas dos sinais de comando;

- garantir pistas o mais curtas e largas possível, as que transportem maiores valores de

corrente, de forma a reduzir as indutâncias parasitas inerentes a estas;

- afastar o circuito de potência dos circuitos de controlo;

- colocar os circuitos de comando dos semicondutores o mais próximo possível dos

semicondutores e afastá-los dos circuitos de controlo;

- usar resistências para amortecer os circuitos LC parasitas;

- usar planos de massa;

- usar linhas de alimentação diferentes para as várias zonas da PCI;

- não usar pistas com ângulos rectos.

Todas estas medidas contribuem para a melhoria da compatibilidade electromagnética do

Conversor Matricial, permitindo que os circuitos operem sem degradação do seu funcionamento.

29

3.3. Determinação da largura das pistas

A definição correcta da largura de cada pista, permite melhorar significativamente o

funcionamento do circuito, pois assim minimizam-se as indutâncias parasitas das mesmas,

contribuindo para uma redução do ruído EMI.

A largura das pistas do circuito impresso foi determinada tendo em conta a espessura da pista, o

valor da corrente que é susceptível conduzirem e a elevação de temperatura da pista ao conduzir

essa corrente.

Figura 3.2 – Diagramas para determinação das larguras das pistas do CI (extraído da norma IPCIC2221, 1998: 38)

30

Para consulta dos diagramas da figura anterior é necessário ter a noção que a espessura das

pistas de cobre pode ser dada nas seguintes unidades:

1OZ/ft2 = 305.152 g/m2 = 35m

1 OZ (onça) = 35m = 1.4mils

1 polegada = 2.54cm = 1000mils

Tabela 4 – Conversões de unidades.

Por

consulta

das

especificações

de

produção

do

fabricante

do

circuito

impresso

(http://www.circuitotal.com/pt/info.htm), considerou-se para o cálculo da largura das pistas, uma

espessura da pista em cobre de 35m.

Foi considerado ∆t = 10ºC para elevação de temperatura admitida para as pistas. Isto significa

que para uma temperatura ambiente laboratorial de 25ºC, as pistas atingirão uma temperatura de

35ºC.

Por exemplo, se quisermos calcular a largura das pistas relativas às fases de entrada ou saída

do circuito de potência, considerando que se espera ter nas fases correntes com cerca de 10 A

observando os diagramas da figura anterior verifica-se que para uma elevação de 10ºC e uma

espessura de pista de 35m, obtém-se uma largura de pista de 0,3 polegadas, ou seja, uma

largura mínima de pista de 7,63mm.

31

3.4. Determinação do espaçamento entre pistas

O espaçamento entre pistas deverá ser maximizado na mesma camada de circuito impresso,

pois quando numa mesma camada existem diferentes níveis de tensões e para além disso,

tensões alternadas, como é o caso deste trabalho, é necessário garantir um afastamento

suficiente entre as pistas de forma a minimizar a interferência electromagnética.

Tabela 5 - Níveis de afastamento entre as diversas pistas segundo diversos níveis de tensões (tabela

6-1 Electrical Conductor Spacing página 39).

O espaçamento entre as pistas do circuito impresso é determinado considerando a norma IPC2221, segundo a qual o espaçamento entre duas pistas vizinhas é determinado segundo os

níveis de tensão entre elas.

3.5. Circuito de disparo

Na figura 3.3, é apresentada o esquemático de ligações do circuito de disparo relativo a um dos

módulos de potência. No protótipo laboratorial existem três módulos de circuitos de disparo,

todos iguais ao representado na Fig. 3.3.

32

Figura 3.3 – Esquemático do circuito de disparo de um dos módulos de potência.

Em relação ao esquemático do circuito de comando existem aspectos a realçar. Por consulta do

catálogo do fabricante, colocou-se aos terminais de saída (+15V e -15V), das fontes de

alimentação comutadas:

- 1 condensador cerâmico, de capacidade 1F, com tensão nominal, no mínimo, três

vezes a tensão de saída;

- 1 condensador de tântalo, de capacidade 10F, com tensão nominal, no mínimo, uma

vez e meia a tensão de saída;

Para além disto, colocaram-se próximo dos terminais de polarização, de todos os circuitos

integrados, condensadores cerâmicos de 0.1F. Este facto deve-se à necessidade de filtrar ruído

provenientes da fonte de alimentação originados por indutâncias inerentes às pistas de

alimentação.

Por último, colocaram-se no circuito, condensadores de desacoplamento de 0,1F.

33

Figura 3.4 – Layout do circuito de comando (face superior).

Figura 3.5 – Layout do circuito de comando (face inferior).

Tendo em conta que as fontes de alimentação comutadas garantem um isolamento galvânico

entre os terminais de polarização (primário) e os terminais de potência (secundário), estas devem

34

ser dispostas na placa de circuito impresso com os terminais do primário mais próximos do

circuito de comando, enquanto os terminais do secundário deverão estar localizadas mais

próximos do circuito de potência, realizando-se assim, tal como acontece com os acopladores

ópticos, um isolamento entre o circuito de potência e de comando. Assim consegue-se filtrar

algum do ruído EMI proveniente do circuito de potência.

3.6. Circuito do filtro de entrada e circuito de protecção

Neste subcapítulo, apresentam-se os esquemáticos e respectivo layout, referente às ligações do

filtro de entrada e das fases (de entrada e saída) do Conversor Matricial. Engloba-se ainda as

ligações relativas aos circuitos de protecção nas fases do conversor.

Figura 3.6 – Esquemático das fases de entrada e saída do Conversor Matricial

35

Figura 3.7 – Esquemático do circuito do filtro de entrada com resistências de descarga, RD, e circuito de

protecção com varistores.

Uma vez que não existem disponíveis no mercado condensadores com a capacidade e tensões

nominais desejadas (capítulo 2.2.3), foi necessário recorrer à associação série de

condensadores, para obter os valores pretendidos. Por esta razão, em vez de se usarem três

condensadores de polipropileno (um entre cada duas fases) de capacidade 13F e com tensão

nominal alternada de 400VAC, foram utilizados seis condensadores de polipropileno (dois em

série entre cada duas fases) de capacidade 20uF, de tensão nominal alternada de 305V AC. Com

esta associação de condensadores obtemos uma capacidade equivalente entre fases de 10F.

Os condensadores utilizados, têm a referência B32926E3206M.

36

Figura 3.8 – Layout do circuito do filtro de entrada com resistências de descarga, RD, e circuito de

protecção com varistores.

No layout do conversor, teve-se o cuidado de colocar o filtro de entrada o mais próximo possível

dos módulos de potência, isto é, dos semicondutores de potência que constituem os

Interruptores Bidireccionais. Com esta medida, pretende-se diminuir ao máximo o comprimento

das pistas, cujas indutâncias parasitas são susceptíveis de originar sobretensões aos terminais

dos semicondutores, podendo causar a sua destruição.

Em relação aos varistores de protecção, fez-se com que estes ficassem colocados o mais

próximo possível dos semicondutores de potência, porque ao diminuir o tamanho das pistas

reduzem-se também as indutâncias parasitas, permitindo que os varistores realizem uma

protecção mais eficaz. Pela mesma razão, os diodos de zener foram colocados próximos das

portas de comando dos transístores IGBT.

37

3.7. Layout global da placa de circuito impresso

Na figura 3.9 apresenta-se o layout da placa de circuito impresso onde ficam alojados os circuitos

de disparo dos transistores IGBT (em baixo, na zona a vermelho, que representa um plano de