Célula, Palavra, Ciclo de Instruções

e Lógica Temporizada

IFBA – Instituto Federal de Educ. Ciencia e Tec Bahia

Curso de Analise e Desenvolvimento de Sistemas

Arquitetura de Computadores – 20 e 21/30

Prof. Msc. Antonio Carlos Souza

Referências Bibliográficas:

1.

2.

3.

Ciência da Computação: Uma visão abrangente - J.Glenn

Brokshear

Introdução à organização de computadores – Mário

Monteiro – LTC

Organização Estrutura de Computadores – Andrew S.

Tanembaum - LTC

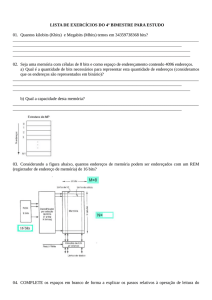

Célula x Tamanho da Memória

1)

Numa MP com 1kbyte de capacidade, onde cada

célula tem 8 bits:

a) quantas células tem a MP?

b) quantos bits são necessários para representar um

endereço de memória?

2)

Um computador endereça 1k células de 16 bits cada

uma. Pede-se:

a) sua capacidade de memória;

b) o maior endereço que o computador pode

endereçar;

3)

A memória de um computador tem capacidade de

armazenar 256 bits e possui um barramento de

dados de 16 bits. Pede-se:

a) o tamanho da célula de memória;

Palavra da CPU

Quantidade de bits que a cpu

processa por vez

¡ Palavra de 16 bits = 2 bytes de

processamento por vez

¡ Palavra de 32 bits = 4 bytes

¡ Palavra de 128 bits

¡

Palavra x Barramento

¡

¡

Há "computadores de 64 bits" mesmo quando

seu barramento de dados é de 32 bits, nesse

caso referindo-se exclusivamente à capacidade

de manipulação da UCP de 64 bits (isto é, sua

UAL e acumulador tem 64 bits).

Os microprocessadores Intel 8086 (16 bits,

sendo todos seus elementos de 16 bits) e seu

"irmão" mais novo 8088, usado nos primeiros

IBM/PC e XT (idêntico sob quase todos os

aspectos ao 8086 e também dito de 16 bits,

sendo que UAL e registradores são de 16 bits

mas o barramento de dados é de apenas 8 bits,

por economia e razões de compatibilidade com

toda uma geração de placas de 8 bits).

Palavras x Barramento

¡

Destaque-se que nesse caso as

transferências de dados através do

barramento de dados se fazem em

duas etapas, um byte de cada vez, e

em conseqüência no 8088 elas

consomem o dobro dos ciclos de

barramento que o 8086), o que torna

suas operações de transferência de

dados mais lentas que as de seu

"irmão" 8086.

Lógica Temporizada

¡

¡

as instruções, os dados e os

endereços "trafegam" no

computador através dos

barramentos (de dados, de

endereços e de controle).

Mas os dados no computador não

ficam estáticos; pelo contrário, a

cada ciclo (cada "estado") dos

circuitos, os sinais variam.

Lógica Temporizada

¡

¡

Ou seja, os sinais ficam estáticos apenas por

um curto espaço de tempo, necessário e

suficiente para os circuitos poderem detetar os

sinais presentes no barramento naquele instante

e reagir de forma apropriada.

Assim, periodicamente, uma nova configuração

de bits é colocada nos circuitos, e tudo isso só faz

sentido se pudermos de alguma forma organizar e

sincronizar essas variações, de forma a que, num

dado instante, os diversos circuitos do

computador possam "congelar" uma configuração

de bits e processá-las.

Lógica Temporizada

¡

¡

Para isso, é preciso que exista um outro

elemento, que fornece uma base de

tempo para que os circuitos e os sinais se

sincronizem.

Este circuito é chamado clock - o relógio

interno do computador. Cada um dos

estados diferentes que os circuitos

assumem, limitados pelo sinal do clock, é

chamado um ciclo de operação.

Lógica Temporizada

¡

A Unidade de Controle da UCP envia a

todos os componentes do computador um

sinal elétrico regular - o pulso de "clock" que fornece uma referência de tempo

para todas as atividades e permite o

sincronismo das operações internas. O

clock é um pulso alternado de sinais de

tensão, gerado pelos circuitos de relógio

(composto de um cristal oscilador e

circuitos auxiliares).

Lógica Temporizada

¡

Cada um destes intervalos regulares de tempo é

delimitado pelo início da descida do sinal,

equivalendo um ciclo à excursão do sinal por um

"low"e um "high" do pulso.

O tempo do ciclo equivale ao período da

oscilação. A física diz que período é o inverso da

freqüência. Ou seja,

P = 1 / f.

A freqüência f do clock é medida em hertz.

Inversamente, a duração de cada ciclo é chamada

de período, definido por P=1/f (o período é o

inverso da freqüência).

Por exemplo, se f = 10 hz logo P = 1/10 = 0,1 s.

Lógica Temporizada

Lógica Temporizada

¡

Os primeiros computadores tinham um único

sinal de clock geral, válido para UCP,

memória, barramentos de E/S (entrada /

saída), etc. À medida que a tecnologia foi se

aperfeiçoando, a freqüência de clock de

operação dos processadores (e, em menor

escala, também a das memórias) aumentou

em uma escala muito maior que a dos

demais componentes.

Lógica Temporizada

¡

¡

Desta forma, foi necessário criar diferentes pulsos de

clock para acomodar as freqüências de operação dos

diferentes componentes.

A placa-mãe de um PC utiliza uma freqüência-mestra

(hoje em geral de 66 Mhz, equivalente a um período

de 15 ns, estando em prancheta placas para 100

MHz) para seu barramento (ciclo de barramento), a

qual é multiplicada ou dividida para ser utilizada

pelos demais componentes:

- o processador tem essa freqüência multiplicada por

2 (133 Mhz) a 4 (266 MHz),

- o barramento PCI usa freqüências reduzidas pela

metade (33 Mhz),

- as memórias (ciclos da ordem de 60 ns) usam

freqüências reduzidas a um quarto e

- as cache secundárias (ciclos entre 10 e 20 ns) usam

a própria freqüência da placa-mãe.

Desempenho dos processadores

¡

¡

¡

¡

Medida em termos da velocidade de

trabalho

Execução de instruções por

intervalo de tempo

MIPS (milhões de instruções por

segundo)

MFLOPS (milhões de operações de

ponto flutuante por segundo)

Cache

Esquema Básico

Ciclo de Intruções

¡

¡

Primeiramente, o programa a ser

executado precisa ser carregado

(armazenado) na MP, o que é feito pelo

Sistema Operacional, que também se

encarrega de informar à UCP onde o

programa começa.

O Sistema Operacional faz isto "setando"

o PC (isto é, colocando no PC o endereço

da MP onde está localizada a primeira

instrução daquele programa).

Ciclo de Instruções

¡

A partir daí se realiza o processamento

automático, executando-se as instruções

seqüencialmente uma a uma, o que é

obtido através do incremento automático

do PC.

¡

Obs: Se o programa inclui uma instrução

de desvio, o fluxo seqüencial pode ser

alterado.

Ciclo de Instruções

¡

¡

A UCP não diferencia um dado de uma instrução.

A UCP não "executa" dados devido ao conteúdo

do CI, que é incrementado pelo tamanho da

instrução e fica sempre apontando para a próxima

instrução.

Mas se em um programa houver uma instrução

de desvio para um endereço em que esteja

contido um dado, a UCP interpretaria o valor

binário do dado como se fosse o código de uma

instrução, tentaria executar e o resultado seria

imprevisível.

Ciclo de Instrução

1 - A UCP busca o código de operação na MP e armazena no

Registrador de Instrução da UC

Fase: Busca da instrução - (Instruction Fetch) - ciclo de busca

RI <--- (PC)

Micro-operações:

- a UC lê o conteúdo do PC (endereço da próxima instrução )

e coloca o endereço no REM;

- a UC envia um sinal à memória de operação de leitura

(memory read), via barramento de controle;

- a memória lê o endereço que está no REM, via barramento

de endereços, e busca o conteúdo da célula referenciada;

- a memória coloca no RDM, via barramento de dados, o

conteúdo da célula lida;

- a memória envia à UC, via barramento de controle, um sinal

de "leitura concluída";

- a UC transfere o código de operação (o conteúdo do RDM)

ao RI.

Ciclo de Instruções

¡

2 - A UC (decodificador de instruções) decodifica o

Código de Operação.

Fase: Busca da instrução - (Instruction Fetch) - ciclo de

busca

Micro-operações:

- o Decodificador de Instruções decodifica o opcode;

- o Decodificador de Instruções determina quantas

células a instrução ocupa;

- a UC incrementa o CI para apontar para a próxima

instrução: PC<--- (PC+ n), onde n = nº de células que

a instrução ocupa.

- a UC incrementa o REM para apontar para o

operando: REM <--- (REM + 1);

Ciclo de Instruções

3 - A UC busca (se houver) o(s) operando(s)

Fase: Busca de operandos (Operand Fetch) - ciclo de

execução

RI <--- (Op)

Micro-operações:

- a UC envia um sinal à memória de operação de

leitura (memory read), via barramento de controle;

- a memória lê o endereço que está no REM, via

barramento de endereços, e busca o conteúdo da

célula referenciada;

- a memória coloca no RDM, via barramento de

dados, o conteúdo da célula lida;

- a memória envia à UC, via barramento de controle,

um sinal de "leitura concluída";

- a UC transfere o operando (o conteúdo do RDM) ao

RI.

Ciclo de Instruções

* Se o operando é o próprio dado:

-- a UC transfere o dado (o conteúdo do RDM) ao ACC.

-- vai para operação 4; caso contrário:

* Se o operando é um ponteiro para onde o dado está

armazenado:

-- a UC coloca no REM o endereço de onde o dado está

armazenado;

-- a UC envia um sinal à memória de operação de leitura

(memory read), via barramento de controle;

-- a memória lê o endereço que está no REM, via barramento

de endereços, e busca o conteúdo da célula referenciada;

-- a memória coloca no RDM, via barramento de dados, o

conteúdo da célula lida;

-- a memória envia à UC, via barramento de controle, um

sinal de "leitura concluída";

-- a UC transfere o dado (o conteúdo do RDM) ao ACC;

-- vai para operação 4.

Ciclo de Instrução

4 - A UC comanda a execução da

instrução (a operação é executada

sobre o dado).

Fase: Execução da instrução - ciclo

de execução

- UAL executa a instrução