Decodificação de I/O e Memória

Cap.6: 1/10

CAPÍTULO VI

DECODIFICAÇÃO DE I/O E MEMÓRIA

•

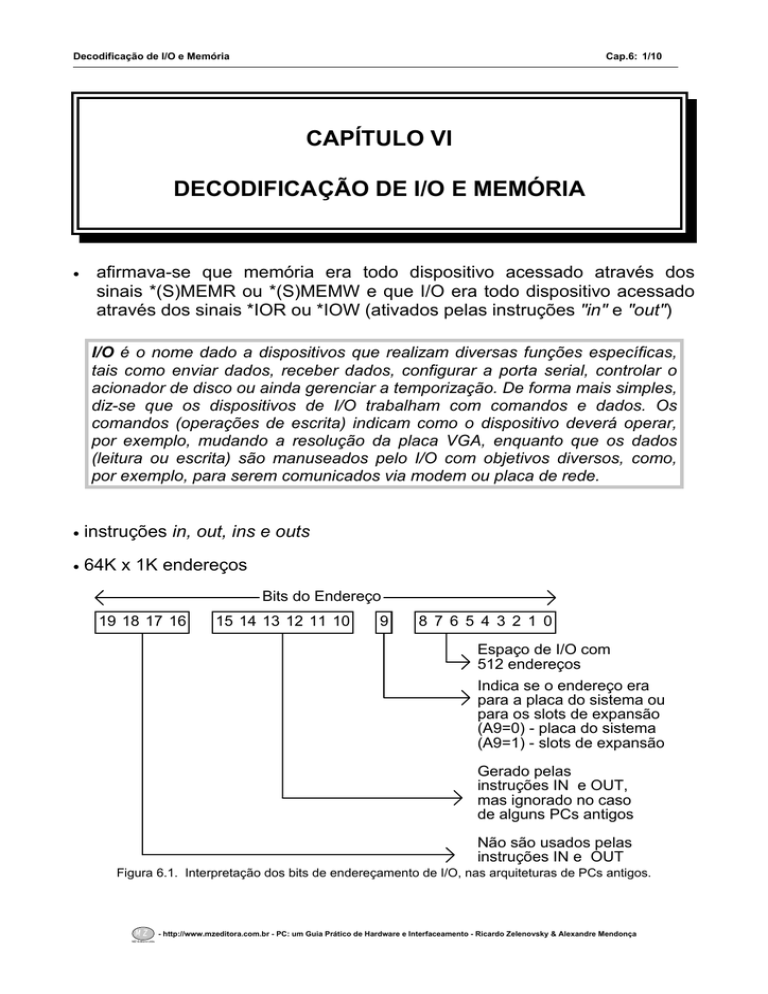

afirmava-se que memória era todo dispositivo acessado através dos

sinais *(S)MEMR ou *(S)MEMW e que I/O era todo dispositivo acessado

através dos sinais *IOR ou *IOW (ativados pelas instruções "in" e "out")

I/O é o nome dado a dispositivos que realizam diversas funções específicas,

tais como enviar dados, receber dados, configurar a porta serial, controlar o

acionador de disco ou ainda gerenciar a temporização. De forma mais simples,

diz-se que os dispositivos de I/O trabalham com comandos e dados. Os

comandos (operações de escrita) indicam como o dispositivo deverá operar,

por exemplo, mudando a resolução da placa VGA, enquanto que os dados

(leitura ou escrita) são manuseados pelo I/O com objetivos diversos, como,

por exemplo, para serem comunicados via modem ou placa de rede.

•

instruções in, out, ins e outs

•

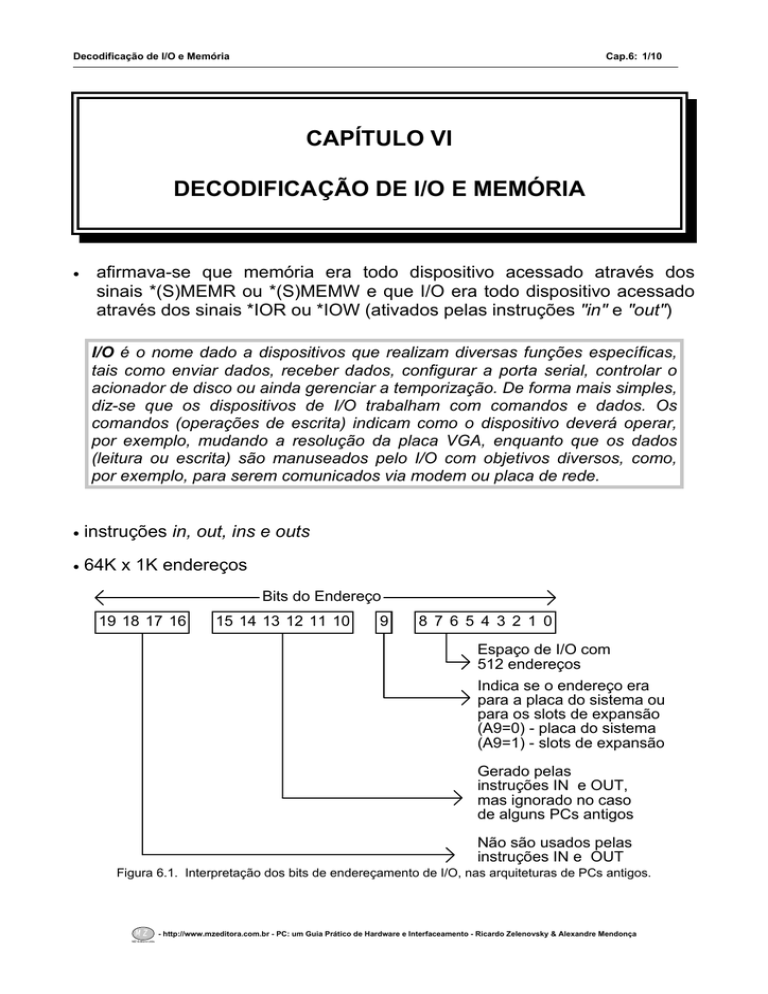

64K x 1K endereços

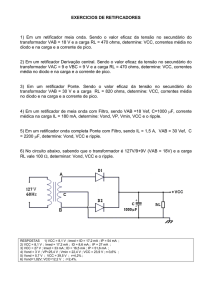

Bits do Endereço

19 18 17 16

15 14 13 12 11 10

9

8 7 6 5 4 3 2 1 0

Espaço de I/O com

512 endereços

Indica se o endereço era

para a placa do sistema ou

para os slots de expansão

(A9=0) - placa do sistema

(A9=1) - slots de expansão

Gerado pelas

instruções IN e OUT,

mas ignorado no caso

de alguns PCs antigos

Não são usados pelas

instruções IN e OUT

Figura 6.1. Interpretação dos bits de endereçamento de I/O, nas arquiteturas de PCs antigos.

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Decodificação de I/O e Memória

Cap.6: 2/10

FFFFh

0400h

03FFh

0200h

01FFh

0000h

64.512

Não usado no projeto inicial do PC

512

Espaço para os slots de expansão

512

Espaço para a placa do sistema

Figura 6.2. Utilização do espaço de endereçamento de I/O nos primeiros PCs.

•

dispositivos "on-board"

Endereços

000h-00Fh

020h-021h

040h-043h

060h-063h

060h-064h

070h-071h

080h-08Fh

0A0h-0A1h

0C0h-0DFh

0F0h-0FFh

1F0h-1FFh

200h-20Fh

238h-23Bh

278h-27Fh

2B0h-2BFh

2C0h-2CFh

2D0h-2DFh

2E8h-2EFh

2F8h-2FFh

320h-32Fh

378h-37Fh

300h-31Fh

3C0h-3CFh

3D0h-3DFh

3E8h-3EFh

3F0h-3F7h

3F8h-3FFh

400h =>

Dispositivo

primeiro controlador de DMA (8237)

primeiro controlador de interrupções (8259)

temporizador programável (8253)

interface paralela 8255 (XT)

controlador 8742 (AT)

RAM CMOS e registrador de máscara NMI (AT)

registradores de paginação para DMA

segundo controlador de interrupções (AT)

segundo controlador de DMA (AT)

coprocessador aritmético (AT)

disco rígido (AT)

porta de jogos

mouse de barramento

LPT2:

vídeo (EGA-VGA)

vídeo (EGA-VGA)

vídeo (EGA-VGA)

COM4:

COM2:

disco rígido (XT)

LPT1:

reservado para protótipos

vídeo (EGA-VGA)

vídeo (CGA)

COM3:

disco flexível

COM1:

projetos PCI

Figura 6.3. Uso do espaço de endereçamento de I/O no PC.

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Decodificação de I/O e Memória

Cap.6: 3/10

Decodificação com endereço fixo

*CS0, *CS1,...,*CS7 com habilitação em nível baixo

• OR dos *CS com *IOR e *IOW

•

D0

D1

D2

D3

D4

D5

D6

D7

Endereço Base = 3E0H

A9

1

A8

1

A7

1

A6

1

A5

1

A4

0

A3

0

A2

X

A0

X

A1

X

8 Endereços

Decodificados

*IOW (B13)

D0

D1

D2

D3

D4

D5

D6

D7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

OC

G

74LS02

74LS373

A

B

C

A0 (A31)

A1 (A30)

A2 (A29)

A9 (A22)

A8 (A23)

A7 (A24)

A6 (A25)

A5 (A26)

74LS04

VCC

A9

A8

A7

A6

G1

G2A

G2B

A5

*A4

*A3

*AEN

74LS30

*CS0 (3E0H)

*CS1 (3E1H)

*CS2 (3E2H)

*CS3 (3E3H)

*CS4 (3E4H)

*CS5 (3E5H)

*CS6 (3E6H)

*CS7 (3E7H)

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

D0

D1

D2

D3

D4

D5

D6

D7

74LS138

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

1G

2G

74LS32

*IOR (B14)

A4 (A27)

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

Saída com

8 Bits

74LS244 Entrada

com

8 Bits

Barramento

74LS04

de Dados do PC

A3 (A28)

74LS04

D0 (A9)

D1 (A8)

D2 (A7)

D3 (A6)

D4 (A5)

D5 (A4)

D6 (A3)

D7 (A2)

AEN (A11)

*IOR (B14)

74LS08

*ADROK

*IORW

74LS32

*IOW (B13)

A1

A2

A3

A4

A5

A6

A7

A8

B1

B2

B3

B4

B5

B6

B7

B8

D0

D1

D2

D3

D4

D5

D6

D7

Barramento Interno

G

DIR

74LS245

*IOR (B14)

Figura 6.4. Decodificação de I/O com endereço fixo.

•

outportb(0x3E0, variável);

•

variável = inportb(0x3E0);

•

uso do 74LS374 ao invés do 74LS373

AEN = 0 é um nível lógico necessário para que os decodificadores de

I/O operem sem conflitar com os ciclos de DMA.

Decodificação programável por chave

•

uso de "dip switch"

•

outportb(endereço, variável);

•

variável = inportb(endereço);

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Decodificação de I/O e Memória

Cap.6: 4/10

Programado pela Chave

A9

1

A8

Y

A7

Y

A6

Y

A5

Y

A4

Y

A3

Y

A2

X

A1

X

D0

D1

D2

D3

D4

D5

D6

D7

A0

X

8 Endereços

Decodificados

*IOW (B13)

D0

D1

D2

D3

D4

D5

D6

D7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

OC

G

74LS02

Saída com

8 Bits

74LS373

A

B

C

A0 (A31)

A1 (A30)

A2 (A29)

VCC

VCC

A9 (A22)

AEN (A11)

A8 (A23)

A7 (A24)

A6 (A25)

A5 (A26)

A4 (A27)

A3 (A28)

6x (8K2)

P0

P1

P2

P3

P4

P5

P6

P7

VCC

SW1

G1

G2A

G2B

P=Q

*CS0 (base)

*CS1 (base+1)

*CS2 (base+2)

*CS3 (base+3)

*CS4 (base+4)

*CS5 (base+5)

*CS6 (base+6)

*CS7 (base+7)

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

74LS138

74LS244

Entrada com

8 Bits

de Dados do PC

D0 (A9)

D1 (A8)

D2 (A7)

D3 (A6)

D4 (A5)

D5 (A4)

D6 (A3)

D7 (A2)

*ADROK

74LS08

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

Barramento

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

74LS688

*IOR (B14)

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

1G

2G

74LS32

*IOR (B14)

G

SW DIP-6

D0

D1

D2

D3

D4

D5

D6

D7

74LS32

*IORW

A1

A2

A3

A4

A5

A6

A7

A8

B1

B2

B3

B4

B5

B6

B7

B8

Barramento Interno

D0

D1

D2

D3

D4

D5

D6

D7

G

DIR

*IOW (B13)

74LS245

*IOR (B14)

Figura 6.5. Decodificação programável por chave, usando o 74LS688.

Programado pela Chave

VCC

VCC

A9

1

Coletor Aberto

4X (8K2)

A8

Y

A7

Y

A6

Y

A5

Y

A4

X

A3

X

A2

X

A1

-

A0

-

4K7

Wired AND

SW1

SW DIP-4

A8 (A23)

74LS266

A7 (A24)

74LS266

A2 (A29)

A3 (A28)

A4 (A27)

A

B

C

ADROK

G1

G2A

G2B

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

*CS0 (base+0)

*CS1 (base+4)

*CS2 (base+8)

*CS3 (base+12)

*CS4 (base+16)

*CS5 (base+20)

*CS6 (base+24)

*CS7 (base+28)

74LS138

A6 (A25)

A5 (A26)

74LS266

74LS266

A

B

NXOR

0

0

1

0

1

0

1

0

0

1

1

1

8 Linhas Decodificadas.

Cada linha seleciona um

bloco de 4 endereços

consecutivos.

74LS04

AEN (A11)

A9 (A22)

74LS09

A=B

A=B

1

0

Figura 6.6. Decodificação programável por chave usando o 74LS266.

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Decodificação de I/O e Memória

•

Cap.6: 5/10

decodificação selecionável por PROM

512X8 PROM

A0 (A31) 8

A1 (A30) 7

A2 (A29) 6

A3 (A28) 5

A4 (A27) 4

A5 (A26) 3

A6 (A25) 2

A7 (A24) 1

A8 (A23) 23

AEN (A11) 21

A0

A1

D1

A2

D2

A3

D3

A4

D4

A5

D5

A6

D6

A7

D7

A8

*CE1

9

D0

*CS0

10 *CS1

11 *CS2

13 *CS3

14 *CS4

15 *CS5

16 *CS6

17 *CS7

N82S141

(60 ηs)

21 *CE2

VCC

A9 (A22) 19

23

CE3

CE4

EXEMPLO: Habilitar *CS0 para o endereço 382h

Endereço

A8 A7 A6 A5 A4 A3 A2 A1 A0

1 1 1 0 0 0 0 1 0

Dado Programado

D7 D6 D5 D4 D3 D2 D1 D0

1 1 1 1 1 1 1 0

Figura 6.7. Decodificação de I/O usando uma PROM.

Expandindo o espaço de endereçamento

•

utilização dos bits de ordem superior

• não funciona desde o surgimento do PCI

•

endereçamento indireto

• RAM CMOS e vídeo VGA

Latch

Dado

D0 - D7

Interpretado

como Endereço

*IOW

I/O Endereçado

Indiretamente

Decodificador

*IOR

IA0-7 Endereço

Indireto

8 / 256

*IOW

*SEL

G

A0-A9

AEN

*CS

D0-D7

*CS0

DECOD.

NORMAL

*CS1

Transceiver

Barramento de Dados Interno

D0 - D7

Barramento

de Dados do PC

Figura 6.9. Esquema simplificado para o endereçamento indireto para I/O.

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Decodificação de I/O e Memória

Cap.6: 6/10

Dado usado

como Endereço

Barramento Dados PC

D0

D1

D2

D3

D4

D5

D6

D7

A0 (A31)

*IOW (B13)

IA0

IA1

IA2

IA3

IA4

IA5

IA6

IA7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

D0

D1

D2

D3

D4

D5

D6

D7

8 Endereços Decodificados

A

B

C

VCC

G1

G2A

G2B

74LS138

OC

G

74LS27

*ICS0

*ICS1

*ICS2

*ICS3

*ICS4

*ICS5

*ICS6

*ICS7

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Saída Digital

Endereçada Indiretamente

74LS373

VCC

6x (8K2)

VCC

SW1

P=Q

P0

P1

P2

P3

P4

P5

P6

P7

A9 (A22)

AEN (A11)

A8 (A23)

A7 (A24)

A6 (A25)

A5 (A26)

A4 (A27)

A3 (A28)

D0

D1

D2

D3

D4

D5

D6

D7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

OC

G

74LS27

*IOW (B13)

74LS373

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

SW DIP-6

D0

D1

D2

D3

D4

D5

D6

D7

D0

D1

D2

D3

D4

D5

D6

D7

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

G

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

1G

2G

74LS688

*IOR (B14)

74LS244

Entrada Digital

Endereçada Indiretamente

Barramento de Dados do PC

D0 (A9)

D1 (A8)

D2 (A7)

D3 (A6)

D4 (A5)

D5 (A4)

D6 (A3)

D7 (A2)

A1

A2

A3

A4

A5

A6

A7

A8

D0

D1

D2

D3

D4

D5

D6

D7

B1

B2

B3

B4

B5

B6

B7

B8

Barramento de Dados

Interno

G

DIR

74LS32

74LS245

*IOR (B14)

A0 (A31)

74LS04

Figura 6.10. Uso de endereçamento indireto para expandir o espaço de I/O.

•

"outportb(base,índice);" seguido de "outportb(base+1,dado);"

I/O mapeado em memória

A19 A18 A17 A16

1

0

1

1

A15 A14 A13 A12

1

1

1

1

A11 A10 A9

1

1

1

A8

1

A7

1

A6

1

A5

1

*MEMW

A4

1

A3

1

A2

0

A1

0

A0

0

D0

D1

D2

D3

D4

D5

D6

D7

D0

D1

D2

D3

D4

D5

D6

D7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

DO0

DO1

DO2

DO3

DO4

DO5

DO6

DO7

OC

G

74LS02

74LS373

A19 (A12)

A18 (A13)

A16 (A15)

A15 (A16)

74LS30

A14 (A17)

A13 (A18)

A12 (A19)

A11 (A20)

74LS04

A10 (A21)

A9 (A22)

A8 (A23)

A7 (A24)

A6

A5

A4

A3

74LS30

(A25)

(A26)

(A27)

(A28)

74LS10

D0 (A9)

D1 (A8)

D2 (A7)

D3 (A6)

D4 (A5)

D5 (A4)

D6 (A3)

D7 (A2)

A1

A2

A3

A4

A5

A6

A7

A8

*MEMR

G

DIR

74LS04

A17 (A14)

A2 (A29)

A1 (A30)

A0 (A31)

B1

B2

B3

B4

B5

B6

B7

B8

Saídas usando o endereço

de memória DFFF8H

D0

D1

D2

D3

D4

D5

D6

D7

Entradas usando o endereço

de memória DFFF8H

74LS245

D0

D1

D2

D3

D4

D5

D6

D7

74S260

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

DI0

DI1

DI2

DI3

DI4

DI5

DI6

DI7

1G

2G

74LS02

Decodificação dos 20 bits do Endereço DFFF8H

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

*MEMR

74LS04

74LS244

Figura 6.11. Registradores de I/O (entrada e saída) mapeados no primeiro megabyte de memória.

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Decodificação de I/O e Memória

Cap.6: 7/10

nunca entra em conflito com os endereços de I/O já utilizados

• aumenta o espaço de I/O

• oferece a possibilidade de usar todas as instruções da família 80x86

•

I/O a 16 bits

A9

...

A1

D0

D1

D2

D3

D4

D5

D6

D7

B1

B2

B3

B4

B5

B6

B7

B8

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

A1

A2

A3

A4

A5

A6

A7

A8

*IOR

G

DIR

74LS245

D0

D1

D2

D3

D4

D5

D6

D7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

OC

G

DO0

DO1

DO2

DO3

DO4

DO5

DO6

DO7

endereço

par

74LS373

*IOW

A0

74LS02

decod.

I/O

*I/OCS16

AEN

74LS04

B1

B2

B3

B4

B5

B6

B7

B8

SD8

SD9

SD10

SD11

SD12

SD13

SD14

SD15

A1

A2

A3

A4

A5

A6

A7

A8

*IOR

G

DIR

74LS245

*IOW

*SBHE

74LS05

D8

D0

D9

D1

D10

D2

D11

D3

D12

D4

D13

D5

D14

D6

D15

D7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

OC

G

74LS373

DO8

DO9

DO10

DO11

DO12

DO13

DO14

DO15

endereço

ímpar

74LS02

Figura 6.12. Esquema para I/O a 16 bits.

•

parte alta e parte baixa (*SBHE e A0)

•

acesso a endereço par

mov dx,300h

•

in ax,dx

• "outport(0x300);" em linguagem C

• endereços acessados: 300h e 301h

• 1 único ciclo de barramento

•

acesso a endereço ímpar

mov dx,301h

•

in ax,dx

• "outport(0x301);" em linguagem C

• endereços acessados: 301h e 302h

• 2 ciclos de barramento

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Decodificação de I/O e Memória

Cap.6: 8/10

•

acesso de 16 bits em barramento PCI

•

acesso de 32 bits em barramento PCI

Decodificação de memória

•

*(S)MEMR e *(S)MEMW

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

A10 (A21)

A9 (A22)

A8 (A23)

A7 (A24)

A6 (A25)

A5 (A26)

A4 (A27)

A3 (A28)

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

BA10

BA9

BA8

BA7

BA6

BA5

BA4

BA3

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

BA2

BA1

BA0

*BMEMR

*BMEMW

BA0

BA1

BA2

BA3

BA4

BA5

BA6

BA7

BA8

BA9

BA10

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

*CS0

*BMEMR

*BMEMW

CE

OE

WE

6116

BA0

BA1

BA2

BA3

BA4

BA5

BA6

BA7

BA8

BA9

BA10

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

1G

2G

74LS244

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

A2 (A29)

A1 (A30)

A0 (A31)

*MEMR (B12)

*MEMW (B11)

1G

2G

74LS244

A

B

A11 (A20)

A12 (A19)

*SEL GRUPO

G

*CS0

*CS1

*CS2

*CS3

Y0

Y1

Y2

Y3

*CS2

*BMEMR

*BMEMW

74LS139

BD0

BD1

BD2

BD3

BD4

BD5

BD6

BD7

D0

D1

D2

D3

D4

D5

D6

D7

BA0

BA1

BA2

BA3

BA4

BA5

BA6

BA7

BA8

BA9

BA10

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

*CS1

*BMEMR

*BMEMW

CE

OE

WE

D0

D1

D2

D3

D4

D5

D6

D7

BD0

BD1

BD2

BD3

BD4

BD5

BD6

BD7

D0

D1

D2

D3

D4

D5

D6

D7

BD0

BD1

BD2

BD3

BD4

BD5

BD6

BD7

6116

BA0

BA1

BA2

BA3

BA4

BA5

BA6

BA7

BA8

BA9

BA10

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

*CS3

*BMEMR

*BMEMW

CE

OE

WE

6116

BD0

BD1

BD2

BD3

BD4

BD5

BD6

BD7

D0

D1

D2

D3

D4

D5

D6

D7

CE

OE

WE

6116

VCC

A19 (A12)

A18 A(13)

A17 (A14)

A16 (A15)

A15 (A16)

A14 (A17)

A13 (A18)

8K2

P0 P=Q

P1

P2

P3

P4

P5

P6

P7

*SEL GRUPO

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

SW DIP-7

A1

A2

A3

A4

A5

A6

A7

A8

D0 (A9)

D1 (A8)

D2 (A7)

D3 (A6)

D4 (A5)

D5 (A4)

D6 (A3)

D7 (A2)

B1

B2

B3

B4

B5

B6

B7

B8

BD0

BD1

BD2

BD3

BD4

BD5

BD6

BD7

G

DIR

*MEMR (B12)

74LS245

G

74LS688

Figura 6.13. Decodificação de 8 KB de memória em blocos de 2 KB.

VCC

8K2

SW DIP-4

A19 (A12)

A18 (A13)

A17 (A14)

A16 (A15)

VCC

A0

A1

A2

A3

B0

B1

B2

B3

A<B

A=B

A>B

A<B

A=B

A>B

Decodificação

de um bloco

de 64KB

74LS85

Figura 6.14. Decodificação de 64 KB com endereço selecionável por chave.

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Decodificação de I/O e Memória

Cap.6: 9/10

Mapa de memória

PC AT

Memória Estendida

100000h

E0000h

Reservado para a PARA ROM BIOS

C0000h

Reservado para ROMs

A0000h

9FFFFh

Buffers de Vídeo

Porção transiente do DOS

Área de Programas

(programas de usuários e dados)

Porção residente do DOS

00500h

Área de dados para ROM BIOS e BASIC

00400h

Área de dados para a ROM BIOS

00000h

Área destinada

ao DOS

Tabela de Vetores de Interrupção

Figura 6.15. Mapa de memória de um típico PC AT.

Exercícios

6-7) Projete um circuito que multiplexe o acesso a 2 registradores num

mesmo endereço, da seguinte forma: o primeiro acesso é realizado em um

dos registradores, o acesso seguinte é feito ao outro e assim

sucessivamente.

6-12) O seguinte conjunto de instruções é utilizado para realizar uma leitura

de 16 bits:

mov dx,300h

in ax,dx

.

Existe alguma diferença de desempenho entre executar estas instruções

com a linha *I/O CS 16 ativada ou não ?

6-13) Repita o problema anterior, substituindo apenas 300h por 301h.

6-14) Nos casos dos problemas 6-12 e 6-13, quais as diferenças de

implementações em hardware ao ativar-se ou não a linha *I/O CS 16 ?

6-15) O que acontecerá se, por engano, um projetista utilizar em seu projeto

os endereços de I/O de 3F0h a 3F7h ?

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.

Decodificação de I/O e Memória

Cap.6: 10/10

6-17) (Concurso para o Quadro de Engenheiros Militares do Exército especialidade eletrônica - 1998)

Para permitir que um microprocessador acesse 3 dispositivos, foi preparada

a decodificação a seguir, onde se utilizaram apenas as 10 linhas de

endereços menos significativas: A0, A1, ..., A9. As demais linhas de

endereços foram ignoradas. Considerando que os dispositivos são

selecionados em nível baixo (quando *CS=0), determine em hexadecimal

todos os endereços possíveis, para cada dispositivo.

A1

74LS138

A2

A3

A

B

C

A9

A8

G1

G2A

G2B

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

*CS

DISP1

*CS

DISP2

*CS

DISP3

A7

A6

A5

VCC

A4

A0

MZ - http://www.mzeditora.com.br - PC: um Guia Prático de Hardware e Interfaceamento - Ricardo Zelenovsky & Alexandre Mendonça

MZ Editora Ltda.