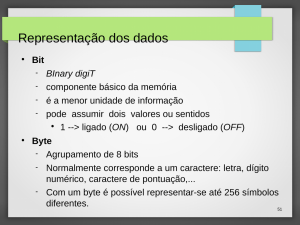

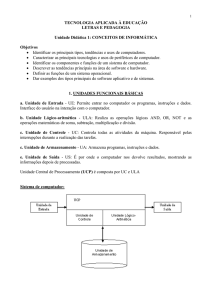

Diminui

o

gargalo

existente

processador e memória principal;

entre

◦ Diferença de velocidade

5 a 10 vezes mais rápidas que a memória

principal;

Ligada diretamente à MP;

Tecnologia semelhante à da CPU e, em

conseqüência, possui tempos de acesso

compatíveis com a mesma, resultando

numa considerável redução da espera

da CPU para receber dados e instruções

da cache.

L1 – Level 1 (nível 1)

◦ Dentro do processador;

◦ Mesma velocidade do processador;

L2 – Level 2 (nível 2)

◦ Dentro do invólucro, fora do chip;

◦ Metade da velocidade do processador;

Pentium Pro, II, III, IV

L3 – Level 3 (nível 3)

◦ Cache externa, situada na placa mãe

K6-3 da AMD;

Invólucro do processador

Processador

Cache L2

Cache L1

Memória

principal

A cache L1 é geralmente dividida em cache

de dados e cache de instruções:

processamento mais rápido

processador

dados

instruções

Cache L1

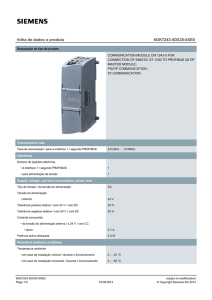

Processado Fabricante

r

Tamanho

486

Intel

8KB

C6

Cyrix

64KB

K5

AMD

24KB

K7

AMD

128KB

Pentium

16KB

Pentium MMX

32KB

Pentium Pro

Pentium III

Intel

16KB

32KB

Processado Fabricante

r

Tamanho

Celeron® D

Processor 365

IntelIntel

512KB L2

CCeleron® D

Processor 350

Intel

L2512KB

Core™ i73770T

Processor

Intel

8M, L1

Phenom™ II

AMD

512KB, L2

Pesquisas mostram que a execução dos

programas se realiza em pequenos grupos

de instruções;

◦ Localidade espacial;

◦ Localidade temporal;

Se um programa acessa uma palavra da

memória, há uma boa probabilidade de que

ele acesse, em seguida, uma palavra

adjacente;

Se um programa acessa uma palavra da

memória, há uma boa probabilidade de que

ele, em breve, acesse a mesma palavra

novamente;

Memória Principal

int F, N;

F = 1;

cin >> N;

If (N = = 0)

cout << “Fatorial de 0 é 1”;

else {

F = N;

while (N !=1){

F = F * (N-1);

N = N –1;

}

cout << “Fatorial de N é”, F;

}

Executado

na seqüência

Executado

na seqüência

loop

Devido ao princípio da localidade, é

interessante

que

a

memória

cache

armazene o pedaço do programa que é

executado repetidas vezes, deixando o

restante do programa que não está sendo

utilizado na memória principal.

Sempre

que o processador vai

buscar uma nova instrução (ou

dado), ele acessa a memória cache:

◦ Se a instrução estiver na cache (acerto

ou hit), ela é transferida em alta

velocidade para o processador

◦ Se a instrução não estiver na cache (falta

ou miss), a execução do programa é

interrompida e a instrução desejada é

transferida da MP para a MC;

Não é feita a transferência somente da

instrução, mas sim de um bloco que,

segundo o princípio da localidade, contém

instruções que serão usadas em seguida;

controlador

de cache

Processador

Memória

principal

Cache

Palavra

(instrução

ou dado)

Bloco

de palavras

Função de mapeamento MP/MC;

Algoritmos de substituição de dados na

cache;

Políticas de escrita;

A função de mapeamento indica quais

blocos da MP estão presentes na cache e

onde eles estão localizados na cache;

◦ A MC e MP estão divididas em blocos de x

palavras;

◦ A MC pode conter m blocos (linhas);

◦ A MP pode conter b blocos;

MP

Bloco 0

.

.

.

Byte 0

Byte 1

Byte 63

Bloco 1

.

.

.

Byte 0

Byte 1

Byte 63

.

.

.

Bloco

226 -1

.

.

.

Byte 0

Byte 1

Byte 63

Divisão da MP de 4G bytes

em blocos de 64 bytes

então tem-se 226 blocos

de 64 bytes

MC

Byte 63

...

Byte 1

Byte 0

Linha 0

Byte 63

...

Byte 1

Byte 0

Linha 1

Byte 63

...

.

.

.

Byte 1

Byte 0

Linha 2

Byte 63

Tag ou

rótulo

...

Byte 1

Byte 0

Linha 1023

Divisão da MC de 64K bytes

em linhas de 64 bytes então

tem-se 1024 linhas de 64

bytes

Cada bloco da MP tem uma linha de cache

previamente definida para ser armazenado;

Muitos blocos irão ser destinados a uma

mesma linha;

Exemplos:

◦ Pentium, K6, K7, Motorola 68030

B0

.

.

.

Byte 0

Byte 1

Byte 63

B1

.

.

.

Byte 0

Byte 1

tag

Byte 63

...

Byte 1 Byte 0 Linha 0

Byte 63

...

Byte 1 Byte 0 Linha 1

Byte 63

...

.

.

.

Byte 1 Byte 0 Linha 2

...

Byte 1 Byte 0 Linha 1023

Byte 63

.

.

.

B

2

26

-1

.

.

.

Bloco 1023

Byte 0

Byte 1

Byte 63

Byte 63

Cada linha da MC deverá acomodar 216

blocos ou 65536 blocos (um de cada vez);

O campo tag serve para identificar qual

bloco a linha está armazenando no

momento ;

Cada endereço de MP pode ser dividido nos

seguintes elementos:

32 bits

Número do bloco

Número da linhaNúmero da palavra

na linha

16 bits

10 bits

6 bits

216= 64K blocos 210= 1024 linhas 26= 64 palavras

Exemplo:

◦ O processador manda para a MC o seguinte

endereço:

00000000000001000000011001001000

4

25

8

00000000000001000000011001001000

25

4

Byte 63

...

Byte 1

Byte 0

Linha 0

Byte 63

...

Byte 1

Byte 0

Linha 1

Byte 63

...

Byte 1

Byte 0

Linha 2

Byte 1

Byte 0

Linha 25

Byte 63

4

Byte 63

Tag ou

rótulo

8

Byte 8

...

Byte 1

Byte 0

Linha 1023

Se o campo tag do endereço for igual ao

campo tag da linha da cache, o conteúdo do

byte

solicitado

é

enviado

para

o

processador;

Se os campos tag forem diferentes, isso

significa que o bloco desejado não se

encontra na cache e, portanto, deve ser

transferido da MP para a linha 25,

substituindo o atual bloco para, em seguida,

a palavra (o byte) requerida ser transferida

para o processador pelo barramento de

dados;

Para buscar o bloco na MP é utilizado os 26

bits mais significativos do endereço pois 226

= 64M bytes

00000000000001000000011001

16 bits

10 bits

A

técnica de mapeamento direto é

simples e de baixo custo;

Desvantagem: fixação da localização

para os blocos;

◦ Imagine se durante a execução de um

programa

um

dado

código

fizer

referências repetidas a palavras situadas

em blocos alocados na mesma linha,

então haverá necessidade de sucessivas

idas à MP para substituição de blocos

(muitas faltas) e queda no desempenho

do sistema;

Os blocos não têm uma linha fixada

previamente para seu armazenamento;

O bloco é armazenado em uma linha que é

selecionada de acordo com o algoritmo de

substituição de cache;

B0

.

.

.

Byte 0

Byte 1

Byte 63

B1

.

.

.

Byte 0

Byte 1

tag

Byte 63

...

Byte 1 Byte 0 Linha 0

Byte 63

...

Byte 1 Byte 0 Linha 1

Byte 63

...

.

.

.

Byte 1 Byte 0 Linha 2

...

Byte 1 Byte 0 Linha 1023

Byte 63

.

.

.

B

2

26

-1

.

.

.

Byte 63

Byte 0

Byte 1

Byte 63

Cada linha da MC pode acomodar um dos

226 blocos da memória principal;

O

campo tag tem agora 26 bits de

tamanho;

Cada endereço de MP é dividido nos

seguintes elementos:

32 bits

Número do bloco

Número da palavra

26 bits

226 blocos

6 bits

26 palavras

Quando o processador realiza um acesso à

memória, o campo bloco do endereço é

comparado com todos os 1024 tags da

cache para verificar se o bloco está ou não

presente;

Se o bloco estiver presente, o byte é

transferido para a CPU, senão o endereço

do bloco é usado para buscar na memória

principal o bloco ausente;

Desvantagem: teste do campo bloco do

endereço de memória com todos os tags da

cache;

Esquema

intermediário entre o direto

e o totalmente associativo;

Número fixo de posições onde um

bloco pode ser armazenado na

cache;

Cache

associativa de n posições:

◦ n posições possíveis para cada bloco;

◦ Cache com conjuntos de n posições;

◦ Blocos mapeados diretamente em um

conjunto e colocado em qualquer

elemento do conjunto;

Cache

com mapeamento direto:

(n. bloco) módulo (n. blocos na cache)

Cache

associativa por conjunto:

(n. bloco) módulo (n. conjunto na cache)

Se

um bloco puder ser alocado a

qualquer posição de um conjunto,

todos os elementos deverão ser

pesquisados

Considere três caches, cada qual com quatro

blocos de uma palavra

1. Mapeada diretamente

2. Associativa por conjunto com 2 posições

3. Totalmente associativa

Qual bloco atualmente armazenado na

cache deve ser retirado para dar lugar a

um novo bloco que está sendo

transferido?

LRU (Least Recently Used): O controlador de

cache escolhe o bloco que está há mais tempo

sem ser utilizado pela CPU;

LFU

(Least

Frenquently

Used):

o

controlador de cache escolhe o bloco que tem

tido menos acessos (menos referências) por

parte da CPU; Escolha aleatória;

FIFO (First in first out): O controlador de

cache escolhe o bloco que está armazenado há

mais tempo na cache, independentemente de

estar sendo usado ou não com freqüência pela

CPU;

Quando o processador realiza uma operação

de escrita, esta acorre imediatamente na

cache;

A

memória

cache

é

uma

memória

intermediária logo é necessário que a MP seja

atualizada para que o sistema mantenha sua

correção e integridade;

Antes da execução

da instrução X = Y + Z

Memória Principal

Cache

Processador

X=1

Y=7

Z=2

X=Y+Z

X=1

Y=7

Z=2

X=Y+Z

X=Y+Z

Bloco 4

Bloco 4

Depois da execução

da instrução X = Y + Z

Memória Principal

Cache

Processador

X=1

Y=7

Z=2

X=Y+Z

X=9

Y=7

Z=2

X=Y+Z

X=Y+Z

Bloco 4

Bloco 4

Processador

Processador

Processador

X=Y+Z

Cache

X=1

Cache

X=1

cache

X=9

X=9

MP

X=9

X=1

X=9

O bloco 4 (o valor de X) precisa ser atualizado

na memória.

Quando?

•

Depende da política de escrita

Cada escrita em uma palavra da cache

acarreta em uma escrita na palavra

correspondente na MP, assegurando validade

permanente e igual ao conteúdo de ambas as

memórias;

Caso haja outras CPUs, estas alterarão

também suas caches;

O bloco é atualizado na memória somente

quando for substituído e se ocorrer alteração;

Utilizados em ambiente com mais de um

processador;

O

controlador

de

cache

notifica

os

processadores sobre a modificação e atualiza

o bloco na memória;

Isto é feito somente quando o bloco é

modificado pela primeira vez;

Os processadores, sabendo da modificação,

impedem o uso do bloco modificado;

As

próximas

modificações

só

serão

modificadas na memória quando o bloco for

substituído;