3. ESTUDO DA CPU

3.1. Formato de Instruções

♦ Programa: consiste numa seqüência de instruções.

♦ Instrução: executa uma ação particular.

♦ Componentes de uma instrução:

• Código de operação: especifica a ação a ser executada.

• Operandos: contêm ou especificam a localização do dado

utilizado pela instrução.

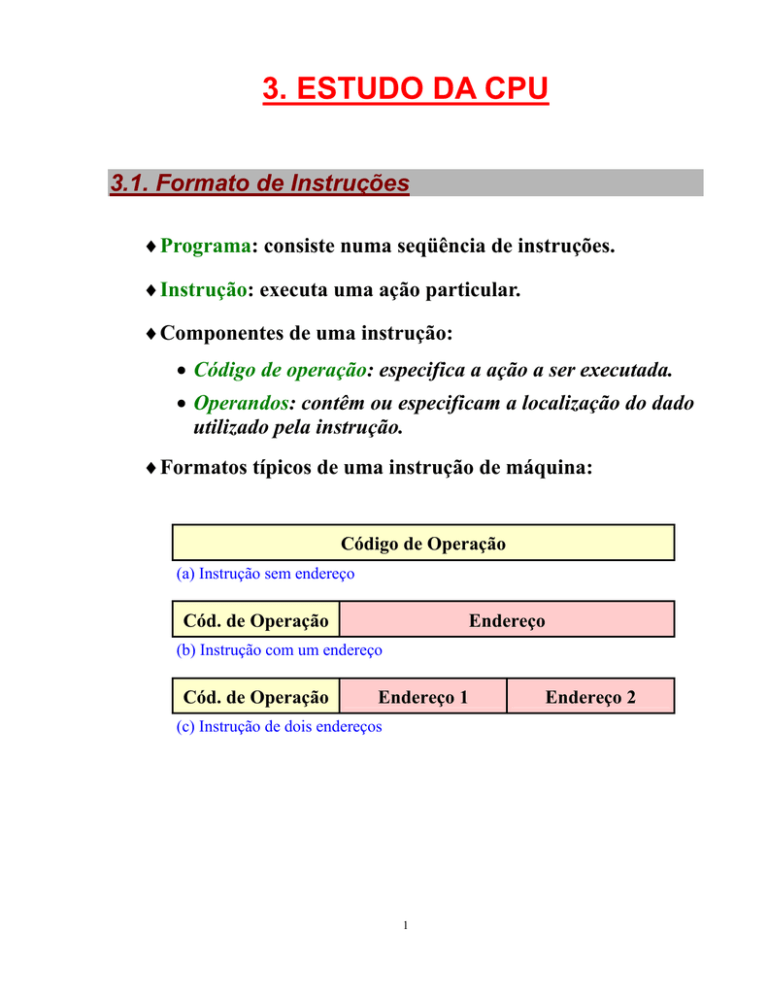

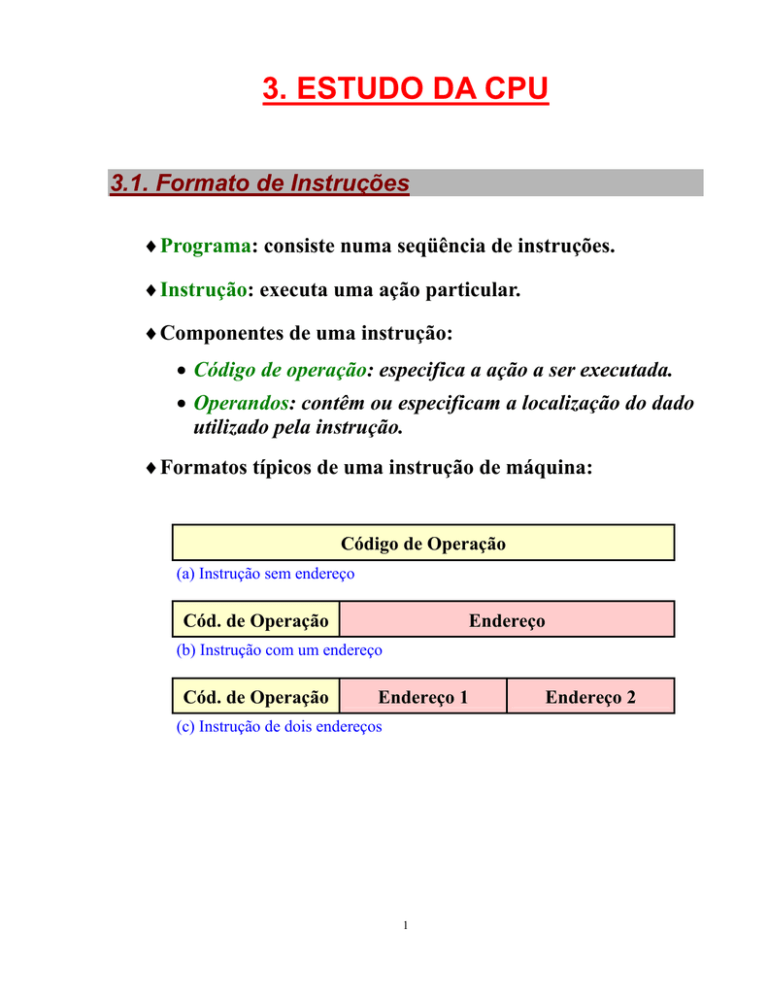

♦ Formatos típicos de uma instrução de máquina:

Código de Operação

(a) Instrução sem endereço

Cód. de Operação

Endereço

(b) Instrução com um endereço

Cód. de Operação

Endereço 1

(c) Instrução de dois endereços

1

Endereço 2

♦ Relações possíveis entre o comprimento de uma instrução e

o comprimento de uma palavra da máquina:

• Todas as instruções possuem o mesmo comprimento.

• As instruções podem assumir dois ou três comprimentos

diferentes.

• As instruções podem ser mais curtas, ter o mesmo

tamanho ou ser mais compridas do que a palavra da

máquina.

• Exemplos:

1 palavra

End.

0

1

2

3

Instrução

Instrução

Instrução

Instrução

1 palavra

End.

0

1

2

3

(a)

Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

(c)

Instrução

Instrução

Instrução

Instrução

(b)

1 palavra

End.

0

1

2

3

4

5

6

7

Instrução

Instrução

Instrução

Instrução

1 palavra

End.

0

1

2

3

4

5

6

7

Instrução Instrução Instrução Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

Instrução Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

Instrução

(d)

2

Critérios de Projeto para Formatos de Instruções

♦ “Instruções curtas são melhores do que instruções longas”.

• Um programa com n instruções de 16 bits consome a

metade do espaço de memória do que um de n instruções

de 32 bits.

• Cada memória tem a sua taxa de transferência

determinada pela tecnologia de projeto.

∗ Número de bits por segundo que pode ser lido da

memória.

∗ Para uma taxa de transferência de t bps e um

comprimento médio de instrução de r bits, a

memória pode fornecer no máximo t/r instruções

por segundo para o processador.

∗ A taxa de instruções executadas por segundo

(velocidade do processador) depende do

comprimento da instrução.

∗ Este critério só não seria importante se o tempo

para a execução das instruções fosse grande

comparado ao tempo de busca da instrução.

♦ “Deve haver espaço suficiente na instrução para expressar

todas as operações desejadas”.

• Uma máquina com 2n operações deve ter instruções com

no mínimo n bits.

♦ “É desejável que o comprimento da palavra de máquina

seja um múltiplo inteiro de seu comprimento de caractere”.

• Se o caractere tiver k bits, o comprimento da palavra deve

ser k, 2k, 3k, ..., para não haver desperdício de espaço

para o armazenamento de caracteres.

3

• Ou uma instrução ocupa um número inteiro de bytes ou

palavras ou uma palavra abriga um número inteiro de

instruções.

♦ “O número de bits no campo de endereços”.

• Considerando-se uma máquina com o caractere de 8 bits

e uma memória principal com capacidade de armazenar

216 caracteres, temos diversas possibilidades, entre elas:

∗ Unidade básica (palavra) de 8 bits:

◊ Memória de 216 bytes, de 0 a 65535.

◊ Um endereço para cada caractere.

∗ Unidade básica (palavra) de 32 bits:

◊ Memória de 214 palavras, de 0 a 16383.

◊ Comparação entre dois caracteres na memória: busca

das palavras e extração dos caracteres dentro das

palavras.

◊ Um endereço mais curto possibilita a existência de

instruções mais curtas.

◊ Permite o endereçamento de uma quantidade de memória

4 vezes maior com o mesmo número de bits de endereços

do anterior.

• Quanto maior a resolução de endereçamento da memória,

maior o tamanho da instrução.

• Exemplos:

∗ Burroughs B 1700: endereçamento de bits.

∗ CDC Cyber: endereçamento de palavras de 60 bits.

4

Expandindo os Códigos de Operação

♦ Considerando-se uma instrução de n + k bits, com o código

de operação de k bits e endereçamento de memória de

n bits.

• Permite 2k operações diferentes.

• Permite 2n células endereçáveis de memória.

♦ Considerando-se uma instrução de n + k bits, com o código

de operação de k - 1 bits e endereçamento de memória de

n + 1 bits.

• Permite 2k/2 operações diferentes.

• Permite 2*2n células endereçáveis de memória ou o

mesmo número com o dobro da resolução.

♦ Considerando-se uma instrução de n + k bits, com o código

de operação de k + 1 bits e endereçamento de memória de

n - 1 bits.

• Permite 2*2k operações diferentes.

• Permite 2n/2 células endereçáveis de memória ou o

mesmo número com a metade da resolução.

5

♦ Expansão do código de operação:

• Exemplo:

∗ Máquina com instruções de 16 bits e endereços de 4

bits.

◊ Permite 16 códigos de operação (4 bits) com 3 endereços

de 4 bits

15 14 13 12 11 10

Código de

Operação

9

8

7

Endereço 1

6

5

4

Endereço 2

3

2

1

0

Endereço 3

∗ Alternativa possível:

◊ 15 instruções de 3 endereços.

• códigos de operação de 4 bits

◊ 14 instruções de 2 endereços.

• códigos de operação de 8 bits

◊ 31 instruções de 1 endereço.

• códigos de operação de 12 bits

◊ 16 instruções sem endereço.

• códigos de operação de 16 bits

• Nem sempre os operandos tem o mesmo comprimento.

6

∗ Código de operação expandido:

16 bits

Código de

Operação de

4 bits

0000

0001

0010

.

.

1100

1101

1110

xxxx

xxxx

xxxx

.

.

xxxx

xxxx

xxxx

yyyy

yyyy

yyyy

.

.

yyyy

yyyy

yyyy

zzzz

zzzz

zzzz

.

.

zzzz

zzzz

zzzz

15 instruções de

3 endereços

Código de

Operação de

8 bits

1111

1111

1111

.

.

1111

1111

1111

0000

0001

0010

.

.

1011

1100

1101

yyyy

yyyy

yyyy

.

.

yyyy

yyyy

yyyy

zzzz

zzzz

zzzz

.

.

zzzz

zzzz

zzzz

14 instruções de

2 endereços

Código de

Operação de

12 bits

1111

1111

.

.

1111

1111

1111

1111

.

.

1111

1111

1110

1110

.

.

1110

1110

1111

1111

.

.

1111

1111

0000

0001

.

.

1110

1111

0000

0001

.

.

1101

1110

zzzz

zzzz

.

.

zzzz

zzzz

zzzz

zzzz

.

.

zzzz

zzzz

31 instruções de

1 endereço

Código de

Operação de

16 bits

1111

1111

1111

.

.

1111

1111

1111

1111

1111

1111

.

.

1111

1111

1111

1111

1111

1111

.

.

1111

1111

1111

0000

0001

0010

.

.

1101

1110

1111

16 instruções de

0 endereço

15 12 11

8 7

4 3

Número de bits

7

0

Exemplos de Formato de Instrução

PDP-11

♦ Instrução possui um código de operação de 4 bits e dois

campos de endereçamento de 6 bits (total de 16 bits).

♦ Código de Operação:

• Primeiro bit indica se a instrução opera sobre um byte ou

sobre uma palavra.

♦ Operando:

• 3 bits para modo

∗ Operando é registrador,

∗ Operando está na memória,

∗ Operando é uma constante, ...

• 3 bits para registrador (8 registradores)

♦ Os modos são os mesmos para os operandos fonte e destino.

♦ Qualquer operação atua sobre qualquer operando fonte e

destino (código de operação é dito ortogonal).

Código de

Byte/

Pal.

Bits

15

Operando Fonte

INSTRUÇÃO

14

13

12

MODO

11

10

Operando Destino

REGISTRADOR

9

8

7

6

MODO

5

4

REGISTRADOR

3

2

1

0

♦ As intruções de um operando utilizam o código de escape

x111, sendo o código de operação representado por 10 bits e

o operando por 6 bits.

8

♦ As instruções que endereçam memória possuem 1 ou 2

palavras adicionais de 16 bits para especificar os endereços.

A Família Intel 8088/80286/80386

♦ Instruções não são muito regulares.

• Geralmente, para uma instrução de dois operandos, se

um operando está na memória, o outro não pode estar na

memória (código não ortogonal).

♦ 8088

• Todo código de operação é de 1 byte.

♦ 80386

• Novas instruções: o código de operação 15 (1111)

funciona como um escape para os códigos de operação de

2 bytes.

♦ O bit menos significativo do código de operação indica em

algumas instruções se a operação é sobre um byte ou

palavra. O bit subseqüente indica se o endereço de

memória (se for o caso) é fonte ou destino.

9

CPU

8088

80286

80386

Formato

da

Instrução

Bits

Comprimento de campos (em bytes)

0-3

0-3

0-5

1

1

1-2

0-1

0-1

0-1

0

0

0-1

0-2

0-2

0-4

0-2

0-2

0-4

Prefixo

Código

de

Operaçã

o

Modo

SIB

Deslocamento

Imediato

6

INSTRUÇÃO

1

Fonte

1

B/P

2

ESCALA

3

ÍNDICE

2

3

3

MOD

REG

R/M

3

BASE

♦ Na maioria das instruções, o byte após o código de

operação indica onde se localizam os operandos:

• Modo (2)

∗ 4 maneiras de se endereçar um operando.

• Registrador (3)

∗ AX, BX, CX, DX, SI, DI, BP ou SP.

ou

∗ AH, BH, CH, DH, AL, BL, CL ou DL.

• Registrador/Memória (3)

∗ O outro registrador ou o modo de endereçamento a

memória (depende do Modo).

♦ No 80386, alguns dos modos requerem um byte adicional,

SIB (Escala, Índice, Base), referente a outros modos de

endereçamento.

10

♦ Algumas instruções possuem mais 1, 2 ou 4 bytes adicionais

para especificar um endereço de memória.

♦ Algumas instruções possuem mais 1, 2 ou 4 bytes adicionais

para especificar um operando constante.

♦ Tamanho das instruções:

• 8088/80286: 1 a 9 bytes.

• 80386: 1 a 17 bytes.

11

A Família Motorola 68000/68020/68030

♦ Tem 3 comprimentos de dados (byte, palavra, palavra

longa).

♦ Tentativa de construir todas as instruções em 16 bits.

• 18 formatos diferentes de instruções (menos pontoflutuante).

• Existem palavras adicionais para prover endereços de

memória e constantes para a instrução.

• Existe um espaço maior para as instruções mais

importantes e mais utilizadas.

∗ Instrução Move: formato 1 (só dois bits

especificam

instrução).

esta

• CÓD. OPERAÇÃO: 2, 4, 8, 9, 10, 11, 12, 16 bits.

• TAM: 1-byte, 2-palavra longa, 3-palavra.

• OPERANDO: 6 bits.

∗ Modo: 3 bits.

∗ Registrador: 3 bits.

◊ 1 dos 8 registradores A ou 1 dos registradores D.

♦ A maioria das instruções de 2 operandos utiliza um campo

REG para especificar o segundo operando. Desta forma,

perde-se a ortogonalidade nestas instruções, pois só é

permitido um dos operandos na memória.

12

♦ Formatos de instrução utilizados no 68000 (primeira

palavra):

15 14 13 12 11 10

1

OP

2

CÓD. OPER.

REG

3

CÓD. OPER.

4

8

7

6

5

4

2

1

0

MOVE

MOD

OPERANDO

ADD, AND, CMP, SUB

REG

OP

OPERANDO

CHK, DIVS, LEA, MULS

CÓD. OPER.

REG

MOD

5

CÓD. OPER.

REG

6

CÓD. OPER.

REG

7

CÓD. OPER.

REG

OP

8

CÓD. OPER.

CONT. OP

OP

TAM

9

CÓD. OPER.

DADO

OP

TAM

OPERANDO

ADDQ, SUBQ

10

CÓD. OPER.

CONDIÇÃO

OP

OPERANDO

Scc

11

CÓD. OPER.

CONDIÇÃO

12

CÓD. OPER.

CONDIÇÃO

14

15

16

17

OPERANDO

3

OPERANDO

13

TAM.

9

OP

TAM

OP

REG

MOVEP

OP

REG

ASL, ASR, ROL, ROR

REG

ABCD, EXG, SBCD

COD. OPER.

CÓDIGO DE OPERAÇÃO

DADO

MOVEQ

OP

REG

DESLOCAMENTO

COD. OPER.

TAM

CÓDIGO DE OPERAÇÃO

TAM

CÓDIGO DE OPERAÇÃO

CÓDIGO DE OPERAÇÃO

Bcc

REG

DBcc

OPERANDO

ADDI, CMPI, NEG, TST

OPERANDO

MOVEM

OPERANDO

JMP, JSR, NBCD, PEA

VETOR

CÓDIGO DE OPERAÇÃO

ASL, ASR, ROL, ROR

REG

TRAP

EXT, LINK, SWAP,

NLINK

18

CÓDIGO DE OPERAÇÃO

NOP, RESET, RST,

TRAPV

13

♦ A diferenciação entre os formatos de instrução não se dá

sempre pelos bits 12 a 15 para os formatos de 2 a 12:

ADDQ

0

1

0

1

DADO

0

TAM

Modo

Reg

SUBQ

0

1

0

1

DADO

1

TAM

Modo

Reg

Scc

0

1

0

1

CONDIÇÃO

1

1

Modo

Reg

DBcc

0

1

0

1

CONDIÇÃO

1

1

0

0

1

REG

• Obs: Tamanho 11 é inválido.

♦ Nos microprocessadores 68020, 68030 o problema se

agrava, devido a existência de instruções adicionais.

• Compiladores e montadores mais complexos.

• Microprogramas mais complicados.

14

3.2. Endereçamento

♦ As instruções podem ser classificadas de acordo com o

número de endereços que elas utilizam. Estes endereços

podem ser:

• Número do registrador a ser utilizado.

∗ Os registradores da CPU constituem uma memória

de alta velocidade e, portanto, um espaço de

endereçamento.

• Posição de memória.

♦ Instruções comuns: especificam 1, 2 ou 3 endereços.

♦ Em muitas máquinas que fazem operações aritméticas com

um endereço apenas, um registrador especial denominado

Acumulador provê um dos operandos.

♦ Instruções de 1 endereço: em geral envolvem o

Acumulador.

• Acumulador := Acumulador + Registrador 1

• Acumulador := Acumulador + Memória[ end1 ]

♦ Instruções de 2 endereços: utilizam um dos endereços como

fonte e o outro como destino ou fonte/destino.

• Fonte/Destino := Fonte/Destino + Fonte

♦ Instruções de 3 endereços: utilizam dois endereços como

fonte e o terceiro como destino.

• Destino := Fonte 1 + Fonte 2

♦ O modo de endereçamento de um operando está

relacionado com a forma como os campos de endereço da

15

instrução são interpretados para se encontrar um

operando.

16

Endereçamento Imediato

♦ É a maneira mais simples de uma instrução especificar um

operando, pois a parte da instrução relativa ao endereço

contém o operando propriamente dito (valor), e não o local

onde ele possa ser encontrado.

♦ Tal operando é dito operando imediato.

♦ O operando é buscado na memória ao mesmo tempo que a

instrução é buscada.

♦ Vantagem: não requer um referência extra à memória para

se buscar o operando.

♦ Desvantagem: restringe o operando a um valor que possa

caber dentro do campo de endereçamento.

• Se o campo de endereço for de 3 bits, sua utilização fica

limitada.

17

Família Intel:

♦ Não possui um modo de endereçamento para operandos

imediatos.

♦ Possui instruções distintas nas quais um dos operandos é

imediato.

Família Motorola:

♦ Possui um modo de endereçamento imediato; qualquer

operando fonte pode ser uma constante.

• 68000: algumas instruções permitem constantes de 8 ou

16 bits.

• 68020, 68030: permitem constantes de 8, 16 ou 32 bits.

• Existem instruções especiais (ADDI, ADDQ e CMPI)

que permitem uma codificação mais eficiente de

instruções imediatas:

∗ Constantes imediatas pequenas são incluídas dentro

da palavra da instrução, sem a necessidade de se

acrescentar bytes adicionais ao final da instrução.

18

Endereçamento Direto

♦ A instrução fornece o endereço da palavra de memória

onde o operando está contido.

♦ Exemplo:

• “Carga do registrador R1 com o conteúdo da posição de

memória de endereço 1000”.

Endereço

Código de

Operação

(*)

R1

1000

(*) Campos que

Especificam o

Endereçamento

Direto

R1

1000

1510

1510

4

1510

∗ Passo 1: O operando é buscado da posição 1000.

∗ Passo 2: O operando é carregado em R1.

19

Intel:

♦ Todas as CPUs possuem endereçamento direto.

• 8088/80286:

∗ Endereços diretos de 16 bits.

• 80386:

∗ Utiliza endereços diretos de 16 bits nos modos real e

virtual, e segmentos de 16 bits no modo protegido.

∗ Utiliza endereços diretos de 32 bits no modo

protegido de 32 bits.

Motorola:

♦ Possui duas formas de endereçamento direto:

• 16 bits

∗ Para endereçamento dos primeiros 64 Kbytes de

memória.

• 32bits

∗ Para endereçamento acima dos 64 Kbytes.

♦ As formas de endereçamento direto são indicadas no campo

MODO de 3 bits e se aplicam a todos os operandos da

instrução.

20

Endereçamento de Registrador

♦ Conceitualmente é semelhante ao endereçamento direto.

O campo de endereço da instrução contém o número do

registrador no qual o operando está armazenado.

♦ O endereçamento da máquina deve ter duas partes:

• Um bit para indicar se será utilizada uma posição de

memória (endereçamento direto) ou um registrador

(endereçamento de registrador) na instrução.

• Um campo de endereço com o número do registrador

(endereçamento de registrador) ou endereço de uma

palavra na memória (endereçamento de direto).

♦ O número de registradores é muito menor do que o número

de palavras de memória: logo, os formatos freqüentemente

são diferentes (para garantir instruções menores).

♦ Fica mais claro quando o bit que diferencia estes dois tipos

de endereçamento se encontra no campo de endereçamento

e não no código de operação.

♦ Motivos para a utilização de registradores:

• O acesso aos registradores é mais rápido do que o acesso

a palavras na memória.

• O endereçamento dos registradores requer apenas alguns

bits, pois estes são em pequeno número.

♦ “Problema”: complica a programação, pois sendo em

pequeno número, o programador (ou o compilador) deve

decidir quais operandos e resultados intermediários devem

permanecer em registrador.

21

♦ Disponível em quantidade nas CPUs Intel e Motorola.

22

Endereçamento Indireto

♦ O campo de endereçamento da instrução especifica qual a

palavra de memória ou registrador contém o endereço do

operando.

♦ Exemplo:

• “Carga do registrador R1 de forma indireta a partir da

posição de memória de endereço 1000”.

Endereço

Código de

Operação

(*)

R1

1000

Apontador

(*) Campos que

Especificam o

Endereçamento

Indireto

R1

1000

1510

1510

4

4

• Passo 1: O apontador para o operando é buscado da

posição 1000.

• Passo 2: O operando é buscado na posição 1510.

• Passo 3: O operando é carregado em R1.

23

Intel:

♦ Os processadores Intel possuem endereçamento indireto via

registrador, mas não permitem um endereçamente indireto

na memória.

♦ 8088/80286:

• Registradores utilizados para endereçamento indireto:

BX, SI e DI.

♦ 80386:

• Todos os registradores podem ser utilizados.

Motorola:

♦ 68000:

• Permite somente o endereçamento indireto via

registrador.

♦ 68020 e 68030:

• Permitem também o endereçamento indireto via memória.

♦ Existem processadores que permitem endereçamento

indireto de múltiplos níveis na memória.

24

Endereçamento Indexado

♦ Muitos algoritmos necessitam da execução de alguma

operação sobre uma seqüência de dados armazenados em

posições consecutivas de memória.

♦ Exemplo:

• Bloco de n palavras ocupando as posições:

A, A+1, A+2,..., A+n-1

que devem ser copiadas para as posições:

B, B+1, B+2,..., B+n-1

• Uma solução possível: se a máquina possuir uma

instrução

MOVE A, B

que copia o conteúdo da posição A para a posição B e

modifica a própria instrução para:

MOVE A+1, B+1

e a executa novamente, e assim sucessivamente, até

completar as n interações.

Problema: os programas ficam difíceis de se depurar

(programa altera a si próprio).

♦ Outra solução: utilizar o endereçamento indireto. A cada

movimentação são alterados os apontadores, que são dados.

♦ No endereçamento indexado é utilizado um ou mais

registradores de índice. Neste caso, os endereços possuem

duas partes:

• O número de um registrador de índice.

• Uma constante.

25

♦ O endereço do operando é a soma da constante com o

conteúdo do registrador de índice.

♦ No exemplo anterior, se o registrador de índice possuir o

valor k, a instrução MOVE A,B copiará o conteúdo da

posição de memória A+k para B+k. Basta o registrador de

índice ser inicialmente carregado com o valor 0, e ser

incrementado do tamanho da palavra de memória a cada

palavra copiada.

♦ Algumas máquinas incrementam ou decrementam o

conteúdo do registrador de índice antes ou depois de cada

utilização: auto-indexação.

♦ CPUs Intel e Motorola: possuem endereçamento indexado.

26

Endereçamento de Pilha

♦ É desejável a existência de instruções de máquina tão

curtas quanto possível.

• Economia de memória e tempo de CPU.

♦ Instruções sem endereço possuem apenas o código de

operação.

♦ Pode-se ter uma arquitetura baseada em instruções sem

endereço, que se utilizam de uma estrutura de dados

denominada pilha. Estas máquinas são denominadas de

stack machines.

♦ Pilha: consiste em itens de dados (palavras, caracteres, bits)

armazenados em ordem consecutiva na memória.

• Base (fundo) da pilha: é o primeiro item colocado na

pilha.

• Ponteiro da Pilha: registrador ou palavra na memória

que contém o endereço do topo da pilha (último dado

armazenado).

27

♦ Exemplo de funcionamento da pilha:

Apontador da pilha

1001

1003

1002

100

40

6

100

40

6

75

100

40

6

(b)

(c)

(d)

Fundo

da

pilha

Endereço

1000

1001

1002

1003

1004

1005

1006

1002

100

40

Topo da

Pilha

(a)

♦ Os computadores orientados para pilha possuem instruções

para:

• Inserir o conteúdo de um registrador ou posição de

memória na pilha, incrementando o ponteiro da pilha

após armazenar o dado.

∗ Exemplo: PUSH.

• Copiar o conteúdo do topo da pilha para um registrador

ou posição de memória, decrementando o ponteiro da

pilha após armazenar o dado.

∗ Exemplo: POP.

♦ Em alguns computadores a pilha cresce no sentido

contrário ao dos endereços.

• Exemplo: CPUs da família Intel.

28

♦ Instruções sem endereço utilizam como operandos dados

existentes na pilha.

• Exemplo:

∗ Uma instrução de adição obtém os dois operandos

retirando-os consecutivamente do topo da pilha e

armazena o resultado na pilha. Os operandos são

retirados da pilha após o uso.

Apontador da pilha

Endereço

1000

1001

1002

1003

1004

1003

1002

1001

4

20

6

5

4

20

30

4

50

(b)

(c)

Topo da

Pilha

(a)

♦ Tipos de notação para uma operação envolvendo dois

operandos:

• Notação Infixada: o operador é colocado entre os

operandos.

∗ Exemplo: x + y.

• Notação Polonesa Reversa ou Notação Pós-Fixada: o

operador é colocado após os operandos.

∗ Exemplo: x y +.

29

Exemplos de Endereçamento

♦ Maneiras de se implementar as diversas formas de

endereçamento:

• Utilizar um código de operação para cada modo:

∗ Exemplos:

◊ ADDim - ADD imediato

◊ ADDd - ADD direto

◊ ADDin - ADD indireto

• Fazer o modo de endereçamento como parte do endereço

da instrução.

30

Endereçamento no PDP-11

♦ Os modos de endereçamento são implementados de forma

elegante, clara e simples.

♦ Os endereços são especificados por um campo de 6 bits.

• Instruções de dois endereços possuem dois destes campos.

♦ Existem 8 registradores: R0 a R7.

• R6 - Ponteiro da Pilha

• R7 - Contador do Programa

∗ O Contador do Programa avança de 2

imediatamente após uma palavra de instrução ser

buscada (2 bytes) e antes de ser executada.

♦ Todas as instruções têm 16 bits, sendo que as vezes são

necessárias 1 ou 2 palavras adicionais após a instrução, que

são utilizadas pela instrução (valor, endereço de memória) e

podem ser consideradas como parte dela.

♦ Formato de uma instrução de dois endereços no PDP-11.

Palavra de 16 bits

End.

N

Código de

Operação

4

Fonte

Modo

Registrador

Fonte

Fonte

3

3

N+2

(Próxima Palavra 1)

N+4

(Próxima Palavra 2)

31

Destino

Modo

Registrador

Destino

Destino

3

3

♦ Descrição dos modos de endereçamento do PDP-11, onde R

é o registrador especificado em Fonte ou Destino.

Modo

Nome

0

Endereçamento

Registrador

Indireto Via

Registrador

AutoIncremento

1

2

3

4

5

6

7

Como o operando é localizado

O operando está em R.

O R contém um apontador para o operando.

O conteúdo de R é buscado e usado como um apontador para

o operando.

Após esse passo, mas antes de a instrução seguinte ser

executada, R é incrementado de 1 (instruções de byte) ou 2

(instruções de palavra).

O endereço de uma palavra na memória que contém um

Autoapontador para o operando é buscado em R. Então R é

Incremento

incrementado de 1 ou 2 antes de a instrução ser executada.

Indireto

AutoR é primeiro decrementado de 1 ou 2. O novo valor de R é

Decremento

então usado como apontador para o operando.

AutoR é primeiro decrementado de 1 ou 2. O novo valor de R é

Decremento

então usado como endereço de uma posição de memória que

Indireto

contém um apontador para o operando.

O operando está no endereço igual à soma de R (registrador

Indexação

de índice) e o deslocamento de 16 bits em complemento de 2

na próxima palavra.

O contador de programa (R7) é incrementado de 2

imediatamente após a próxima palavra ser buscada.

Indexação +

A posição da memória que contém um apontador para o

Endereçamento operando é encontrada somando o conteúdo de R e o

Indireto

deslocamento de 16 bits em complemento de 2 na próxima

palavra.

O contador de programa (R7) é incrementado de 2

imediatamente após a próxima palavra ser buscada.

• Casos especiais:

∗ Modos 6 e 7 requerem uma constante de 16 bits.

∗ Modo 2 com o registrador R7: endereçamento imediato.

∗ Modo 3 com o registrador R7: endereçamento direto.

∗ Modo 6 com o registrador R7: endereçamento auto-relativo ou

endereçamento independentemente de posição. Se utilizado no

lugar do endereçamento direto, tem-se programas que podem

ser carregados em qualquer posição de memória.

32

♦ Exemplo: possibilidades da instrução MOV R, R4.

Palavra de 16 bits

End.

1000

MOV

(*)

Fonte

Modo

Registrador

Fonte

Fonte

M

R

4

1002

3

3

Destino

0

4

3

3

(Próxima Palavra) K

(*) Considerando as instruções que manipulam palavras, com o primeiro bit igual a 1.

• Nomenclatura:

∗ R - registrador;

∗ $ - operando imediato;

∗ * - indica indireção.

• Um único código de operação produz um grande número

de instruções diferentes, já que os modos de

endereçamento fonte e destinos são especificados

independentemente.

33

Modo

R=0-5

Fonte (M)

0 Move R para R4.

Ex: MOV R3, R4

1 Move a palavra de memória apontada por

R para R4.

2

3

4

5

6

7

R=6

R=7

Move o contador de programa para R4.

Ex: MOV PC, R4

Move K para R4; o contador de programa não

é incrementado, assim K será executado como

a próxima instrução.

Ex: MOV *R3, R4

Ex: MOV *SP, R4

Ex: MOV *PC. R4

Move a palavra de memória apontada por Remove uma palavra da pilha e a coloca Move K para R4 (endereçamento imediato).

R para R4 e soma 2 a R.

em R4 (instrução de desempilhamento).

Ex: MOV (R3)+, R4

Move para R4 a palavra da memória

endereçada pela palavra que R aponta e

soma 2 a R.

Ex: MOV *(R3)+, R4

Decrementa R de 2 e então carrega R4 a

partir do endereço apontado por R.

Ex: MOV -(R3), R4

Decrementa R de 2 e então carrega R4

indiretamente a partir do endereço

apontado por R.

Ex: MOV *-(R3), R4

Carrega R4 com a palavra de memória

em (R) + K (indexação).

Ex: MOV 24 (R3), R4

Carrega R4 com a palavra de memória

apontada por (R) + K (indexação +

endereçamento indireto)

Move o apontador de pilha para R4.

Ex: MOV SP, R4

Move o topo da pilha para R4, mas não

o remove da pilha.

Ex: MOV (SP)+, R4

Desempilha o endereço do operando

fonte e move o próprio operando fonte

para R4.

Ex: MOV *(SP)+, R4

M=4 e R=6 não é fonte útil; entretanto, é

usado como destino em instruções para

empilhar.

Ex. de empilhamento.: MOV $6, -(SP)

Ex: MOV $24, R4

Carrega R4 a partir do endereço de memória

K (endereçamento direto).

Não é usado.

Não é usado.

(causa um loop infinito).

Carrega R4 com a palavra K/2 (posição

abaixo do topo da pilha).

Carrega R4 com a palavra distante K/2

palavras desta instrução (endereçamento autorelativo). Calculada pelo montador.

Ex: MOV X, R4 (X calculado pelo montador)

Carrega R4 com a palavra apontada pela

palavra distante K bytes desta instrução

(endereçamento indireto).

Ex: MOV 24 (SP), R4

Carrega R4 a partir da palavra cujo

endereço está K/2 palavras abaixo do

topo da pilha.

34

Ex: MOV *$24, R4

Não é usado.

(causa um loop infinito).

Ex: MOV *24 (R3), R4

Ex: MOV *24 (SP), R4

35

Ex: MOV *X, R4

(X calculado pelo montador)

Endereçamento na Família Intel: 8088/80286/80386

♦ Os endereçamentos no 8088, 80286 e 80386 (considerando

segmentos de 16 bits) são iguais.

♦ O byte MODO controla os modos de endereçamento. Um

dos operandos é especificado pela combinação dos campos

MOD (2 bits) e R/M (3 bits).

♦ O outro operando é sempre um registrador e é controlado

pelo campo REG.

♦ Para MOD=00 e R/M=000, a soma BX+SI representa um

ponteiro para a memória de onde será obtida a palavra ou

byte, de acordo com bit menos significativo do código de

operação.

MOD

000

001

010

R/M 011

100

101

110

111

00

01

10

11

M[BX + SI]

M[BX + DI]

M[BP + SI]

M[BP + DI]

M[SI]

M[DI]

Endereçamento Direto

M[BX]

M[BX + SI + DISP8]

M[BX + DI + DISP8]

M[BP + SI + DISP8]

M[BP + DI + DISP8]

M[SI + DISP8]

M[DI + DISP8]

M[BP + DISP8]

M[BX + DISP8]

M[BX + SI + DISP16]

M[BX + DI + DISP16]

M[BP + SI + DISP16]

M[BP + DI + DISP16]

M[SI + DISP16]

M[DI + DISP16]

M[BP + DISP16]

M[BX + DISP16]

AX ou AL

CX ou CL

DX ou DL

BX ou BL

SP ou AH

BP ou CH

SI ou DH

DI ou BH

♦ Os modos não são ortogonais.

♦ A indireção é permitida apenas através dos registradores

BX, SI e DI.

♦ Endereçamento direto existe, mas através da eliminação do

registrador BP.

36

♦ Somente algumas combinações de somas de registradores

são permitidas para formar apontadores.

♦ Não existe nenhum modo imediato, que é implementado

através de códigos de operações adicionais.

♦ Não é permitida a auto-indexação.

♦ O MOD=11 indica um segundo operando registrador.

O bit 1 do código de operação indica qual o operando fonte

e destino.

♦ 80386:

• Possui um novo esquema de endereçamento para os

segmentos de 32 bits, que permite o endereçamento

indireto através de mais registradores.

MODO

00

000

001

010

R/M 011

100

101

110

111

M[EAX]

M[ECX]

M[EDX]

M[EBX]

SIB (*)

Endereçamento Direto

M[ESI]

M[EDI]

01

M[EAX + DISP8]

M[ECX + DISP8]

M[EDX + DISP8]

M[EBX + DISP8]

SIB com DISP8

M[EBP + DISP8]

M[ESI + DISP8]

M[EDI + DISP8]

10

M[EAX + DISP32]

M[ECX + DISP32]

M[EDX + DISP32]

M[EBX + DISP32]

SIB com DISP32

M[EBP + DISP32]

M[ESI + DISP32]

M[EDI + DISP32]

11

EAX ou AL

ECX ou CL

EDX ou DL

EBX ou BL

ESP ou AH

EBP ou CH

ESI ou DH

EDI ou BH

(*) SIB - Escala, Índice, Base

• Quando o SIB (Escala, Índice, Base) está presente,

se:

tem-

∗ Endereço do operando é calculado pela soma do

Registrador de Base ao Registrador de Índice

multiplicado pelo fator de escala (1, 2, 4 ou 8). Podese adicionar ainda um deslocamento de 8 ou 32 bits.

37

∗ Exemplo de utilização do SIB: arranjos, como para

o seguinte comando em Pascal:

for i:=0 to n do a[i]:=0;

onde a é um arranjo de 4 bytes locais ao procedimento

corrente.

Pode-se armazenar a[i] numa única instrução, enquanto no

8088 seriam necessárias 4 instruções.

EBP

Estrutura

de Pilha

Outras

variáveis

locais

a[0]

a[1]

a[2]

i em EAX

EBP + 8

EBP + 12

EBP + 16

38

M[4 * EAX + EBP + 8]

Endereçamento na Família Motorola: 68000/68020/68030

♦ Cada operando é especificado por um campo de 6 bits:

• 3 bits para especificar o modo de endereçamento.

• 3 bits para especificar o registrador.

♦ O ponteiro da pilha é endereçável (A7), sendo que todos os

modos de endereçamento de pilha se aplicam.

Modo Reg

0

1

2

3

4

D

A

A

A

A

5

6

A

A

7

7

7

0

1

2

7

3

7

4

Palavra

s

Extras

0

0

0

0

0

Descrição

Operando no registrador D.

Operando no registrador A.

Apontador para o operando no registrador A.

Apontador em A; auto-incrementa A após o uso.

Auto-incrementa A; então usa-o como

apontador.

1

Modo indexado com deslocamento de 16 bits.

1

A + registrador de índice + deslocamento de 8

bits produz o endereço

1

Endereçamento direto com endereço de 16 bits.

2

Endereçamento direto com endereço de 32 bits.

1

O endereço do operando é PC + deslocamento de

16 bits.

1

O endereço do operando é PC + índice +

deslocamento de 8 bits.

1 ou 2 Dado imediato.

♦ Novos modos de endereçamento foram adicionados para

permitir o acesso a arranjos e outras estruturas a partir de

uma única instrução, a partir do 68020.

39

♦ Exemplo de instrução do 680x0:

a) Instrução de um operando no 680x0.

b) Palavra de extensão no 68000.

c) Formato curto da palavra de extensão no 68020 e 68030.

d) Formato completo de palavras de extensão no 68020 e

68030.

Bits

(a)

10

3

3

CÓDIGO DE OPERAÇÃO

MODO

REG

(b)

D/A

REG

W/L

(c)

D/A

REG

W/L ESCALA

D/A

W/L ESCALA 1 BS IS TAM. DE DB

REG

0

DESLOCAMENTO BASE (0, 1 ou 2 palavras)

DESLOCAMENTO EXTERNO (0, 1 ou 2 palavras)

(d)

00

0

DESLOCAMENTO

0

DESLOCAMENTO

I/IS

Legenda:

D/A - 0 seleciona um registrador D; 1 seleciona um registrador A.

REG - seleciona um registrador (0-7) ou um índice.

W/L - 0 indica palavra; 1 indica palavra longa.

ESCALA - 0-3 indica fatores de escala 1, 2, 4 ou 8.

BS - suprime registrador de base.

IS - suprime registrador de índice.

TAMANHO DE DB - Tamanho do deslocamento em relação a base

(0, 1 ou 2 palavras).

I/IS - Seleciona entre indexado ou indireto.

40

Discussão Acerca dos Modos de Endereçamento

♦ Os modos de endereçamento geralmente utilizados pelos

compiladores de linguagens de alto nível são:

• Auto-indexação

∗ Empilhamento e desempilhamento de parâmetros

de procedimentos.

• Direto

∗ Acesso a variáveis globais.

• Imediato

∗ Transferência de constantes.

• Indexado

∗ Acesso a variáveis locais.

• Registrador

∗ Armazenamento de variáveis locais.

• Registrador indireto

∗ Armazenamento de ponteiros de estruturas.

41

PDP-11:

♦ Possui 8 modos de endereçamento, sendo os modos 1, 3, 5, 7

iguais aos modos 0, 2, 4, 6 adicionando-se uma indireção.

♦ Esquema simples, fácil de ser entendido e implementado a

nível de micro-código, e engloba todas as formas de

endereçamento importantes.

Motorola 68000:

♦ Tentou-se copiar o esquema do PDP-11, mas existiam 16

registradores ao invés de 8. Logo, sobrariam 2 bits para o

campo modo.

♦ Optou-se por ter um modo de endereçamento para os

registradores D e a maioria funcionando somente para os

registradores A.

♦ Difere do PDP-11 por não permitir modos de

endereçamento envolvendo o contador do programa.

♦ Os modos de endereçamento mais importantes estão

presentes.

♦ Modos de endereçamento quase ortogonal para os códigos

de operação.

♦ Os processadores 68020 e 68030 incorporaram novos

modos de endereçamento complicados:

• Microcódigo e compiladores mais complicados.

42

Intel 8088 e 80286:

♦ Possuem apenas 2 bits de modo de endereçamento.

♦ Todos os 8 registradores de uso geral são diferentes.

♦ Somente 3 registradores permitem endereçamento indireto

(SI, DI e BX) e somente 4 registradores permitem

indexação (SI, DI, BX e BP).

♦ O modo de endereçamento imediato é suprido pela

existência de códigos de operação específicos para isso.

♦ Não permitem a auto-indexação (existem instruções

específicas para a manipulação de cadeia de caracteres que

implementam a auto-indexação).

♦ Não possui endereçamento de pilha, permitindo o acesso a

pilha através das instruções PUSH e POP. O PUSP não

permite o armazenamento de valores imediatos na pilha.

♦ O 80386 possui um modo de endereçamento melhor com a

criação do byte SIB.

DEC VAX:

♦ Solução para se utilizar mais registradores e manter a

ortogonalidade: 4 bits para o modo e 4 bits para o

registrador.

♦ Cada operando necessita de 1 byte.

♦ Uma instrução de dois operandos necessita de no mínimo 3

bytes.

43

3.3. Tipos de Instrução

Instruções de Transferência de Dados

♦ Transferência de dados significa a cópia de dados de um

lugar para outro, e é a mais fundamental de todas as

operações.

♦ A transferência neste contexto significa a criação de um

novo objeto com o mesmo padrão de bits do original,

deixando a cópia original intacta.

♦ Locais possíveis de armazenamento de dados:

• palavra na memória

• registrador

• pilha (pode ser implementada em registradores ou na

memória, mas a forma de acessá-la é particular).

♦ Devem especificar implicitamente ou explicitamente o

operando fonte (original) e destino (onde será guardada a

cópia).

♦ Exemplos:

• Motorola (680x0):

∗ MOVE: instrução de propósito geral, que permite a

transferência entre registradores, memória ou pilha.

• Intel (8088/80x86):

∗ MOV, etc: instruções bem mais limitadas. Existem

muitas delas, que tornam possível a transferência

entre dois lugares quaisquer.

44

Operações Diádicas

♦ Operações diádicas são aquelas que combinam dois

operandos para produzir um resultado.

♦ Encontramos neste grupo as operações aritméticas e

lógicas.

♦ Instruções Aritméticas:

• Adição, subtração, multiplicação e divisão.

♦ Instruções Lógicas:

• AND, OR, XOR.

• AND: calcula o produto booleano bit a bit de dois

argumentos de uma palavra cada, gerando como

resultado também uma palavra.

∗ Uso importante: extração de bits de uma palavra,

através de uma máscara. A operação AND tende a

remover os bits iguais a 1.

∗ Exemplo: extração do segundo caractere de uma

palavra de 4 bytes para ser imprimido.

◊ Solução: isolá-lo dos demais bytes e justificá-lo à direita.

◊ Extração:

10110111 10111100 11011011 10001011

A

00000000 11111111 00000000 00000000

B (máscara)

00000000 10111100 00000000 00000000

A AND B

• OR: calcula a operação booleana OR bit a bit de dois

argumentos de uma palavra cada, gerando como

resultado também uma palavra.

45

∗ Uso importante: empacotamento de bits em uma

palavra, que significa o inverso da extração. A

operação OR tende a inserir bits 1 no resultado.

∗ Exemplo: trocar os 8 bits mais à direita de uma

palavra de 4 bytes, sem alterar os demais bits.

◊ Solução: limpar o byte a ser alterado, mantendo os

demais, e incluir o novo byte.

◊ Empacotamento:

10110111 10111100 11011011 10001011

A

11111111 11111111 11111111 00000000

B (máscara)

10110111 10111100 11011011 00000000

A AND B

00000000 00000000 00000000 01010111

C

10110111 10111100 11011011 01010111

(A AND B) OR C

• XOR: calcula a operação booleana XOR bit a bit de dois

argumentos de uma palavra cada, gerando como

resultado também uma palavra.

∗ Uso importante: permite a inversão de

determinados bits de uma palavra, aplicando a

operação XOR com um operando que possua 1s

nestes bits. A operação XOR com um bits iguais a 0

não altera o resultado.

∗ É uma operação simétrica, pois na média não tende

nem a inserir nem a remover bits iguais a 1.

46

∗ Exemplo: inverter os 8 bits do segundo caractere de

uma palavra de 4 bytes, sem alterar os demais bits.

◊ Inversão de bits:

10110111 10111100 11011011 10001011

A

00000000 11111111 00000000 00000000

B (máscara)

10110111 01000011 11011011 10001011

A XOR B

♦ Operações aritméticas em ponto-flutuante:

• Antigamente eram implemantada via software.

• Atualmente muitas máquinas possuem instruções de

máquina que implementam operações em ponto-flutuante

diretamente por hardware (maior velocidade).

∗ Tamanho menor dos operandos: maior velocidade.

∗ Tamanho maior dos operandos: maior precisão.

• Em muitos casos estas operações são realizadas por

processadores numéricos, também chamados de coprocessadores. Tais processadores realizam também

outras operações que não sejam de ponto-flutuante.

47

Operações Monádicas

♦ Operações monádicas são aquelas que têm um operando e

produzem um resultado.

♦ Em geral são mais curtas que as operações diádicas, pois só

necessitam da especificação de um operando.

♦ Encontramos neste grupo as operações para deslocar e

rodar o conteúdo de uma palavra.

♦ Deslocamentos: são operações nas quais os bits do

operando são movidos para a esquerda ou direita,

perdendo os bits deslocados para fora da palavra,

formando o resultado.

• As posições vagas são preenchidas com 0.

• Um deslocamento para a direita de k bits significa uma

divisão do operando por 2k.

• Um deslocamento para a esquerda de k bits significa uma

multiplicação do operando por 2k.

• Exemplo: deslocamento de 2 bits de uma palavra para a

direita.

00000000 00000000 00000000 01110011

A

00000000 00000000 00000000 00011100 11

A deslocado

de 2 bits para

a direita

48

♦ Rotações: são operações nas quais os bits do operando são

movidos para a esquerda ou direita, sendo que os bits que

saem da palavra reaparecem do outro lado, formando o

resultado.

• Exemplo: rotação de 2 bits de uma palavra para a direita.

00000000 00000000 00000000 01110011

A

11000000 00000000 00000000 00011100

A rodado de 2

bits para a

direita

• Propriedade: “Se uma palavra de n bits é rodada k bits

para um lado, o resultado é o mesmo caso tivesse sido

rodada n-k bits para o outro lado”.

♦ Deslocamentos com sinal: são operações de deslocamentos

para a direita que mantêm o sinal do operando para gerar

o resultado.

• Na prática, isso significa que as posições vagas do lado

esquerdo são preenchidas com o bit de sinal original, 0 ou

1. Logo, um número negativo permanecerá negativo.

49

• Exemplo: deslocamento de 2 bits de uma palavra para a

direita, sem a extensão do sinal e com a extensão do sinal.

11111111 11111111 11111111 11110000

00111111 11111111 11111111 11111100

11111111 11111111 11111111 11111100

A

A deslocado de 2 bits

para a direita sem

extensão do sinal

A deslocado de 2 bits

para a direita com

extensão do sinal

♦ Certas operações diádicas muito utilizadas com operandos

específicos podem ser fornecidas na forma monoádica.

• Exemplos:

∗ Mover o valor 0 para uma palavra de memória ou

registrador:

◊ Instrução CLEAR.

∗ Somar/subtrair 1 a/de uma palavra de memória ou

registrador:

◊ Instrução INC/DEC.

∗ Negar o valor de X (significa fazer a operação

0 - X):

◊ Instrução NEGATE.

• Intel: as suas CPUs fornecem instruções INC e DEC.

• Motorola: as suas CPUs fornecem instruções mais

genéricas, ADDQ e SUBQ que podem somar ou subtrair

uma constante na faixa de 1 a 8.

50

Comparações e Desvios Condicionais

♦ Praticamente todos os programas precisam da capacidade

de testar seus dados e alterar a seqüência de instruções a

serem executadas.

• Exemplo:

x

∗ Se x é negativo, retorna mensagem de erro; caso

contrário, calcular a raiz quadrada de x.

♦ Solução: a máquina deve possuir instruções de salto

condicional (desvio condicional).

♦ As instruções de desvio condicional testam alguma

condição e saltam para um determinado endereço se a

condição é satisfeita, e continuam a seqüência normal do

programa caso contrário.

• O desvio pode ocorrer se uma determinada condição for

satisfeita ou então se uma determinada condição não for

satisfeita, de acordo com algum bit da instrução.

♦ A condição mais comum a ser testada é se um bit específico

na máquina é 0 ou 1.

51

• Exemplo: teste do bit de sinal de um resultado.

∗ Se o bit de sinal é 1 (número negativo), o programa

continua a partir do endereço Rótulo. Se o bit de

sinal é 0, o programa continua a partir da instrução

seguinte a instrução de salto.

Rótulo:

JNEG REG1, Rótulo

INSTR

1

INSTR

2

.

.

INSTR

3

INSTR

4

.

.

; desvia se o registrador REG1 for negativo.

; próxima instrução caso REG1 seja positivo.

; próxima instrução caso REG1 seja negativo.

♦ Muitas máquinas possuem bits que são utilizados para

indicar condições específicas, denominados flags de

máquina. Os flags, de certa forma, indicam o estado atual

do processador, e em geral refletem o ocorrido na ULA após

a última operação lógica ou aritmética executada.

• Exemplo: vai-um do bit mais a esquerda de uma

operação, indicando o estouro numa operação aritmética.

♦ Teste do bit mais a direita de uma palavra: permite avaliar

se um número é par ou ímpar.

♦ Teste por zero: permite avaliar se uma palavra é 0 ou não,

sendo importante para loops.

52

♦ Comparação entre duas palavras: permite avaliar se elas

são iguais ou qual é a maior.

• Instrução que a princípio precisa de três endereços: dois

para os operandos e um para o endereço de desvio.

• Se a máquina não permite instruções de três endereços,

uma solução é disponibilizar dois tipos de instruções:

∗ Instrução de comparação, que armazena alguns bits

de condição a respeito do resultado.

∗ Instrução de desvio condicional, que consulta os bits

de condição e eventualmente faz o desvio.

∗ Este tipo de solução é adotada pelas famílias

Motorola e Intel.

♦ O resultado de uma comparação depende dos sinais dos

operandos. Em geral, faz-se a comparação entre dois

valores de mesmo sinal, ou precisa-se ter instruções

específicas para números sem sinal e números com sinal.

Sem sinal

0

1

2

3

4

5

6

7

Com sinal

000

001

010

011

100

101

110

111

100

101

110

111

000

001

010

011

-4

-3

-2

-1

0

1

2

3

♦ Outra forma de desvio condicional: pular a próxima

instrução.

♦ Desvio Incondicional é um desvio que sempre é satisfeito.

Logo, necessita de um endereço somente.

53

Instruções de Chamada de Procedimentos

♦ Procedimento ou sub-rotina ou simplesmente rotina: é um

grupo de instruções que realiza uma tarefa e que pode ser

chamado de diversas partes do programa.

♦ Um procedimento, após ser executado, deve retornar para o

comando após a sua chamada.

• O procedimento deve receber de alguma forma o endereço

para onde ele deve retornar após realizar a sua tarefa

(endereço de retorno).

• Formas de se armazenar o endereço de retorno:

∗ Memória:

◊ Posição Fixa: não permite encadeamentos de subrotinas.

◊ Primeira palavra da sub-rotina: cada sub-rotina sabe

onde buscar o endereço de retorno. Não permite recursão

direta ou indireta.

∗ Registrador:

◊ A instrução de chamada de sub-rotina armazena o

endereço de retorno num registrador, deixando a cargo

da sub-rotina armazenar o endereço num local seguro.

∗ Pilha:

◊ A instrução de chamada de sub-rotina armazena o

endereço de retorno na pilha. A sub-rotina, para retornar,

desempilha o endereço da pilha e o coloca no contador

do programa (logo, retorna).

◊ Método utilizado pela Intel e Motorola.

54

Controle de Loop

♦ Um programa em geral necessita executar um grupo de

instruções um número fixo de vezes - loop.

♦ O controle de loop pode ser implementado através das

instruções elementares, devendo:

• Ter um contador, que é decrementado ou incrementado de

uma constante a cada interação.

• Testar o contador a cada interação, terminando o loop se

uma condição for atingida.

♦ Tipos de loop:

• Loop com teste no final

∗ Sempre será executado ao menos uma vez. Falha

para n igual a zero.

• Loop com teste no início

♦ Exemplos de controles de loops:

i:=1;

1:

2:

i:=1;

{primeiro comando}

{segundo comando}

.

.

{último comando}

i := i + 1;

if i <= n then goto 1;

{primeiro comando após o loop}

1:

2:

(a) teste no final

if i > n then goto 2;

{primeiro comando}

{segundo comando}

.

.

{último comando}

i := i + 1;

goto 1;

{primeiro comando após o loop}

(b) teste no início

Código equivalente em Pascal

for i := 1 to n do begin ... end

55

♦ Algumas máquinas podem disponibilizar instruções

especiais que fazem o controle de contagem de interações,

teste de condição e desvio numa única instrução.

• Intel:

∗ 8088/80286: Instrução LOOP, que decrementa o

registrador CX de 1 e salta para um dado rótulo se

o resultado não for 0. Se for 0, a execução continua a

partir da próxima instrução.

∗ 80386: Idem para o registrador ECX.

• Motorola:

∗ Instrução para uma solução mais geral:

◊ Primeiro testa uma determinada condição, que se não

satisfeita, encerra o loop.

◊ Decrementa um registrador D, que se resultar num valor

maior ou igual a 0, repete o loop; caso contrário, encerra

o loop.

56

Entrada e Saída

♦ Apresentam grande variação de máquina para máquina.

♦ Se o espaço de endereçamento de entrada e saída (E/S) não

estiver mapeado em memória (ou seja, os dispositivos de

E/S também possuem endereços, da mesma forma que a

memória), devem existir instruções especiais (mapeamento

em E/S) que permitam:

• A leitura de um dado num dispositivo de entrada.

∗ Instrução: IN.

• A escrita de um dado num dispositivo saída.

∗ Instrução: OUT.

♦ Intel:

• Instruções específicas para E/S: IN e OUT:

∗ Especificam o endereço da porta de E/S de forma

direta ou indireta via registrador DX.

∗ Utilizam o registrador AX / EAX como elemento de

transferência entre o dispositivo e a CPU.

♦ Motorola:

• Registradores dos dispositivos são endereçados via

mapeamento de memória.

57

3.4. Fluxo de Controle

♦ O Fluxo de controle corresponde à seqüência na qual as

instruções são executadas.

♦ As instruções executadas sucessivamente são buscadas de

posições de memória consecutivas.

♦ As alterações do fluxo normal de controle do programa

podem ocorrer através de:

• Chamadas de Procedimentos.

• Co-rotinas.

• Armadilhas (Traps).

• Interrupções.

58

Fluxo de Controle Seqüencial e Desvios

♦ Após a execução de cada instrução:

• O contador de programa é incrementado do número de

posições de memória da instrução (comprimento da

instrução).

• A próxima instrução é buscada na memória e executada.

♦ Ao longo do tempo, o contador do programa é

aproximadamente uma função linear crescente em função

do tempo (as instruções são executadas na ordem em que

aparecem numa listagem).

• Se não houver desvio (a), o contador avança linearmente.

• Se houver desvio (b), o contador avança linearmente por

partes, entre os desvios.

C

O

N

T

A

D

O

R

C

O

N

T

A

D

O

R

D

O

D

O

P

R

O

G

R

A

M

A

P

R

O

G

R

A

M

A

Tempo

(a) Sem desvios

Desvios

Tempo

(b) Com desvios

59

Procedimentos

♦ A utilização de procedimentos é a técnica mais importante

para se estruturar programas.

♦ A chamada de um procedimento altera o fluxo de controle

do programa, como ocorre com um desvio, mas permite o

retorno para a instrução seguinte à instrução de chamada.

♦ A instrução de chamada de um procedimento pode ser

entendida como uma instrução de alto nível. O que importa

é o que o procedimento faz, não como ele faz.

♦ Procedimento recursivo: é um procedimento que chama a si

mesmo.

• Exemplos de problemas solucionados através de

procedimentos recursivos:

∗ Torre de Hanói.

∗ Fatorial: 5! = 5 * 4! = 5 * 4 * 3! = 5 * 4 * 3 * 2! ...

60

♦ Chamada de um procedimento B a partir de um

procedimento A:

(A)

(B)

Procedimento

que chama

Procedimento

chamado

A chamado

pelo

programa

principal

A retorna

ao programa

principal

♦ O procedimento B sempre começa do seu início.

♦ Sistema de chamada e retorno de um procedimento:

• O procedimento A utiliza uma instrução de chamada de

sub-rotina (p.ex. CALL), que armazena o endereço de

retorno, por exemplo, no topo da pilha, e carrega o

contador do programa com o endereço do procedimento

B.

• Para retornar, o procedimento B executa uma instrução

de retorno (p.ex. RET), que retira do topo da pilha o

endereço de retorno e o transfere para o contador do

programa.

61

Co-rotinas

♦ Co-rotinas são procedimentos que chamam uns aos outros,

sendo que a cada nova chamada o procedimento continua

do ponto onde parou na última vez, ou seja, a partir do

comando seguinte ao último retorno.

(A)

(B)

A chamado

pelo

programa

principal

A retorna

ao programa

principal

♦ Este esquema pode ser implementado se existir alguma

instrução que permita trocar o topo da pilha com o

contador do programa. Inicialmente é necessário a

colocação do endereço de uma das duas co-rotinas na pilha.

• Uma instrução de chamada de co-rotina é denominada de

resume.

62

Armadilhas (Traps)

♦ Uma armadilha ou trap é um tipo de chamada automática

de procedimento disparada por alguma condição causada

pelo programa; em geral, uma condição importante ou

rara.

♦ Exemplo: estouro numa operação aritmética (overflow).

• Numa operação aritmética, ao ocorrer um resultado que

excede o maior número que puder ser representado,

ocorre um trap, o que significa que o fluxo de controle

será transferido para alguma posição fixa na memória

em vez de continuar seqüencialmente.

• A partir desta posição fixa, existe um salto para um

procedimento denominado rotina de tratamento de trap,

que toma alguma ação apropriada (quem faz esta rotina

de tratamento do trap coloca esta instrução de desvio).

♦ O trap pode ser considerado uma interrupção de caráter

síncrono, pois ocorre sincronamente com a execução da

instrução.

♦ Exemplos de Traps:

• Overflow e Underflow em ponto-flutuante.

• Overflow em inteiro.

• Violação de proteção.

• Código de operação indefinido.

• Estouro da pilha.

• Divisão por zero.

63

Interrupções

♦ Uma interrupção ou conjunto de interrupções é um

mecanismo que permite suspender temporariamente a

execução de um programa, para tratar um evento, de

forma a possibilitar o seu posterior prosseguimento de

execução.

♦ As interrupções podem ser classificadas em:

• Interrupções Síncronas ou Traps: são interrupções cujo

evento está diretamente sincronizado com a execução de

uma determinada instrução.

∗ Exemplos: overflow, divisão por zero.

• Interrupções Assíncronas: são interrupções relacionadas

a eventos externos.

∗ Exemplos: o pressionar de uma tecla num

computador.

♦ Uma interrupção pára o programa em execução e transfere

o controle do programa para uma sub-rotina de tratamento

de interrupção, que executa alguma ação apropriada. Ao

terminar de tratar o evento, a sub-rotina de tratamento de

interrupção retorna o controle para o programa

interrompido.

♦ As interrupções possuem duas fases distintas:

• Reconhecimento da interrupção por parte da CPU.

• Tratamento da interrupção (execução da sub-rotina de

tratamento de interrupção ou rotina de serviço).

64

♦ Problemas: o programa interrompido deve voltar a ser

executado no mesmo estado em que estava antes de ocorrer

a interrupção.

♦ As interrupções assíncronas podem ser implementadas

num determinado hardware de duas formas:

• Interrupções diretas por hardware: são aquelas

interrupções que vêm diretamente dos dispositivos de E/S

para a CPU que sabe, a partir do sinal de interrupção em

particular, em que local da memória (fixo) buscar o

endereço da sub-rotina de tratamento da interrupção.

• Interrupções vetoradas: são interrupções que fornecem,

além do sinal de pedido de interrupção, o vetor de

interrupção (número inteiro que identifica o dispositivo)

pela via de dados do sistema.

∗ Permite a canalização de diversos pedidos de

interrupção através de um único sinal.

∗ O gerenciamento dos diversos pedidos é feito

externamente por um controlador de interrupção.

`

INT

Controlador

do

Dispositivo

de

E/S

INTA

DADOS

CPU

Vetor de

Interrupção

♦ Considerando a ocorrência de uma interrupção vetorada,

existem procedimentos a serem realizados pelo hardware e

65

procedimentos a serem realizados pelo software, que em

conjunto, devem garantir o tratamento do evento e o

posterior prosseguimento do programa interrompido, como

se nada tivesse ocorrido.

• Tarefas do Hardware:

1. O controlador do dispositivo gera um pedido de

interrupção (INT - Interrupt Request).

2. Quando a CPU puder atender ao pedido de interrupção

(por exemplo, ao terminar de executar a instrução

corrente), ela envia um sinal de reconhecimento de

interrupção (INTA - Interrupt Acknoledge).

3. Recebendo o reconhecimento da interrupção, o

controlador do dispositivo envia pela via de dados o seu

número de identificação (vetor de interrupção).

4. A CPU obtém o vetor de interrupção e o armazena

internamente.

5. A CPU salva o seu status mínimo, (PSW - Processor

Status Word), na pilha, como o Contador do Programa, o

Acumulador e os Flags de Máquina.

6. A CPU carrega o Contador do Programa com o endereço

da sub-rotina de tratamento daquela interrupção, obtido

da memória (tabela de vetores de interrupção), a partir do

vetor de interrupção recebido.

∗ Por exemplo, se o dispositivo tem número n e os

endereços são de 2 bytes (portanto, o Contador do

Programa tem 2 bytes), o endereço da sub-rotina é

obtido nas posições de memória [2*n] e [2*n+1].

66

Memória

Tabela

de

Vetores

de

0000h

0002h

0004h

0006h

0008h

000Ah

Endereço do vetor 0

Endereço do vetor 1

Endereço do vetor 2

Endereço do vetor 3

Endereço do vetor 4

Endereço do vetor 5

000Ch

000Eh

Endereço do vetor 6

Endereço do vetor 7

Interrupção

• Tarefas do Software:

1. A sub-rotina de tratamento da interrupção salva o

conteúdo dos registradores da CPU que irá utilizar, por

exemplo, na pilha.

2. A sub-rotina realiza a sua tarefa propriamente dita: a

operação de E/S (por exemplo, lê o código da tecla

pressionada e o armazena num buffer).

3. A sub-rotina restaura o conteúdo dos registradores

salvos.

4. A sub-rotina executa uma instrução de retorno da

interrupção, permitindo a CPU recuperar o seu status

mínimo (PSW).

5. O programa interrompido prossegue então como se a

interrupção não tivesse ocorrido.

♦ Conceito relativos a interrupção:

• Transparência: uma sub-rotina de interrupção é dita

transparente quando após o retorno da sub-rotina o

programa interrompido volta para o estado exato em que

estava anteriormente a chegada da interrupção.

• Mascaramento: mecanismo que permite desabilitar uma

interrupção ou um conjunto de interrupções.

67

• Simultaneidade de Interrupções: se duas interrupções

ocorrem ao mesmo instante, a de maior prioridade será

atendida.

68

• Uma interrupção pode ocorrer enquanto outra está sendo

tratada pela sua sub-rotina de tratamento. Soluções

possíveis:

∗ Inibição: todas as sub-rotinas de tratamento de

interrupção inibem interrupções subseqüentes antes

de tomar qualquer outra atitude.

◊ Problema: pode-se perder outras interrupções.

∗ Prioridade: cada interrupção tem uma prioridade

diferente, definida na PSW, por exemplo. Eventos

mais prioritários são atribuídos a interrupções de

maior prioridade. Quando uma interrupção de

prioridade n estiver sendo tratada, somente eventos

mais prioritários podem interrompê-la; eventos

menos prioritários devem aguardar.

69

♦ Exemplo: Supor um sistema com uma impressora, um disco

e uma interface RS232, com prioridades 2, 4 e 5

respectivamente.

Interrupção

da disco.

Prioridade 4.

Pendente.

RSI da RS232

termina.

Interrupção

do disco

Interrupção

da RS232.

Interrupção Prioridade 5.

da

impressora.

Prioridade

2.

0

10

15

RSI do disco

termina.

RSI da

impressora

termina.

20

25

35

40

Tempo

Programa RSI da

impresdo

sora

usuário

RSI

da

RS232

Usuário

Usuário

RSI

do

disco

Usuário

Usuário

Impressora Impressora

Impressora

70

RSI da Program

a do

impresusuário

sora

Pilha

Intel

♦ Possuem dois níveis de prioridade:

• Interrupções não mascarável: utilizadas para sinalizar

catástrofes, como erro de paridade.

• Interrupções mascaráveis:

∗ Utilizam o vetor de interrupção para indexar uma

tabela de 256 entradas de 4 bytes cada, para

encontrar o endereço da rotina de serviço de

interrupção.

◊ 8088: vetor começa na posição de memória 0.

◊ 80286/80386: vetor pode começar em qualquer lugar da

memória.

∗ A prioridade é fornecida por um controlador de

interrupção externo 8259A. A CPU deve indicar

quando a rotina de serviço terminou, sinalizando

isso através de uma escrita num registrador do

8259A.

Motorola:

♦ Possuem 256 vetores de interrupção de 4 bytes cada, a

partir do endereço 0 de memória.

♦ Possui 3 pinos para indicar níveis de prioridade de 0 a 7. O

nível 7 não é mascarável.

♦ Existem três bits no PSW que permitem definir a

prioridade.

71