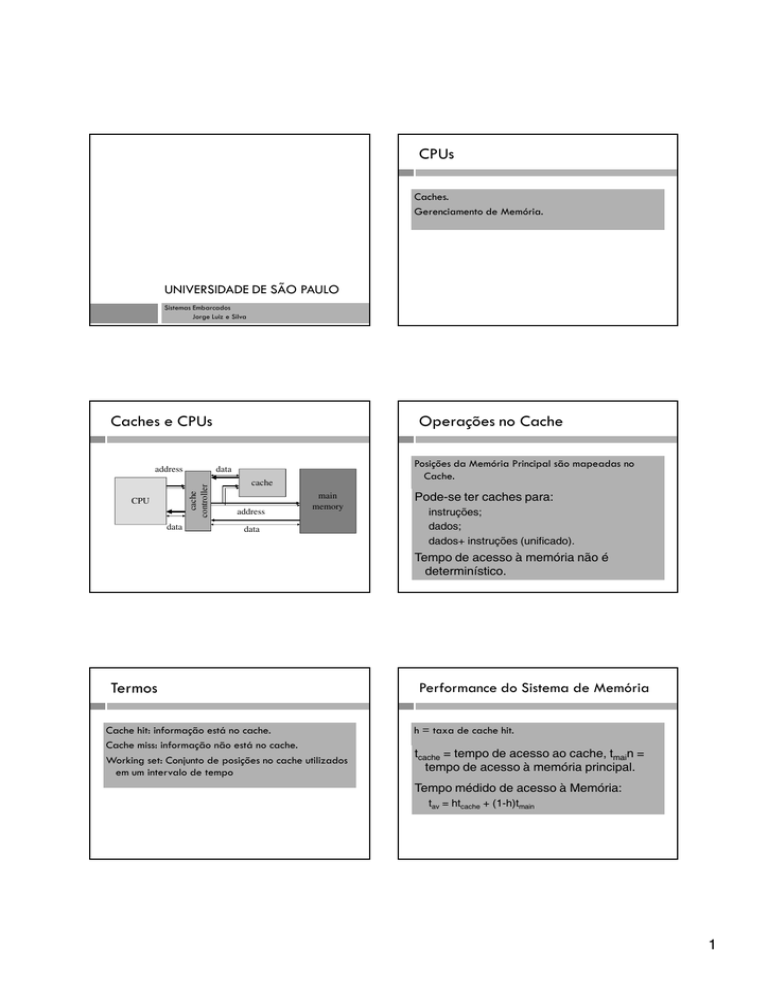

CPUs

Caches.

Gerenciamento de Memória.

UNIVERSIDADE DE SÃO PAULO

Sistemas Embarcados

Jorge Luiz e Silva

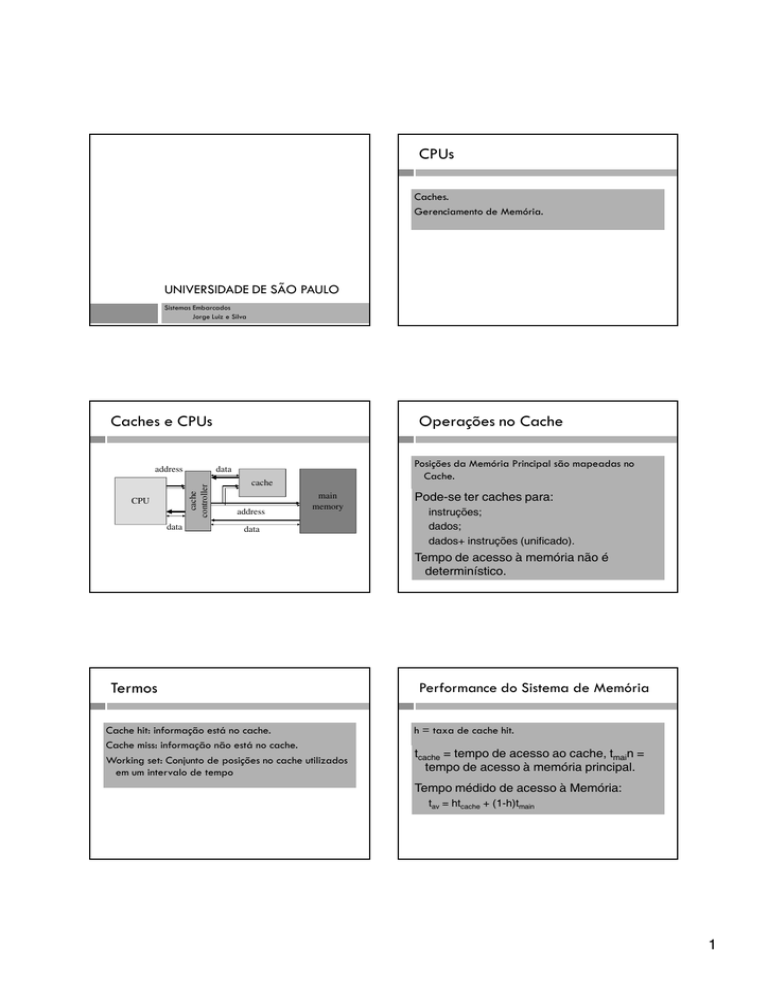

Caches e CPUs

CPU

data

Posições da Memória Principal são mapeadas no

Cache.

data

cache

controller

address

Operações no Cache

cache

address

main

memory

data

Pode-se ter caches para:

instruções;

dados;

dados+ instruções (unificado).

Tempo de acesso à memória não é

determinístico.

Termos

Cache hit: informação está no cache.

Cache miss: informação não está no cache.

Working set: Conjunto de posições no cache utilizados

em um intervalo de tempo

Performance do Sistema de Memória

h = taxa de cache hit.

tcache = tempo de acesso ao cache, tmain =

tempo de acesso à memória principal.

Tempo médido de acesso à Memória:

tav = htcache + (1-h)tmain

1

Tempo de acesso para Múltiplos níveis de

cache

Múltiplos níveis de cache

h1 = taxa de cache hit.

h2 = Taxa para miss em L1, hit em L2.

CPU

L1 cache

L2 cache

Tempo médio de acesso à memória:

tav = h1tL1 + (h2-h1)tL2 + (1- h1-h2)tmain

CPU

Políticas de Reposição

Politica de Reposição: estratégias para escolher no

cache quem sai e quem fica.

Duas estratégias populares:

Random.

Least-recently used (LRU).

L1 cache

L2 cache

Organização do Cache

Fully-associative: Qualquer posição de memória pode

ser armazenado em qualquer posição no cache

(nunca foi implementado).

Direct-mapped: cada posição de memória é

mapeado exatamente em uma posição no

cache.

N-way set-associative: cada posição de memória

pode estar em uma de n posições.

Operações de Write

Write-through: copia imediatamente na memória

principal.

Write-back: copia para a memória principal

somente quando a posição é removida do

cache.

Memory management units

Memory management unit (MMU) translates

addresses:

logical

address

CPU

physical

memory

address

management

unit

main

memory

2

Terefas da MMU

Translação de Endereços

Mover programas para memória física durante

execução.

Requer registradores/tabelas para permitir um

mapeamento para endereços físicos.

Memória Virtual:

Dois esquemas básicos:

Imagem da memória em memória secundária;

Imagem retorna para a memoria principal em

função de execução.

Falta de Página: solicita por posições não

presentes na memória principal.

Segmentos e Páginas

page 1

page 2

segment 1

memory

segmentado;

paginado.

Segmentação e paginação podem ser

combinados.

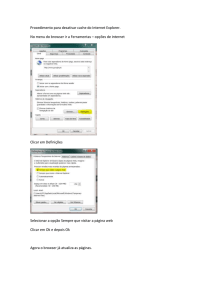

Translação de endereço de Cache

Tabela grande de translação requer acesso à

memória principal.

TLB(Translation Lookaside buffer) : Para

translação de endereço em cache.

pequeno.

segment 2

3