Universidade Federal do Rio Grande do Norte

CT – Centro de Tecnologia

DEE – Departamento de Engenharia Elétrica

Disciplina: Instrumentação Eletrônica

Professor: Luciano Fontes

RELATÓRIO

Capacímetro Digital

Aluno: Eilson Siqueira Spínola

Natal, Novembro de 2008

RESUMO

Este texto expõe detalhes operacionais e construtivos de um modelo de medidor

digital de capacitância – capacímetro –, baseado no tempo de carga e descarga de um

capacitor através de uma resistência. Arquitetamos o projeto a partir dessa concepção, e

iremos aqui esmiúça-lo, para a melhor compreensão possível.

SUMÁRIO

1. INTRODUÇÃO: ESTADO DA ARTE EM CAPACÍMETROS

2. PROJETO PROPOSTO: DIAGRAMA EM BLOCOS

3. O MONOESTÁVEL

4. FAIXA DE TRABALHO: CÁLCULOS DO PROJETO

5. LÓGICA DOS CONTADORES

6. CIRCUITO COMPLETO

7. MATERIAL UTILIZADOS

8. RESULTADOS E CONCLUSÕES

9. REFERÊNCIAS

4

5

6

7

8

9

9

9

9

1. INTRODUÇÃO: ESTADO DA ARTE EM CAPACÍMETROS DIGITAIS

TIPOS DE CAPACÍMETROS

Os capacímetros são encontrados em duas topologias básicas: pontes LCR, que além

de medir capacitância, podem medir indutância e resistência através de um detector

“Zero Volts”, e os capacímetros digitais, que são baseados no tempo de descarga de

capacitores, interpretado digitalmente.

Entre os capacímetros digitais, encontramos versões portáteis e versões de bancada,

variando muito na tecnologia empregada. Porém, generalizadamente os capacímetros

digitais são construídos com CI’s CMOS, Amp. Ops. e, às vezes, com

microprocessadores, que são responsáveis pela mudança automática de escala.

(a)

(b)

Figura 1 – (a) Ponte RLC, (b) capacímetro digital portátil

1.2. TÉCNICAS DE MEDIÇÃO

As técnicas de medição utilizadas nos capacímetros digitais podem ser realizadas

através de circuito integradores, ou então de monoestáveis, como aqui em nosso projeto.

Mostraremos a seguir o diagrama de blocos da técnica mais utilizada, com integradores

e um microprocessador.

Figura 2 – Diagrama em blocos de um dos principais tipos de capacímetro

Sem entrar em detalhes de projeto, o funcionamento de tal tipo de circuito pode ser

resumido:

O microprocessador controla o nível de corrente aplicado ao circuito

analógico, reconhecendo a escala adequada ao capacitor em teste. A rampa

integrada é continuamente comparada com uma tensão de referência, e

quando a ultrapassa, interrompe o circuito analógico.

A tensão remanescente no capacitor, o nível de corrente utilizado, e a

contagem digital são armazenados no registrador, que, por último, tem seus

dados acessados pelo microprocessador.

O microprocessador tem então a tarefa de processar esses dados e enviar o

valor da capacitância para o display.

CARACTERÍSTICAS TÉCNICAS

•A maioria dos capacímetros portáteis no comércio apresenta 4 dígitos e 7 ou 8 escalas

diferentes de medição.

Tabela 1 – Faixas nominais

MÁXIMA INDICAÇÃO

RESOLUÇÃO

(MOSTRADOR DIGITAL)

200 pF

199,9 pF

0,1 pF

2 nF

1,999 nF

0,1 pF

20 nF

19,99 nF

10 pF

200 nF

199,9 nF

100 pF

2 µF

1,999 µF

1000 pF

20 µF

19,99

0,01 µF

200 µF

1999 µF

1 µF

FAIXA NOMINAL

• A exatidão geralmente é dada por:

+/- ( 1,0% da leitura + 1 dígito )

Mostrador digital: 0,5" (13mm) cristal líquido.

Razão de leitura: 2 leituras/seg.

Indicação de Bateria Descarregada ( LO BAT )

Alimentação: bateria 9VCC ou eliminador de baterias

2. PROJETO PROPOSTO: DIAGRAMA EM BLOCOS

Figura 3 – Diagrama em blocos do capacímetro

A idéia do projeto, representada no diagrama em blocos acima, é bastante

simples. O monoestável produz um nível alto em sua saída durante um determinado

tempo, denominado largura de pulso. A largura de pulso será proporcional à

capacitância aplicada ao monoestável. Enquanto a saída do monoestável estiver em

nível alto, a porta “AND” habilitará a passagem do clock, iniciando o processo de

contagem. O clock, que pode ser produzido por um gerador de sinais ou por um circuito

astável, terá sua freqüência ajustada de tal forma, que durante a sua habilitação produza

tantos pulsos (ou períodos) quanto à capacitância correspondente. Finalmente, a

contagem binária BCD armazenada no contador será decodificada para decimal, e

mostrada em um display.

5V

+

GERADOR DE CLOCK

0.01uF

555

Gnd

Trg

Out

Rst

Vcc

Dis

Thr

Ctl

R2

40k

+

Saída de clock

R1

40k

C2

1uF

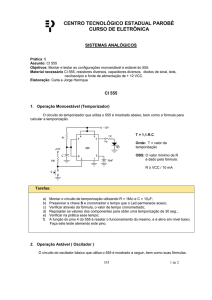

O gerador de clock consiste no CI 555, no modo astável, ao qual são acoplados

duas resistências e dois capacitores. Seguem abaixo os cálculos dos valores das

resistências e dos capacitores para atingir a freqüência de 99Hz que gerará a base para a

escala do capacímetro.

1.44

frequency

( R A 2 RB )C

1.44

99

( RA 2 RB ).1

RA 2RB 14,545k

3. O MONOESTÁVEL

Utilizamos o CI 555 para funcionar como monoestável. A configuração do

circuito como monoestável é mostrada abaixo:

Figura 4 – Bloco monoestável com 555

A fórmula teórica para calcular o tempo em que, após o disparo, o pino 3 ficará em

nível lógico 1 (+Vcc = 5V) é dada por:

T = 1,1 x R x C

Onde: T = tempo em segundos; R = resistor R em ohms; C = capacitor C em Farads.

Entretanto, a constante 1,1 é apenas teórica, sendo imprecisa na prática. Testamos a

configuração com diversos resistores e capacitores, e obtivemos uma constante média

de 1,2.

TMONO=1,2 x R x C

Na condição de "stand by", o circuito integrado encontra-se em repouso. O pino de

disparo (pino 2) ficará com nível lógico 1 (+Vcc = 5V) e o pino 3, com nível lógico 0

(0V). No instante em que o pino 2 for posto em nível lógico 0, o pino 3 passará ao nível

1 instantaneamente e assim permanecerá enquanto se mantiver o nível 0 no pino 2.

Ocorrendo uma nova transição de nível do pino 2, o circuito continuará apresentando o

nível 1 no pino 3 só que durante o tempo determinado pela fórmula acima. Esgotado

este tempo, o pino 3 retornará ao nível 0 e o circuito entrará novamente em "stand by".

Figura 5 – Diagramas do 555

Função dos componentes no circuito

-R1 - Resistor de polarização. Responsável por manter o pino 2 do CI555 sempre em

nível lógico 1 na ausência do sinal de disparo (nível lógico 0). É da ordem de 2,2 KΩ.

-Pino 8 e 1 - São os pinos de alimentação do circuito integrado 555.

O pino 4 tem a função de "reset". Quando o nível lógico neste pino for 1, o circuito

funciona normalmente porém, se o nível lógico for 0, o circuito fica bloqueado

apresentando o nível lógico 0 no pino 3 independentemente do nível lógico presente no

pino 2.

-R e C - Conjunto RC que determina o tempo em que o pino 3 do circuito integrado 555

ficará em nível lógico 1 após a mudança de estado (pino 2) de 0 para 1.

-A conexão do pino 5, nesta configuração, é opcional. Conecta-se um capacitor de 100

nF entre este pino e o terra (pólo negativo) afim de dar mais estabilidade ao circuito.

Esta é a recomendação do fabricante.

4. FAIXA DE TRABALHO: CÁLCULOS DO PROJETO

Como um protótipo, nosso experimento será restringido a apenas dois displays,

isto é, apenas dois dígitos representarão a capacitância, nos levando a adotar uma faixa

de medição de 0 a 99 sub-unidades de Farad. Inicialmente escolhemos μF, mas

facilmente poderemos comutar o circuito para qualquer uma outra.

Em nosso circuito, deseja-se que a contagem final do contador, ou seja, o

número de pulsos de clock incrementados pelo mesmo, seja numericamente igual a

capacitância a ser medida. A resolução será então de 1 μF, onde cada μF corresponderá

a um pulso de clock. Se escolhermos a largura de pulso do monoestável para o capacitor

de 99 μF como sendo de 1 segundo, teremos:

TMONO 1,2 R 99 106 1s R 8,42k

e a freqüência do clock será de 99Hz, já que deverão passar 99 pulsos ao contador em

um segundo.

f clock 99Hz

Para uma mudança de escala para ŋF, por exemplo, basta que multipliquemos a

resistência R por de 1000, sem alterar a freqüência de clock.

5. LÓGICA DOS CONTADORES

O problema aqui é que temos que fazer com que dois contadores binários atuem como

um contador BCD de dois dígitos. Isto é realizado com a lógica mostrada no diagrama

abaixo.

Figura 6 – Diagrama de conexão dos contadores

O contador LS (Least Signicant ou Menos Significante) deverá contar

ciclicamente de 0 a 9. Chegando a 10, manda um bit para o contador MS (Most

Significant ou Mais Significativo) e se auto-apaga, ficando preparado para mais um

ciclo. Como 10 em binário é 1010, os bit D e B são nível “1” e habilitam o reset LS, ao

mesmo tempo que mandam um pulso para o MS. O circuito será inibido quando uma

capacitância ultrapassar a faixa de 99 μF, ou seja, os contadores MS e LS atingem a

contagem 1010 simultaneamente. Nesse estágio, os dois contadores serão apagados e

um flip-flop armazenará “0” em sua saída invertida, fazendo com que o clock tenha

sua passagem inibida.

6. CIRCUITO COMPLETO

Figura 7 – Circuito completo

7. MATERIAL UTILIZADO (Simulador)

•2 CI TIMER 555

•2 CIs CONTADORES 4 BITS TTL – 7493

•2 CIs DECODIFICADORES BCD TTL – 7447

•2 DISPLAYS ANODO COMUM

•1 CI AND-3 PORTAS TTL –7411

•1 CI OR-2 PORTAS TTL - 7432

•1 CI INVERSOR TTL – 7404

•1 CI FLIP-FLOP JK TTL - 7473

•RESISTORES

3 x 14,5K

1 x 2,2K

1 x 1K

1 x 8,2K

•CAPACITORES

8. RESULTADOS E CONCLUSÕES

• A experiência foi valiosa por, além de exercitarmos o lado teórico e projetista, também

o fazemos com o lado prático e engenhoso, principalmente em hora de solucionar

problemas.

9. REFERÊNCIAS

• Notas de aula da disciplina Instrumentação Eletrônica, Prof. Luciano Fontes.

• Datasheets de CIs TTL, Texas Instruments.

• www.inf.ufsc.br/~hung/disciplinas/eel5310/frequencimetro.doc

• Tocci, Albert. Sistemas Digitais, 7a Edição.